# Article **PSP-Equivalent Model for Double-Gate and Surrounding-Gate Field Effect Transistors for Circuit Simulation**

Luigi Colalongo<sup>1,\*</sup>, Simone Comensoli<sup>2</sup> and Anna Richelli<sup>1</sup>

- <sup>1</sup> Dipartimento di Ingegneria dell'Informazione (DII), University of Brescia, 25123 Brescia, Italy; anna.richelli@unibs.it

- <sup>2</sup> PDF Solutions, Desenzano Del Garda, 25015 Brescia, Italy

- \* Correspondence: luigi.colalongo@unibs.it

Abstract: We introduce a compact core model for double-gate (DGFET) and surrounding-gate (SGFET) MOSFETs designed for circuit simulations. Despite its high precision, the model is crafted to retain the same analytic formulation of the industry standard Pennsylvania State and Philips (PSP). Instead of linearizing the drain current as in the PSP model, we employ a quadratic symmetric polynomial interpolation of the charge in the channel. This eliminates the need for cumbersome derivatives, simplifications, and intricate coding when integrating into a circuit simulator, thereby preventing singularities during numerical iterations. Moreover, thanks to its mathematical formulation equivalent to PSP, this model simplifies the coding of terminal charges, capacitances, potentials, and electric fields in the channel within circuit simulators. We validate the accuracy of the model through comparisons with numerical solutions and experiments from the literature.

Keywords: double-gate; surrounding-gate; MOSFET; SPICE; surface potential; PSP

## check for updates

Citation: Colalongo, L.; Comensoli, S.; Richelli, A. PSP-Equivalent Model for Double-Gate and Surrounding-Gate Field Effect Transistors for Circuit Simulation. *Electronics* 2024, *13*, 1725. https:// doi.org/10.3390/electronics13091725

Academic Editor: Fabian Khateb

Received: 10 March 2024 Revised: 27 April 2024 Accepted: 28 April 2024 Published: 30 April 2024

**Copyright:** © 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https:// creativecommons.org/licenses/by/ 4.0/).

## 1. Introduction

Multiple gate MOSFETs (MGFETs), including FINFETs and nano sheets, have gained widespread adoption in the electronics industry as replacements for conventional planar transistors [1]. This is due to their enhanced gate control, nearly ideal subthreshold slope, and mitigated short-channel effects (SCE). In theory, MGFETs hold the potential to scale down the MOSFETs as technology advances to the end of the roadmap. Consequently, there is a significant interest in the development of compact CAD models of MGFETs for circuit simulation [2–12]. A compact CAD model for circuit simulations comprises a core model of an ideal long-channel transistor, wherein SCE and quantum effects (QE) are subsequently introduced as appropriate approximations. In the literature, various excellent closed-form equations for the drain current of symmetric DGFETs and SGFETs have been developed [2–12]. Nevertheless, the exact closed-form expressions of the terminal charges prove to be somewhat more cumbersome compared to compact models for planar transistors, requiring simplifications. Furthermore, the complexity of existing core models does not easily allow for the inclusion of short-channel and quantum effects. The objective of this work is to introduce a new compact model of MGFETs without resorting to the charge-sheet approximation. A quadratic symmetric polynomial interpolation is employed to compute the transistor current. In [11], we demonstrated that this approach is particularly suited to accurately model DGFETs and SGFETs. Here, the model from [11] is reformulated to be entirely equivalent to the widely recognized PSP current equation. Then, the terminal charges, capacitances, surface potential and electric field in the channel are worked out to hold the same expression of the PSP but with higher precision. The midpoint charge of PSP is replaced with an equivalent midpoint charge. The equivalent midpoint charge accommodates nonlinearities in the channel, maintaining high accuracy even when the surface potential exhibits strong nonlinearity. The model retains all the appealing characteristics of the traditional compact models of planar MOSFETs. These include computational

efficiency, symmetry, and straightforward polynomial expressions of current, terminal charges, potentials, and electric fields in the channel. Furthermore, despite its compactness and ease of integration into circuit simulators, it attains a remarkable level of accuracy. The largest error of the drain current, compared to the numerical solution, is so minimal that the model can be assumed to be equivalent to the exact solution. Finally, this core model, thanks to its high accuracy, numeric stability, versatility, and ease of implementation in circuit simulations, can be exploited as a core model in a variety of recent technologies, for example, junctionless, dual-material, dual-metal cylindrical gate-all-around MOSFETs, heterojunction tunneling transistors, nanotubes, etc. [13–17].

### 2. DGFET Drain Current

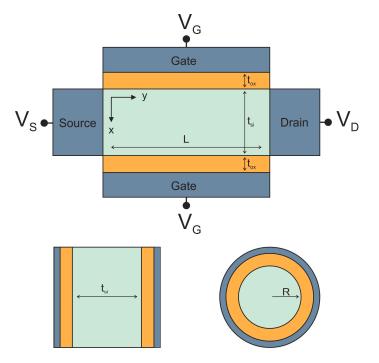

In the DGFET, the channel is typically undoped (or lightly doped) to mitigate threshold voltage fluctuations. Here, the device geometry and all the symbols are exactly the same as in the well-known paper of Taur [2] (Figure 1) and, for the sake of brevity, are summarized in Table 1. Assuming the current flows in the y-direction, in order to compute the surface potential, Poisson's equation must be solved. Poisson's equation is solved following the same approach as Taur [2]. The solution, without introducing any approximations, reads

$$\frac{q(V_{GS} - \Delta \psi - V)}{2kT} - \ln\left[\frac{2}{t_{si}}\sqrt{\frac{2\varepsilon_{si}kT}{q^2n_i}}\right] = \ln\beta - \ln[\cos\beta] + \frac{2\varepsilon_{si}t_{ox}}{\varepsilon_{ox}t_{si}}\beta\tan\beta \qquad (1)$$

where  $\beta$  is a parameter that is computed by solving transcendental Equation (1), q is the electron charge, k is the Boltzmann constant, T is the lattice temperature,  $\Delta \psi$  is the work function difference between the gate electrode and the intrinsic silicon, V is the channel potential,  $n_i$  is the intrinsic concentration,  $\varepsilon_{ox}$  is the insulator dielectric constant,  $\varepsilon_s$  is the silicon dielectric constant,  $t_{ox}$  is the insulator thickness,  $t_{si}$  is the semiconductor thickness, and  $V_{GS}$  is the voltage applied to the gate. Once  $\beta$  is computed, the electrostatic potential normal to the channel (*x*-direction) in the semiconductor reads [2,11]

$$\psi(x) = V - \frac{2kT}{q} \ln \left[ \frac{t_{si}}{2\beta} \sqrt{\frac{q^2 n_i}{2\varepsilon_{si}kT}} \cos\left(\frac{2\beta x}{t_{si}}\right) \right]$$

(2)

and the inversion charge in the channel [2] reads

$$Q_i = C_{ox}(V_{GS} - \Delta \psi - \psi_s) = 2\varepsilon_{si} \frac{2kT}{q} \frac{2\beta}{t_{si}} \tan\beta$$

(3)

where  $\psi_s = \psi(\pm t_{si}/2)$  and  $C_{ox} = \varepsilon_{ox}/t_{ox}$ . To develop a surface potential formulation for the drain current, it is important to note that the charge sheet approximation (CSM), commonly employed in planar MOSFET modeling, is not applicable to DGFETs. Specifically, for DGFETs, the exact solution of the Pao–Sah equation becomes necessary to precisely model the volume inversion in the subthreshold region [2,9–11]. Following the approach of [9], in [11], the Pao–Sah double integral is worked out using a second-order symmetric polynomial centered at the midpoint of the surface potential,  $\psi_M = (\psi_{sS} + \psi_{sD})/2$ , without the charge sheet simplification. This method yields a precise and considerably simplified representation of drain current and terminal charges compared to the current core models of DGFETs, all while maintaining a clear physical interpretation. The drain current reads [11]

$$I_D = 2\frac{W}{L}\mu \left[\frac{4\widetilde{Q}_{iM} + \widetilde{Q}_{iD} + \widetilde{Q}_{iS}}{6} + C_{ox} v_T\right]\phi$$

(4)

where

$$\overset{\sim}{Q}_{i} = Q_{i} \left[ 1 + \frac{\gamma}{4} g(\beta) \right]$$

(5)

$$g(\beta) = \frac{\sin\left(2\beta\right) - 2\beta\cos(2\beta)}{\beta\tan\left(\beta\right)\left[2\beta + \sin(2\beta)\right]}, \ \gamma = \frac{\varepsilon_{ox}t_{si}}{\varepsilon_{si}t_{ox}}$$

(6)

and  $v_T = kT/q$ ;  $Q_{iS}$ ,  $Q_{iD}$ , and  $Q_{iM}$  are the "perturbed charges" of Equation (5), computed at the source, drain, and surface potential midpoint, and  $\phi = \psi_{sD} - \psi_{sS}$  [11]. It is important to highlight that  $\phi$ ,  $Q_{iS}$ ,  $Q_{iD}$ , and  $Q_{iM}$  are explicit functions of  $\beta_S$ ,  $\beta_D$ , and  $\beta_M$ . In turn,  $\beta$  is computed through numerical iteration using Equation (1) at the source drain and midpoint. Nonetheless, numerous highly accurate explicit approximations for  $\beta$  are reported in the literature [18], and the numeric iteration is not required. Equation (4) represents an accurate and considerably simplified version of the drain current compared to existing core models of DGFETs, while maintaining a clear physical interpretation [11]. The linear and concise mathematical expression of Equation (4), its high accuracy, and the availability of precise explicit approximations for  $\beta$  make this model particularly well suited for integration into circuit simulation programs. Furthermore, Equation (4), despite its similarity to the wellknown PSP model, removes the requirement to calculate derivatives at the midpoint [7-10]. The derivative is cumbersome and requires careful coding during integration into a circuit simulator to prevent issues like division by zero or imaginary solutions during numerical iterations. Now, taking into account that the DGFET has two gates and that both Equation (4) and the PSP model are linear functions of charges and potentials, Equation (4) can be reformulated to be fully equivalent to the PSP current equation  $[I_{DS}]_{PSP}$  as follows:

$$[I_{DS}]_{PSP} = 2\frac{W}{L}\mu (Q_M - v_T \alpha)\phi \equiv [I_{DS}]_{eq.(4)} = 2\frac{W}{L}\mu (Q_{Meq} - v_T \alpha_{eq})\phi$$

(7)

where

$$Q_{Meq} = \frac{\left(4\widetilde{Q}_{iM} + \widetilde{Q}_{iD} + \widetilde{Q}_{iS}\right)}{6}, \quad \alpha_{eq} = -C_{os}$$

and the midpoint charge  $Q_M$  of the PSP here is replaced by an equivalent midpoint charge  $Q_{Meq}$  as well as the charge derivative  $\alpha_{eq} = dQ_i/d\psi_s$ . It is noteworthy that Equation (7), as it stands, is the same as Equation (4) but presented in a different form and seemingly does not introduce anything new compared to [11]. However, its utility lies in efficiently computing the terminal charges, capacitances, surface potential, and electric field in the channel, as shown below. Equation (7) is a matter of efficiency when implemented in a circuit simulator.

Figure 1. Schematic cross sections of the DGFET (left) and SGFET (right).

|                                            | DGFET | SGFET |

|--------------------------------------------|-------|-------|

| L [µm]                                     | 1     | 1     |

| t <sub>Si</sub> [nm]                       | 5     | —     |

| R [nm]                                     | —     | 2.5   |

| $t_{OX}$ [nm]                              | 1.5   | 1.5   |

| $\mu \left[ \text{cm}^2/\text{Vs} \right]$ | 300   | 300   |

| $ \mu \ [cm^2/Vs] \\ \Delta \psi \ [V] $   | 0     | 0     |

| ε <sub>Si</sub>                            | 11.7  | 11.7  |

| ε <sub>OX</sub>                            | 3.9   | 3.9   |

Table 1. Physical and geometrical parameters.

Physical and geometrical device parameters for both the DGFET and SGFET [2,4].

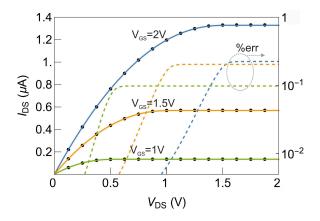

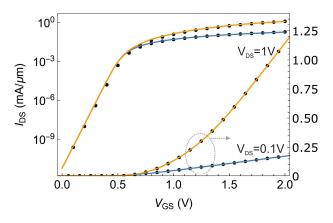

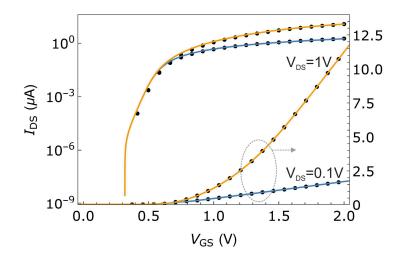

To assess the accuracy of Equation (7), in Figure 2, it is juxtaposed with the exact numerical solution of the Pao–Sah double integral [2]. In Figure 2, the percentage error, defined as  $100 \times |(\Delta I_{DS}) / I_{DS}|$ , is shown. All device parameters and terminal voltages are identical to those in [2,11]. Furthermore, in [2], the analytic solution is further verified through validation against numerical simulations and experimental data. Equation (7) provides a continuous and very accurate expression of the current with smoot derivatives [11,12]. Additionally, Equation (7) successfully passes the Gummel symmetry tests [11,12]. These characteristics are crucial for achieving rapid and seamless convergence in circuit simulations and for implementing short-channel effects (SCE). Equation (7) reproduces the numerical solution with a larger percentage error of approximately 0.1% (Figure 2). Notably, the error is about one order of magnitude smaller compared to the compact models in [9,10], as shown in Figures 2 and 3.

**Figure 2.** DGFET output currents and percentage error (% err =  $100 \times |(\Delta I_{DS}) / I_{DS}|$ ) at  $V_{GS}$  = 2 V (blue), 1.5 V (orange), and 1 V (green); lines indicate numerical solutions, and dots indicate Equation (7). The largest percentage error is about 0.2% (dashed lines). The simulation parameters are reported in Table 1. Both the numerical solution and Equation (7) accurately fit the experiments in [2].

**Figure 3.** DGFET transfer characteristics at  $V_{DS} = 0.1$  V; 1 V: lines indicate numerical solutions, and dots indicate Equation (7). Both the numerical solution and Equation (7) accurately fit the experiments in [2].

#### 3. SGFET Drain Current

An equivalent formulation can be developed for the cylindrical n-type SGFET of radius *R* in Figure 1. The geometry and symbols are the same as in [4]. Assuming that transport is in the y-direction (0 < r < R is the direction normal to the current), the integral of Poisson's equation reads [4]:

$$\frac{q(V_{GS} - \Delta \psi - V)}{kT} - \ln\left(\frac{8}{\delta R^2}\right) = \ln(1 - \beta) - \ln\beta^2 + \eta\left(\frac{1 - \beta}{\beta}\right)$$

(8)

where  $\eta = 4\varepsilon_{si}/(C_{ox}R)$ , and  $\delta = q^2 n_i/(kT\varepsilon_{si})$ . All other parameters carry the same meaning as in the DGFET. Once  $\beta$  is known after solving transcendental Equation (8), the potential in the semiconductor as a function of *r* can be readily calculated [4]:

$$\psi(r) = V + \frac{kT}{q} \ln \left( \frac{-8B}{\delta \left( 1 + Br^2 \right)^2} \right)$$

(9)

as well as the charge in the channel

$$Q_i = C_{ox}(V_{GS} - \Delta \psi - \psi_s) = 2\varepsilon_{si} \frac{2kT}{q} \frac{1}{\beta R} (1 - \beta)$$

(10)

where  $C_{ox} = \varepsilon_{ox} / [Rln(1 + t_{ox}/R))]$ ,  $\psi_s = \psi(R)$ , and  $\beta = 1 + BR^2$ . Pao–Sah's double integral for a cylindrical SGFET reads [11]

$$I_D = \frac{2\pi R}{L} \left[ \frac{4\widetilde{Q}_{iM} + \widetilde{Q}_{iD} + \widetilde{Q}_{iS}}{6} + C_{ox} v_T \right] \phi$$

(11)

where

$$Q_i = Q_i g(\beta) \tag{12}$$

$$g(\beta) = 1 + \frac{\frac{1}{\beta_{S}} - \frac{1}{\beta_{D}} + \ln\left(\frac{\beta_{S}}{\beta_{D}}\right)}{\gamma\left(\frac{1}{\beta_{S}^{2}} - \frac{1}{\beta_{D}^{2}} + \frac{2}{\beta_{D}} - \frac{2}{\beta_{S}}\right)}$$

(13)

and

$$\gamma = \frac{2\varepsilon_{si}}{\varepsilon_{ox}} \ln\left(1 + \frac{t_{ox}}{R}\right) \tag{14}$$

where  $Q_{iM}$ ,  $Q_{iS}$ ,  $Q_{iD}$ ,  $Q_{iS}$ , and  $Q_{iD}$  are calculated by means of Equations (10)–(14). Equation (11) depends on the terminal voltages through  $\psi_{sS}$  and  $\psi_{sD}$  and, in turn, on  $\beta$ , as is the case for the DGFET.

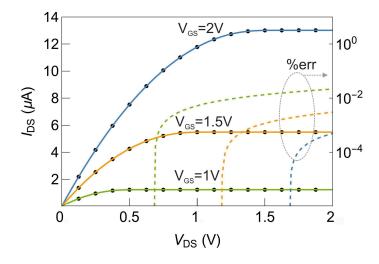

Yet again, Equation (11) reproduces the numerical solution of the drain current  $I_D$  with a percentage error smaller than 0.1%. In [18], an accurate explicit approximate solution of  $\beta$  is worked out for the SGFET as well. It makes this model very suitable for circuit simulators. In Figures 4 and 5, Equation (11) is compared to the numerical solution. Now, Equation (11) can also be reformulated to be entirely equivalent to the widely recognized PSP current equation:

$$I_D = \frac{2\pi R}{L} \mu \left( Q_{Meq} - v_T \alpha_{eq} \right) \phi.$$

(15)

In (15), the charge at the midpoint of PSP is substituted by an equivalent charge  $Q_{Meq} = \left(4\widetilde{Q}_{iM} + \widetilde{Q}_{iD} + \widetilde{Q}_{iS}\right)/6$  derived from (11), as well as  $\alpha_{eq} = -C_{ox}$ .

**Figure 4.** SGFET output currents and percentage error (% err =  $100 \times |(\Delta I_{DS}) / I_{DS}|$ ) at  $V_{GS}$  = 2 V (blue), 1.5 V (orange), 1 V (green); solid lines indicate exact numerical solutions, and dots indicate Equation (15). The largest percentage error is about 0.1% (dashed lines). The simulation parameters are reported in Table 1. Both the numerical solution and Equation (7) accurately fit the experiments in [4].

**Figure 5.** SGFET transfer characteristics at  $V_{DS} = 0.1$  V; 1 V: lines indicate numerical solutions, and dots indicate Equation (15). Both the numerical solution and Equation (7) accurately fit the experiments in [4].

#### 4. PSP-Equivalent Charge Model

Although the drain currents of the DGFET and SGFET in [2,4] are derived with no simplifications, they are complex functions of  $\beta$  that cannot be used to calculate terminal charges without introducing simplifications. In ref. [11], the terminal charges, derived from Equations (4) and (11), are computed without simplification, exploiting the polynomial equations of the charge in the channel. However, these calculations result in complex polynomial functions. In contrast, here, thanks to Equations (7) and (15), which are fully equivalent to Equations (4) and (11), the terminal charges are directly and easily computed, akin to the PSP approach. The terminal charges will be derived for the DGFET, and similar equations hold for the SGFET. The terminal charges are worked out by means of the well-known Ward–Dutton charge partitioning [19] as follows:

$$\frac{Q_G}{2W} = \int_0^L Q_i dy = \int_{-\phi/2}^{\phi/2} Q_i \frac{dy}{d\psi_s} d\psi_s$$

(16)

$$Q_S = Q_G - Q_D \tag{18}$$

where  $Q_G$ ,  $Q_S$ , and  $Q_D$  are the gate, source, and drain terminal charge densities per unit area. The above integrals are worked out as in PSP [7,8], exploiting the equivalence devised in Equation (7). To compute the terminal charges, first the expressions of  $y(\psi_s)$  and  $dy/d\psi_s$  must be derived. Since the current in the channel is solenoidal [7–11],

$$I_D = 2W\mu \left( \widetilde{Q}_i \frac{d\psi_s}{dy} - v_T \frac{dQ_i}{dy} \right)$$

(19)

and, recalling that in (7),  $dQ_i/d\psi_s = \alpha_{eq} = -C_{ox}$ , Equation (19) can be rewritten as

$$I_D = 2W\mu \left( Q_{Meq} + v_T \alpha_{eq} \right) \frac{d\psi_s}{dy}$$

<sup>(20)</sup>

and in turn,  $dy/d\psi_s$  reads

$$\frac{d\psi_s}{dy} = \frac{I_D}{2W\mu \left(Q_{Meq} + v_T \alpha_{eq}\right)}.$$

(21)

Finally, after substituting the drain current of (7) into Equation (21) and following the linear approach of PSP,  $dy/d\psi_s$  reads [7,8]

$$\frac{dy}{d\psi_s} = \frac{L}{\phi} \left( 1 - \frac{\psi_s - \psi_M}{H_{eq}} \right)$$

(22)

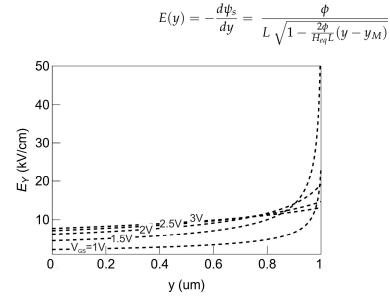

where  $H_{eq} = v_T - Q_{Meq}/\alpha_{eq} = v_T + Q_{Meq}/C_{ox}$ . It is worth noting that Equation (22) is related to the electric field parallel to the channel:

$$E_{Y}(\psi_{s}) = -\frac{d\psi_{s}}{dy} = \frac{\phi}{L} \frac{H_{eq}}{\psi_{s} - \psi_{M} - H_{eq}}.$$

(23)

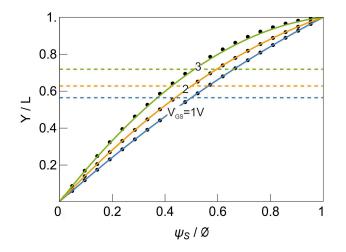

Then, after integrating Equation (22), the analytical expression of the position in channel y with respect to the surface potential reads [7,8]

$$y = y_M + \frac{L}{\phi} \left[ \psi_s - \psi_M - \frac{(\psi_s - \psi_M)^2}{2H_{eq}} \right]$$

(24)

where  $y_M$  represents the "surface potential midpoint", which is the *y*-coordinate corresponding to  $\psi_M$ :

$$y_M = \frac{L}{2} \left[ 1 - \frac{\phi}{4H_{eq}} \right]. \tag{25}$$

Note that when  $\phi > 0$ ,  $y_M > L/2$ , indicating that the potential midpoint shifts towards the drain from the geometric midpoint (Figure 6).

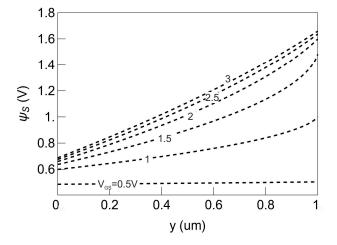

Conversely, the dependence  $\psi_s(y)$  can be derived by solving Equation (19) with respect to  $\psi_s$ , yielding

$$\psi_{s} = \psi_{M} + H_{eq} \left[ 1 - \sqrt{1 - \frac{2\phi}{H_{eq}L}(y - y_{M})} \right].$$

(26)

A close comparison between Equations (23)–(26) and the original model [11] reveals that the significantly simplified expression in Equation (26), which is based on the PSP-like approach, is nearly numerically identical to the exact expression presented in [11]. The maximum error of the surface potential is always smaller than 2%.

**Figure 6.** Position in the channel y(s) as a function of the surface potential at  $V_{GS} = 3$  V (blue),  $V_{GS} = 2$  V (orange),  $V_{GS} = 1$  V (green), and  $V_{DS} = 1$  V. Dashed line, surface potential midpoint  $y_M$ .

Furthermore, the expressions above are identical to those for bulk MOSFETs [7,8], with the only difference being the value of H, which is  $H_{eq}$  here. The position dependence of the surface potential is shown in Figure 7.

**Figure 7.** Surface potential (Equation (26)) vs. *y* in the channel of the DGFET at  $V_s = 0$  V,  $V_D = 1$  V, and  $V_{GS} = 0.5$ , 1, 1.5, 2, 2.5, and 3 V.

Then, substituting Equations (22) and (24) in Equation (16) and integrating, the gate charge  $Q_G$  reads

$$Q_G = 2\left(Q_{iM} - \frac{\alpha_{eq}\phi^2}{12H_{eq}}\right).$$

(27)

Also, in turn, replacing Equations (22) and (24) with Equation (17), the drain charge  $Q_D$  reads

$$Q_D = 2 \left[ \frac{Q_{iM}}{2} + \frac{\alpha_{eq} \phi}{12} \left( 1 - \frac{\phi}{2H_{eq}} - \frac{\phi^2}{20H_{eq}} \right) \right].$$

(28)

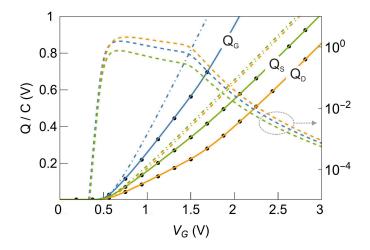

In Figure 8, the terminal charges derived with the PSP-equivalent approach are compared to both the numerical solution and the polynomial expressions of [11]. Again, the percentage error, with respect to the numerical solution, is below 2%. As a further check of Equations (27) and (28), the asymptotic behavior when  $V_{DS} \rightarrow 0$  is also shown in Figure 8 (dashed lines). When  $V_{DS} \rightarrow 0$ , the gate charge equals the inversion charge density and  $Q_D = Q_S = Q_G/2$ . In fact, if using the explicit expression of the charges when  $V_{DS} \rightarrow 0$ ,  $\phi \simeq 0$ ,  $\widetilde{Q}_{iS} \simeq \widetilde{Q}_{iD} \simeq \widetilde{Q}_{iM}$ , then

$$\lim_{\phi \to 0} H_{eq} = \lim_{\phi \to 0} \left( v_T - \frac{Q_{Meq}}{\alpha_{eq}} \right) = \lim_{\phi \to 0} \left( v_T - \frac{4\widetilde{Q}_{iM} + \widetilde{Q}_{iD} + \widetilde{Q}_{iS}}{6 \alpha_{eq}} \right) \cong v_T + \frac{\widetilde{Q}_{iM}}{C_{ox}}$$

(29)

and, eventually, the terminal charges read

$$\lim_{\phi \to 0} Q_G = \lim_{\phi \to 0} 2 \left[ Q_{iM} - \frac{C_{ox}}{12 \left( v_T + \frac{\widetilde{Q}_{iM}}{C_{ox}} \right)} \phi^2 \right] \approx 2Q_{iM}$$

(30)

$$\lim_{b \to 0} Q_D = \lim_{\phi \to 0} 2 \left[ \frac{Q_{iM}}{2} + \frac{\alpha_{eq} \phi}{12} \left( 1 - \frac{\phi}{2H_{eq}} - \frac{\phi^2}{20H_{eq}} \right) \right] \cong Q_{iM}$$

(31)

$$Q_S \cong Q_G - \frac{Q_G}{2} \cong \frac{Q_G}{2} \cong Q_{iM}.$$

(32)

**Figure 8.** Normalized terminal charges (27) and (28) vs. numerical solution (circles) and [11] at  $V_s = 0$  V and  $V_D = 1$  V: Q<sub>G</sub> (blue), Q<sub>S</sub> (green), and Q<sub>D</sub> (orange). The numerical solution and [11] perfectly overlap and are almost indistinguishable. Dot dashed lines indicate normalized charges at low drain voltage:  $V_D = 0.1$  V. Dashed line: percentage error (% err =  $100 \times |(\Delta Q) / Q|$ ).

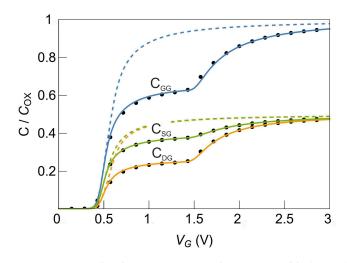

Furthermore, Figure 9 also shows that the transcapacitances ( $C_{ij} = (2\delta_{ij} - 1) \partial Q_i / \partial V_j$ , with i, j = G, S, D) essentially overlap with the exact numeric solution. Again, the larger percentage error is on the order of 2%. The expressions in Equations (7), (27), and (28) represent a new form of symmetric linearization, typical of PSP, for MGFETs. Unlike the simpler formulation with respect to [11], the result is, of course, the same for the drain current and, although simplified, very accurate for the terminal charges and transcapacitances as well (Figure 9). An important feature of this formulation of  $Q_G$ ,  $Q_S$ , and  $Q_D$  is that they are extremely simple, with PSP [7,8] differing only with the expression of *H*. This means that small-geometry effects can be worked out as they were in [7,8], and these effects were previously shown to be accurate with respect to numeric simulations and experimental data. Finally, the electric field in the channel, required to implement short-channel effects (SCE), quantum effects (QE), and other advanced physical phenomena, is derived as it was in [7,8]. E(y) is worked out by replacing Equation (27) with Equation (23). In Figure 10, the electric field for different gate voltages, both in the saturation and linear regions, is shown.

**Figure 9.** Normalized transcapacitances: lines are  $C_{GG}$  (blue),  $C_{SG}$  (green), and  $C_{DG}$  (orange) vs. numerical solution (circles) and [11] at  $V_s = 0$  V and  $V_D = 1$  V. The numerical solution and [11] perfectly overlap and are almost indistinguishable. Dashed lines indicate normalized capacitances at low drain voltage:  $V_D = 0.1$  V.

**Figure 10.** Electric field parallel to channel (33) vs. *y* at  $V_s = 0$  V,  $V_D = 1$  V, and  $V_G = 1$ , 1.5, 2, 2.5, and 3 V.

#### 5. Symmetry and Derivatives

A common issue of surface potential-based models in bulk MOSFETs, and consequently, MGFETs, involves resolving implicit transcendental Equations (1) and (8). Iterative methods represent the most commonly employed approach for addressing implicit equations due to their potential for high accuracy. Nevertheless, they are accompanied by several drawbacks, including computational inefficiency and occasional exceptions, such as divergence. Hence, an explicit approximation of Equations (1) and (8) that offers sufficient accuracy is always preferable to streamline applications for industry standards.

In ref. [18], an accurate explicit solution of Equations (1) and (8) is presented, utilizing high-order mathematical corrections. This solution exhibits accuracy not only concerning drain current but also with respect to its derivatives. The explicit expression of  $\beta$  is very efficient: it requires the computation of two exponents, two square roots, and three logarithms. Despite the compact form of  $\beta$  as described in [18], the algorithm yields a  $\beta$  with a maximum error of 17 fV, which proves sufficient for computing current and its derivatives with precision that is suitable for circuit simulation. A more stringent way to

(33)

understand the accuracy of the solution is to compare the derivatives of the drain current or the terminal charges.

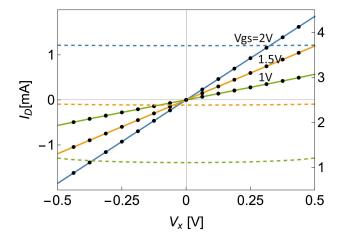

Partial derivatives, such as drain conductance, transconductance, and transcapacitance, play a crucial role in AC and transient circuit simulations. These derivatives are particularly sensitive to the errors of intermediate parameters. Moreover, when designing integrated circuits, such as passive RF mixers and transfer gates, it is essential for a compact model to show symmetry with respect to the interchange of the source and drain terminals. This property is frequently referred to as Gummel symmetry (GS). The Gummel symmetry of Equations (7) and (11) is depicted as solid lines in Figures 11 and 12 for the DGFET and SGFET, respectively, indicating that this model successfully passes this GS test. The GS is extremely important when the model is implemented in a circuit simulator. When implementing a compact model in a circuit simulator, the condition  $I_D = f(V_S, V_D, V_{GS}) = -f(-V_S, -V_D, V_{GS})$  is enforced, regardless of the internal symmetry of the model. If a compact MOSFET model inherently possesses symmetry, the imposition of this symmetry condition by the circuit simulator has no effect. However, for asymmetric models, enforcing this condition may lead to singularities that typically manifest as the nonexistence of the second derivative. The results shown in Figures 11 and 12 demonstrate that the model not only passes the GS test but also accurately reproduces the exact numerical solution (symbols).

**Figure 11.** Gummel symmetry test for the DGFET (Equation (7)):  $V_s = V_x$ ,  $V_D = -V_x$  at  $V_{GS} = 2$  V (blue), 1.5 V (orange), and 1 V (green).  $I_D$ , left axis (solid line);  $dI_D/dV_X$  (dashed line), right axis. Dots are the exact numerical solution.

**Figure 12.** Gummel symmetry test for the SGFET (Equation (15)):  $V_s = V_x$ ,  $V_D = -V_x$  at  $V_{GS} = 2$  V (blue), 1.5 V (orange), and 1 V (green).  $I_D$ , left axis (solid line);  $dI_D/dV_X$ , right axis (dashed line). Dots are the exact numerical solution.

## 6. Conclusions

This work presents a compact core model for MGFETs designed for advanced CAD applications. It provides a remarkably accurate and considerably simplified expression of the Pao–Sah equation while maintaining a clear physical interpretation. The largest percentage error with respect to the numerical solution was on the order of 0.1%. Moreover, the current equations of [11] were formulated to be fully equivalent to the Pennsylvania State and Philips model, PSP. Due to its formulation, this model simplifies the coding of terminal charges, capacitances, potentials, and electric fields in the channel within circuit simulators. This is highly advantageous, given that the complexity of the exact DGFET and SGFET core models makes it challenging to incorporate small-geometry effects and hinders the direct application of experience (and code) gained in the development of advanced bulk and SOI models. The model is fully scalable and is suitable for the full range of device geometries, from the long-channel limit down to the shortest channels, with a single set of parameters. We validated the accuracy of this core model through comparisons with exact numerical solutions and experimental data from the literature [2,4]. It is a useful kernel for the future generation of SPICE models of FINFET and nano sheets, maintaining the same ease of implementation of today's most advanced planar MOSFET models.

**Author Contributions:** Conceptualization, L.C. and S.C.; Writing—review & editing, L.C., S.C. and A.R. All authors have read and agreed to the published version of the manuscript.

Funding: This research received no external funding.

Data Availability Statement: Data is contained within the article.

**Conflicts of Interest:** Author Simone Comensoli was employed by the company PDF Solutions. The remaining authors declare that the research was conducted in the absence of any commercial or financial relationships that could be construed as a potential conflict of interest.

#### References

- 1. Colinge, J.-P. Multiple gate SOI MOSFETs. Solid State Electron. 2004, 48, 897–905. [CrossRef]

- Taur, Y.; Liang, X.; Wang, W.; Lu, H. A continuous, analytic drain current model for DG-MOSFETs. *IEEE Electron Device Lett.* 2004, 25, 107–109. [CrossRef]

- Lu, H.; Yu, B.; Taur, Y. A unified charge model for symmetric double-gate and surrounding-gate MOSFETs. *Solid State Electron*. 2008, 52, 67–72. [CrossRef]

- Jimenez, D.; Iniguez, B.; Sune, J.; Marsal, F.L.; Pallares, J.; Roig, J. Continuous analytic current–voltage model for surrounding-gate MOSFETs. IEEE Electron Device Lett. 2004, 25, 571–573. [CrossRef]

- Iniguez, B.; Jimenez, D.; Roig, J.; Hamid, H.A.; Marsal, L.F.; Pallares, J. Explicit continuous model for long-channel undoped surrounding gate MOSFETs. IEEE Trans. *Electron Devices* 2005, 52, 1868–1873. [CrossRef]

- 6. Yu, B.; Lu, W.-Y.; Lu, H.; Taur, Y. Analytic charge model for surrounding-gate MOSFETs. *IEEE Trans. Electron Devices* 2007, 54, 492–496. [CrossRef]

- Gildenblat, G.; Wang, H.; Chen, T.; Gu, X.; Cai, X. SP: An Advanced Surface-Potential-Based Compact MOSFET Model. *IEEE JSSC* 2004, 39, 1394–1406. [CrossRef]

- Gildenblat, G.; Li, X.; Wu, W.; Wang, H.; Jha, A.; van Langevelde, R.; Smit, G.D.J.; Scholten, A.J.; Klaassen, D.B.M. PSP: An Advanced Surface-Potential-Based MOSFET Model for Circuit Simulation. *IEEE Trans. Electron Devices* 2006, 53, 1979–1993. [CrossRef]

- Dessai, G.; Dey, A.; Gildenblat, G.; Smit, G.D.J. Symmetric linearization method for double-gate and surrounding-gate MOSFET models. *Solid State Electron.* 2009, 53, 548–556. [CrossRef]

- Smit, G.D.J.; Scholten, A.J.; Curatola, G.; van Langevelde, R.; Gildenblat, G.; Klaassen, D.B.M. PSP-based scalable compact FinFET model. NSTI-Nanotech 2007, 3, 520–525.

- 11. Colalongo, L.; Comensoli, S.; Richelli, A. A unified core model of double-gate and surrounding-gate MOSFETs for circuit simulation. *Solid State Electron.* **2024**, *213*, 108849. [CrossRef]

- 12. Colalongo, L.; Richelli, A. A Second-Order Surface Potential Core Model for Submicron MOSFETs. *IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst.* 2022, 41, 2652–2656. [CrossRef]

- 13. Guan, Y.; Dou, Z.; Lu, J.; Huang, S.; Chen, H. An Accurate and Full-Range Analytical Current Model for Nanowire Heterojunction TFET. *IEEE Trans. Electron Devices* **2023**, *70*, 6004–6011. [CrossRef]

- 14. Mo, F.; Elfi Spano, C.; Ardesi, Y.; Ruo Roch, M.; Piccinini, G.; Vacca, M. NS-GAAFET Compact Modeling: Technological Challenges in Sub-3-nm Circuit Performance. *Electronics* **2023**, *12*, 1487. [CrossRef]

- 15. Chen, Z.; Zhang, Y.; Jiang, J.; Chen, C. An Improved Dual-Gate Compact Model for Carbon Nanotube Field Effect Transistors with a Back-Gate Effect and Circuit Implementation. *Electronics* **2024**, *13*, 620. [CrossRef]

- Kushwaha, P.; Agarwal, H.; Mishra, V.; Dasgupta, A.; Lin, Y.; Kao, M.; Chauhan, Y.S.; Salahuddin, S.; Hu, C. Modeling the Quantum Gate capacitance of Nano-Sheet Gate-All-Around MOSFET. In Proceedings of the IEEE SOI-3D-Subthreshold Microelectronics Technology Unified Conference (S3S), San Jose, CA, USA, 14–17 October 2019. [CrossRef]

- 17. Ganapati, R.; RaoSamoju, V.; RaoJammu, B. Analytical Modeling of Threshold Voltage for Dual-Metal Double-Gate Gate-All-Around (DM-DG-GAA) MOSFET. *Silicon* 2021, *13*, 2869–2880. [CrossRef]

- Yu, B.; Lu, H.; Liu, M.; Taur, Y. Explicit Continuous Models for Double-Gate and Surrounding-Gate MOSFETs. *IEEE Trans. Electron Devices* 2007, 54, 2715–2722. [CrossRef]

- Ward, D.; Dutton, R. A charge-oriented model for MOS transistor capacitances. *IEEE J. Solid State Circuits* 1978, 13, 703–708. [CrossRef]

**Disclaimer/Publisher's Note:** The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content.