# **Progress in Gallium Oxide Field-Effect Transistors for High-Power and RF Applications**

Ory Maimon <sup>1,2</sup> and Qiliang Li <sup>1,2,3,\*</sup>

- <sup>1</sup> Department of Electrical Engineering, George Mason University, Fairfax, VA 22030, USA; omaimon@gmu.edu

- <sup>2</sup> Nanoscale Device and Characterization Division, National Institute of Standards and Technology, Gaithersburg, MD 20899, USA

- <sup>3</sup> Quantum Science & Engineering Center, George Mason University, Fairfax, VA 22030, USA

- \* Correspondence: qli6@gmu.edu

Abstract: Power electronics are becoming increasingly more important, as electrical energy constitutes 40% of the total primary energy usage in the USA and is expected to grow rapidly with the emergence of electric vehicles, renewable energy generation, and energy storage. New materials that are better suited for high-power applications are needed as the Si material limit is reached. Beta-phase gallium oxide ( $\beta$ -Ga<sub>2</sub>O<sub>3</sub>) is a promising ultra-wide-bandgap (UWBG) semiconductor for high-power and RF electronics due to its bandgap of 4.9 eV, large theoretical breakdown electric field of 8 MV cm $^{-1}$ , and Baliga figure of merit of 3300, 3–10 times larger than that of SiC and GaN. Moreover,  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> is the only WBG material that can be grown from melt, making large, high-quality, dopable substrates at low costs feasible. Significant efforts in the high-quality epitaxial growth of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> and  $\beta$ -(Al<sub>x</sub>Ga<sub>1-x</sub>)<sub>2</sub>O<sub>3</sub> heterostructures has led to high-performance devices for high-power and RF applications. In this report, we provide a comprehensive summary of the progress in  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> field-effect transistors (FETs) including a variety of transistor designs, channel materials, ohmic contact formations and improvements, gate dielectrics, and fabrication processes. Additionally, novel structures proposed through simulations and not yet realized in  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> are presented. Main issues such as defect characterization methods and relevant material preparation, thermal studies and management, and the lack of p-type doping with investigated alternatives are also discussed. Finally, major strategies and outlooks for commercial use will be outlined.

**Keywords:** gallium oxide; wide-bandgap semiconductor; field-effect transistors (FETs); high power; RF; defects

# 1. Introduction

The power semiconductor market observed a 30% growth in 2022, and continual growth is expected as more electrical energy passes through power electronics, approximately 30% in 2019 and up to 80% in the next decade [1,2]. High-power semiconductor applications are classified into high-power (low-frequency) or high-frequency, RF. As silicon power devices reach their limit at breakdown voltages up to 6.5 kV and have a high temperature capability up to 200 °C [3], wide-bandgap (WBG) materials offer improved efficiency, large power ratings, high switching speeds, and RF performance. While SiC and GaN have been the dominant WBG semiconductors with commercially available devices, ultra-wide-bandgap (UWBG) beta-phase gallium oxide ( $\beta$ -Ga<sub>2</sub>O<sub>3</sub>) is emerging as a material for next-generation high-power and RF electronics.

With its bandgap of 4.7–4.9 eV, large theoretical breakdown field of 8 MV cm<sup>-1</sup>, and high electron saturation velocity of  $2 \times 10^7$  cm s<sup>-1</sup>,  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> has a Baliga figure of merit (BFOM), indicating DC conduction losses, as well as a Johnson figure of merit (JFOM) for RF performance, higher than those of GaN and SiC [4–7]. Additionally, the ability to grow bulk substrates from the melt gives  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> a significant cost advantage over SiC and GaN [8]. However, difficult challenges face  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> in the form of a lack of shallow

Citation: Maimon, O.; Li, Q. Progress in Gallium Oxide Field-Effect Transistors for High-Power and RF Applications. *Materials* **2023**, *16*, 7693. https://doi.org/10.3390/ ma16247693

Academic Editor: Alexander A. Lebedev

Received: 30 October 2023 Revised: 21 November 2023 Accepted: 23 November 2023 Published: 18 December 2023

**Copyright:** © 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https:// creativecommons.org/licenses/by/ 4.0/). p-type dopants and low thermal conductivity, which is especially difficult for high-power applications where heat dissipation is essential. Heterostructures with p-type oxides have been fabricated with high performance; however, most of the research on  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> has focused on unipolar devices.

Great strides have been made in both high-power and RF  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> field-effect transistors (FETs) with continually improving material quality and fabrication processes. Highpower lateral FETs have reported breakdown voltages up to 10 kV and BFOMs near 1 GW cm<sup>-2</sup>, while vertical devices have yet to achieve similar performance. The factors limiting vertical FETs are largely the lack of p-type dopants, which minimizes currentblocking capabilities, gate dielectric quality, stability, and robustness [9]. Many of the FET structural and material improvements, discussed in Section 3, that have been tested on lateral FETs can similarly be applied to vertical devices. Most  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FETs are depletionmode (D-mode), or normally on, due to the unipolar nature of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> devices. The off-state leakage in D-mode FETs is more prominent than in enhancement-mode (E-mode), or normally off, FETs; however, their fabrication is more difficult and often requires band bending a heterointerface to deplete the existing channel. RF FETs are predominantly lateral devices with thin channel layers and highly scaled gate lengths for strong gate control and reduced parasitics. Techniques such as delta-doping and modulation doping are used to form a two-dimensional electron gas (2DEG) with a high carrier concentration and mobility. Maximum oscillating frequencies near 50 GHz with high breakdown electric fields have been reported, showing potential for high-power RF  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FETs in the future. With the tremendous progress that has already been accomplished in the field, β-Ga<sub>2</sub>O<sub>3</sub> presents itself as a strong candidate for high-power and high-frequency applications, but not without its challenges to overcome.

Previous review articles on  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FETs have reported the chronological development in device design and performance [10], or focused specifically on RF FETs [7], E-mode FETs [11], or vertical GaN and  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FETs [9]. Other review papers have covered FETs designed for both high-power and RF applications [12,13]. This review is formatted to aid current and future  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> high-power and RF FET researchers by separately discussing the different steps of FET fabrication, ranging from structures, materials, ohmic contacts, gate dielectrics, and material preparation. An overview of various material and FET defect characterization techniques is presented as well.

This article presents a comprehensive overview of the progress in  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FETs, current challenges, and potential strategies to overcome them. Section 2 discusses the crystal structure and material properties, including FOM comparisons, bulk and epitaxial growth, and the doping of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>. Section 3 reviews many of the recent transistor designs for both high-power and RF applications. Section 3.1 focuses on structures that have been implemented, as well as proposed structures through technology computer-aided design (TCAD). Section 3.2 summarizes FETs with different channel and substrate materials such as semi-insulating homoepitaxial or heterostructure layers in the channel, and high thermally conductive substrates. Section 3.3 reviews metals and processes for high-quality ohmic contact formation and Section 3.4 gives an overview of different gate dielectrics used in  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FETs. Section 4 discusses the importance of defect engineering, various characterization methods, and material preparation to improve interface quality. Section 5 gives a high-level overview of the current challenges and steps needed to add  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> devices to the market. Section 6 briefly summarizes the most promising applications and trends of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FETs. Section 7 then summarizes the advancements in  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> and provides an outlook of the future of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>.

# 2. Crystal Growth and Material Properties of β-Ga<sub>2</sub>O<sub>3</sub>

#### 2.1. Different Phases

In 1952, Roy et al. discovered five polymorphs of  $Ga_2O_3$  ( $\alpha$ ,  $\beta$ ,  $\gamma$ ,  $\delta$ , and  $\varepsilon$ ) using a gallia gel–water system, and determined that the  $\beta$  phase is the stable form [14]. Using first-principles calculations, Yoshioka et al. found that the theoretical formation energies of

the different phases are in the order of  $\beta < \varepsilon < \alpha < \delta < \gamma$ , confirming that  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> is stable, while the other polymorphs show metastable behavior and transform into  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> at high temperatures [15]. In 2013, Playford et al. discovered another metastable phase ( $\kappa$ ) via the thermal decomposition of Ga<sub>5</sub>O<sub>7</sub>(OH) above 500 °C [16]. The phase transitions compiled from Roy et al. and Playford et al. are shown in ref. [17].

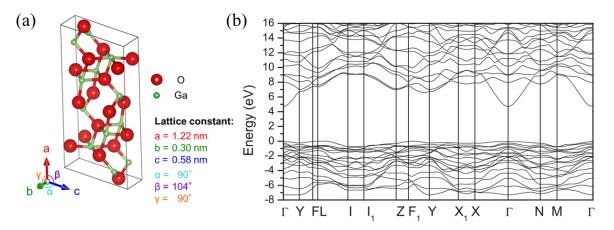

The crystal structure of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> is monoclinic and belongs to the C2/m space group with lattice constants of a = 12.2 Å, b = 3.0 Å, c = 5.8 Å,  $\alpha$  = 90°,  $\beta$  = 104°, and  $\gamma$  = 90° (Figure 1a). The unique structure has two Ga sites, one with a tetrahedral geometry and one with an octahedral geometry, as well as three O sites, leading to high anisotropy in many of its material properties [18–21].

**Figure 1.** (a)  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> unit cell. Reproduced from [22]. © IOP Publishing. Reproduced with permission. All rights reserved. (b)  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> band diagram. Reprinted with permission from [19]. Copyright 2017 by the American Physical Society.

#### 2.2. Material Properties

The band structure of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>, calculated using first-principles density functional theory (DFT) (Figure 1b), shows an indirect gap of 4.84 eV and a direct gap of 4.88 eV; however,  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> is largely considered a direct-gap semiconductor because of the close proximity of the gaps. The conduction band dispersion estimates an electron effective mass of  $\approx 0.28$  m<sub>e</sub>, where m<sub>e</sub> is the rest electron mass. The valence band, however, exhibits almost no dispersion and, therefore, exhibits a very large hole effective mass due to the localized self-trapping of holes [19,23].

Experimentally observed bandgaps range between 4.7 and 4.9 eV [19,24], projecting a critical breakdown electric field,  $E_{br}$ , of 6–8 MV cm<sup>-1</sup>. Various figures of merit (FOM), discussed below, have been developed to compare semiconductors for high-power applications. The Baliga FOM (BFOM) is an estimate of DC conduction losses in a material and is defined as both  $\varepsilon \cdot \mu \cdot E_{br}^{3}$ , where  $\varepsilon$  is the material dielectric constant and  $\mu$  is the carrier mobility, and as  $V_{br}^{2} R_{on,sp}^{-1}$  for devices, where  $V_{br}$  is the breakdown voltage and  $R_{on,sp}$  is the specific on-resistance. The theoretical BFOM of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> is approximately 28 GW cm<sup>-2</sup> and  $\approx$ 3214 times larger than that of Si. Other power device metrics include the Johnson FOM (JFOM), which represents the power–frequency capability; the Baliga high-frequency FOM (BHFFOM), which is a measure of switching losses; the Keyes FOM for thermal capability for power density and speed; and the Huang chip area manufacturing FOM (HCAFOM) as an indicator of chip area requirements. The material properties and FOMs of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> compared to other materials are summarized in Table 1 [6,12,25].

It is important to note the low and anisotropic thermal conductivity in  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> of 27.0 W m<sup>-1</sup> K<sup>-1</sup> in the [010] direction and 10.9 W m<sup>-1</sup> K<sup>-1</sup> in [100] [26]. The difference in thermal conductivity of [010]  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> and [100]  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> might not seem large compared to those of other (ultra)-wide-bandgap ((U)WBG) materials; however, simulations have shown that the max temperature rise in devices has a decreasing rate dependence on thermal

conductivity, and that  $\approx 105$  °C and  $\approx 61$  °C max temperature rises are simulated for [100] and [010]  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>, respectively. On the other hand, the simulated max temperature rises for SiC and diamond are  $\approx 34$  °C and  $\approx 30$  °C, respectively [27].

At low doping densities below  $10^{18}$ – $10^{19}$ , electron interactions with polar longitudinal optical (LO) phonons is identified as the dominant scattering mechanism, limiting the theoretical bulk mobility to  $\leq 250 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ , while at higher doping concentrations, impurity scattering is dominant [28–30]. Even though  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> has a low mobility,  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> maintains higher FOMs than GaN and SiC because of the square or cubic dependence on breakdown voltage and only a linear dependence on mobility.

**Table 1.** Material properties and FOMs, relative to Si, of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> compared to other semiconductors [6,12,31].

| Material Properties                                                         | Si   | GaAs | 4H-SiC | GaN   | $\beta$ -Ga <sub>2</sub> O <sub>3</sub> | Diamond |

|-----------------------------------------------------------------------------|------|------|--------|-------|-----------------------------------------|---------|

| Bandgap, Eg (eV)                                                            | 1.1  | 1.4  | 3.3    | 3.4   | 4.9                                     | 5.5     |

| Dielectric Constant, $\varepsilon$                                          | 11.8 | 12.9 | 9.7    | 9     | 10                                      | 5.5     |

| Breakdown field, $E_{br}$ (MV cm <sup>-1</sup> )                            | 0.3  | 0.4  | 2.5    | 3.3   | 8                                       | 10      |

| Electron mobility, $\mu$ (cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> ) | 1480 | 8400 | 1000   | 1250  | 200-250                                 | 2000    |

| Saturation velocity, $v_{sat}$ (10 <sup>7</sup> cm s <sup>-1</sup> )        | 1    | 1.2  | 2      | 2.5   | 1.8–2                                   | 1       |

| Thermal conductivity, $\lambda$ (W m <sup>-1</sup> K <sup>-1</sup> )        | 150  | 55   | 270    | 210   | 10.9-27                                 | 1000    |

| $BFOM = \varepsilon_r \mu E_{hr}^3$                                         | 1    | 14.7 | 317    | 846   | 3214                                    | 24,660  |

| $JFOM = E_{hr}^2 v_s^2 / 4\pi^2$                                            | 1    | 1.8  | 278    | 1089  | 2844                                    | 1100    |

| BHFFOM = $\mu E_{br}^2$                                                     | 1    | 10.1 | 46.3   | 100.8 | 142.2                                   | 1501    |

| Keyes FOM = $\lambda [(c \cdot v_s)/(4\pi\epsilon)]^{1/2}$                  | 1    | 0.3  | 3.6    | 1.8   | 0.2                                     | 41.5    |

| HCAFOM = $\varepsilon \mu^{0.5} E_{br}^2$                                   | 1    | 5    | 48     | 85    | 279                                     | 619     |

#### 2.3. Crystal Growth

One of the greatest advantages of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> is the potential for ultra-low-cost, large-size (diameter 100–150 mm), high-quality substrates made possible via melt growth.  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> is the only WBG semiconductor that can be grown from the melt, and therefore, the cost of a  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> wafer is expected to be approximately 80% cheaper than that of SiC [8]. The different bulk crystal growth techniques are edge-defined film-fed growth (EFG) [32,33], Czochralski (CZ) [34], vertical Bridgman (VB) [35,36], floating zone (FZ) [37,38], and Verneuil [39,40]. From all the methods, EFG has so far grown larger-diameter substrates with high quality, low defect densities, and a relatively wide doping range [22,41].

#### 2.4. Epitaxial Growth

The main methods of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> thin film growth that have been developed include molecular beam epitaxy (MBE), plasma-assisted MBE (PAMBE), metal-organic chemical vapor deposition (MOCVD), halide vapor-phase epitaxy (HVPE), and low-pressure chemical vapor deposition (LPCVD). MBE has the advantage of growing very high-quality thin films with less impurities and precise control over the growth rate and doping  $(10^{16}-10^{20} \text{ cm}^{-3})$ . It suffers, however, from low growth rates of  $0.05-0.18 \ \mu m \ h^{-1}$  that make it impractical for thick epitaxial layers used in vertical devices, but ideal for lateral thin-channel devices. PAMBE uses an activated oxygen source to help the growth of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> thin films, and has been shown to reduce background (unintentional) impurity concentrations [42-44]. MOCVD, also called metal-organic vapor-phase epitaxy (MOVPE), also produces highpurity thin films with controlled doping  $(10^{17}-8 \times 10^{19} \text{ cm}^{-3})$  at higher growth rates of 0.8  $\mu$ m h<sup>-1</sup> and less costly than MBE, making MOCVD conducive for large-scale production. HVPE has a minimum doping concentration at the order of  $10^{15}$  cm<sup>-3</sup> and a significantly higher growth rate, with the maximum reported rate of 250  $\mu$ m h<sup>-1</sup>. It is therefore used in thick epi layer growth for vertical devices [45]. The tradeoff for the higher growth rates in HVPE is lower-quality thin films with rougher surfaces and more defects. LPCVD is a scalable and lower-cost method that produces high-quality thin films with growth rates ranging from 0.5 to 10  $\mu$ m h<sup>-1</sup>, controlled doping in the range of

$10^{17}$ – $10^{19}$  cm<sup>-3</sup>, and a heterostructure capability [46,47]. LPCVD is the least used of the three growth techniques, but can provide a path for scalable, production-level  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> wafers. Additionally, MBE, MOCVD, and LPCVD can grow heterostructures, unlike HVPE. More detail on these growth methods can be found in refs. [17,48,49].

#### 2.5. Doping Strategies

DFT calculations have been used to find the energy levels of various impurities, oxygen vacancies (V<sub>O</sub>), and gallium vacancies (V<sub>Ga</sub>) in the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> bandgap. Oxygen vacancies act as deep donors more than 1 eV below the conduction band (E<sub>C</sub>), and gallium vacancies act as deep acceptors more than 1 eV above the valence band (E<sub>V</sub>) [50,51]. These vacancies do not contribute to conduction, but only act as doping compensation. Shallow donors found via DFT include Si<sub>Ga(I)</sub> (Si impurity in Ga<sub>I</sub> site), Ge<sub>Ga(I)</sub>, Sn<sub>Ga(II)</sub>, Cl<sub>O(I)</sub>, and F<sub>O(I)</sub>, with energy levels very near E<sub>C</sub> [52]; however, the majority of experimentally used donors are Si, Sn, and Ge [53,54]. Acceptor impurities such as N, Sr, Zn, Cd, Ca, Be, Mg, and Fe all have levels more than 1.3 eV above E<sub>V</sub>, indicating that p-type doping is not possible, and is a major challenge in the development of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> devices [50,55]. Deep acceptors are used to form highly resistive semi-insulating layers.

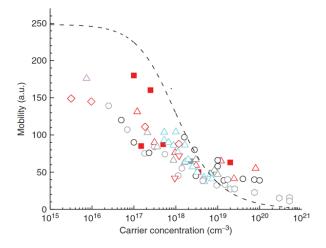

The donor levels of Si and Ge in MBE, LPCVD, CZ, and EFG samples, calculated using temperature-dependent Hall and conductivity measurements, ranged from 15 to 31 meV below  $E_C$ , indicating shallow donors, while the Mg and Fe levels were located at  $E_C$ —0.86 eV and  $E_C$ —1.1 eV, respectively [53]. Mobility dependence on carrier concentration is expected to flatten at 250 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> as the carrier concentration approaches  $10^{15}$  cm<sup>-3</sup>, and drops significantly as it increases above  $10^{17}$  cm<sup>-3</sup> (Figure 2) [31].

**Figure 2.** Electron mobility vs. carrier concentration in  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> for Si, Sn, and Ge dopants in layers grown using various crystal and thin film techniques. Adapted with permission from Chen et al. [31] © 2023 John Wiley & Sons, Ltd.

While p-type behavior is not available when using conventional methods, some groups have observed hole conduction when compensating donors are reduced [56]. The p-type conductivity of thin-film  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> by reducing the mean free path of carriers using amphoteric Zn doping was able to achieve ultra-high breakdown fields of 13.2 MV cm<sup>-1</sup>, beyond that of the theoretical  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> [57]. Another technique to modulate between high n-type and p-type conductivity was developed via controlled H incorporation, where p-type conductivity with an acceptor state 42 meV above E<sub>V</sub> was observed after direct H diffusion, and n-type conductivity with a donor state 20 meV below E<sub>C</sub> was observed after filling up oxygen vacancies by annealing in O<sub>2</sub> [58].

# 3. β-Ga<sub>2</sub>O<sub>3</sub> FET Designs

The following section reviews many of the current FET designs, including their structure, channel materials, substrate materials, ohmic contact formation, and gate dielectrics. Their process steps, use cases, advantages, and disadvantages are discussed. The tables below compare the many different device designs for D-mode high-power (Table 2), E-mode high-power (Table 3), and D-/E-mode RF applications (Table 4). Table 4 also includes the RF performance of mature GaN HEMTs and emerging hydrogen-terminated diamond HEMTs to illustrate the differences in performance of other material systems to  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>.

| Ref. | FET Design                                                                  | On/Off          | I <sub>D,max</sub><br>(mA mm <sup>-1</sup> ) | V <sub>br</sub> (V) | E <sub>br</sub><br>(MV cm <sup>-1</sup> ) | R <sub>on,sp</sub><br>(Ω cm <sup>2</sup> ) | $\mu^{\mu}$ (cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> ) | BFOM<br>(MW cm <sup>-2</sup> ) |  |

|------|-----------------------------------------------------------------------------|-----------------|----------------------------------------------|---------------------|-------------------------------------------|--------------------------------------------|----------------------------------------------------------------|--------------------------------|--|

| [59] | MESFET, T-gate + SFP, OA                                                    | $10^{6}$        | 3.3                                          | 10 k                | 1                                         | 2.92                                       | NR                                                             | >34.2                          |  |

| [60] | Delta-doped MESFET<br>w/GFP                                                 | $10^{7}$        | 180                                          | 315                 | 2.3                                       | NR                                         | 73                                                             | 118                            |  |

| [61] | Delta-doped SAG                                                             | $10^{3}$        | 560                                          | NR                  | NR                                        | NR                                         | 65                                                             | NR                             |  |

| [62] | Recessed and T-gate                                                         | 109             | 49                                           | 1.80 k              | 1.8                                       | 20.9 m                                     | 128                                                            | 155                            |  |

| [63] | Tri-gate lateral FinFET                                                     | $10^{10}$       | 187                                          | 1.13 k              | 4.2                                       | 1.34 m                                     | 184                                                            | 950                            |  |

| [64] | Composite + SU8 GFP                                                         | $10^{9}$        | 40                                           | 7.16 k              | 1.79                                      | 8.98                                       | NR                                                             | 5.71                           |  |

| [65] | SFP, T-gate, Al <sub>2</sub> O <sub>3</sub> /HfO <sub>2</sub><br>gate oxide | 10 <sup>9</sup> | 230                                          | 1.40 k              | 2.90                                      | 7.08 m                                     | NR                                                             | 277                            |  |

| [66] | Scaled T-gate MESFET                                                        | $10^{4}$        | 60                                           | 2.45 k              | 2.08                                      | 17.3 m                                     | 84                                                             | 347                            |  |

| [67] | SOI on sapphire                                                             | $10^{8}$        | 232                                          | 800                 | NR                                        | 7.41 m                                     | 137                                                            | 86.3                           |  |

| [68] | Back-gate SOI on SiO <sub>2</sub> /Si                                       | $10^{10}$       | 1500                                         | NR                  | NR                                        | NR                                         | NR                                                             | NR                             |  |

| [69] | CAVET, N <sup>++</sup> ion implant                                          | $10^{8}$        | $420 \text{ A cm}^{-2}$                      | 25                  | NR                                        | 31.5 m                                     | 140                                                            | NR                             |  |

| [70] | AlGO/GO w/GFP                                                               | $10^{8}$        | NR                                           | 1.37 k              | 0.86                                      | 120 m                                      | 101                                                            | 15.6                           |  |

| [71] | SOI on AlN/Si                                                               | 10 <sup>9</sup> | 580                                          | 118                 | 1.04                                      | 1.44 m                                     | 82.9                                                           | 9.70                           |  |

| [72] | SiC/GO composite wafer                                                      | $10^{8}$        | NR                                           | 2.37 k              | 1.23                                      | 18.4 m                                     | 94                                                             | 303                            |  |

| [73] | SOI on Diamond                                                              | NR              | 980                                          | NR                  | NR                                        | NR                                         | NR                                                             | NR                             |  |

| [74] | p-NiO gate oxide                                                            | $10^{10}$       | 450                                          | 1.12 k              | 2.48                                      | 3.19 m                                     | NR                                                             | 390                            |  |

| [75] | p-NiO gate oxide                                                            | $10^{10}$       | 282                                          | 2.15 k              | 3.5                                       | 6.24 m                                     | 130                                                            | 740                            |  |

| [76] | p-NiO/SiO <sub>2</sub> gate oxide                                           | 109             | 300                                          | 1.32 k              | 1.47                                      | 4.30 m                                     | NR                                                             | 405                            |  |

| [77] | p-SnO gate oxide                                                            | $10^{6}$        | 100                                          | 750                 | 1.9                                       | 3.15 m                                     | 100                                                            | 178                            |  |

| [78] | BTO ( $\varepsilon \approx 235$ ) gate oxide                                | $10^{5}$        | 359                                          | 640                 | 1.5                                       | 1.08 m                                     | 72                                                             | 376                            |  |

| [79] | Al <sub>2</sub> O <sub>3</sub> /BTO gate oxide                              | 107             | 220                                          | 840                 | 4.10                                      | 1.72 m                                     | 85                                                             | 408                            |  |

Table 2. Performance comparison of D-mode high-power FETs.

Table 3. Performance comparison of E-mode high-power FETs.

| Ref. | FET Design                                                                                                | On/Off            | I <sub>D,max</sub><br>(mA mm <sup>-1</sup> ) | V <sub>br</sub> (V) | E <sub>br</sub><br>(MV cm <sup>-1</sup> ) | R <sub>on,sp</sub><br>(Ω cm <sup>2</sup> ) | $\mu^{\mu}$ (cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> ) | BFOM<br>(MW cm <sup>-2</sup> ) |

|------|-----------------------------------------------------------------------------------------------------------|-------------------|----------------------------------------------|---------------------|-------------------------------------------|--------------------------------------------|----------------------------------------------------------------|--------------------------------|

| [80] | Recessed gate                                                                                             | 10 <sup>9</sup>   | 40                                           | 505                 | 0.84                                      | 17.2 m                                     | 106                                                            | 14.8                           |

| [81] | Multi-fin vertical FET                                                                                    | $10^{8}$          | $230 \text{ A cm}^{-2}$                      | 2.66 k              | NR                                        | 25.2 m                                     | 40                                                             | 280                            |

| [82] | SOI on SiO <sub>2</sub> /Si                                                                               | $10^{10}$         | 450                                          | 185                 | 2                                         | $20 \Omega  mm$                            | 55.2                                                           | NR                             |

| [83] | Mg-diffused CAVET                                                                                         | 10 <sup>9</sup>   | $150 \text{ A cm}^{-2}$                      | 72                  | NR                                        | NR                                         | 7.5                                                            | NR                             |

| [84] | Vertical U-trench w/CBL                                                                                   | $6.4	imes10^4$    | $11 \text{ A cm}^{-2}$                       | 102                 | NR                                        | 1.48                                       | NR                                                             | 0.007                          |

| [76] | p-NiO/SiO <sub>2</sub> gate oxide                                                                         | $10^{8}$          | NR                                           | 2.96 k              | 0.985                                     | 115 m                                      | NR                                                             | 76                             |

| [75] | p-NiO gate oxide                                                                                          | $10^{7}$          | 43.2                                         | 1.98 k              | 3.3                                       | 13.8 m                                     | 140                                                            | 284                            |

| [85] | Back-gate SOI on SiO <sub>2</sub> /Si<br>p-SnO on top                                                     | $2.26 	imes 10^6$ | 14.1                                         | NR                  | NR                                        | NR                                         | 191                                                            | NR                             |

| [86] | SOI on SiO <sub>2</sub> /Si<br>HfO <sub>2</sub> gate oxide                                                | 10 <sup>5</sup>   | 11.1                                         | 80                  | 0.16                                      | 82 m                                       | 81                                                             | 0.078                          |

| [87] | Multi-stack gate:<br>HZO/Al <sub>2</sub> O <sub>3</sub> /HfO <sub>2</sub> /Al <sub>2</sub> O <sub>3</sub> | 10 <sup>8</sup>   | 23.2                                         | 2.14 k              | 3.45                                      | 24 m                                       | 97                                                             | 193                            |

| Ref.  | Туре | Structure                                               | On/Off            | I <sub>D,max</sub><br>(mA mm <sup>-1</sup> ) | V <sub>br</sub><br>(V) | E <sub>br</sub><br>(MV cm <sup>-1</sup> ) | $\mu^{\mu}$ (cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> ) | f <sub>T</sub> (GHz) | f <sub>max</sub><br>(GHz) | G <sub>p</sub> (dB) | G <sub>T</sub><br>(dB) | P <sub>out</sub><br>(mW mm <sup>-1</sup> ) | PAE<br>(%) | f <sub>T</sub> V <sub>br</sub><br>(THz V) | $v_{sat}$ (f <sub>T</sub> L <sub>g</sub> 2 $\pi$ )<br>(cm s <sup>-1</sup> ) |

|-------|------|---------------------------------------------------------|-------------------|----------------------------------------------|------------------------|-------------------------------------------|----------------------------------------------------------------|----------------------|---------------------------|---------------------|------------------------|--------------------------------------------|------------|-------------------------------------------|-----------------------------------------------------------------------------|

|       |      | T-gate                                                  |                   |                                              |                        |                                           |                                                                |                      |                           |                     |                        |                                            |            |                                           |                                                                             |

| [88]  | D-M  | delta-doped<br>MESFET                                   | 108               | 260                                          | 150                    | 1.07                                      | 70                                                             | 27                   | 16                        | NR                  | NR                     | NR                                         | NR         | 4.05                                      | $2.01 	imes 10^6$                                                           |

| [89]  | D-M  | SAG                                                     | 108               | Pulsed $\approx 300$                         | NR                     | NR                                        | 74                                                             | NR                   | NR                        | NR                  | 13                     | 715                                        | 23.4       | NR                                        | NR                                                                          |

| [90]  | D-M  | Recessed gate<br>SiO <sub>2</sub> passivation           | 106               | 150                                          | NR                     | NR                                        | 96                                                             | 3.3                  | 12.9                      | 5.1                 | 1.8                    | 230                                        | 6.3        | NR                                        | $1.45 	imes 10^6$                                                           |

| [91]  | D-M  | Tri-gate FinFET                                         | NR                | 88                                           | NR                     | NR                                        | NR                                                             | 5.4                  | 11.4                      | NR                  | NR                     | NR                                         | NR         | NR                                        | $1.19	imes10^6$                                                             |

| [92]  | D-M  | SiO <sub>2</sub> GFP                                    | NR                | 58                                           | NR                     | NR                                        | NR                                                             | NR                   | NR                        | 4.81                | NR                     | 130                                        | 22.4       | NR                                        | NR                                                                          |

|       |      | T-gate, SiN <sub>x</sub>                                |                   |                                              |                        |                                           |                                                                |                      |                           |                     |                        |                                            |            |                                           |                                                                             |

| [93]  | D-M  | passivation                                             | $1.23 	imes 10^5$ | 285                                          | 192                    | 5.4                                       | 80                                                             | 11                   | 48                        | NR                  | NR                     | NR                                         | NR         | 2.112                                     | $2.45	imes10^6$                                                             |

|       |      | SiO <sub>2</sub> gate oxide<br>T-gate, shallow          |                   |                                              |                        |                                           |                                                                |                      |                           |                     |                        |                                            |            |                                           | <i>,</i>                                                                    |

| [94]  | D-M  | ion-implanted<br>channel<br>OA, SiN <sub>x</sub> T-gate | 108               | 165                                          | 193                    | 2.09                                      | 23                                                             | 29                   | 35                        | 7                   | NR                     | 11.2 dBm                                   | 11.6       | 5.597                                     | $2.73 \times 10^{6}$                                                        |

|       | DV   | Multi-stack gate                                        | 100               | 200                                          | NID                    | NID                                       |                                                                | 1.0                  | 4.0                       | 2 (                 | NID                    | 100                                        | ( 12       | NID                                       | 1 1 0 1 0 6                                                                 |

| [95]  | D-M  | oxide:                                                  | 109               | 200                                          | NR                     | NR                                        | 75                                                             | 1.8                  | 4.2                       | 3.6                 | NR                     | 430                                        | 6.42       | NR                                        | $1.13 	imes 10^6$                                                           |

|       |      | Al <sub>2</sub> O <sub>3</sub> /HfO <sub>2</sub>        |                   |                                              |                        |                                           |                                                                |                      |                           |                     |                        |                                            |            |                                           |                                                                             |

| [96]  | D-M  | AlGO/GO HFET                                            | NR                | Pulsed $\approx 80$                          | NR                     | NR                                        | NR                                                             | 14                   | 22                        | NR                  | NR                     | NR                                         | NR         | NR                                        | $1.76 	imes 10^6$                                                           |

| [97]  | E-M  | AlGO/GO HFET                                            | $1.55	imes10^5$   | 74                                           | 23                     | 1.35                                      | NR                                                             | 30                   | 37                        | NR                  | NR                     | NR                                         | NR         | NR                                        | $3.02	imes10^6$                                                             |

|       |      |                                                         |                   |                                              |                        |                                           | GaN and Diamon                                                 | d RF FETs            |                           |                     |                        |                                            |            |                                           |                                                                             |

| [98]  | D-M  | GaN HEMT                                                | 10 <sup>3</sup>   | 1000                                         | 60                     | 0.4                                       | 1900                                                           | 104                  | 205                       | 8                   | NR                     | 5100                                       | 43.6       | 6.24                                      | $9.80	imes10^6$                                                             |

| [99]  | D-M  | GaN HEMT                                                | $3 \times 10^5$   | Pulsed 1300                                  | 50                     | NR                                        | 1423                                                           | 156                  | 308                       | 15                  | NR                     | 2500                                       | 70         | 7.8                                       | $5.89 \times 10^{6}$                                                        |

| [100] | D-M  | Diamond HEMT                                            | NR                | 500                                          | 121                    | 0.81                                      | 101                                                            | 6.2                  | 17                        | 12.2                | NR                     | 4200                                       | 21.5       | 0.75                                      | $3.51 \times 10^{6}$                                                        |

# 3.1. $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FET Structures

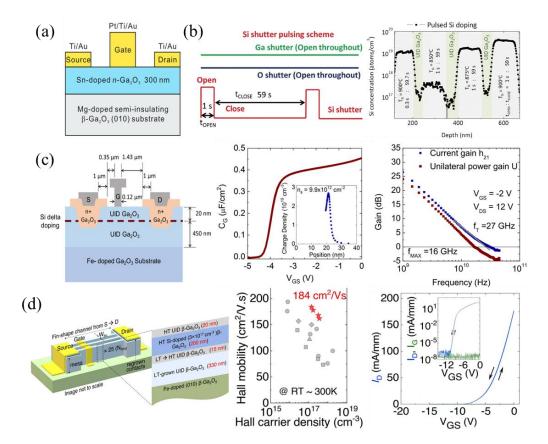

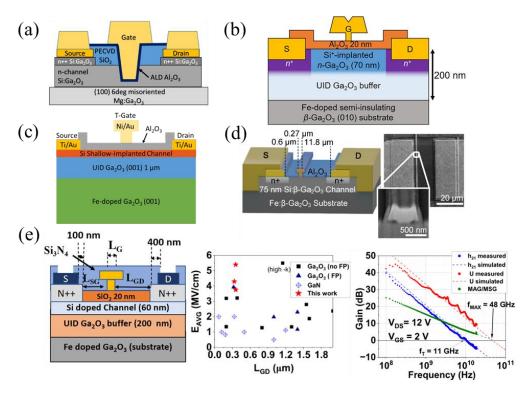

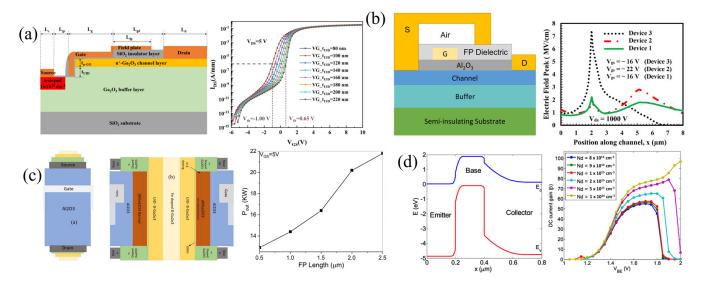

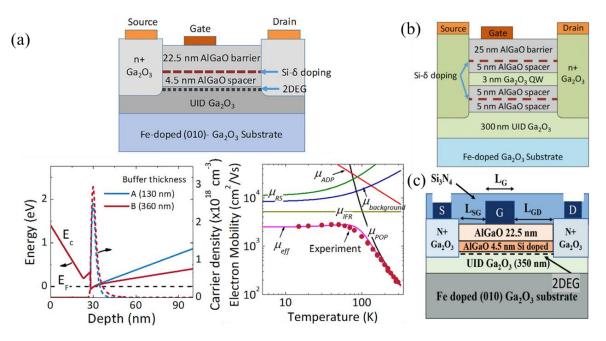

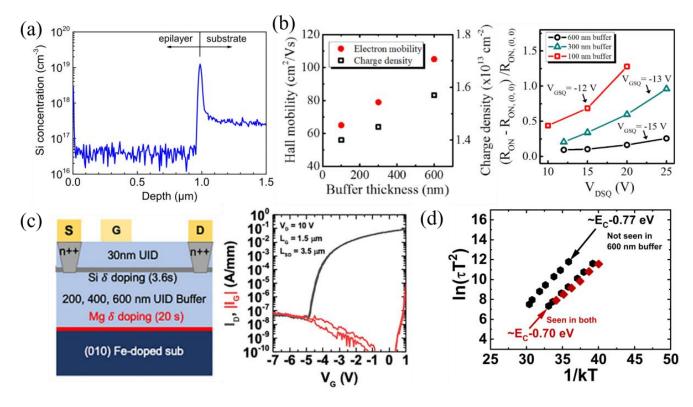

# 3.1.1. MESFETs and Delta Doping

The metal-semiconductor field-effect transistor (MESFET) in Figure 3a, fabricated by Higashiwaki et al., was the first demonstrated single-crystal  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> transistor [101]. Many of the following MESFETs, reported by the Rajan group, incorporated delta doping [60,88,102–106]. The delta-doping technique was first developed in 2017 by Krishnamoorthy et al. [102] in attempts to improve Si doping during PAMBE epi layer growth. The Si source oxidized quickly, reducing the Si doping level in the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>, creating doping spikes. Pulsing the Si shutter for 1 s over a period of 1 min removed the oxide and created uniform, highly doped regions with UID spacers (Figure 3b), leading to the delta-doping method for  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> devices. This resulted in a 2D electron gas (2DEG), highelectron-mobility transistor (HEMT) behavior with an increased carrier sheet concentration and mobility, as well as reduced contact and sheet resistances. These improvements and lower gate capacitance of MESFETs compared to MOSFETs lend delta-doped MESFETs more for RF applications. Regrown ohmic contacts, discussed in the Section "Regrown Layers", are required for delta-doped FETs to reach the 2DEG because it is surrounded by UID  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>. The Rajan group fabricated delta-doped MESFETs using regrown contacts, gate-connected field plates (GFP), and highly scaled T-gate structures with gate lengths  $(L_G)$  down to 120 nm to improve their low- and high-frequency performance, with a BFOM of 118 MW cm<sup>-2</sup> [60], a mobility of 95 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> [104], and a current gain cutoff frequency (f<sub>T</sub>) of 27 GHz (Figure 3c) [88]. The GFP and T-gate structures are also discussed in Sections 3.1.5 and 3.1.7, respectively.

**Figure 3.** (a) First MESFET reported in 2013. Reproduced from [101], with the permission of AIP Publishing. (b) Shutter pulsing scheme and doping variation showing alternating UID and uniformly doped layers. Reproduced from [102]. © The Japan Society of Applied Physics. Reproduced with the permission of IOP Publishing Ltd. All rights reserved. (c) Highly scaled T-gate delta-doped MESFET

with high cutoff and maximum frequencies. © (2019) IEEE. Reprinted with permission from [88]. (d) Tri-gate MESFETs with low-temp/high-temp grown layers resulting in ultra-high mobilities and negligible I-V hysteresis. © (2022) IEEE. Reprinted with permission from [63].

Bhattacharyya et al. reported high-performing, non-delta-doped lateral MESFETs using a combination of regrown ohmic contacts for a low contact resistivity of  $8.3 \times 10^{-7} \Omega \text{ cm}^2$  [107], GFP for a V<sub>br</sub> up to 4.4 kV [108,109], and a fin-shaped channel design surrounded by variable-temperature MOCVD-grown layers, achieving a mobility of 184 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, negligible hysteresis, and a BFOM of 0.95 GW cm<sup>-2</sup> [63]. Passivating layers such as Al<sub>2</sub>O<sub>3</sub> and SiN<sub>x</sub> can also be used to improve both low-frequency BFOMs and high-frequency Huang's Material Figure of Merit (HMFOM) [63,66]. The current highest-reported FET breakdown voltage of 10 kV was achieved using a MESFET design with a T-gate structure, source-connected field plates (SFPs), SiN<sub>x</sub> passivation, oxygen annealing (OA), Si ion implantation, UID buffer layers surrounding the channel region, and B implantation for device isolation [59]. These device improvements will be discussed in more detail in later sections.

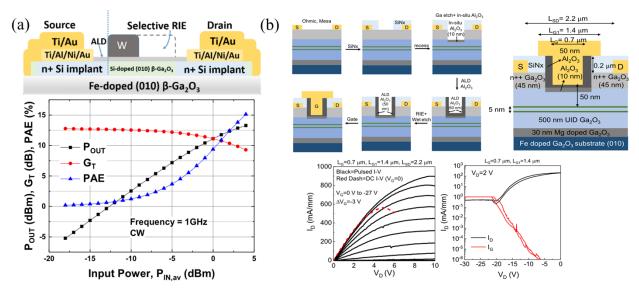

# 3.1.2. Self-Aligned Gate (SAG) FETs

The self-aligned gate (SAG) FET design is a well-known process developed to reduce series resistance and aggressively scale devices by reducing the source–gate spacing ( $L_{SG}$ ), essentially eliminating the source–gate access region. The earliest  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> SAG FETs, developed by AFRL, were designed by first depositing the Al<sub>2</sub>O<sub>3</sub> gate dielectric using plasma-assisted atomic layer deposition (PA-ALD), which acts as the ion implantation cap. A refractory metal gate of W or W/Cr, able to withstand the high ion activation temperature, is patterned to protect the gate and drift regions. The source-gate and drain-gate access regions are then very highly doped via Si ion implantation and activated at 900 °C using rapid thermal annealing (RTA) for 2 min in  $N_2$  ambient conditions [89,110]. The gate metal is then etched via reactive ion etching (RIE) from the drift region and the ohmic contacts are formed (Figure 4a). A low contact resistance ( $R_C$ ) of 1.5  $\Omega$  mm, a sheet charge density  $(n_s)$  of  $4.96 \times 10^{12}$  cm<sup>-2</sup>, and a Hall mobility of 48.4 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> were measured in these devices [110]. RF load-pull continuous wave (CW) power measurements were reported for these early SAG FETs, with a high output power ( $P_{out}$ ), transducer gain ( $G_T$ ), and power-added efficiency (PAE) of 715 mW mm<sup>-1</sup>, 13 dB, and 23.4%, respectively, at 1 GHz (Figure 4a) [89,111].

A recent PAMBE-grown delta-doped SAG FET structure incorporated delta doping, in situ Ga etching for gate recess, and in situ  $Al_2O_3$  gate dielectric growth, achieving sub-100 nm source-gate and gate-drain access regions [61]. A 30 nm Mg-doped layer was initially grown to compensate the Si impurities at the substrate/epi interface, followed by a 500 nm UID buffer layer. Then, two delta-doping layers, 5 nm apart, another 40 nm UID layer, and a 45 nm n++ cap layer were grown. The n++ cap layers were used as an alternative to ion implantation, enabling SAG. The SAG fabrication process (Figure 4b) began with ohmic contact fabrication and the plasma-enhanced chemical vapor deposition (PECVD) of  $SiN_x$  with patterning to expose the gate region. The sample was placed into an MBE system, where in situ Ga etching of the n++ cap layer was performed at a substrate temperature of 550 °C and Ga flux of  $1.5 \times 10^{-7}$  Torr. Ga droplets were removed at a temperature of 600 °C, followed by 10 nm in situ Al<sub>2</sub>O<sub>3</sub> deposition at a temperature of 400 °C. Conformal ex situ ALD was used to uniformly deposit 60 nm of  $Al_2O_3$  in the gate and sidewall regions. Anisotropic RIE and isotropic BOE wet-etching of the Al<sub>2</sub>O<sub>3</sub> reduced the gate and sidewall dielectric thickness to 20 nm and 50 nm, respectively. This FET outperformed the initial SAG FETs, with a source–gate access resistance of 1.3  $\Omega$  mm, an  $n_s$ of  $2.8 \times 10^{13}$  cm<sup>-2</sup>, and a mobility of 65 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, leading to record peak DC and pulsed drain currents of 560 mA mm<sup>-1</sup> and 895 mA mm<sup>-1</sup>, respectively, for a lateral FET on a native  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> substrate. The FET exhibited a high gate leakage and low current on/off ratio due to a low-quality gate dielectric or remaining Ga droplets at the interface. A drain

current droop was observed in the DC measurements, indicating excessive self-heating, as shown by the red dashed line in Figure 4b. The use of SAG FETs has not yet been translated to vertical devices but is expected to improve performance for both low- and high-frequency operation.

**Figure 4.** (a) SAG FET using refractory metal gate W and Si ion implantation for self-alignment with an  $L_{SG}$  of 0 µm. The RF  $P_{out}$ ,  $G_T$ , and PAE as a function of input power at 1 GHz are plotted. Reproduced from [89]. CC BY 4.0. (b) SAG process enabled by using an n++ grown cap layer as opposed to ion implantation. High gate leakage and low on/off ratio are indicative of a leaky dielectric due to its deposition or residual Ga droplets at the interface. Reproduced from [61], with the permission of AIP Publishing.

# 3.1.3. Trench/Recessed-Gate FETs

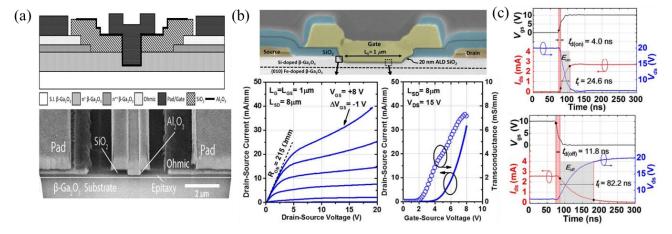

Another FET design, first implemented by AFRL in 2017 [90], is the trench or recessed gate to scale devices down to sub-µm gate lengths for improved RF performance. The FET in ref. [90] was fabricated on an n+ 180 nm channel layer with an n++ 25 nm ohmic cap layer grown via MOVPE. Post-ohmic contact formation, the n++ cap layer was etched and 200 nm of SiO<sub>2</sub> was deposited via PECVD as the passivation and field-plate dielectric. A 0.7 µm gate region was patterned on the SiO<sub>2</sub> and etched via RIE nearly halfway into the epi layer, followed by ALD-Al<sub>2</sub>O<sub>3</sub> deposition as the gate dielectric, Ni/Au gate stack evaporation, and the evaporation of interconnects (Figure 5a). The measured cutoff frequency ( $f_T$ ) and maximum oscillating frequency ( $f_{MAX}$ ) were 3.3 GHz and 12.9 GHz [90].

E-mode FETs are useful in reducing off-state power loss; however, they are difficult to fabricate in  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> due to the lack of p-type doping, large hole effective mass, and hole self-trapping. The recessed-gate approach is among the few early methods used to achieve E-mode operation by etching into the channel region, such that the remaining channel is fully depleted due to band bending at the oxide/epi and epi/substrate interfaces [112,113]. Chabak et al. [80] studied the band bending of a 200 nm Si-doped 5.5 × 10<sup>17</sup> cm<sup>-3</sup> epi due to 5.5 × 10<sup>12</sup> cm<sup>-2</sup> surface states at the SiO<sub>2</sub>/ $\beta$ -Ga<sub>2</sub>O<sub>3</sub> interface, noting an approximately 100 nm depletion, and 34 nm of depletion due to the Fe-doped substrate. The E-mode FET with a threshold voltage (V<sub>th</sub>) of +2 V was realized due to a gate recess of 140 nm (Figure 5b). E-mode recessed-gate FETs with an epi thickness of 200 nm, etch depth of 180 nm, and an L<sub>G</sub> of 2 µm were also reported to have high switching characteristics, with turn-on/off delay times of 4.0 ns/11.8 ns and rise/fall times of 24.6 ns/82.2 ns (Figure 5c). The longer fall time is attributed to low electron mobility and slow discharging from interface states. While switching losses are reduced with higher switching speeds, a high on-resistance (R<sub>on</sub>), identified based on the V<sub>DS</sub> of  $\approx 5$  V in the top plot of Figure 5c, results in high

on-state power losses that might be more limiting than switching losses [114]. A high  $R_{on}$  and increased power losses are observed for many trench FETs; however, further  $L_G$  scaling by incorporating SAG can reduce the channel resistance contribution.

**Figure 5.** (a) First recessed-gate FET reported with sub- $\mu$ m L<sub>G</sub>. Reprinted with permission from [90]. (b) First E-mode recessed-gate FET and respective transfer and output curves. © (2018) IEEE. Reprinted with permission from [80]. (c) Switching characteristics of a recessed-gate lateral FET where turn-on delay time, t<sub>d(on)</sub>, is defined as the time between  $0.1V_{gs}$  and  $0.1I_{ds}$ . Likewise, t<sub>d(off)</sub> is the time between  $0.9V_{gs}$  and  $0.9I_{ds}$ . Similarly, the rise time, t<sub>r</sub>, is the time between  $0.1I_{ds}$  and  $0.9I_{ds}$ , and the fall time, t<sub>f</sub>, is the time between  $0.9I_{ds}$  and  $0.0I_{ds}$ . © (2019) IEEE. Reprinted with permission from [114].

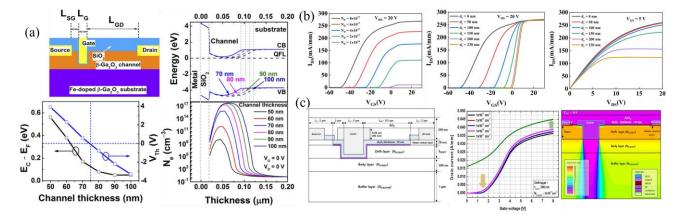

Various TCAD studies have been reported on the effects of doping and recess depth in E-mode recessed-gate FETs. The band diagram variation, electron concentration, and  $V_{th}$  at different channel thicknesses (epi thickness-recess depth) is shown in Figure 6a. At zero gate and drain bias, the electron concentration drops off very quickly as the channel thickness drops below 80 nm, down to  $\approx 10^8$  cm<sup>-3</sup> at 50 nm, because of the oxide/epi and substrate/epi depletion. A threshold voltage near 0 V is observed for a 75 nm channel thickness going up to +4 V for 50 nm [115]. Decreasing the doping concentration in the channel layer is observed to both decrease the peak drain current and increase the  $V_{th}$ , such that a doping of  $1 \times 10^{16}$  cm<sup>-3</sup> causes E-mode behavior (Figure 6b). A larger recess depth (smaller channel thickness) increased the V<sub>th</sub> from  $\approx$  -50 V to near 0 V from the I-V transfer curves but decreased the drain current in the I-V output curves (Figure 6b) [116]. At high  $V_{CS}$  and  $V_{DS}$ , however, the drain current is nearly equal, indicating that the recess depth has little actual effect on the peak drain current. A slightly different trench FET design using body and epitaxial drift layers with different dopings, as well as recess through the entire drift layer, is shown in Figure 6c [117]. From I-V transfer curves with a drift layer doping of  $3 \times 10^{17}$  cm<sup>-3</sup> and varying body doping from  $1 \times 10^{13}$  to  $1 \times 10^{17}$  cm<sup>-3</sup>, E-mode operation was only realizable for a body doping of  $1 \times 10^{15}$  cm<sup>-3</sup> or less, showing a larger current and more negative Vth for higher doping concentrations. A 2D view of the electron concentration at a V<sub>GS</sub> of 0 V,  $N_{Bodv}$  of  $1 \times 10^{15}$  cm<sup>-3</sup>, and  $N_{Drift}$  of  $3 \times 10^{17}$  cm<sup>-3</sup> (Figure 6c) shows normally off conditions due to the full depletion of the body layer from band bending at the oxide/body interface.

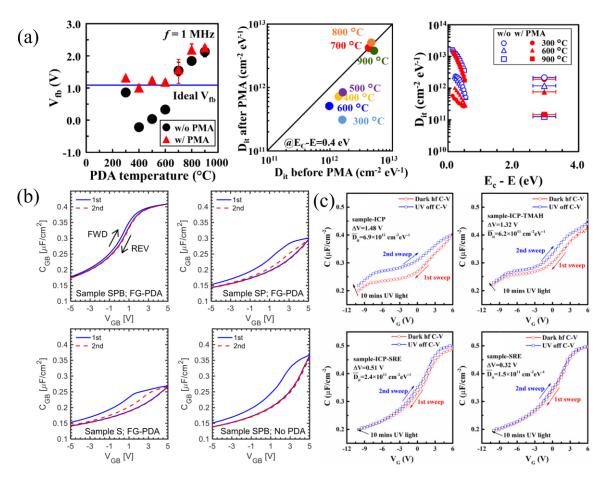

**Figure 6.** (a) TCAD model of a recessed-gate FET studying variations in fermi level,  $V_{th}$ , and electron concentration with channel thickness. Reproduced from [115]; licensed under a Creative Commons Attribution (CC BY) license. (b) TCAD model of a recessed-gate FET studying variations in  $V_{th}$  and current density with doping and recess depth. Reprinted from [116], Copyright (2023), with permission from Elsevier. (c) A novel recessed-gate FET design with different body and drift layers recessing fully through the drift layer. Body-doping effects on E-/D-mode operation as well as a 2D cross-section of band bending through the body layer at low dopings. Reproduced from [117]. CC BY 4.0.

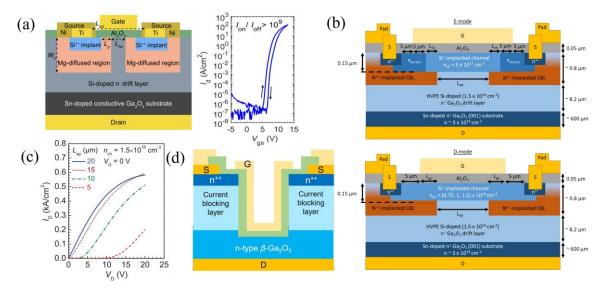

#### 3.1.4. FinFETs

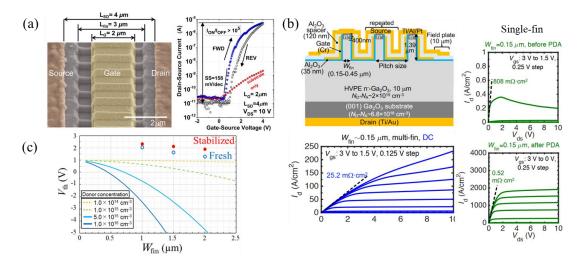

The first FinFET structures were lateral devices designed by Chabak et al. in 2016 using inductively coupled plasma (ICP) over-etching into the substrate to create thin 300 nm triangular-shaped fins as the channel (Figure 7a) [113]. E-mode operation was enabled by channel depletion due to the gate, with the I-V transfer curve shown in Figure 7a. Substrate conduction, shown by the red curve in Figure 7a, was observed and attributed to uncompensated carriers at the substrate surface. Hu et al. fabricated various vertical singlefin E-mode FETs [118–120] with current densities reaching 1 kA cm<sup>-2</sup>, a V<sub>br</sub> of 1.6 kV, and a low subthreshold slope (SS) of 80 mV dec<sup>-1</sup>, giving an interface trap state density (D<sub>it</sub>) of  $>6 \times 10^{11}$  cm<sup>-2</sup> eV<sup>-1</sup>. Interface traps were observed to reduce the field-effect mobility and current density by depleting the channel, as well as limiting breakdown by exacerbating drain-induced barrier lowering (DIBL) [118]. Single- and multi-fin E-mode FETs were later fabricated by Li et al. with single/multi-fin current densities of 2 kA cm<sup>-2</sup>/230 A cm<sup>-2</sup>, a  $R_{on,sp}$  of 35.2 m $\Omega$  cm<sup>2</sup>/25.2 m $\Omega$  cm<sup>2</sup>, and BFOMs of 172 MW cm<sup>-2</sup>/280 MW cm<sup>-2</sup> for a fin width (W<sub>fin</sub>) of 0.15 µm. Another advantage of multi-fin FETs is that, unlike single-fin FETs, current spreading does not drastically change the active area, making the BFOM and Ron, sp less ambiguous. The fabrication was performed on a 10 µm HVPE epi layer with doping of  $2 \times 10^{15}$  cm<sup>-3</sup> grown on a conductive substrate. First, the epi layer was Si-ion implanted and activated at 1000 °C for the source ohmic contact, followed by e-beam lithography and dry etching to form sub-µm fin channels. A Ti/Au stack was deposited on the backside as the drain contact and a 35 nm ALD-Al<sub>2</sub>O<sub>3</sub> was used as the gate dielectric. A sputtered Cr gate metal and 120 nm ALD-Al<sub>2</sub>O<sub>3</sub> spacer were patterned with an SAG process. Finally, a Ti/Al/Pt stack was sputtered, forming the source and source-connected field plate. The devices were measured before and after post-deposition annealing (PDA) at 350  $^{\circ}$ C in N<sub>2</sub>, resulting in significant improvements (Figure 7b) [81]. It has been shown that V<sub>th</sub> strongly decreases with increasing W<sub>fin</sub> and N<sub>D</sub> (Figure 7c), giving a small window for normally off devices. The previously mentioned FinFETs were fabricated with sub-0.5  $\mu m$   $W_{fin}$  and  $N_D$ below  $1 \times 10^{16}$  cm<sup>-3</sup>, enabling a positive V<sub>th</sub>. Because Si doping below  $3 \times 10^{15}$  is difficult in epi growth, a resistive layer via nitrogen doping of  $1 \times 10^{16}$  cm<sup>-3</sup> during HVPE growth was shown to significantly minimize the Vth dependence on Wfin and achieve normally off operation for  $W_{fin}$  up to 2  $\mu$ m (Figure 7c) [121].

**Figure 7.** (a) Lateral E-mode FinFETs and transfer curves with observed substrate conduction due to free carriers at the semi-insulating substrate. Reproduced from [113]. CC BY 4.0. (b) Cross-section of vertical multi-fin FETs, I-V curves of a single-fin FET showing significant improvement through PDA, and multi-fin FET I-V curves. © (2019) IEEE. Reprinted with permission from [81]. (c) Nitrogen doping mitigating the V<sub>th</sub> dependence on W<sub>fin</sub> and maintaining E-mode operation for large W<sub>fin</sub>. Reproduced from [121]. © The Japan Society of Applied Physics. Reproduced by permission of IOP Publishing Ltd. All rights reserved.

Other vertical FinFETs have been reported on (100) oriented substrates to potentially reduce intrinsic growth defects, even though the majority are fabricated on (001) substrates [122]. Lateral tri-gate FinFETs have also reported high RF performance [91], high BFOMs of 0.95 GW cm<sup>-2</sup>, and mobilities of 184 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> using high/low temperature MOCVD growths [63], as mentioned in Section 3.1.1.

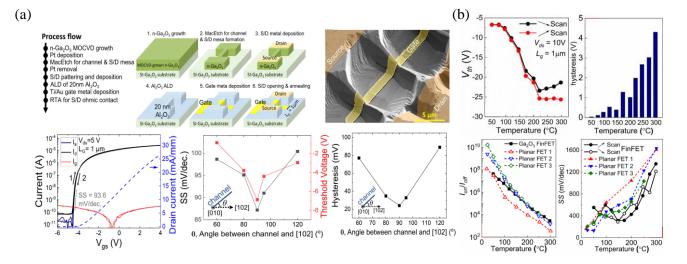

A highly selective wet-etching technique, metal-assisted chemical etching (MacEtch), is an attractive, damage-free alternative to dry etching that is typically used in FinFET fabrication [123]. More details on the MacEtch techniques and chemical reactions can be found in Ref. [124]. Lateral FinFETs fabricated via MacEtch have recently been reported (Figure 8a), with an aspect ratio of 4.2:1, an R<sub>on,sp</sub> of 6.5 m $\Omega$  cm<sup>2</sup>, and a BFOM of 21 MW cm<sup>-2</sup> [125]. The lowest SS, V<sub>th</sub>, and hysteresis of 87.2 mV dec<sup>-1</sup>, -6.9 V, and 24 mV, respectively, were measured on FinFETs with a 90° orientation from the [102] direction (Figure 8a). A previous study showed that fins perpendicular to [102] had the most vertical sidewalls and lowest D<sub>it</sub> of  $2.73 \times 10^{11}$  cm<sup>-2</sup> eV<sup>-1</sup> [126]. DC I-V measurements of these FinFETs at high temperatures up to 298 °C (Figure 8b) reported increasing off-state currents and a lower on/off ratio, attributed to thermionic emission from source to drain, a decrease in V<sub>th</sub> by  $\approx 20$  V due to trapping/de-trapping at the gate metal/oxide and oxide/semiconductor interfaces, and increasing hysteresis up to 4.29 V and SS up to 1.35 V dec<sup>-1</sup>, indicating thermal degradation of the interface or dielectric [127].

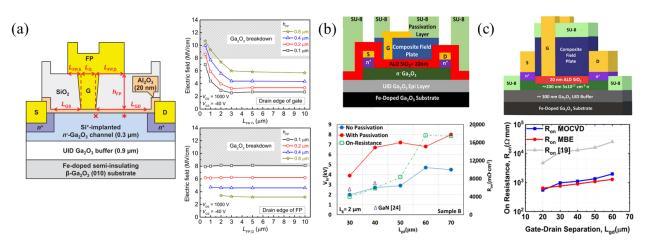

# 3.1.5. Gate-Connected Field Plates

It is widely known that field plates can improve device breakdown by reducing the peak electric field near the contact edges. The gate-connected field plate (GFP) extends into the gate-drain access region, where most of the voltage drop occurs, "spreading" the electric field. The first  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> GFP FET was reported by Wong et al., using SiO<sub>2</sub> as the FP dielectric (Figure 9a). TCAD simulations of the peak electric field for various field-plate heights, h<sub>FP</sub>, and field-plate drain lengths, L<sub>FP,D</sub>, at the drain edge of the gate (top), depicted by the symbol x in the diagram, and drain edge of FP (bottom), depicted by the symbol \* in the diagram, are shown in Figure 9a. Increasing the L<sub>FP,D</sub> is seen to quickly reduce the electric field at the gate edge, while having little effect on the field at the FP edge. However,

as the  $h_{FP}$  increases, the field at the gate edge rises while the field at the FP edge falls, indicating an ideal window for  $h_{FP}$  [128].

**Figure 8.** (a) FinFETs fabricated via MacEtch with process and TEM image. I-V curves as well as SS and hysteresis dependence on channel angle relative to [102] are shown. Channels perpendicular to [102] show the best performance. Reproduced from [125], with the permission of AIP Publishing. (b) Temperature dependence of V<sub>th</sub>, hysteresis, on/off ratio, and SS in MacEtch FinFETs indicating thermal degradation of the interface and/or dielectric. Reprinted from [127], with the permission of AIP Publishing.

Since then, other SiO<sub>2</sub> FPs, SiO<sub>2</sub> composite FPs with polymer passivation, and SiN<sub>x</sub> FPs passivated with SiO<sub>2</sub> have been reported [64,92,108,109,129–131] with some of the highest breakdown voltages and BFOMs of 8.56 kV and 355 MW cm<sup>-2</sup>, respectively. SiN<sub>x</sub> is better suited both to spread electric fields due to its higher dielectric constant and in mitigating virtual gate effects originally discovered in AlGaN/GaN HEMTs [132], but is also mentioned as a possible mechanism of current dispersion [133] and series resistance increases [134] in  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FETs.

**Figure 9.** (a) GFP FET cross-section with the symbols x and \* indicating peak electric fields in the channel. Plots of simulated breakdown electric field dependence on  $L_{FP,D}$  and  $h_{FP}$  are shown at the location of symbol x (top plot) and \* (bottom plot). © (2016) IEEE. Reprinted with permission from [128]. (b) FET with composite PECVD-SiO<sub>2</sub> /ALD-SiO<sub>2</sub> GFP and SU8 passivation used to increase  $V_{br}$ . © (2020) IEEE. Reprinted with permission from [131]. (c) GFP FET similar to that in (b) but with SU8 as part of the FP and vacuum annealing, increasing  $V_{br}$  and reducing  $R_{on}$ . © (2022) IEEE. Reprinted with permission from [64].

Zeng et al. in the Singisetti group used a composite FP composed of a thick 350 nm PECVD-SiO<sub>2</sub> below a denser, high-quality 50 nm ALD-SiO<sub>2</sub> layer to improve break-down [129,130]. Sharma et al., also in the Singisetti group, then improved on the GFP design by adding a polymer, SU8, passivation layer on the composite FP and S/D regions, reaching some of the highest reported breakdown voltages of 8.03 kV (Figure 9b) and 8.56 kV (Figure 9c) [64,131]. The high R<sub>on</sub> led to low BFOMs, but vacuum annealing before FP deposition resulted in a ×10 reduction in R<sub>on</sub>, with little change in V<sub>br</sub> (Figure 9c) [64].

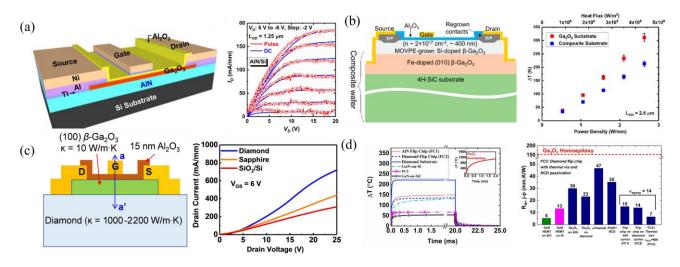

# 3.1.6. Source-Connected Field Plates

Source-connected field plates (SFPs) are another viable FP strategy where the source metal extends past the gate, and can be considered a better field-spreading method across the gate region and at the drain side of the gate [135,136]. One of the first SFP FETs measured a BFOM of 50.4 MW cm<sup>-2</sup> in 2019 (Figure 10a) [137]. Simulated electric field profiles in Figure 10a show field spreading and a reduced peak electric field using an SFP. A T-gate structure can be used in conjunction with SFPs for further field management, achieving higher BFOMs of 277 MW cm<sup>-2</sup> (Figure 10b [65]) and a record V<sub>br</sub> of 10 kV (Figure 10c [59]).

**Figure 10.** (a) Lateral MOSFET with SFP and simulated TCAD electric field profiles clearly showing field spreading and reduction in overall peak field value. © (2019) IEEE. Reprinted with permission from [137]. (b) FET with SFP and T-gate structure, breakdown I-V, and benchmark plot. © (2020) IEEE. Reprinted with permission from [65]. (c) FET with SFP, T-gate, oxygen annealing (OA), and B-implantation for device isolation. The blue/red lines represent an L<sub>GD</sub> of 40/100  $\mu$ m and solid/open symbols represent without/with SFP. A breakdown of 10 kV is observed. © (2023) IEEE. Reprinted with permission from [59].

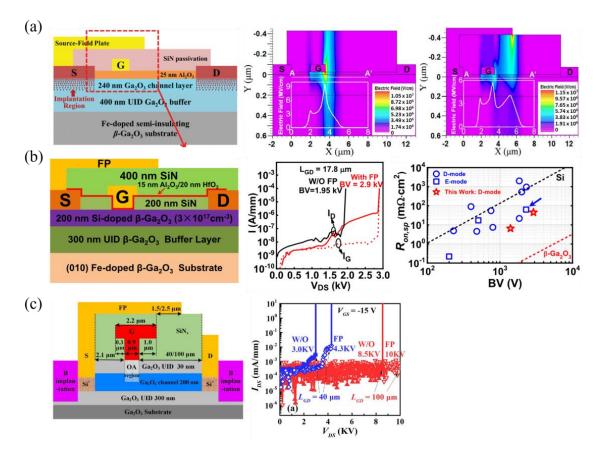

# 3.1.7. T-Gates

T-gates, as mentioned previously, are unique in that they not only improve breakdown as a field-plate structure [59,62], but also improve RF results in thin-channel FETs by decreasing the L<sub>G</sub> while maintaining a large cross-section. This reduces the gate access resistance and decreases the electron transport time, but does not degrade the noise figure [138]. Various T-gate RF FET structures are shown in Figure 11a–e that incorporate recessed gates with SiO<sub>2</sub> FP dielectrics (Figure 11a [139]), air FP dielectrics with implanted channels (Figure 11b,c [94,140]), MESFET with Al<sub>2</sub>O<sub>3</sub> passivation (Figure 11d [66]), and SiO<sub>2</sub> gate dielectrics with SiN<sub>x</sub> passivation (Figure 11e [93]). The FET in Figure 11e has the highest-reported f<sub>max</sub> to date of 48 GHz and a high breakdown field of 5.4 MV cm<sup>-1</sup>. A T-gate MESFET with an f<sub>T</sub> of 27 GHz was also discussed and shown in Figure 3b [88]. RF FETs with a T-gate structure must use highly scaled L<sub>G</sub>, typically in the range of 100–300 nm, for peak RF performance.

**Figure 11.** A variety of RF T-gate FETs are shown. (a) FET incorporates a recessed-gate architecture. Reprinted with permission from [139]. (b) FET uses air as the FP dielectric. Reprinted from [140], with the permission of AIP Publishing. (c) FET uses both an air FP dielectric and an ultra-thin implanted channel [94]. (d) FET incorporating  $Al_2O_3$  surface and gate metal passivation. Reprinted from [66]. CC BY-NC-ND 4.0. (e) T-gate RF FET with SiN<sub>x</sub> passivation with highest-reported f<sub>max</sub> and high breakdown field of 48 GHz and 5.4 MV cm<sup>-1</sup>, respectively. Reproduced from [93], with the permission of AIP Publishing.

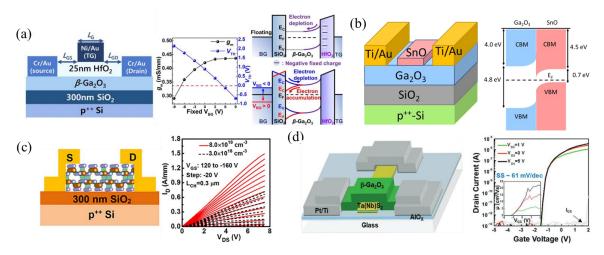

#### 3.1.8. Semiconductor-on-Insulator (SOI)

Another important property of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> is the anisotropic cleavage planes, making the (100) plane easy to exfoliate as a nanomembrane, similar to graphene. This makes the fabrication of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> devices on different substrates, or heterojunctions with unconventional materials such as transition metal dichalcogenides (TMDs), much simpler. The first SOI  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FET was reported in 2014, with an exfoliated  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> layer placed on a p+ Si wafer with 285 nm of thermally grown SiO<sub>2</sub> acting as the gate oxide [141]. The SOI FET was then fabricated via back-gate metal and top-source/drain ohmic contact deposition. The corresponding I-V curves proved that channels could be created using the mechanical exfoliation of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>. Other p+ back-gate SOI FETs have been fabricated and studied [68,82,142–151]. One advantage of SOI FETs compared to non-SOI FETs is that more devices can be fabricated from  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> wafers and, therefore, studies on transport, irradiation, thermal effects, etc., can be more cheaply and readily performed. Different methods of tuning the V<sub>th</sub> have been implemented, such as by varying the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> channel layer thickness [82,145], fluorine plasma [147], adding a p-type material such as p-SnO on the channel of back-gate FETs [85], and using a fixed back-gate bias (V<sub>BG</sub>) on top-gate FETs. A top-gate FET with V<sub>BG</sub> shows variation in transconductance (g<sub>m</sub>) and V<sub>th</sub> with V<sub>BG</sub>, obtaining a V<sub>th</sub> of 0 V for V<sub>BG</sub>  $\approx$  6 V (Figure 12a) [152]. Other studies about defect impacts on current dispersion [148], proton irradiation [144], scattering mechanisms [153], and device improvement using thermal management via different thermally conductive substrates have been reported using SOI FETs [71,73,154–159]. These will be discussed more in the Sections "AlN/GO", "SiC/GO", and "Diamond/GO". High-performing SOI FETs have also been realized, with the highest reported mobility of 191 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> (Figure 12b [85]), high current densities reaching 1.5 A mm<sup>-1</sup> (Figure 12c [68]), an SS of 61 mV dec<sup>-1</sup> very near the thermionic limit using a TMD-TaS<sub>2</sub>/ $\beta$ -Ga<sub>2</sub>O<sub>3</sub> heterojunction (Figure 12d [160]), a V<sub>br</sub> up to 800 V [67], and BFOMs of 100 MW cm<sup>-2</sup>. The high BFOM of 100 MW cm<sup>-2</sup> is achieved by a  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>-on-SiC FET using ion cutting, a novel heterogenous wafer-scale integration technique for  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> on SiC [156,159].

**Figure 12.** (a) SOI FET with V<sub>th</sub> modulation using constant back-gate voltage to accumulate or deplete the channel, while the top gate controls the device. © (2019) IEEE. Reprinted with permission from [152]. (b) SOI FET obtaining a record mobility of 191 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> using a floating p-SnO layer in the channel [85]. (c) SOI FET with a p++ back gate and doping of  $8 \times 10^{18}$  cm<sup>-3</sup>, measuring record currents of 1.5 A mm<sup>-1</sup>. Reprinted from [68], with the permission of AIP Publishing. (d) TMD high Schottky barrier gate with near-ideal SS of 61 mV dec<sup>-1</sup> when using TaS<sub>2</sub>. Reprinted with permission from Kim et al. [160] © 2023 Wiley-VCH GmbH.

Other SOI FETs have integrated  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> nanomembranes with various p-type 2D materials such as WSe<sub>2</sub> [161,162], MoTe<sub>2</sub> [162], and black phosphorus (BP) [163] to act as p-type gates, and large work function materials such as NbS<sub>2</sub> and TaS<sub>2</sub> to improve SS (61 mV dec<sup>-1</sup>) and off-state behavior [160]. Double-gate FETs using top-gate dielectrics such as HfO<sub>2</sub> [152], h-BN [164], and bottom-gate dielectrics as the SiO<sub>2</sub> on p-Si wafers have been utilized for improved gate control and V<sub>th</sub> tuning. Monolithically integrated top and bottom graphene gates with both E-mode and D-mode FETs on the same layer are one of the first mentions of a  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> logic circuit with both E-mode and D-mode FETs [165].

# 3.1.9. Other Novel Structures