Article

# Modeling of Charge-to-Breakdown with an Electron Trapping Model for Analysis of Thermal Gate Oxide Failure Mechanism in SiC Power MOSFETs

Jiashu Qian <sup>1,\*</sup>, Limeng Shi <sup>1</sup>, Michael Jin <sup>1</sup>, Monikuntala Bhattacharya <sup>1</sup>, Atsushi Shimbori <sup>2</sup>, Hengyu Yu <sup>1</sup>, Shiva Houshmand <sup>1</sup>, Marvin H. White <sup>1</sup> and Anant K. Agarwal <sup>1,\*</sup>

- Department of Electrical & Computer Engineering, The Ohio State University, Columbus, OH 43210, USA; shi.1564@osu.edu (L.S.); jin.845@osu.edu (M.J.); bhattacharya.119@osu.edu (M.B.); yu.3868@osu.edu (H.Y.); houshmand.3@osu.edu (S.H.); white.1829@osu.edu (M.H.W.)

- Ford Motor Co., Dearborn, MI 48126, USA; ashimbor@ford.com

- \* Correspondence: qian.539@osu.edu (J.Q.); agarwal.334@osu.edu (A.K.A.)

**Abstract:** The failure mechanism of thermal gate oxide in silicon carbide (SiC) power metal oxide semiconductor field effect transistors (MOSFETs), whether it is field-driven breakdown or charge-driven breakdown, has always been a controversial topic. Previous studies have demonstrated that the failure time of thermally grown silicon dioxide (SiO<sub>2</sub>) on SiC stressed with a constant voltage is indicated as charge driven rather than field driven through the observation of Weibull Slope β. Considering the importance of the accurate failure mechanism for the thermal gate oxide lifetime prediction model of time-dependent dielectric breakdown (TDDB), charge-driven breakdown needs to be further fundamentally justified. In this work, the charge-to-breakdown ( $Q_{BD}$ ) of the thermal gate oxide in a type of commercial planar SiC power MOSFETs, under the constant current stress (CCS), constant voltage stress (CVS), and pulsed voltage stress (PVS) are extracted, respectively. A mathematical electron trapping model in thermal SiO<sub>2</sub> grown on single crystal silicon (Si) under CCS, which was proposed by M. Liang et al., is proven to work equally well with thermal SiO<sub>2</sub> grown on SiC and used to deduce the  $Q_{BD}$  model of the device under test (DUT). Compared with the  $Q_{BD}$  obtained under the three stress conditions, the charge-driven breakdown mechanism is validated in the thermal gate oxide of SiC power MOSFETs.

**Keywords:** thermal gate oxide; SiC; MOSFET; charge-driven breakdown;  $Q_{BD}$ ; CCS; CVS; PVS; electron trapping model

Citation: Qian, J.; Shi, L.; Jin, M.; Bhattacharya, M.; Shimbori, A.; Yu, H.; Houshmand, S.; White, M.H.; Agarwal, A.K. Modeling of Charge-to-Breakdown with an Electron Trapping Model for Analysis of Thermal Gate Oxide Failure Mechanism in SiC Power MOSFETs. *Materials* 2024, 17, 1455. https:// doi.org/10.3390/ma17071455

Academic Editors: Marilena Vivona and Mike Jennings

Received: 5 February 2024 Revised: 12 March 2024 Accepted: 20 March 2024 Published: 22 March 2024

Copyright: © 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

## 1. Introduction

Silicon carbide (SiC) power MOSFETs are gradually gaining market attention due to their lower switching losses, higher temperature capability, higher switching frequencies, and increasingly competitive price compared to their silicon (Si) counterparts [1,2]. Especially in the field of electric vehicles (EVs), the aforementioned advantages make them largely attractive to EV OEMs and tier-one suppliers for potential applications in onboard chargers and drivetrain inverters [3–5]. Planar SiC power MOSFETs, with their relatively more mature process and cheaper manufacturing costs, have become the mainstream commercial SiC power MOSFETs on the market [6–11]. Trench SiC power MOSFETs, although optimized in device performance due to enhanced electron mobility and elimination of JFET resistance, as well as smaller cell pitch, still hold a relatively small market share due to their higher cost and lower reliability [12,13]. The lower reliability is mainly caused by electric field crowding at the corner of the trench gate and implantation-induced basal plane dislocation (BPD) [14–17]. Therefore, although the performance and structural limitations of planar SiC power MOSFETs are gradually becoming apparent, unless trench SiC power MOSFETs with better economy and reliability are commercialized, the main

way to improve the performance of planar SiC power MOSFETs is to operate the devices at a higher gate oxide field to increase the channel electron density [18,19]. However, this places more stringent demands on the reliability of gate oxide in planar SiC power MOSFETs. One major area of concern is that the prediction of gate oxide lifetime under the typical operation, with an increased gate oxide field, still needs to meet conservative design requirements [20]. This requires not only improvements to the thermal growth process of gate oxide in planar SiC power MOSFETs, but also sufficient accuracy in the gate oxide lifetime prediction model [21]. The key to determining the accuracy of the prediction model is the failure mechanism of thermal gate oxide grown on SiC [22].

The commonly used gate oxide lifetime prediction method in the industry for planar SiC power MOSFETs is the time-dependent dielectric breakdown (TDDB) test. As MOSFETs are voltage-controlled devices, the conventional TDDB test in the industry is constant voltage stress TDDB (CVS-TDDB) based on the thermochemical E model, as it provides the most conservative lifetime extrapolation, even without physical or even experimental justification [23-25]. The thermochemical E model is considered to be based on the thermal gate oxide failure mechanism of field-driven breakdown [26]. P. Moens et al. questioned this mechanism and proposed a more rational failure mechanism of charge-driven breakdown [27]. The team grew approximately 53 nm of silicon dioxide (SiO<sub>2</sub>) on n-epi SiC to form circular capacitor structures with n+ doped polysilicon gates. By measuring the gate leakage current as a function of the gate oxide field at different temperatures, they concluded that the electron tunneling mechanism from SiC to SiO<sub>2</sub> transitions from thermally assisted tunneling (TAT) to Fowler-Nordheim tunneling (FNT) as the gate oxide field increases. During the transition, there is a phase where both the electron tunneling mechanisms jointly influence. This transition in the electron tunneling mechanism cannot be described in the conventional Weibull plots of CVS-TDDB based on field-driven breakdown but can be accurately depicted in new Weibull plots based on charge-driven breakdown, where the Weibull Slope  $(\beta)$  at the TAT dominant stage, FNT dominant stage, and the joint influence stage each have a specific value that decreases in the stage order of TAT dominance, joint influence, and FNT dominance. Therefore, the failure mechanism of thermal gate oxide grown on SiC is considered to be charge-driven breakdown rather than field-driven breakdown, and a more optimistic lifetime prediction model based on  $Q_{BD}$  has been proposed. Since the stressor is charge rather than field, constant current stress (CCS) is considered as a better stress method because it is not negatively affected by trapped electrons in the gate oxide and can reach  $Q_{BD}$  faster [28]. The  $\beta$  value of the Weibull plots based on the CCS- $Q_{BD}$  approach has also been proven to accurately describe the transition in the electron tunneling mechanism.

This work draws on the electron trapping model in very thin SiO<sub>2</sub> (no more than 10 nm) thermally grown on Si under CCS by M. Liang et al., proving its applicability also in approximately 4–5 times thicker SiO<sub>2</sub> thermally grown on SiC through CCS-TDDB tests on thermal gate oxide in a type of commercial planar SiC power MOSFETs until failure [29]. Based on this electron trapping model, a  $Q_{BD}$  model for thermal gate oxide in the commercial planar SiC power MOSFETs under test is established. Considering that the gate voltage signal for MOSFETs is a pulse-width-modulated (PWM) signal rather than a constant in actual applications, MOSFETs are voltage-controlled devices [30]. Therefore, in addition to conventional CVS, this paper also extracts the  $Q_{BD}$  of the thermal gate oxide in commercial planar SiC power MOSFETs under pulsed voltage stress (PVS) and CCS at different stress levels for comparison with the established  $Q_{BD}$  model. The high match between the extracted  $Q_{BD}$  and the  $Q_{BD}$  model indicates that different stress methods do not change the failure mechanism of thermal gate oxide, and the existence of a specific  $Q_{BD}$ that causes the thermal gate oxide to fail under different stress methods further proves that charge-driven breakdown is the failure mechanism of thermal gate oxide. Additionally, the lifetime prediction model established based on this failure mechanism can be considered more credible even if it is not as conservative as the thermochemical E model [31]. This will also provide a theoretical basis for suggesting the industry adopt more aggressive Materials **2024**, 17, 1455 3 of 15

screening methods to more effectively screen out extrinsic defects in thermal gate oxide according to the more optimistic lifetime prediction [32].

#### 2. Materials and Methods

#### 2.1. Devices under Test (DUTs)

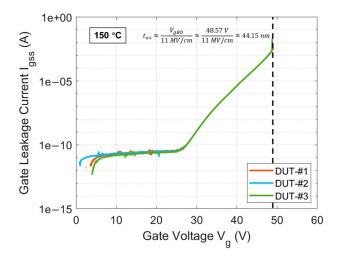

In this work, the devices under test (DUTs) are commercial 1200 V planar SiC power MOSFETs packaged in TO-247-3 from Vendor E. Considering that as more and more EV OEMs upgrade from 400 V systems to 800–900 V systems, the voltage rating of 1200 V will receive more attention from the market, so selecting this DUT is a better reference for the industry [33–37]. The curves of gate leakage current ( $I_{gss}$ ) for three DUTs at 150 °C, as a function of gate voltage  $(V_g)$ , are presented in Figure 1. The high overlap of the three curves demonstrates the high uniformity in gate oxide quality of the commercial DUTs. This indicates that these commercial DUTs undergo stringent gate oxide screening before leaving the factory, reducing the adverse impact of early oxide failure caused by extrinsic defects on subsequent test results [38]. The  $I_{gss}$  curves for all three DUTs exhibit breakdown near 50 V, with an average gate oxide breakdown voltage of about 48.57 V. Based on the assumption that the critical breakdown electric field is about 11 MV/cm for SiO<sub>2</sub>, the gate oxide thickness of DUTs can be estimated to be approximately 44.15 nm [39]. According to the total capacitance ( $C_{tot}$ ) derived from the gate C-V measurements of DUTs and  $C_{ox}$  of SiO<sub>2</sub>, the gate oxide area in each DUT is estimated to be about 0.9 mm<sup>2</sup>. General information of the commercial DUTs used in this work is summarized in Table 1.

**Figure 1.**  $I_{gss}$  curves as a function of  $V_g$  at 150 °C until oxide breakdown for three DUTs. The dashed line indicates the oxide breakdown voltage.

**Table 1.** General information of DUTs in this work.

| Vendor | Voltage<br>Rating (V) | Current<br>Rating (A) | Structure | Est. Oxide<br>Thickness (nm) | Est. Oxide<br>Area (mm²) |

|--------|-----------------------|-----------------------|-----------|------------------------------|--------------------------|

| E      | 1200                  | 11                    | Planar    | 44.15                        | 0.9                      |

## 2.2. Experimental Methods

## 2.2.1. Liang and Hu's Electron Trapping Model

A mathematical model for describing the electron trapping phenomenon in very thin  $SiO_2$  thermally grown on Si under CCS has been proposed by M. Liang and C. Hu [29]. In this model, M. Liang et al. have demonstrated that when the thickness of  $SiO_2$  in a polycrystalline- $Si-SiO_2$ -Si MOS capacitor structure reaches a certain level, the change in  $V_g$  ( $\Delta V_g$ ) between the polycrystalline-Si gate and the grounded Si measured under CCS tends to saturate at a high electron fluence (F). However, in the case of thinner  $SiO_2$ ,  $\Delta V_g$  does not show a saturation trend with F but instead tends to linearly increase until

Materials **2024**, 17, 1455 4 of 15

the oxide breakdown. This phenomenon is also observed under various CCS, and with different thicknesses of SiO<sub>2</sub>, as long as they do not exceed the critical oxide thickness. Therefore, for thinner SiO<sub>2</sub>, M. Liang et al. believe that in addition to the pre-existing electron traps in SiO<sub>2</sub>, new electron traps are being generated during CCS. The pre-existing electron traps and the generated electron traps, having different trap capture cross-sections and trap centroids, collectively capture electrons tunneling from Si into the oxide, thus affecting  $\Delta V_g$ . Based on this, a comprehensive mathematical model is established and used to characterize the electron trapping phenomenon in the 100 Å SiO<sub>2</sub> of a fabricated Si MOS capacitor structure.

In this model, the density of filled electron traps can be expressed as follows:

$$N_{ot}(\sigma_p, \sigma_g, F) = N_{opt}(\sigma_p, F) + N_{ogt}(\sigma_g, F) = N_{op}(\sigma_p) \left(1 - e^{-\sigma_p F}\right) + q \frac{g}{J} \left[F - \frac{1}{\sigma_g} (1 - e^{-\sigma_g F})\right]$$

(1)

where

$N_{ot}$ —density of filled electron traps;

$N_{op}/N_{opt}$ —density of pre-existing total/filled electron traps;

*N<sub>ogt</sub>*—density of filled generated electron traps;

$\sigma_p/\sigma_g$ —capture cross-section of pre-existing/generated electron traps;

*q*—electric charge of an electron;

*J*—current density of the specific CCS;

*F*—electron fluence ( $F = J \cdot t/q$ , t is the stress time under the specific CCS);

g—generation rate of generated electron traps under the specific CCS.

Therefore,  $\Delta V_g$  due to the filled electron traps can be expressed as follows:

$$\Delta V_g(F) = \frac{q}{\varepsilon_{ox}} \overline{x}(F) N_{ot}(\sigma_p, \sigma_g, F)$$

(2)

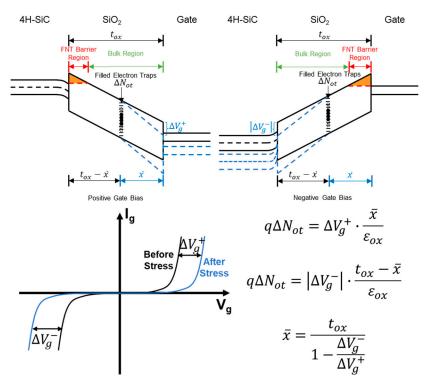

where  $\varepsilon_{ox}$  is the dielectric constant of SiO<sub>2</sub> and  $\overline{x}$  is the centroid of electron traps measured from the gate. Figure 2 presents a method for extracting  $\overline{x}$  with respect to F through shifts in  $I_g$ - $V_g$  curves at different stages under a specific CCS as shown below.

Also,  $\overline{x}$  can be represented by the centroid of pre-existing electron traps  $(\overline{x_p})$  and the centroid of generated electron traps  $(\overline{x_g})$  as follows:

$$\overline{x}(F) = \frac{\overline{x_p} N_{opt} + \overline{x_g} N_{ogt}}{N_{opt} + N_{ogt}}$$

(3)

When *F* is large enough under a specific CCS,  $\Delta V_g$  can be simplified to the following:

$$\Delta V_{g}(F) = \frac{q}{\varepsilon_{ox}} \left[ \overline{x_{p}} N_{op} - \overline{x_{g}} q \frac{g}{J} \frac{1}{\sigma_{g}} + \overline{x_{g}} q \frac{g}{J} F \right] = \frac{q}{\varepsilon_{ox}} \overline{x_{g}} q \frac{g}{J} \cdot F + \frac{q}{\varepsilon_{ox}} \left( \overline{x_{p}} N_{op} - \overline{x_{g}} q \frac{g}{J} \frac{1}{\sigma_{g}} \right)$$

(4)

Considering that  $\overline{x_p}N_{op}$  is a constant characteristic value regarding pre-existing electron traps and the generation rate of generated electron traps g under a specific CCS is also considered as a specific constant value in the model, Equation (4) can be regarded as a linear expression of  $\Delta V_g$  with respect to F when F is large enough. Moreover, differentiating Equation (4) can give the constant slope of this linear expression as follows:

$$\frac{d\Delta V_g}{dF} = \frac{q}{\varepsilon_{ox}} \overline{x_g} q \frac{g}{I} \tag{5}$$

From Equation (3), it is known that  $\bar{x}$  varies due to the ratio change between  $N_{opt}$  and  $N_{ogt}$  under different F. When F is large enough,  $N_{opt}$ , having tended to saturate earlier, becomes almost negligible relative to  $N_{ogt}$ , which continues to increase with the constant generation rate of new electron traps. In this case,  $\bar{x}$  tends to saturate, and the saturation value approached can be estimated as  $\bar{x}_g$ . In the model,  $\bar{x}_g$  is found to be a constant value,

Materials **2024**, 17, 1455 5 of 15

unaffected by CCS. This phenomenon is also reflected in the measurements of gate oxide in commercial SiC DUTs in this work.

**Figure 2.** Energy band variation caused by  $\Delta V_g$  to maintain a constant FNT barrier for a constant  $|I_{gss}|$ .  $\overline{x}$  can be extracted based on  $\Delta V_g$  at different stages under the constant  $|I_{gss}|$ .

## 2.2.2. Extraction of Charge-to-Breakdown ( $Q_{BD}$ )

$Q_{BD}$  measurement is a standard destructive method used to determine the quality of gate oxide in MOS devices.  $Q_{BD}$  is extracted by calculating the total charge passing through the dielectric (i.e., the product of total electron fluence and the electric charge of an electron, or the integral of electron current over time-to-breakdown ( $t_{BD}$ ), making it a time-dependent measurement [27]. The extraction of  $Q_{BD}$  can be represented as follows:

$$Q_{BD} = q \cdot F \cdot A_{ox} = \int_0^{t_{BD}} I(t)d(t)$$

(6)

#### 3. Results

3.1. Modeling of  $\Delta V_g$  When Breakdown Occurs ( $\Delta V_{gBD}$ ) in Commercial SiC DUTs

## 3.1.1. $\overline{x_g}$ Extraction

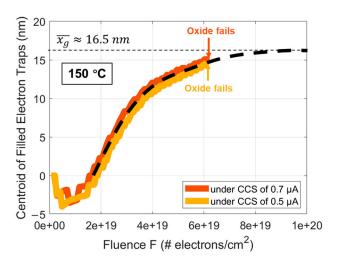

In Figure 3, based on the above method of extracting  $\overline{x}$ , the curves of  $\overline{x}$  versus F for the commercial SiC DUTs at 150 °C under a CCS of 0.5 and 0.7  $\mu$ A are shown. It is observable that the two curves highly coincide, consistent with what is measured in the oxide thermally grown on Si that there is no correlation with the CCS. However, due to the inferior quality of oxide thermally grown on SiC compared to Si, the oxide fails before F is large enough for  $\overline{x}$  to reach its saturation value [40]. Therefore, by fitting the overlapped curves of  $\overline{x}$  versus F, the  $\overline{x_g}$  of DUTs is estimated to be approximately 16.5 nm measured from the gate.

Materials **2024**, 17, 1455 6 of 15

**Figure 3.**  $\overline{x}$  curves as a function of *F* for DUTs at 150 °C under a CCS of 0.5 and 0.7  $\mu$ A, respectively, using the extraction method introduced in Figure 2.

#### 3.1.2. Mathematical Expression of $\Delta V_{gBD}$

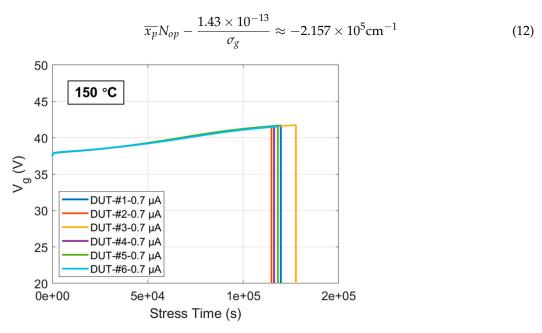

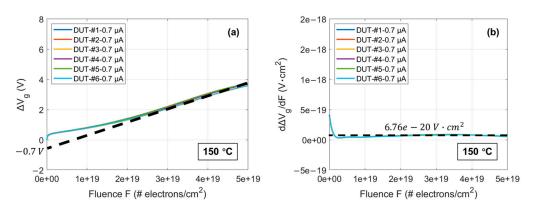

In Figure 4, the curves of  $V_g$  over stress time until the oxide breakdown at 150 °C for six DUTs under a CCS of 0.7  $\mu$ A are shown.  $\Delta V_g$  can be obtained by subtracting the initial  $V_g$  from  $V_g$  at different time points. Multiplying time by the known current density under CCS and dividing by the electric charge of an electron yields the electron fluence. Figure 5a presents the curves of  $\Delta V_g$  versus F until the oxide breakdown at 150 °C for the six DUTs under a CCS of 0.7 µA. Differentiating the curves in Figure 5a results in the curves shown in Figure 5b. The high consistency among the six curves in both again proves the uniformity of the oxide quality in these commercial SiC DUTs after a possible stringent gate oxide screening. According to Equation (4), the electron trapping phenomenon in the oxide of these commercial SiC DUTs shows characteristics similar to those predicted by the model for very thin oxide thermally grown on Si. By extending the linear part of the curves within the high F range in Figure 5a to intersect with the y-axis, the value of intersection point is estimated to be approximately -0.7 V. Additionally, the saturation value extracted in Figure 5b within the corresponding F range for the linear part of the curves in Figure 5a is about  $6.76 \times 10^{-20} \text{ V} \cdot \text{cm}^2$ . Therefore, the relevant mathematical expressions can be represented as follows:

$$\frac{q}{\varepsilon_{ox}} \left( \overline{x_p} N_{op} - \overline{x_g} q \frac{g}{J} \frac{1}{\sigma_g} \right) \approx -0.7 \text{ V}$$

(7)

$$\frac{q}{\varepsilon_{ox}} \overline{x_g} q \frac{g}{I} \approx 6.76 \times 10^{-20} \text{ V} \cdot \text{cm}^2$$

(8)

Since  $J \approx 0.7 \,\mu\text{A}/0.9 \,\text{mm}^2 \approx 7.8 \times 10^{-5} \,\text{A/cm}^2$  and  $\overline{x_g} \approx 16.5 \,\text{nm}$ , the above expressions can be transformed into the following:

$$g(0.7 \,\mu\text{A}) \approx 4.3 \times 10^7 \,\text{cm}^{-2} \cdot \text{s}^{-1}$$

(9)

$$\overline{x_p}N_{op} - \frac{1.46 \times 10^{-13}}{\sigma_g} \approx -1.51 \times 10^6 \text{cm}^{-1}$$

(10)

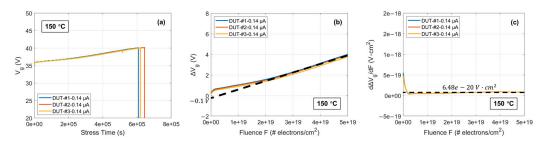

Similarly, Figure 6a displays the curves of  $V_g$  over stress time until the oxide breakdown for three DUTs under CCS of 0.14  $\mu$ A. Moreover, both the characteristics of  $\Delta V_g$  versus F for three DUTs under a CCS of 0.14  $\mu$ A shown in Figure 6b, and of the differentiated curves in Figure 6c, are very similar to those in Figure 5a,b. Therefore, by repeating the aforementioned method, similar relevant mathematical expressions can be obtained as

$$g(0.14 \,\mu\text{A}) \approx 8.47 \times 10^6 \,\text{cm}^{-2} \cdot \text{s}^{-1}$$

(11)

Materials **2024**, 17, 1455 7 of 15

**Figure 4.**  $V_g$  curves as a function of stress time until oxide breakdown at 150 °C for six DUTs under a CCS of 0.7  $\mu$ A.

**Figure 5.** (a)  $\Delta V_g$  curves as a function of *F* until oxide breakdown at 150 °C for the six DUTs under a CCS of 0.7  $\mu$ A; (b) Differentiated curves from (a). # is a number sign representing the number of electrons.

**Figure 6.** (a)  $V_g$  curves as a function of stress time until the oxide breakdown at 150 °C for three DUTs under CCS of 0.14  $\mu$ A; (b)  $\Delta V_g$  curves as a function of F until the oxide breakdown at 150 °C for the three DUTs under CCS of 0.14  $\mu$ A; (c) Differentiated curves from (b).

Considering that the DUTs stressed under a CCS of 0.7 and 0.14  $\mu$ A are from the same batch of identical devices produced on the same wafer using exactly the same process,  $\overline{x_p}N_{op}$  can be considered a constant value unaffected by CCS. Also, in the model, the generated electron traps under CCS have been proven to have a centroid always at a specific and constant position unaffected by CCS, with CCS mainly affecting their generation rate.

Materials **2024**, 17, 1455 8 of 15

Furthermore,  $\sigma_g$ , as a specific attribute of the generated electron traps, is also considered to be a constant value unaffected by CCS. Therefore, relating Equations (10) and (12) can give  $\overline{x_p}N_{op}$  and  $\sigma_g$  values of approximately  $6.2 \times 10^7$  cm<sup>-1</sup> and  $2.317 \times 10^{-21}$  cm<sup>2</sup>. Since the electron-fluence-to-breakdown ( $F_{BD}$ ) with respect to  $t_{BD}$  of the oxide can be expressed as  $F_{BD} = J \cdot t_{BD}/q$ , and with the CCS value  $I \approx 0.009 \cdot J$ , the mathematical relationship between  $\Delta V_{gBD}$  and I can be expressed as follows:

$$\Delta V_{gBD}(I) \approx 7.7 \times 10^{-13} \cdot g(I) \cdot t_{BD} - 4.68 \times 10^{-13} \cdot \frac{g(I)}{I} + 28.74 \text{ V}$$

(13)

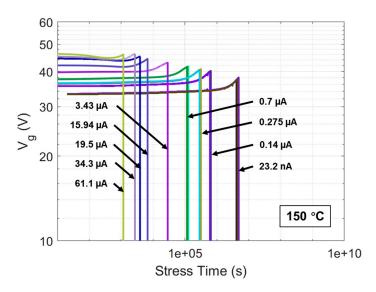

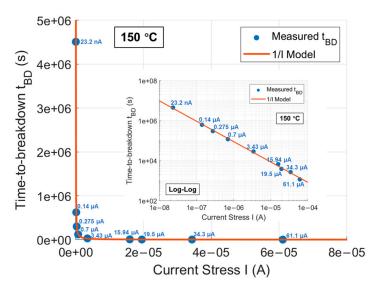

Figure 7 shows the curves of  $V_g$  over stress time until oxide breakdown for DUTs under all CCS scenarios used in this work. The applied CCS values include 23.2 nA, 0.14  $\mu$ A, 0.275  $\mu$ A, 0.7  $\mu$ A, 3.43  $\mu$ A, 15.94  $\mu$ A, 19.5  $\mu$ A, 34.3  $\mu$ A, and 61.1  $\mu$ A, corresponding to gate oxide electric fields of 7.5, 8, 8.2, 8.5, 9, 9.5, 9.6, 9.8, and 10 MV/cm, respectively, estimated by correlative  $V_g$  of CCS in Figure 1 divided by the oxide thickness. The  $t_{BD}$  of gate oxide in DUTs under each CCS can be extracted when the curves of  $V_g$  sharply drop and the average  $t_{BD}$  at 150 °C under each CCS are reflected in Figure 8. It can be observed that under CCS,  $t_{BD}$  follows a 1/I model, which can be expressed as follows:

$$t_{BD}(I) = A \cdot I^{-B} \tag{14}$$

where *A* and *B* are constant. For DUTs in this work, under CCS,  $t_{BD}(I)$  is fitted by the 1/I model as follows:

$$t_{BD}(I) = 0.071 \cdot I^{-1.017} \cdot s \tag{15}$$

Or in the log-log scale, Equation (14) can be transformed into the following:

$$\log(t_{BD}(I)) \approx -1.017 \cdot \log(I) - 1.1492$$

(16)

Which is in a linear relationship as shown in the inset of Figure 8.

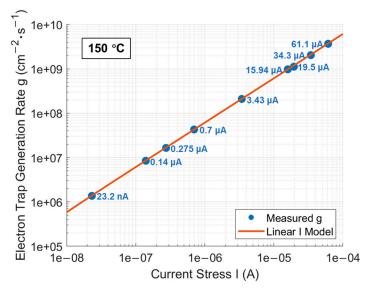

Using the method described earlier for extracting *g* of generated electron traps under a specific CCS, *g* under each CCS is extracted and is presented in Figure 9. It can be observed that *g* follows a linear *I* model. The mathematical expression for this linear *I* model is as follows:

$$g(I) \approx 6.13 \times 10^{13} \cdot I - 30324.35 \,\mathrm{cm}^{-2} \cdot \mathrm{s}^{-1}$$

(17)

**Figure 7.**  $V_g$  curves as a function of stress time until oxide breakdown at 150 °C for multiple DUTs under CCS values of 23.2 nA, 0.14 μA, 0.275 μA, 0.7 μA, 3.43 μA, 15.94 μA, 19.5 μA, 34.3 μA, and 61.1 μA, respectively.

Materials **2024**, 17, 1455 9 of 15

**Figure 8.** Average  $t_{BD}$  of gate oxide at 150 °C under each CCS for multiple DUTs fitted by a 1/*I* model. The inset shows the log–log scale with a linear relationship.

**Figure 9.** *g* extracted from the measured data at 150 °C under each CCS fitted by a linear *I* model.

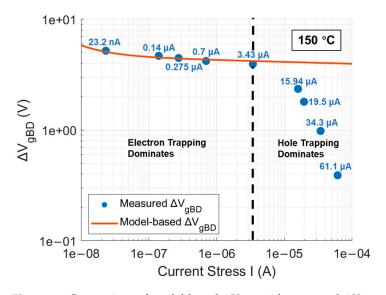

Therefore, the mathematical expression of  $\Delta V_{qBD}$  as a function of I can be summarized as the combination of Equations (13), (14), and (17). The curve of the mathematical expression is displayed in Figure 10 as model-based  $\Delta V_{gBD}$ . Additionally,  $\Delta V_{gBD}$  for DUTs under each CCS can be obtained from Figure 7 by subtracting the initial  $V_g$  from  $V_g$  at the point of gate oxide breakdown, which is also reflected in Figure 10. It is observed that the measured  $\Delta V_{gBD}$  under all CCS values not exceeding 3.43  $\mu$ A highly coincides with the curve of model-based  $\Delta V_{gBD}$  as a function of I. However, as CCS gradually exceeds 3.43  $\mu$ A, the measured  $\Delta V_{gBD}$  starts to fall below the model expectation. This discrepancy arises because, under CCS not exceeding 3.43 µA, the electron tunneling mechanism is predominantly thermally assisted tunneling (TAT), with the oxide's trapped charge mainly consisting of electrons, making the electron trapping model applicable in this range. The tunneling electrons lack sufficient energy to trigger enough impact ionization, thus preventing trapped holes induced by anode hole injection (AHI) from dominating over trapped electrons. In contrast, when CCS exceeds 3.43 µA, the electron tunneling mechanism shifts more toward Fowler-Nordheim tunneling (FNT). In this regime, the tunneling electrons possess enough energy at the beginning to cause significant impact ionization, leading to a

dominance of trapped holes in the oxide during the first stage of CCS, although trapped electrons subsequently regain dominance. Since the electron trapping model does not account for trapped holes and is solely based on trapped electrons, it is not applicable in the CCS range where trapped holes also play a role. This explanation is corroborated by the trends observed in Figure 7, where under CCS values up to 3.43  $\mu$ A, the  $V_g$  curves consistently show an increasing trend due to electron trapping in the oxide throughout the entire stress to breakdown. In contrast, under CCS values exceeding 3.43  $\mu$ A, the  $V_g$  curves initially show a decreasing trend due to hole trapping in the oxide, followed by a dominance of electron trapping leading to an increasing trend up to breakdown, and the initial decrease in the  $V_g$  curves becomes more pronounced as CCS increases beyond 3.43  $\mu$ A. In summary, it can be concluded that Liang and Hu's electron trapping model, established for very thin (no more than 10 nm) thermally grown SiO<sub>2</sub> on Si, is equally applicable to thicker (up to 45 nm in this work) SiO<sub>2</sub> thermally grown on SiC. This finding will aid in developing a  $Q_{BD}$  model for the commercial SiC DUTs.

**Figure 10.** Comparison of model-based  $\Delta V_{gBD}$  with measured  $\Delta V_{gBD}$  at 150 °C.

# 3.2. Modeling of $Q_{BD}$ in Commercial SiC DUTs

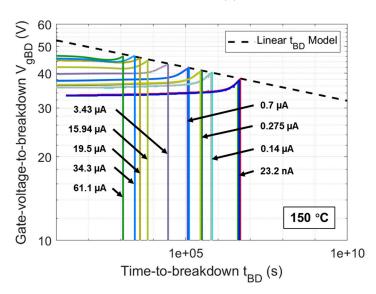

The  $V_g$  curves measured in Figure 11 show that the oxide breakdown points of the  $V_g$  curves under all CCS values follow a linear  $t_{BD}$  model on a log–log scale. The mathematical expression for this linear  $t_{BD}$  model can be represented as follows:

$$\log V_{gBD} = -0.0242 \cdot \log t_{BD} + 1.7448 \tag{18}$$

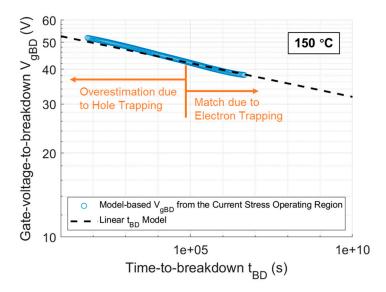

If the segment of the  $I_{gss}$  curves for DUTs in Figure 1, ranging from approximately 21 nA to 1.2 mA, is extracted as the current stress operating region, the corresponding  $V_g$  range is approximately 33 to 48 V. By adding  $\Delta V_{gBD}$ , extracted using its mathematical expression from the current stress operating region, to  $V_g$  corresponding to this region, the  $V_{gBD}$  from this region is obtained and then plotted on a log-log scale in Figure 12 for comparison with the linear  $t_{BD}$  model from Figure 11 represented by the black dashed line. It is observed that there is a distinct demarcation in the current stress operating region. To the left of this demarcation point, the extracted  $V_{gBD}$  is overestimated due to hole trapping, while to the right, the extracted  $V_{gBD}$  starts to perfectly match the linear relationship of  $V_{gBD}$  measured in DUTs. This strongly validates the feasibility of the mathematical expression for  $\Delta V_{gBD}$  established for the thermally grown gate oxide in commercial SiC DUTs in previous works. It also confirms that  $t_{BD}$  under CCS for DUTs, following a 1/I model, is correct and

theoretically founded. Therefore, based on Equations (6) and (15), the mathematical model for the  $Q_{BD}$  of gate oxide in DUTs under CCS can be established and expressed as follows:

$$Q_{BD}(I) = 0.071 \cdot I^{-0.017} \cdot C \tag{19}$$

**Figure 11.**  $V_{gBD}$  extracted from  $V_g$  curves at 150 °C fitted by a linear  $t_{BD}$  model.

**Figure 12.** Comparison of model-based  $V_{gBD}$  from the current stress operating region at 150 °C with the linear  $t_{BD}$  model.

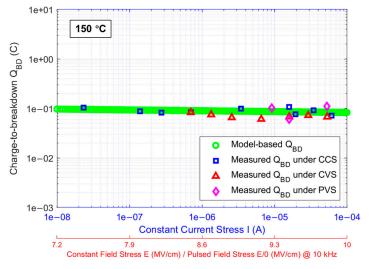

From Equation (19), it can be observed that the power exponent of 1/I is 0.017, which approaches zero, causing the power in the expression to be minimally influenced by I and tending toward 1. Consequently, this makes the  $Q_{BD}(I)$  for DUTs approach a constant value of 0.071 C, with the influence of I being almost negligible. This is consistent with the failure mechanism of charge-driven breakdown, theoretically supporting the notion that the failure mechanism of thermally grown SiO<sub>2</sub> on SiC under CCS is charge-driven breakdown.

#### 3.3. Extraction of $Q_{BD}$ in Commercial SiC DUTs under CVS and PVS

From Section 3.2, the  $Q_{BD}$  model for the gate oxide of DUTs in this work has been established. However, this model has limitations as it is based on the condition of CCS as the stress method for the gate oxide of DUTs. To prove the universality of the model and eliminate the limitations, it is necessary to expand the stress method for the gate oxide of

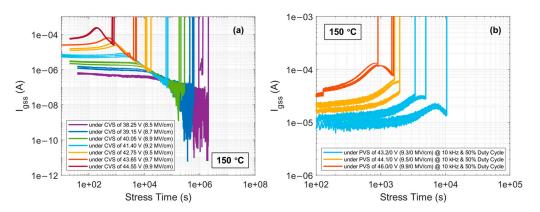

DUTs. CVS, a routine stress method used in the industry for the TDDB test of thermal oxide in commercial SiC power devices, is considered. Additionally, PVS, which more closely replicates the dynamic stress experienced by the thermal oxide in actual operations of commercial SiC power devices, is also taken into account. Figures 13a and 13b respectively show  $I_{gss}$  over stress time until the oxide breakdown at 150 °C for DUTs under various CVS and PVS, with different CVS and PVS scenarios also detailed in the figures. Following Equation (6),  $Q_{BD}$  values for DUTs under these two stress methods are extracted and presented in Figure 14. As for the  $Q_{BD}$  values for DUTs under CCS, they can be easily extracted through the product of constant I and  $t_{BD}$ , depicted in Figure 14 as well. For comparison, the mathematical-model-based  $Q_{BD}$  under CCS is also displayed in Figure 14.

**Figure 13.**  $I_{gss}$  curves as a function of stress time until the oxide breakdown at 150 °C for DUTs under various (a) CVS; (b) PVS.

**Figure 14.** Comparison of model-based  $Q_{BD}$  with measured  $Q_{BD}$  under CCS, CVS, and PVS at 150 °C.

## 4. Discussion

From Figure 14, it can be observed that at 150 °C, CVS and PVS correspond to each other through the electric field stress applied on the gate oxide of DUTs. According to the details in Figure 13 for CVS and PVS scenarios, the difference lies in that under CVS, the gate oxide of DUTs is subjected to a continuous electric field stress until the gate oxide breakdown, whereas under PVS, the same electric field stress applied to the gate oxide of DUTs is a pulsed stress with a frequency of 10 kHz and a duty cycle of 50% until the gate oxide breakdown. The electric field stress applied to the gate oxide is roughly estimated by the ratio of the positive voltage applied to the gate and the gate oxide thickness. Under CCS, the gates of DUTs are subjected to a continuous current stress towards the gate oxide until its breakdown, and CCS corresponds to the electric field stress on the gate oxide under

$V_g$  associated with the current stress in Figure 1, further corresponding to CVS and PVS. The  $Q_{BD}$  values of gate oxide in DUTs extracted under the three different stress methods are distributed in the figure according to the above correspondence and are compared with the model-based  $Q_{BD}$  extracted from the  $Q_{BD}$  model of thermal gate oxide in DUTs established under CCS. It is significantly observed that the  $Q_{BD}$  values of thermal gate oxide in DUTs extracted under the three stress methods conform to the model expectation. The slight differences in the extracted  $Q_{BD}$  data fall within the error margin caused by individual differences among the DUTs, which is acceptable and can be almost neglected.

#### 5. Conclusions

In this work, the mathematical model established for describing the electron trapping phenomenon in thermal oxide grown on Si, intended for very thin SiO<sub>2</sub>, is considered for transplantation to the gate oxide of commercial SiC power MOSFETs, which is thermally grown on SiC. Given that the mathematical model was initially proven to be applicable only for SiO<sub>2</sub> grown on Si with a thickness not exceeding 10 nm, its applicability to SiO<sub>2</sub> thermally grown on SiC, which is approximately 4–5 times thicker in commercial SiC power MOSFETs, is worth discussing. Based on the CCS-TDDB data of the commercial SiC DUTs featuring approximately 45 nm thick sections of thermal gate oxide, the feasibility of this electron trapping model, under conditions where the oxide charge trapping mechanism is predominantly governed by electron trapping, is confirmed in the commercial SiC cases. Following this model, a  $Q_{RD}$  model for the thermal gate oxide of commercial SiC DUTs under CCS is established in this work. Apart from the CCS-TDDB test, the CVS-TDDB and PVS-TDDB tests are also conducted on these DUTs. The  $Q_{BD}$  values of thermal gate oxide in DUTs are extracted from the TDDB data under the three different stress methods through the integral of  $I_{gss}$  over stress time, and are compared with the established  $Q_{BD}$  model. The results demonstrate that the measured  $Q_{BD}$  values align with the model expectation, indicating that  $Q_{BD}$ , as a characteristic value of the quality of thermal oxide grown on SiC, remains stable and unaffected by the stressors. This is consistent with and confirms the expectation that the failure mechanism of thermal oxide grown on SiC is charge-driven breakdown. This provides a solid theoretical foundation for establishing a new, more accurate lifetime prediction model based on  $Q_{BD}$  for commercial SiC power MOSFETs with thermal gate oxide. Additionally, since  $Q_{BD}$  is not affected by the stressors and considering the reduced efficiency in extracting  $Q_{BD}$  due to the suppression effect of trapped electrons on Igss under CVS, CCS is recommended as a faster and more accurate method for extracting  $Q_{BD}$  in the industry, compared with the conventional CVS, for establishing lifetime prediction models based on  $Q_{BD}$  for SiC power MOSFETs with thermal gate oxide.

**Author Contributions:** Conceptualization, J.Q., M.H.W. and A.K.A.; methodology, J.Q. and M.J.; software, J.Q. and L.S.; validation, J.Q., L.S., M.J. and M.B.; formal analysis, J.Q., L.S., M.J., M.B., A.S., H.Y., S.H., M.H.W. and A.K.A.; investigation, J.Q., L.S., M.J., M.B. and H.Y.; resources, J.Q.; data curation, J.Q. and L.S.; writing—original draft preparation, J.Q.; writing—review and editing, J.Q., A.S. and A.K.A.; visualization, J.Q.; supervision, A.K.A.; project administration, A.S.; funding acquisition, A.S. All authors have read and agreed to the published version of the manuscript.

Funding: This research was funded by Ford Auto Co., grant number GR123387.

**Institutional Review Board Statement:** Not applicable.

Informed Consent Statement: Not applicable.

Data Availability Statement: Data are contained within the article.

**Acknowledgments:** This research is supported under the Ford-OSU Alliance Project-Phase II to The Ohio State University. The authors would like to thank the team members from Ford Motor Co. under the project for the helpful discussion.

Conflicts of Interest: Author Atsushi Shimbori was employed by the company Ford Motor Co. The remaining authors declare that the research was conducted in the absence of any commercial or financial relationships that could be construed as potential conflicts of interest. The authors declare that this study received funding from Ford Auto Co. The funders had no role in the design of the study; in the collection, analyses, or interpretation of data; in the writing of the manuscript; or in the decision to publish the results.

#### References

- 1. Choi, H. Overview of Silicon Carbide Power Devices; Fairchild Semiconductor: Sunnyvale, CA, USA, 2016.

- 2. FastSiC. SiC Is Replacing Si in Electric Vehicles. Available online: https://fastsic.com/2020/06/24/sic-is-replacing-si-in-electric-vehicles/ (accessed on 1 June 2020).

- 3. Emilio, M. SiC enabling EV applications. Available online: https://www.powerelectronicsnews.com/sic-enabling-ev-applications/ (accessed on 12 April 2019).

- 4. Russell, S.; Gammon, P. ROHM Gen 4: A Technical Review. Available online: https://www.techinsights.com/blog/rohm-gen-4-technical-review (accessed on 2 August 2022).

- 5. Telford, M. SiC Making Further Inroads into Silicon for EV Powertrains. *SemiconductorTODAY* **2023**, *18*. Available online: https://www.semiconductor-today.com/news\_items/backissues/semiconductor-today-april-2023.pdf (accessed on 17 April 2023).

- 6. Li, H.F.; Dimitrijev, S.; Harrison, H.B.; Sweatman, D. Interfacial characteristics of N<sub>2</sub>O and NO nitrided SiO<sub>2</sub> grown on SiC by rapid thermal processing. *Appl. Phys. Lett.* **1997**, 70, 2028–2030. [CrossRef]

- 7. Li, H.; Dimitrijev, S.; Harrison, H.B. Improved reliability of NO-nitrided SiO<sub>2</sub> grown on p-type 4H-SiC. *IEEE Electron Device Lett.* **1998**, *19*, 279–281.

- 8. Fukuda, K.; Suzuki, S.; Tanaka, T.; Arai, K. Reduction of interface-state density in 4H–SiC n-type metal–oxide–semiconductor structures using high-temperature hydrogen annealing. *Appl. Phys. Lett.* **2000**, *76*, 1585–1587. [CrossRef]

- 9. Chung, G.Y.; Tin, C.C.; Williams, J.R.; McDonald, K.; Di Ventra, M.; Pantelides, S.T.; Feldman, L.C.; Weller, R.A. Effect of nitric oxide annealing on the interface trap densities near the band edges in the 4H polytype of silicon carbide. *Appl. Phys. Lett.* **2000**, 76, 1713–1715. [CrossRef]

- 10. Itoh, H.; Enokizono, T.; Miyase, T.; Hori, T.; Wada, K.; Furumai, M. High-Quality SiC Epitaxial Wafer "EpiEra" Realizing High-Reliability Large-Current Power Devices. *Sumitomo Electr.* **2020**, *91*, 47–50.

- 11. Zhao, Z.; Li, Y.; Xia, X.; Wang, Y.; Zhou, P.; Li, Z. Growth of high-quality 4H-SiC epitaxial layers on 4° off-axis C-face 4H-SiC substrates. *J. Cryst. Growth* **2020**, *531*, 125355. [CrossRef]

- 12. Kim, J.; Kim, K. 4H-SiC Double-Trench MOSFET with Side Wall Heterojunction Diode for Enhanced Reverse Recovery Performance. *Energies* **2020**, *13*, 4602. [CrossRef]

- 13. Chaturvedi, M.; Dimitrijev, S.; Haasmann, D.; Moghadam, H.A.; Pande, P.; Jadli, U. Comparison of Commercial Planar and Trench SiC MOSFETs by Electrical Characterization of Performance-Degrading Near-Interface Traps. *IEEE Trans. Electron Devices* **2022**, *69*, 6225–6230. [CrossRef]

- 14. Seok, O.; Kang, I.; Moon, J.; Kim, H.; Ha, M.; Bahng, W. Double p-base structure for 1.2-kV SiC trench MOSFETs with the suppression of electric-field crowding at gate oxide. *Microelectron. Eng.* **2020**, 225, 111280. [CrossRef]

- 15. Park, Y.; Yoon, H.; Kim, C.; Kim, G.; Kang, G.; Seok, O.; Ha, M. Design and Optimization of 1.2 kV SiC Trench MOSFETs Using a Tilted Ion Implantation Process for High Breakdown Voltage. *Jpn. J. Appl. Phys.* **2023**, *62*, 011001. [CrossRef]

- 16. Stahlbush, R.; Mahakik, K.; Lelis, A.; Green, R. Effects of Basal Plane Dislocations on SiC Power Device Reliability. In Proceedings of the 2018 IEEE 64th International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 1–5 December 2018.

- 17. Qian, J.; Shi, L.; Jin, M.; Bhattacharya, M.; Shimbori, A.; Yu, H.; Houshmand, S.; White, M.H.; Agarwal, A.K. An Investigation of Body Diode Reliability in Commercial 1.2 kV SiC Power MOSFETs with Planar and Trench Structures. *Micromachines* **2024**, *15*, 177. [CrossRef] [PubMed]

- 18. Roccaforte, F.; Greco, G.; Fiorenza, P. Processing Issues in SiC and GaN Power Devices Technology: The Cases of 4H-SiC Planar MOSFET and Recessed Hybrid GaN MISHEMT. In Proceedings of the 2018 International Semiconductor Conference (CAS), Sinaia, Romania, 10–12 October 2018.

- 19. Yao, J. Working principle and characteristic analysis of SiC MOSFET. J. Phys. Conf. Ser. 2023, 2435, 012022. [CrossRef]

- 20. Keukeleire, C. Silicon Carbide (SiC)—From Challenging Material to Robust Reliability. Available online: https://www.onsemi.com/pub/collateral/tnd6396-d.pdf (accessed on 10 December 2022).

- 21. Ni, Z.; Lyu, X.; Yadav, O.; Singh, B.; Zheng, S.; Cao, D. Overview of Real-Time Lifetime Prediction and Extension for SiC Power Converters. *IEEE Trans. Power Electron.* **2020**, *35*, 7765–7794. [CrossRef]

- Ikpe, S.; Lauenstein, J.; Carr, G.; Hunter, D.; Ludwig, L.; Wood, W.; Castillo, L.; Fitzpatrick, F.; Chen, Y. Silicon-Carbide Power MOSFET Performance in High Efficiency Boost Power Processing Unit for Extreme Environments. *Addit. Pap. Present.* 2016, 2016, 184–189. [CrossRef]

- 23. Liu, T.; Zhu, S.; White, M.H.; Salemi, A.; Sheridan, D.; Agarwal, A.K. Time-Dependent Dielectric Breakdown of Commercial 1.2 kV 4H-SiC Power MOSFETs. *J. Electron Devices Soc.* **2021**, *9*, 633–639. [CrossRef]

24. McPherson, J.W.; Mogul, H.C. Underlying Physics of the Thermochemical E Model in Describing Low-field Time-dependent Dielectric Breakdown in SiO<sub>2</sub> Thin Films. *J. Appl. Phys.* **1998**, *84*, 1513–1523. [CrossRef]

- 25. Liu, T. Gate Oxide Reliability of 4H-SiC MOSFETs. Level of Thesis, The Ohio State University, Columbus, OH, USA, 11 April 2022.

- 26. Ghetti, A. Gate Oxide Reliability: Physical and Computational Models. Available online: https://link.springer.com/chapter/10.1 007/978-3-662-09432-7\_6 (accessed on 8 May 2004).

- Moens, P.; Franchi, J.; Lettens, J.; Schepper, L.D.; Domeij, M.; Allerstam, F. A Charge-to-Breakdown (QBD) Approach to SiC Gate Oxide Lifetime Extraction and Modeling. In Proceedings of the 2020 32nd International Symposium on Power Semiconductor Devices and ICs (ISPSD), Vienna, Austria, 13–18 September 2020.

- Tan, W.; Zhao, L.; Lu, C.; Nie, W.; Gu, X. An In-depth Investigation of Gate Leakage Current Degradation Mechanisms in 1.2kV 4H-SiC Power MOSFETs. Microelectron. Reliab. 2023, 142, 114907. [CrossRef]

- 29. Liang, M.; Hu, C. Electron trapping in very thin thermal silicon dioxides. In Proceedings of the 1981 International Electron Devices Meeting (IEDM), Washington, DC, USA, 7–9 December 1981.

- 30. Wang, H.; Jiang, D. Design of High Temperature Gate Driver for SiC MOSFET for EV Motor Drives. In Proceedings of the 2017 IEEE Transportation Electrification Conference and Expo, Asia-Pacific (ITEC Asia-Pacific), Harbin, China, 7–10 August 2017.

- 31. Zhu, S.; Liu, T.; Shi, L.; Jin, M.; Maddi, H.; White, M.H.; Agarwal, A.K. Comparison of Gate Oxide Lifetime Predictions with Charge-to-Breakdown Approach and Constant-Voltage TDDB on SiC Power MOSFET. In Proceedings of the 2021 IEEE 8th Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Redondo Beach, CA, USA, 7–11 November 2021.

- 32. Shi, L.; Zhu, S.; Qian, J.; Jin, M.; Bhattacharya, M.; Shimbori, A.; Liu, T.; White, M.H.; Agarwal, A.K. Investigation of different screening methods on threshold voltage and gate oxide lifetime of SiC Power MOSFETs. In Proceedings of the 2023 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 26–30 March 2023.

- 33. Sarnago, H.; Lucía, Ó.; Jiménez, R.; Gaona, P. Differential-Power-Processing On-Board-Charger for 400/800-V Battery Architectures using 650-V Super Junction MOSFETs. In Proceedings of the 2021 IEEE Applied Power Electronics Conference and Exposition (APEC), Phoenix, AZ, USA, 14–17 June 2021.

- 34. Kegley, L. Exploring On-Board EV Systems from 400 V to 800 V. Available online: https://www.powerelectronicsnews.com/exploring-on-board-ev-systems-from-400-v-to-800-v/ (accessed on 17 April 2023).

- 35. Jung, C. Power Up with 800-V Systems: The benefits of upgrading voltage power for battery-electric passenger vehicles. *IEEE Electrif. Mag.* **2017**, *5*, 53–58. [CrossRef]

- 36. Hussey, A. Lucid Air to be the Fastest Charging EV, Featuring a 900V+ Architecture Delivering a Charging Rate of Up to 20 Miles Per Minute. Available online: https://lucidmotors.com/media-room/lucid-air-fastest-charging-ev (accessed on 19 August 2020).

- 37. Goldberg, L. Exploiting SiC MOSFETs to Power EV Innovation. Available online: https://www.electronicdesign.com/markets/automotive/article/21262547/electronic-design-exploiting-sic-mosfets-to-power-ev-innovation (accessed on 23 March 2023).

- 38. Shi, L.; Qian, J.; Jin, M.; Bhattacharya, M.; Yu, H.; White, M.H.; Agarwal, A.K.; Shimbori, A.; Xu, Z. An Effective Screening Technique for Early Oxide Failure in SiC Power MOSFETs. In Proceedings of the 2023 IEEE 10th Workshop on Wide Bandgap Power Devices & Applications (WiPDA), Charlotte, NC, USA, 4–6 December 2023.

- 39. Koga, Y.; Kurita, K. Fabrication of Silicon on Insulator Wafer with Silicon Carbide Insulator Layer by Surface-activated Bonding at Room Temperature. *Jpn. J. Appl. Phys.* **2020**, *59*, 051002. [CrossRef]

- 40. Pu, S. Reliability Assessment, Condition Monitoring and Lifetime Estimation of Silicon Carbide MOSFETs. Ph.D. Thesis, The University of Texas at Dallas, TX, USA, 20 July 2021.

**Disclaimer/Publisher's Note:** The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content.