# Article An S–K Band 6-Bit Digital Step Attenuator with Ultra Low Insertion Loss and RMS Amplitude Error in 0.25 μm GaAs p-HEMT Technology

Quanzhen Liang <sup>1,2,3</sup>, Kuisong Wang <sup>1,3</sup>, Xiao Wang <sup>1,3</sup>, Yuepeng Yan <sup>1,3</sup> and Xiaoxin Liang <sup>1,3,\*</sup>

- <sup>1</sup> Communication Center, Institute of Microelectronics of the Chinese Academy of Sciences, Beijing 100029, China; liangquanzhen@ime.ac.cn (Q.L.); wangkuisong@ime.ac.cn (K.W.); wangxiao@ime.ac.cn (X.W.); yanyuepeng@ime.ac.cn (Y.Y.)

- <sup>2</sup> University of Chinese Academy of Sciences, Beijing 101408, China

- <sup>3</sup> Beijing Key Laboratory of New Generation Communication RF Technology, Beijing 100029, China

- \* Correspondence: liangxiaoxin@ime.ac.cn; Tel.: +86-198-0031-9190

# Featured Application: The DSA proposed in this paper is well suited for wideband phasedarray systems.

**Abstract:** This paper presents an ultra-wideband, low insertion loss, and high accuracy 6-bit digital step attenuator (DSA). To improve the accuracy of amplitude and phase shift of the attenuator, two innovative compensation structures are proposed in this paper: a series inductive compensation structure (SICS) designed to compensate for high frequency attenuation values and a small bit compensation structure (SBCS) intended for large attenuation bits. Additionally, we propose insertion loss reduction techniques (ILRTs) to reduce insertion loss. The fabricated 6-bit DSA core area is only 0.51 mm<sup>2</sup>, and it exhibits an attenuation range of 31.5 dB in 0.5 dB steps. Measurements reveal that the root-mean-square (RMS) attenuation and phase errors for the 64 attenuation states are within 0.18 dB and 7°, respectively. The insertion loss is better than 2.54 dB; the return loss is better than -17 dB; and the input 1 dB compression point (IP1 dB) is 29 dBm at IF 12 GHz. To the best of our knowledge, this chip presents the highest attenuation accuracy, the lowest insertion loss, the best IP1dB, and a good matching performance in the range of 2–22 GHz using the 0.25  $\mu$ m GaAs p-HEMT process.

**Keywords:** digital step attenuator; GaAs; insertion loss reduction technique; series inductive compensation structure; small bit compensation structure

# 1. Introduction

Attenuators serve as a crucial component in RF communication, radar, and measurement systems. Their primary function is to provide amplitude control, including linearity adjustment and damage protection [1,2]. The phased array system, with its high precision beam pointing, fast beam synthesis, and scanning capability, is widely used in modern RFintegrated systems such as radar remote sensing and low orbit broadband satellite communications. In phased-array systems, attenuators are required for high accurate amplitude control to obtain lower side lobe levels, better null points, and higher beam sharpness. Digital step attenuators (DSAs) show superior switching speed, reduced power consumption, enhanced linearity, minimal current variation, precise amplitude control, and diminished amplitude/phase change characteristics when compared to variable gain amplifiers. Furthermore, digital attenuators demonstrate higher attenuation accuracy, an improved voltage standing wave ratio, and a broader attenuation dynamic range when compared to continuous variable attenuators [3–6].

**Citation:** Liang, Q.; Wang, K.; Wang, X.; Yan, Y.; Liang, X. An S–K Band 6-Bit Digital Step Attenuator with Ultra Low Insertion Loss and RMS Amplitude Error in 0.25 µm GaAs p-HEMT Technology. *Appl. Sci.* **2024**, 14, 3887. https://doi.org/10.3390/ app14093887

Academic Editor: Alessandro Lo Schiavo

Received: 29 March 2024 Revised: 26 April 2024 Accepted: 29 April 2024 Published: 1 May 2024

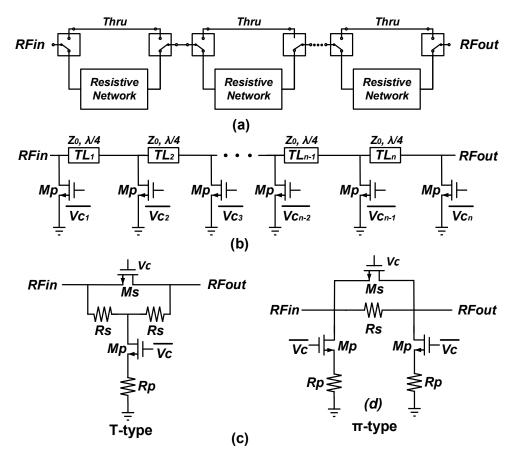

**Copyright:** © 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https:// creativecommons.org/licenses/by/ 4.0/). In passive DSAs, three primary topologies have been investigated in the literature: distributed, switched path, and switched T-/ $\pi$ -type attenuators [7–13], where, TL is a  $\lambda/4$  microstrip line, Ms is a series transistor, Mp is a parallel transistor, Rs is a series branch resistor, Rp is a parallel branch resistor, and Vc and Vc are a pair of complementary voltages for controlling the on and off of the transistor.

Switched path attenuators use single-pole-double-throw (SPDT) switches to steer the signal path between a thru line and a resistive network, as shown in Figure 1a. This topology provides low phase variation over attenuation states, but it shows high insertion losses at reference states due to the cumulative losses of all SPDT switches for a multi-bit design, and it occupies a large chip area [7,8].

**Figure 1.** Topologies of DSAs. (a) Switched path attenuator. (b) Distributed attenuator. (c) Switched  $T/\pi$  attenuators.

Distributed attenuators do not have series switches in the signal path and therefore have the advantage of low insertion loss, as shown in Figure 1b. However, they show lower maximum attenuation values and larger chip sizes [9,10].

Switched T-/ $\pi$ -type attenuators show low IL, high maximum attenuation, and compact size, as shown in Figure 1c. However, they still show relatively large attenuation variation and phase variation at higher frequencies, which can limit fine amplitude control in broadband applications [11–13].

The primary source of errors in the amplitude and phase of switched  $T/\pi$  attenuators is attributed to the parasitic capacitance (Coff) of switching transistors [14]. In order to minimize the Coff-induced errors and improve the accuracy of the attenuator amplitude and phase, several compensation structures have been proposed recently. References [15,16] introduced a parallel capacitive compensation structure that transforms the attenuator into a two-pole, two-zero system, significantly reducing phase error. However, the insertion loss of this structure rapidly deteriorates with frequency increase. At 6 GHz, the insertion loss

reaches 2.3 dB and 4 dB, respectively. Consequently, this structure is unsuitable for ultrawideband attenuators. Adding a tail capacitor in the shunt branch was reported in [17], but this series capacitor limits the bandwidth, counteracting the benefits of the switched-type topology. The inductive compensation structure shows a lower insertion loss compared to the capacitive compensation structure. A parallel inductive compensation structure was introduced by reference [18]. However, the inductor is parallel to the resistance network, resulting in a smaller attenuation value. To address this issue, additional series resistance needs to be incorporated, thereby increasing circuit complexity. Furthermore, as frequency increases, the impact of the phase lag in the parallel inductive compensation structure gradually diminishes. Therefore, this structure is only suitable for low-frequency applications. Consequently, the challenge arises with increasing bandwidth to maintain high linearity, low insertion loss, compact area, and minimal amplitude and phase error concurrently.

In this paper, we propose two innovative compensation structures: a series inductive compensation structure (SICS) designed to compensate for high frequency attenuation values and a small bit compensation structure (SBCS) for large attenuation bits. Additionally, this study adopts a simplified T-type structure and low-pass compensation structure, which not only reduces the insertion loss but also greatly improves the matching performance. Building upon the aforementioned innovations, the proposed 6-bit DSA shows ultra-low insertion loss, excellent attenuation accuracy, high power capacity, and commendable matching performance.

This paper is structured as follows:

In Section 2, we give an in-depth analysis of the conventional switch T-/ $\pi$  structure, deriving optimal resistance values for each attenuation topology to avoid undesired impedance mismatch.

In Section 3, we explain the limitations of conventional digital attenuator design.

In Section 4, we propose a series inductive compensation structure and a small bit compensation structure to effectively extend the operating bandwidth of the attenuator and reduce the additional phase shift.

In Section 5, we propose two methods to reduce the insertion loss, which reduce the insertion loss by 50%.

In Section 6, we cascade the six attenuation bits to maximize performance over the entire bandwidth (from 2 GHz to 22 GHz).

In Section 7, we present the measurement results of the chip and compare with other recently published broadband digital attenuators. The measurement results show that the DSA proposed in this paper can achieve ultra-wideband operation from 2 GHz to 22 GHz with high amplitude tuning accuracy (i.e., <0.18 dB RMS amplitude error) and low phase error (i.e., <7° RMS phase error). Therefore, the proposed DSA can meet the requirements of multi-band phased array systems.

# 2. Design Method of Conventional Switched Type Attenuators

Conventional attenuators of the switched type typically show three prevalent topologies: T-type [19–25], simplified T-type [4–6,26,27], and  $\pi$ -type [24–31] structures. Each topology is capable of functioning in two distinct states: reference state and attenuation state. The disparity in loss between these two states constitutes the relative attenuation. Given that these three topologies display varying attenuation characteristics, their selection necessitates careful consideration to design specific attenuation bits. Although the resistances of the three topologies can be found in [6,32], calculations ignoring transistor losses are inaccurate for switching attenuators. In this section, we derive the optimal attenuation resistance values considering transistor losses.

# 2.1. Conventional T-Type Attenuator

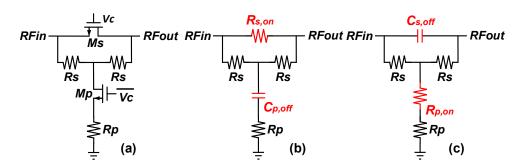

Figure 2 shows the conventional T-type attenuation structure and its equivalent circuits.

**Figure 2.** (a) Schematic diagram of the conventional T-type attenuation structure and its equivalent circuits. (b) Reference state. (c) Attenuation state.

In the reference state, transistor Ms is on, and transistor Mp is off. The insertion loss is determined by the on-resistance of transistor Ms and the series resistance Rs. Consequently, the corresponding transmission S-parameter can be expressed as follows:

$$S_{21,REF-T} = 1 - \frac{R_s R_{s,on}}{(2R_s + R_{s,on})Z_0 + R_s R_{s,on}}$$

(1)

where *Rs,on* represents the on-resistance of the transistor *Ms*, and *Z*0 is the characteristic impedance.

In the attenuation state, transistor *Ms* is off, and transistor *Mp* is on; the insertion loss is determined by the T-type attenuation network and the on-resistance of transistor *Mp*. Consequently, the corresponding transmission S-parameter can be expressed as follows:

$$S_{21,ATT-T} = \frac{2Z_0(R_p + R_{p,on})}{2(Z_0 + R_s)(R_p + R_{p,on}) + 2Z_0R_s + Z_0^2 + {R_s}^2}$$

(2)

where *Rp,on* represents the on-resistance of the transistor *Mp*.

The relative attenuation  $\Delta S21$  can be expressed as follows:

$$\Delta S_{21} = \frac{S_{21,REF-T}}{S_{21,ATT-T}}$$

(3)

Furthermore, it is imperative that the *S*11 of both the reference state and attenuation state be as minimal as possible to ensure impedance matching. Notably, the transistor *Ms*, typically larger in size, is designed to minimize insertion loss. Consequently, this results in a superior impedance matching of the reference state. The *S*11 of attenuation state can be expressed as follows:

$$S_{11,ATT-T} = \frac{2R_s(R_p + R_{p,on}) + R_s^2 - Z_0^2}{2Z_0(R_p + R_{p,on}) + 2Z_0R_s + 2R_s(R_p + R_{p,on}) + R_s^2 + Z_0^2}$$

(4)

When the value of  $S_{11,ATT-T} = 0$ , it allows for the computation of the following:

$$R_s = \frac{Z_0(1 - S_{21,ATT-T})}{(1 + S_{21,ATT-T})}$$

(5)

$$R_p = \frac{2Z_0 S_{21,ATT-T}}{(1 - S_{21,ATT-T}^2)} - R_{p,on}$$

(6)

Based on (1), (3), (5), and (6), we can calculate *Rs* and *Rp* under the optimal impedance matching condition.

# 2.2. Simplified T-Type Attenuator

When the value of attenuation is small, the resistance of the series resistor Rs in the T-type structure is also small. Taking the 0.5 dB attenuation bit as an example, we find that the resistance of the series resistor Rs in the T-type structure is only 1.34  $\Omega$ , which means that the microstrip line can be used to replace the series resistor Rs.

Figure 3 shows the simplified T-type structure and its equivalent circuits. In this configuration, *Cp,off* represents the equivalent capacitance of the parallel transistor in its off state, while *Rp,on* denotes the on resistance during the parallel transistor's on state. The simplified T-type design eliminates both the series resistor *Rs* and the series transistor *Ms* found in conventional T-type structure. This allows for targeted attenuation by solely adjusting *Rp* and *Mp* [26,27]. Notably, this architecture boasts reduced insertion loss and a compact layout area.

**Figure 3.** (a) Schematic diagram of the simplified T-type attenuation structure and its equivalent circuits. (b) Reference state. (c) Attenuation state.

In the reference state, the transistor Mp is turned off, and the signal to ground shows a high resistance state; at this time, the insertion loss tends to be close to zero. Conversely, in the attenuation state, the transistor Mp is on, and the signal leaks to the ground to achieve the attenuation. The resistance value of Rp can still be obtained by (6).

# 2.3. Conventional $\pi$ -Type Attenuator

As can be seen from (4), as attenuation increases, Rp diminishes, and the return loss of the T-type structure deteriorates. Notably, when the attenuation reaches 8 dB, there is a marked deterioration in the return loss, indicating that the T-type structure is not suitable for large attenuation bits. In contrast, the  $\pi$ -type structure shows greater suitability for large attenuation bits. Figure 4 shows the conventional  $\pi$ -type structure and its equivalent circuits.

**Figure 4.** (a) Schematic diagram of the  $\pi$ -type attenuation structure and its equivalent circuits. (b) Reference state. (c) Attenuation state.

In the reference state, transistor *Ms* is on, and transistor *Mp* is off. The insertion loss is determined by the on-resistance of transistor *Ms* and the series resistance *Rs*. Consequently, the corresponding transmission *S*-parameter can be expressed as follows:

$$S_{21,REF-\pi} = 1 - \frac{R_s R_{s,on}}{2(R_s + R_{s,on})Z_0 + R_s R_{s,on}}$$

(7)

In the attenuation state, transistor *Ms* is off, and transistor *Mp* is on; the insertion loss is determined by the T-type attenuation network and the on-resistance of transistor *Mp*. Consequently, the corresponding transmission *S*-parameter can be expressed as follows:

$$S_{21,ATT-\pi} = \frac{2Z_0(R_p + R_{p,on})^2}{(2Z_0 + R_s)(R_p + R_{p,on})^2 + (2R_p + 2R_{p,on} + R_s)Z_0^2}$$

(8)

The relative attenuation  $\Delta S21$  can be expressed as follows:

$$\Delta S_{21} = \frac{S_{21,REF-\pi}}{S_{21,ATT-\pi}}$$

(9)

The S11 of attenuation state can be expressed as follows:

$$S_{11,ATT-\pi} = \frac{R_s (R_p + R_{p,on})^2 - Z_0^2 (2R_p + 2R_{p,on} + R_s)}{(R_s + 2Z_0)(R_p + R_{p,on})^2 + 2Z_0 (R_s + Z_0)(R_p + R_{p,on}) + R_s Z_0^2}$$

(10)

Similarly, when the value of S11,ATT- $\pi = 0$ , it allows for the computation of the following.

The relative attenuation  $\Delta S21$  can be expressed as follows:

$$R_s = \frac{Z_0 (1 - S_{21,ATT - \pi}^2)}{2S_{21,ATT - \pi}}$$

(11)

$$R_p = \frac{Z_0(1 + S_{21,ATT-\pi})}{(1 - S_{21,ATT-\pi})} - R_{p,on}$$

(12)

Based on (7), (8), (11), and (12), we can calculate *Rs* and *Rp* under the optimal impedance matching condition.

# 3. Limitations of Conventional Structures

In general, attenuation bits with large attenuation values contribute large amplitude and phase variations and limit the bandwidth. In this section, the limitations of the conventional structure are analyzed using a conventional  $\pi$ -type attenuator as an example.

Figure 4 shows the equivalent circuit of the conventional  $\pi$ -type attenuator. Considering the parasitic capacitance of the transistor, the equivalent circuit of the reference state can be considered as a low-pass filter with phase lag, and the parasitic capacitance *Cp*,off of the shunt transistor will cause the leakage of the high-frequency signal to ground. Conversely, the equivalent circuit of the attenuation state can be considered as a high-pass filter with phase advance, and the high-frequency signal can be directly output through the parasitic capacitance *Cs*,off of the series transistor. Consequently, the presence of *Cs*,off and *Cp*,off leads to a relative attenuation value that is less than the ideal one, accompanied by an additional phase shift exceeding 0°.

The transmission matrix for a conventional  $\pi$ -type structure in the reference state is given by the following (13):

$$\begin{pmatrix} A & B \\ C & D \end{pmatrix} = \begin{pmatrix} 1 + \frac{\omega^2 C_{p,off}^2 R_p R_{s,on} R_S}{R_s + R_{s,on}} + \frac{j\omega C_{p,off} R_{s,on} R_s}{R_s + R_{s,on}} & \frac{R_s R_{s,on}}{R_s + R_{s,on}} \\ 2\omega^2 C_{p,off}^2 (R_p - \frac{R_s R_{s,on}}{R_s + R_{s,on}}) + j2\omega C_{p,off} & 1 + \frac{\omega^2 C_{p,off}^2 R_p R_{s,on} R_s}{R_s + R_{s,on}} + \frac{j\omega C_{p,off} R_{s,on} R_s}{R_s + R_{s,on}} \end{pmatrix}$$

(13)

The corresponding transmission S-parameter is given by the following (14):

$$S_{21} = \left(\frac{2}{A + \frac{B}{Z_0} + Z_0C + D}\right) = \frac{1}{1 + \frac{R_{s,on}R_s}{R_{s,on} + R_s}\left(\omega^2 C_{p,off}^2 R_P + j\omega C_{p,off} + \frac{1}{2Z_0}\right) + \omega Z_0 C_{p,off}\left(\omega C_{p,off} R_P - \frac{\omega C_{p,off} R_{s,on} R_s}{R_{s,on} + R_s} + j\right)}$$

(14)

where C<sub>n</sub> off is the parasitie capacitance in the off state of the parallel transistor

where *Cp,off* is the parasitic capacitance in the off state of the parallel transistor. The transmission phase in the reference state can be expressed as follows:

$$\varphi_R \approx -\tan^{-1} \frac{2\omega Z_0^2 C_{p,off} (R_{s,on} + R_s)^2 (R_{s,on} R_s + R_{s,on} Z_0^2 + R_s Z_0^2)}{R_{s,on} R_s}$$

(15)

Similarly, the transmission phase in the attenuation state can be expressed as follows:

$$\varphi_A \approx -\tan^{-1} \frac{\omega C_{s,off}(Z_0^2 + R_{p,on}R_p)}{2R_{p,on}Z_0^2 + 2R_pZ_0^2}$$

(16)

where  $\omega^2 C_{s,off}^2 R_s^2$  and  $\omega^2 C_{p,off}^2 R_p^2$  are omitted to simplify the calculations.

In order for the transmission phase difference to be zero, the following equation must be satisfied:

$$\Delta \varphi = \varphi_A - \varphi_R = 0 \tag{17}$$

The transmission phase  $\varphi_R$  is less than or equal to 0, while  $\varphi_A$  is greater than or equal to 0°. Therefore, to achieve zero transmission phase difference, the following relationship should be satisfied:

$$\varphi_A = \varphi_R = 0 \tag{18}$$

However, the parasitic capacitance of the transistor cannot be zero, so the phase of the attenuation state of the conventional  $\pi$ -type topology is always ahead of the phase of the reference state. Additionally, as the frequency increases, the reactance of the capacitor decreases, which can exacerbate the amplitude and phase errors between the two states.

#### 4. Design of the Proposed Structures

In this section, we propose two innovative compensation structures: a series inductive compensation structure (SICS) designed to compensate for high frequency attenuation values and a small bit compensation structure (SBCS) for large attenuation bits. The proposed compensation structures effectively broaden the bandwidth of the attenuator and reduce the high-frequency additional phase shift. Furthermore, the compensation structures are equally applicable to T-type attenuators.

#### 4.1. Series Inductive Compensation Structure (SICS)

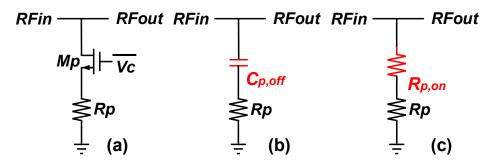

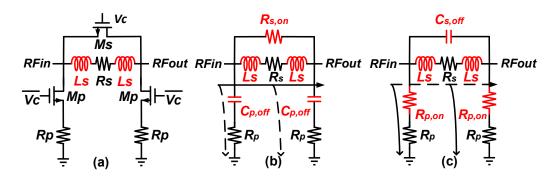

Figure 5 shows the modified  $\pi$ -type attenuator with a series inductive compensation structure and its equivalent circuits for the reference and attenuation states.

**Figure 5.** (a) Schematic diagram of the modified  $\pi$ -type attenuator and its equivalent circuits. (b) Reference state. (c) Attenuation state.

For the amplitude, when the resistance Rs is connected in series with two inductors Ls, the resultant total impedance becomes  $Rs + 2j\omega Ls$ . Notably, the total impedance value escalates in correlation with the frequency, thereby compensating for the attenuation values at high frequencies.

For the phase, the transmission phases  $\varphi_R$  and  $\varphi_A$  in the reference and attenuation states of SICS can be written as (1) and (2), respectively.

$$\varphi_{R} = -\tan^{-1}\left(\frac{2((R_{s,on}^{2} + 4\omega^{2}L_{s}C_{p,off}Z_{0}(Z_{0} + R_{s,on}))L_{s} + (Z_{0}R_{s,on}^{2} + R_{s}R_{s,on}(R_{s,on} + 4Z_{0}) + R_{s}^{2}(Z_{0} + R_{s,on}))Z_{0}C_{p,off})\omega}{(2Z_{0} + R_{s})R_{s,on}^{2} + 4R_{s,on}R_{s}^{2} + 2(R_{s}^{2} + 2R_{s}R_{s,on})Z_{0} - 2\omega^{2}L_{s}(2C_{p,off}R_{s,on}^{2}Z_{0} - 2L_{s}R_{s,on} - 4L_{s}Z_{0})}\right)$$

(19)

$$p_A = \tan^{-1}\left(\frac{(C_{s,off}R_s^2 + 12\omega^2 L_s^2 C_{s,off} - 2L_s)(R_p + Z_0)\omega}{(R_s R_p + Z_0 R_s + 4Z_0 R_p)(1 - 4\omega^2 L_s C_{s,off})}\right)$$

(20)

The inductor required to realize (17) is derived as follows:

φ

$$L_{S} \simeq \frac{1 - \sqrt{1 - 16\omega^{2}R_{s}^{2}C_{s,off}^{2}}}{2\omega^{2}C_{s,off}}$$

(21)

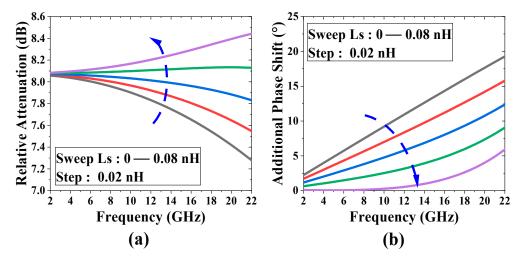

Figure 6 shows the simulated relative attenuation and additional phase shift versus frequency for different *Ls* values of the 8 dB modified  $\pi$ -type attenuator. As the value of compensation inductance *Ls* increases, both the relative attenuation value and additional phase shift progressively approach ideal values. Selecting the appropriate *Ls*, the attenuation bandwidth can be broadened, and the additional phase shift can be optimized. This paper uses microstrip lines instead of series inductors to achieve compensation functions.

**Figure 6.** Simulated (**a**) relative attenuation and (**b**) additional phase shift using SICS for different *Ls* values.

It is worth noting that *Ls* has little effect on the low-frequency performance, which is critical for designing ultra-wideband attenuators.

# 4.2. Small Bit Compensation Structure (SBCS)

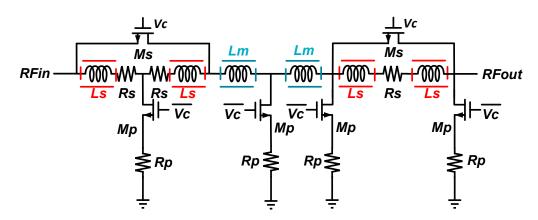

The conventional method to achieve a 16 dB attenuator is to cascade two 8 dB conventional  $\pi$ -type attenuators. However, there are many parasitic parameters in the  $\pi$ -type structure, and the parasitic effect will cause errors in the high frequency attenuation and additional phase shift. Cascading two  $\pi$ -type attenuators will accumulate these errors and deteriorate matching performance. The matching performance of the conventional T-type structure deteriorates with the increase of attenuation, which will lead to the deterioration of the performance of the whole 6-bit DSA.

Figure 3a shows the simplified T-type structure, which has the dual capability of compensating attenuation and minimizing insertion loss. Notably, the attenuation values of both the T-type and  $\pi$ -type structures diminish with increasing frequency. In contrast, the attenuation value of the simplified T-type structure escalates with frequency, enabling a small bit compensation through its utilization. Specifically, a modified  $\pi$ -type and T-type attenuator is employed to achieve most of the attenuation firstly, and a simplified T-type attenuator is then inserted between them to compensate for the high-frequency attenuation and further improve the matching performance, as shown in Figure 7.

Figure 7. Schematic of 16 dB attenuator with small bit compensation structure.

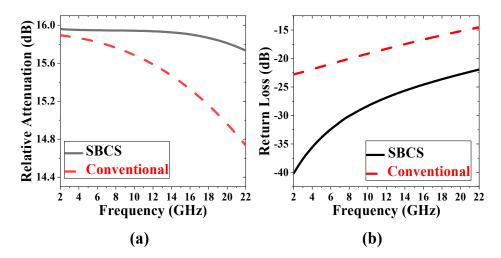

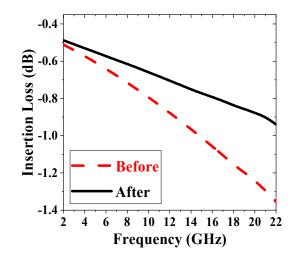

Figure 8 shows the comparison of simulation results for these two structures, where, the dashed line represents the simulation results of the conventional structure, and the solid line represents the simulation results of the small bit compensation structure proposed in this paper. The simulation results show that the implementation of SBCS enhances the high-frequency attenuation value of a 16 dB attenuator by 1.2 dB, significantly broadening the operating bandwidth of the attenuator. Furthermore, it substantially improves the return loss.

**Figure 8.** Simulation results of conventional structure and SBCS. (a) Relative attenuation and (b) return loss.

The SBCS offers an effective design strategy for the creation of attenuators with large attenuation value.

## 5. Insertion Loss Reduction Techniques (ILRTs)

The primary sources of DSA insertion loss are twofold: the transistor on-resistance and reflection between multiple attenuation bits. Consequently, this paper proposes ILRTs to minimize circuit insertion loss and enhance matching performance.

# 5.1. Simplified T-Structure

The insertion loss of a conventional T-type attenuator is related to the on-resistance of the series transistors. While the on-resistance of series switches is unavoidable in a switching T-type topology, in some cases, the series transistors can be removed without loss of functionality.

Figures 2a and 3a show the T-type and simplified T-type structure, respectively. The simplified T-type structure removes the series transistor Ms and series resistors *Rs*, which greatly reduces the insertion loss.

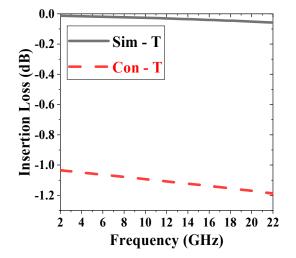

Figure 9 shows the insertion loss of the simplified T-type and the T-type attenuators, where, the dashed line shows the simulation results for the conventional T-structure and the solid line shows

the simulation results for the simplified T-structure. The result shows that the insertion loss of the simplified T-type structure is reduced by 1.15 dB. In this paper, both 0.5 dB and 1 dB attenuation bits use the simplified T-type structure, which reduces the insertion loss of the 6-bit DSA by 2.3 dB.

Figure 9. Comparison of insertion loss between T-type and simplified T-type attenuators.

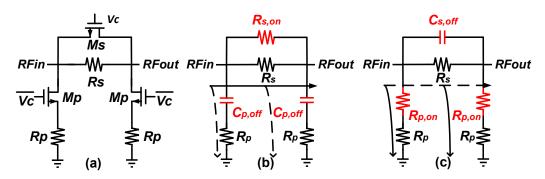

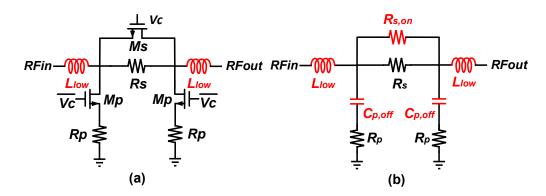

# 5.2. Low-Pass Inductive Compensation Structure

When cascading attenuation bits, the parasitic capacitance of transistors causes mismatch, which results in reflected signal power and causes unnecessary loss. Since the transistor parasitic capacitance forms a high-pass structure, we aim to construct a low-pass filter to compensate for its tendency to change; thus, we connect inductors in series at the input and output of the  $\pi$ -type structure to realize the low-pass filtering function, and the  $\pi$ -type topology of the structure employing low-pass inductive compensation is shown in Figure 10a.

**Figure 10.** (a)  $\pi$ -structure with low-pass inductive compensation and its equivalent circuit. (b) Reference state.

Figure 10b shows the equivalent circuit of Figure 10a in its reference state. *Llow, Cp,off, Rs,on* and *Rs* form a low-pass filter.

Figure 11 shows the insertion loss before and after using low-pass inductive compensation structure to the conventional 8 dB  $\pi$ -type attenuator. Low-pass inductive compensation structure reduces the insertion loss from -1.36 dB to -0.92 dB, effectively compensating for the circuit's capacitive losses. This paper uses microstrip lines instead of inductors to achieve compensation functions.

**Figure 11.** Comparison of insertion loss between the  $\pi$ -type attenuator before and after using low-pass inductive compensation structure.

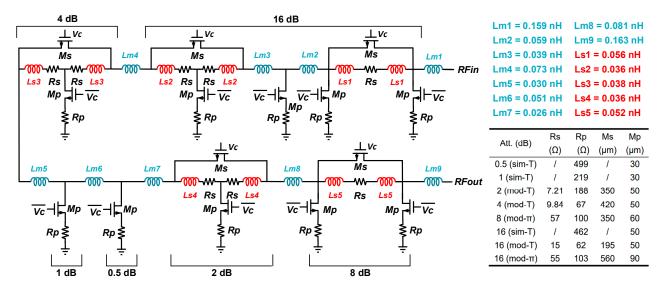

#### 6. Implementation of The Six-Bit DSA

Figure 12 shows the complete schematic of the 6-bit DSA, which has an attenuation range of up to 31.5 dB in 0.5 dB steps. The 0.5 dB and 1 dB attenuation bits use a simplified T-type structure to minimize insertion loss; the 2 dB and 4 dB attenuation bits use a modified T-type structure based on SICS; the 8 dB attenuation bit uses a modified  $\pi$ -type structure based on SICS; and the 16 dB attenuation bits use an innovative multi-type structure based on SBCS to minimize amplitude errors and phase fluctuations. Since the parasitic capacitance associated with the transistors and the interconnection structures presents a negative imaginary impedance, this shifts S<sub>11</sub> and S<sub>22</sub> down along the 50  $\Omega$  circle on the Smith chart. Inserting series inductors *Lm* between bits improves the matching characteristics, thereby maximizing operational bandwidth. In this paper, transmission lines are used instead of inductors. In addition, the transistors in each attenuation bit are optimized to achieve a balance between insertion loss and phase error.

Figure 12. Schematic of the 6-bit DSA.

#### 7. Measurement Results

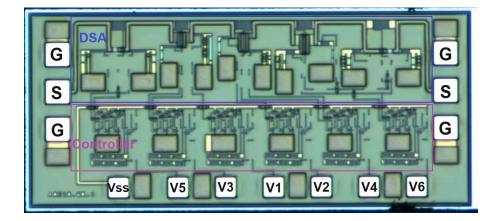

Figure 13 shows the chip micrograph of the proposed 6-bit DSA implemented by a 0.25  $\mu$ m GaAs process, with a core area of 0.51 mm<sup>2</sup>. The chip integrates a positive voltage controller and realizes compatibility with conventional CMOS TTL control voltage.

Figure 13. Micrograph of the proposed 6-bit DSA.

To evaluate the performance of the DSA, the root mean square (RMS) amplitude/phase error is defined as follows:

$$RMS\_Amplitude\_Error = \sqrt{\frac{1}{2^n - 1} \sum_{i=1}^{i=2^n - 1} \left(RA_{i\_measured} - RA_{i\_ideal}\right)^2}$$

(22)

$$RMS\_Phase\_Error = \sqrt{\frac{1}{2^{n}-1} \sum_{i=1}^{i=2^{n}-1} (\phi_{i\_measured} - \phi_{ref})^{2}}$$

(23)

where *RAi\_measured* and *RAi\_iedal* are the relative attenuation values measured at state i and the ideal relative attenuation value of state *i*, respectively. Similarly,  $\varphi_{i_measured}$  and  $\varphi_{ref}$  are the additional phase shift measured at state *i* and the reference state, respectively.

The electrical properties of the chip were measured on-chip using a Cascade probe station, an ACP-GSGI50 microwave probe, an Agilent 5227B vector network analyzer, a digital multi-channel power supply, and a DC bias power supply. The DC bias voltage applied to the chip, along with the truth table for the digitally controlled power supply, is detailed in Table 1, where 0 represents 0 V, and 1 represents 5 V. This configuration enables the chip to attain 64 states by changing the control voltages.

| Bias Voltage/V | Digitally Controlled Voltage |     |     |     |     |     |          |  |

|----------------|------------------------------|-----|-----|-----|-----|-----|----------|--|

|                | Vc1                          | Vc2 | Vc3 | Vc4 | Vc5 | Vc6 | – Status |  |

| -5             | 0                            | 0   | 0   | 0   | 0   | 0   | 0 dB     |  |

| -5             | 0                            | 0   | 0   | 0   | 0   | 1   | 0.5 dB   |  |

| -5             | 0                            | 0   | 0   | 0   | 1   | 0   | 1 dB     |  |

| -5             | 0                            | 0   | 0   | 1   | 0   | 0   | 2 dB     |  |

| -5             | 0                            | 0   | 1   | 0   | 0   | 0   | 4 dB     |  |

| -5             | 0                            | 1   | 0   | 0   | 0   | 0   | 8 dB     |  |

| -5             | 1                            | 0   | 0   | 0   | 0   | 0   | 16 dB    |  |

| -5             | 1                            | 1   | 1   | 1   | 1   | 1   | 31.5 dB  |  |

Table 1. Bias Voltage and Truth Table.

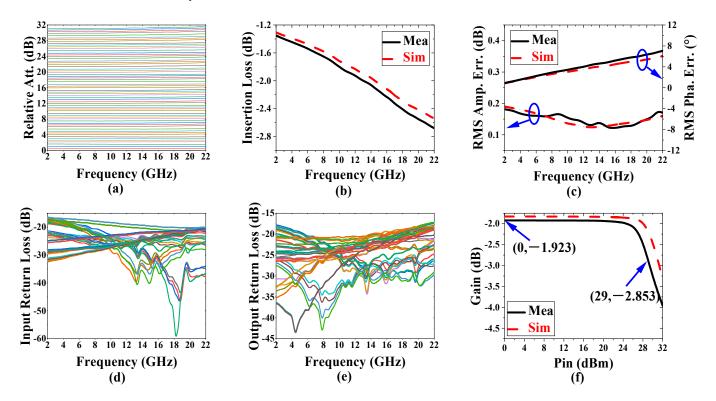

Figure 14 shows the results for this chip. Figure 14a shows the measured relative attenuation of all 64 states, with no overlap. Figure 14b shows the measured insertion loss of -2.54 dB. This remarkably low insertion loss can be primarily ascribed to ILRTs. Figure 14c shows the measured RMS amplitude and phase errors, which are within 0.18 dB and 7°, respectively, exhibiting the lowest amplitude error with small phase error between in 2 to 22 GHz in the GaAs process. As expected, the phase error increases when the frequency is increased. However, the additional phase shift is greatly reduced due to the use of series inductive compensation structures. Figure 14d, e show the measured return loss, and the return loss of all 64 states is better than -17 dB, indicating excellent matching performance. Figure 14f shows the measured power capacity at the reference state with the input 1 dB compression point (IP1 dB) of 29 dBm at IF 12 GHz, indicating that the DSA has a

sufficiently high-power performance to notbe a limiting factor in the linearity of the phased array system.

**Figure 14.** (a) Measured relative attenuation. (b) Simulated and measured RMS amplitude and phase errors. (c) Simulated and measured insertion loss. (d) Measured input return loss. (e) Measured output return loss. (f) Simulated and measured IP1 dB at 12 GHz.

Table 2 presents the comparison of the designed DSA with the published attenuators with stateof-the-art performance. The results show that the proposed DSA shows the best performance in terms of insertion loss, RMS amplitude error, return loss, linearity, and FOM.

| Reference               | [33]  | [34] | [35]  | [6]        | This Work |

|-------------------------|-------|------|-------|------------|-----------|

| Technology              | GaAs  | GaAs | GaAs  | CMOS       | GaAs      |

| BW (GHz)                | 6-18  | 5-18 | DC-23 | DC-20      | 2–22      |

| Range (dB)              | 31.75 | 31.5 | 31.5  | 31.5       | 31.5      |

| IL (dB)                 | 9     | 6.2  | 6.2   | 7.4        | 2.6       |

| RMS Amp error (dB)      | 0.6   | 1.1  | 0.35  | 0.37       | 0.18      |

| RMS Phase error (°)     | 5     | 2    | 5     | 4          | 7         |

| RL (dB)                 | 12    | 8    | 10    | 12         | 17        |

| IP1dB (dBm)             | N/A   | 24   | N/A   | 10         | 29        |

| Area (mm <sup>2</sup> ) | 5.4   | 3.75 | 0.47  | 0.98*/0.14 | 0.51      |

| FOM <sup>#</sup>        | 169   | 240  | 668   | 690        | 3269      |

Table 2. Comparison of The Prior-Art Attenuators.

\* with pads and non-active space. # FOM =  $\frac{BW \times Range \times RL}{IL \times RMS AmpErr \times RMS PhaseErr}$ .

# 8. Conclusions

In this paper, insertion loss reduction techniques reduce the insertion loss of 6-bit DSA by 50%; series inductive compensation and small bit compensation structures are innovatively proposed to greatly broaden the bandwidth of the attenuator and effectively improve the return loss. To the best of our knowledge, the fabricated DSA shows the lowest insertion loss, optimal impedance matching, the highest attenuation accuracy and linearity, and the best FOM using the 0.25  $\mu$ m GaAs process and is suitable for wideband phased array systems.

**Author Contributions:** Conceptualization, Q.L., K.W., X.W., Y.Y. and X.L.; methodology, Q.L., K.W., Y.Y. and X.L.; software, Q.L. and X.W.; validation, Q.L., K.W. and X.W.; data curation, Q.L. and X.W.; writing—original draft preparation, Q.L. and K.W.; writing—review and editing, Q.L., Y.Y. and X.L. All authors have read and agreed to the published version of the manuscript.

Funding: This research received no external funding.

Institutional Review Board Statement: Not applicable.

Informed Consent Statement: Not applicable.

Data Availability Statement: The data can be obtained from the authors on request.

**Conflicts of Interest:** The authors declare no conflicts of interest.

# References

- Nehring, J.; Schutz, M.; Dietz, M.; Nasr, I.; Aufinger, K.; Weigel, R.; Kissinger, D. Highly Integrated 4–32-GHz Two-Port Vector Network Analyzers for Instrumentation and Biomedical Applications. *IEEE Trans. Microw. Theory Tech.* 2017, 65, 229–244. [CrossRef]

- Dogan, H.; Meyer, R.G. Intermodulation Distortion in CMOS Attenuators and Switches. *IEEE J. Solid-state Circuits* 2007, 42, 529–539. [CrossRef]

- Wang, K.; Zhou, T.; Zhang, H.; Qiu, L. A 28–40-GHz Digital Step Attenuator with Low Amplitude and Phase Variations. *IEEE Microw. Wirel. Components Lett.* 2021, 31, 64–67. [CrossRef]

- 4. Cheon, C.D.; Rao, S.G.; Lim, W.; Cardoso, A.S.; Cho, M.-K.; Cressler, J.D. Design methodology for a wideband, low insertion loss, digital step attenuator in SiGe BiCMOS technology. *IEEE Trans. Circuits Syst. II Express Briefs* **2022**, *69*, 744–748. [CrossRef]

- Zeng, J.; Yu, Z.; Li, J.; Yuan, Y. A Wideband Compact 6-bit Digital Step Attenuator. In Proceedings of the 2022 IEEE MTT-S International Microwave Workshop Series on Advanced Materials and Processes for RF and THz Applications (IMWS-AMP), Guangzhou, China, 13–15 November 2022; pp. 1–3.

- 6. Song, I.; Cho, M.-K.; Cressler, J.D. Design and Analysis of a Low Loss, Wideband Digital Step Attenuator with Minimized Amplitude and Phase Variations. *IEEE J. Solid-state Circuits* **2018**, *53*, 2202–2213. [CrossRef]

- Sjogren, L.; Ingram, D.; Biedenbender, M.; Lai, R.; Allen, B.; Hubbard, K. A low phase-error 44-GHz HEMT attenuator. *IEEE Microw. Guid. Wave Lett.* 1998, 8, 194–195. [CrossRef]

- Cho, M.-K.; Kim, J.-G.; Baek, D. A Broadband Digital Step Attenuator with Low Phase Error and Low Insertion Loss in 0.18-μm SOI CMOS Technology. *ETRI J.* 2016, 35, 638–643. [CrossRef]

- 9. Kim, K.; Lee, H.-S.; Min, B.-W. V-W Band CMOS Distributed Step Attenuator with low Phase Imbalance. *IEEE Microw. Wirel. Components Lett.* **2014**, *24*, 548–550. [CrossRef]

- 10. Min, B.-W.; Rebeiz, G.M. A 10–50-GHz CMOS distributed step attenuator with low loss and low phase imbalance. *IEEE J. Solid-state Circuits* 2007, 42, 2547–2554. [CrossRef]

- 11. Cheng, W.; Alink, M.S.O.; Annema, A.J.; Wienk, G.J.M.; Nauta, B. A Wideband IM3 Cancellation Technique for CMOS II- and T-Attenuators. *IEEE J. Solid-state Circuits* **2013**, *48*, 358–368. [CrossRef]

- 12. Dogan, H.; Meyer, R.G.; Niknejad, A.M. Analysis and Design of RF CMOS Attenuators. *IEEE J. Solid-state Circuits* 2008, 43, 2269–2283. [CrossRef]

- Huang, Y.-Y.; Woo, W.; Yoon, Y.; Lee, C.-H. Highly Linear RF CMOS Variable Attenuators with Adaptive Body Biasing. *IEEE J. Solid-state Circuits* 2011, 46, 1023–1033. [CrossRef]

- 14. Bae, J.; Lee, J.; Nguyen, C. A 10–67-GHz CMOS Dual-Function Switching Attenuator with Improved Flatness and Large Attenuation Range. *IEEE Trans. Microw. Theory Tech.* 2013, *61*, 4118–4129. [CrossRef]

- Zhang, Z.; Li, N.; Gao, H.; Li, M.; Wang, S.; Kuan, Y.-C.; Song, C.; Yu, X.; Gu, Q.J.; Xu, Z. A DC-*Ka*-Band 7-Bit Passive Attenuator with Capacitive-Compensation-Based Bandwidth Extension Technique in 55-nm CMOS. *IEEE Trans. Microw. Theory Tech.* 2021, 69, 3861–3874. [CrossRef]

- He, Y.; Zhang, T.; Tang, Y.; Fan, C.; Yan, B. Wideband pHEMT Digital Attenuator with Positive Voltage Control Driver. *IEEE Microw. Wirel. Technol. Lett.* 2023, 33, 295–298. [CrossRef]

- 17. Zhang, L.; Zhao, C.; Zhang, X.; Wu, Y.; Kang, K. A CMOS K-Band 6-bit Attenuator with Low Phase Imbalance for Phased Array Applications. *IEEE Access* 2017, *5*, 19657–19661. [CrossRef]

- Davulcu, M.; Caliskan, C.; Kalyoncu, I.; Kaynak, M.; Gurbuz, Y. 7-Bit SiGe-BiCMOS Step Attenuator for X-Band Phased-Array RADAR Applications. *IEEE Microw. Wirel. Components Lett.* 2016, 26, 598–600. [CrossRef]

- 19. Li, N.; Zhang, Z.; Li, M.; Gao, H.; Wang, S.; Song, C.; Xu, Z. A DC–28-GHz 7-Bit High-Accuracy Digital-Step Attenuator in 55-nm CMOS. *IEEE Microw. Wirel. Components Lett.* **2021**, *32*, 157–160. [CrossRef]

- Nguyen, L.; Nguyen, V.; Phan, K.; Vu, T.; Lee, S.; Huynh, C. Low-loss 6-bit Sub-7 GHz Digital Step Attenuator. In Proceedings of the 2019 International Symposium on Electrical and Electronics Engineering (ISEE), Ho Chi Minh City, Vietnam, 10–12 October 2019; pp. 13–18. [CrossRef]

- Nagaveni, H.; Karthik, S. 0.5–4 GHz 7-bit GaAs MMIC Digital Attenuator with High Accuracy and Low Insertion Phase. In Proceedings of the 2022 International Conference for Advancement in Technology (ICONAT), Goa, India, 21–22 January 2022; pp. 1–4. [CrossRef]

- Li, A.; Ding, Y.; Chen, Z.; Wang, W.; Jiang, S.; Sun, S.; Chen, Z.; Chi, B. A Fully Integrated 27.5-30.5 GHz 8-element phased-array transmit front-end module in 65 nm CMOS. In In Proceedings of the 2019 IEEE Asian Solid-State Circuits Conference (A-SSCC), Macau, China, 4–6 November 2019; pp. 153–156.

- 23. Suh, B.; Min, B.-W. A 20–36-GHz voltage-controlled analog distributed attenuator with a wide attenuation range and low phase imbalance. *IEEE Trans. Microw. Theory Tech.* **2021**, *69*, 2485–2493. [CrossRef]

- Khaira, N.K.; Singh, T.; Mansour, R.R. RF MEMS Based 60 GHz Variable Attenuator. In Proceedings of the 2018 IEEE MTT-S International Microwave Workshop Series on Advanced Materials and Processes for RF and THz Applications (IMWS-AMP), Ann Arbor, MI, USA, 16–18 July 2018; pp. 1–3. [CrossRef]

- Xiao, H.; Hu, J.; Ma, K. A DC-6 GHz 7-Bit Digital Attenuator with Low Insertion Loss. In Proceedings of the 2021 IEEE 4th International Conference on Electronics Technology (ICET), Chengdu, China, 7–10 May 2021; pp. 95–98. [CrossRef]

- Cho, M.-K.; Han, J.-H.; Kim, J.-H.; Kim, J.-G. An X/Ku-band bi-directional true time delay T/R chipset in 0.13 µm CMOS technology. In Proceedings of the 2014 IEEE MTT-S International Microwave Symposium—IMS 2014, Tampa, FL, USA, 1–6 June 2014; pp. 1–3. [CrossRef]

- Cho, M.-K.; Song, I.; Cressler, J.D. A True Time Delay-based SiGe Bi-directional T/R Chipset for Large-Scale Wideband Timed Array Antennas. In Proceedings of the 2018 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Philadelphia, PA, USA, 10–12 June 2018; pp. 272–275. [CrossRef]

- 28. Banerjee, S.; Pradhan, B. Design of S-Band Source-Controlled MMIC Voltage Variable Attenuator. In Proceedings of the 2021 IEEE Pune Section International Conference (PuneCon), Pune, India, 16–19 December 2021; pp. 1–4. [CrossRef]

- Zhao, C.; Guo, J.; Liu, H.; Yu, Y.; Wu, Y.; Kang, K. A 33–41-GHz SiGe-BiCMOS digital step attenuator with minimized unit impedance variation. *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.* 2021, 29, 568–579. [CrossRef]

- 30. Hu, Z.; Zhou, S.; He, R.; Zhang, Q. A Broadband Voltage Variable Attenuator with High-Power Tolerance and Compact Size Based on Dual-Gate GaN HEMTs. *IEEE Trans. Power Electron.* **2023**, *38*, 6108–6115. [CrossRef]

- Park, K.; Lee, S.; Jeon, S. A new compact CMOS distributed digital attenuator. *IEEE Trans. Microw. Theory Tech.* 2020, 68, 4631–4640. [CrossRef]

- Gharibdoust, K.; Mousavi, N.; Kalantari, M.; Moezzi, M.; Medi, A. A Fully Integrated 0.18- μm CMOS Transceiver Chip for X-Band Phased-Array Systems. *IEEE Trans. Microw. Theory Tech.* 2012, 60, 2192–2202. [CrossRef]

- Jeong, J.-C.; Yom, I.-B.; Kim, J.-D.; Lee, W.-Y.; Lee, C.-H. A 6–18-GHz GaAs Multifunction Chip with 8-bit True Time Delay and 7-bit Amplitude Control. *IEEE Trans. Microw. Theory Tech.* 2018, 66, 2220–2230. [CrossRef]

- Bangar, N.; Yadav, A.P.S.; Chaturvedi, S.; Naik, A.A. Design of Monolithic 5–18 GHz Digital Attenuator with Low Attenuation and Phase Error. In Proceedings of the 2022 IEEE Microwaves, Antennas, and Propagation Conference (MAPCON), Bangalore, India, 12–16 December 2022; pp. 796–799. [CrossRef]

- Li, Z.; Zhang, W.; Hao, D.; Liu, X.; Liang, Y.; Liu, Y. A DC-23 GHz Broadband Digital Step Attenuator MMIC Using Capacitive-Inductive Joint Compensation. *IEEE Microw. Wirel. Technol. Lett.* 2023, 34, 291–294. [CrossRef]

**Disclaimer/Publisher's Note:** The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content.