Experiment Study of Single Event Functional Interrupt in Analog-to-Digital Converters Using a Pulsed Laser

Abstract

:1. Introduction

2. Experimental Devices and Methods

2.1. Experimental Setup

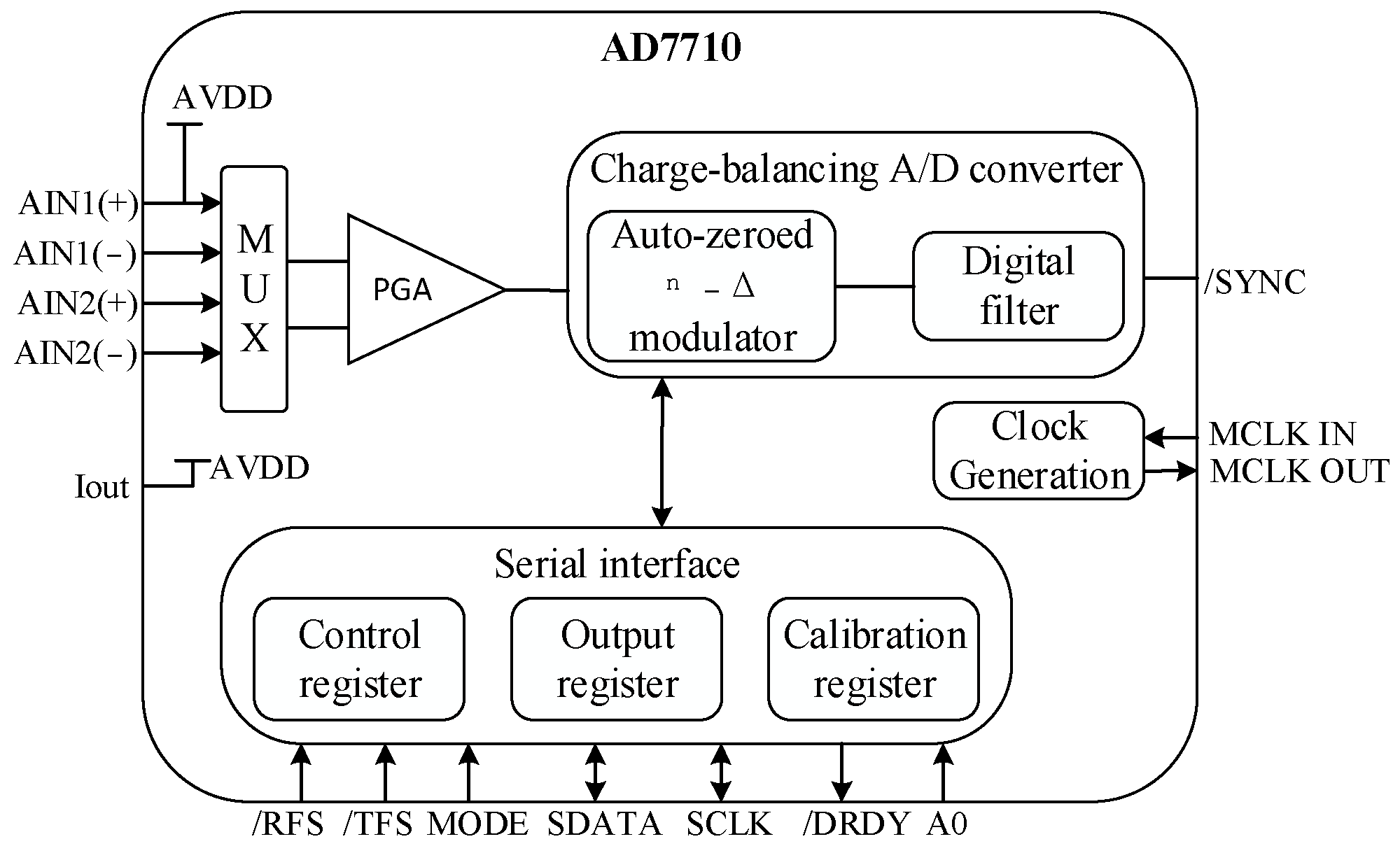

2.2. DUT

2.3. Experimental Method

3. Results and Discussion

3.1. SEFI Caused by Configuration Register Flipping

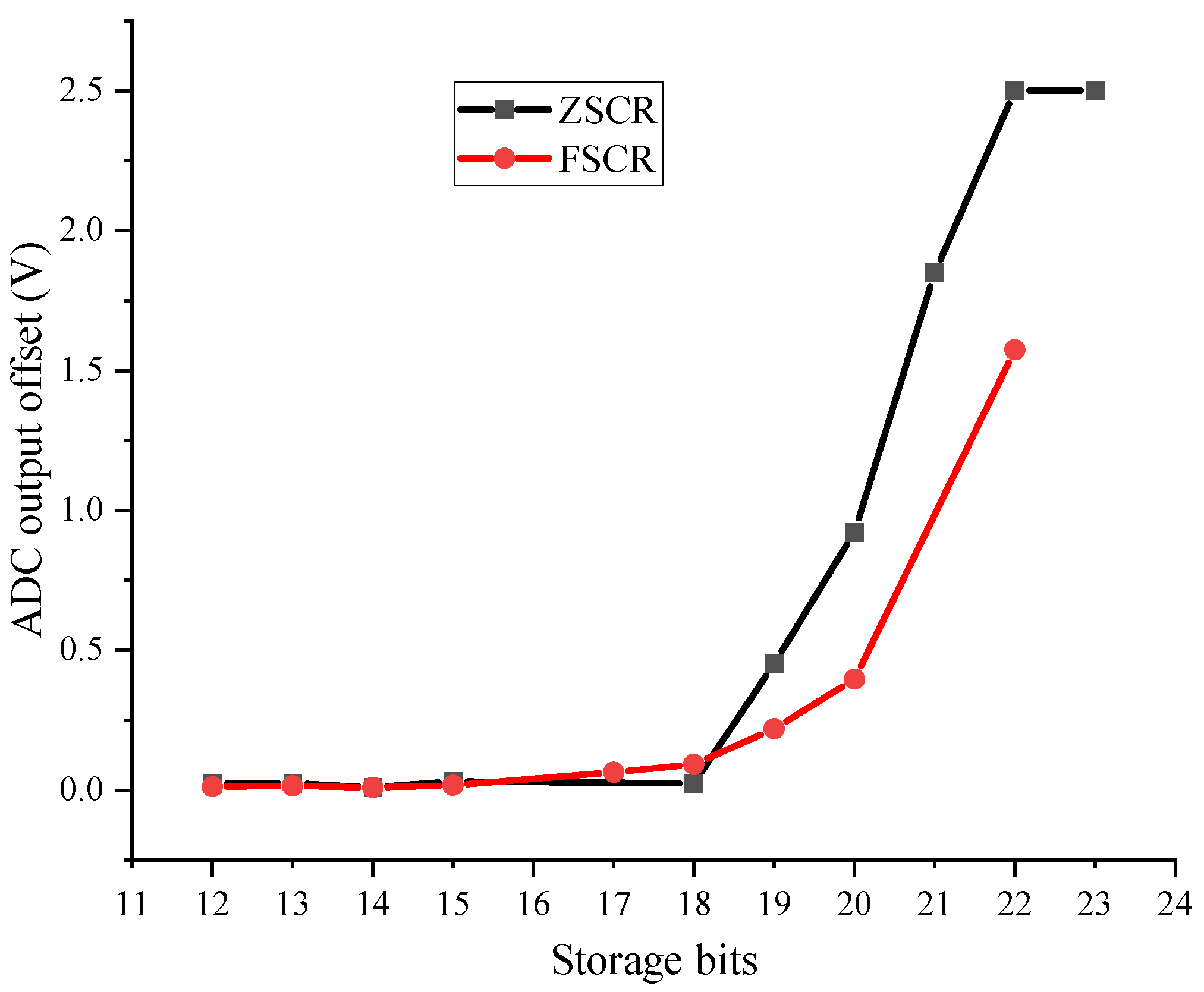

3.2. SEFI Caused by Calibration Register Flipping

3.3. SEFI Caused by Pin Current Latch-Up

4. SEFI Protection

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Koga, R.; Penzin, S.H.; Crawford, K.B.; Crain, W.R. Single event functional interrupt (SEFI) sensitivity in microcircuits. In Proceedings of the 4th European Conference on Radiation and Its Effects on Components and Systems (RADECS 97), Cannes, France, 15–19 September 1997; pp. 311–318. [Google Scholar]

- Ju, A.A.; Guo, H.X.; Ding, L.L.; Zhang, F.Q.; Zhong, X.L.; Pan, X.Y.; Zhang, H.; Bi, J.S. Analysis of Ion-Induced SEFI and SEL Phenomena in 90 nm NOR Flash Memory. IEEE Trans. Nucl. Sci. 2021, 68, 2508–2515. [Google Scholar] [CrossRef]

- Yang, W.; Li, Y.; Li, Y.; Hu, Z.; Xie, F.; He, C.; Wang, S.; Zhou, B.; He, H.; Khan, W.; et al. Atmospheric neutron single event effect test on Xilinx 28 nm system on chip at CSNS-BL09. Microelectron. Reliab. 2019, 99, 119–124. [Google Scholar] [CrossRef]

- Bagatin, M.; Gerardin, S.; Cellere, G.; Paccagnella, A.; Visconti, A.; Beltrami, S.; Harboe-Sorensen, R.; Virtanen, A. Key Contributions to the Cross Section of NAND Flash Memories Irradiated With Heavy Ions. IEEE Trans. Nucl. Sci. 2008, 55, 3302–3308. [Google Scholar] [CrossRef]

- Nekrasov, P.V.; Karakozov, A.B.; Bobrovskyi, D.V.; Marfin, V.A. Investigation of single event functional interrupts in microcontoller with PIC17 architecture. In Proceedings of the 2015 15th European Conference on Radiation and Its Effects on Components and Systems (RADECS), Moscow, Russia, 14–18 September 2015; pp. 1–4. [Google Scholar]

- Chen, D.; Wilcox, E.; Berg, M.; Kim, H.; Phan, A.; Figueiredo, M.; Seidleck, C.; LaBel, K. Single-event effect performance of a conductive-bridge memory EEPROM. IEEE Trans. Nucl. Sci. 2015, 62, 2703–2708. [Google Scholar] [CrossRef] [Green Version]

- Sánchez-Macián, A.; Reviriego, P.; Tabero, J.; Regadío, A.; Maestro, J.A. SEFI protection for nanosat 16-bit chip onboard computer memories. IEEE Trans. Device 2017, 17, 698–707. [Google Scholar] [CrossRef]

- Aranda, L.A.; Sánchez-Macián, A.; Maestro, J.A. A Methodology to Analyze the Fault Tolerance of Demosaicking Methods against Memory Single Event Functional Interrupts (SEFIs). Electronics 2020, 9, 1619. [Google Scholar] [CrossRef]

- Koga, R.; Yu, P.; Crain, S.; George, J. Proton and heavy ion induced semi-permanent upsets in double data rate SDRAMs. In Proceedings of the 2007 IEEE Radiation Effects Data Workshop, Honolulu, HI, USA, 23–27 July 2007; pp. 199–203. [Google Scholar]

- Guertin, S.M.; Patterson, J.D.; Nguyen, D.N. Dynamic SDRAM SEFI detection and recovery test results. In Proceedings of the 2004 IEEE Radiation Effects Data Workshop (IEEE Cat. No. 04TH8774), Atlanta, GA, USA, 22 July 2004; pp. 62–67. [Google Scholar]

- Tanaka, T.; Liao, W.; Hashimoto, M.; Mitsuyama, Y. Impact of Neutron-Induced SEU in FPGA CRAM on Image-Based Lane Tracking for Autonomous Driving: From Bit Upset to SEFI and Erroneous Behavior. IEEE Trans. Nucl. Sci. 2022, 69, 35–42. [Google Scholar] [CrossRef]

- George, J.; Koga, R.; Swift, G.; Allen, G.; Carmichael, C.; Tseng, C. Single event upsets in Xilinx Virtex-4 FPGA devices. In Proceedings of the 2006 IEEE Radiation Effects Data Workshop, Ponte Vedra Beach, FL, USA, 17–21 July 2006; pp. 109–114. [Google Scholar]

- Xiong, X.; Du, X.; Zheng, B.; Chen, Z.; Jiang, W.; He, S.; Zhu, Y. Soft Error Sensitivity Analysis Based on 40 nm SRAM-Based FPGA. Electronics 2022, 11, 3844. [Google Scholar] [CrossRef]

- Scheick, L.Z.; Allen, G.R.; Edmonds, L.D. Single-Event Effect Qualification of 24 Bit Analog-to-Digital Converters. In Proceedings of the 50th Annual IEEE Nuclear and Space Radiation Effects Conference (NSREC)/IEEE Radiation Effects Data Workshop (REDW), San Francisco, CA, USA, 8–12 July 2013. [Google Scholar]

- Esteban, A.; Bogorad, A.; Likar, J.; Moyer, S.; Herschitz, R. Single Event Effects on New High Speed Analog to Digital Converters, Digital to Analog Converters, Hybrid MUXDAC Devices, and Voltage Converters. In Proceedings of the 2006 IEEE Radiation Effects Data Workshop, Ponte Vedra Beach, FL, USA, 17–21 July 2006; pp. 43–49. [Google Scholar]

- Chen, K.; Chen, H.; Kierstead, J.; Takai, H.; Rescia, S.; Hu, X.; Xu, H.; Mead, J.; Lanni, F.; Minelli, M. Evaluation of commercial ADC radiation tolerance for accelerator experiments. J. Instrum. 2015, 10, P08009. [Google Scholar] [CrossRef] [Green Version]

- Kruckmeyer, K.; Trinh, T. Single event effects characterization of Texas Instruments ADC12D1600CCMLS, 12 bit, 3.2 GSPS analog-to-digital converter with static and dynamic inputs. In Proceedings of the 2014 IEEE Radiation Effects Data Workshop (REDW), Paris, France, 14–18 July 2014; pp. 1–7. [Google Scholar]

- Analog Devices Inc. AD7710 Datasheet. Available online: https://www.analog.com/media/en/technical-documentation/data-sheets/AD7710.pdf (accessed on 1 June 2023).

- Bougerol, A.; Miller, F.; Guibbaud, N.; Gaillard, R.; Moliere, F.; Buard, N. Use of Laser to Explain Heavy Ion Induced SEFIs in SDRAMs. IEEE Trans. Nucl. Sci. 2010, 57, 272–278. [Google Scholar] [CrossRef]

- Li, S.; Han, J.W.; Chen, R.; Shangguan, S.P.; Ma, Y.Q.; Wang, X. Study on the single-event upset sensitivity of 65-nm CMOS sequential logic circuit. Ieice Electron. Express 2020, 17. [Google Scholar] [CrossRef] [Green Version]

- Xin, J.; Zhu, X.; Ma, Y.; Han, J. Study of Single Event Latch-Up Hardness for CMOS Devices with a Resistor in Front of DC-DC Converter. Electronics 2023, 12, 550. [Google Scholar] [CrossRef]

- Feng, G.; Shangguan, S.; Ma, Y.; Han, J. SEE characteristics of small feature size devices by using laser backside testing. J. Semicond. 2012, 33, 014008. [Google Scholar] [CrossRef]

- Darracq, F.; Lapuyade, H.; Buard, N.; Mounsi, F.; Foucher, B.; Fouillat, P.; Calvet, M.-C.; Dufayel, R. Backside SEU laser testing for commercial off-the-shelf SRAMs. IEEE Trans. Nucl. Sci. 2002, 49, 2977–2983. [Google Scholar] [CrossRef]

- Johnston, A.; Baze, M. Mechanisms for the latchup window effect in integrated circuits. IEEE Trans. Nucl. Sci. 1985, 32, 4017–4025. [Google Scholar] [CrossRef]

- Plaag, R.; Baze, M.; Johnston, A. A distributed model for radiation-induced latchup. IEEE Trans. Nucl. Sci. 1988, 35, 1563–1569. [Google Scholar] [CrossRef]

- Johnston, A. The influence of VLSI technology evolution on radiation-induced latchup in space systems. IEEE Trans. Nucl. Sci. 1996, 43, 505–521. [Google Scholar] [CrossRef]

- Becker, H.N.; Miyahira, T.F.; Johnston, A.H. Latent damage in CMOS devices from single-event latchup. IEEE Trans. Nucl. Sci. 2002, 49, 3009–3015. [Google Scholar] [CrossRef] [Green Version]

- Jeong, S.-H.; Lee, N.-H.; Cho, S.-I. A Design of High-speed Power-off Circuit and Analysis. Trans. Korean Inst. Electr. Eng. 2014, 63, 490–494. [Google Scholar] [CrossRef] [Green Version]

- Andjelković, M.S.; Petrović, V.; Stamenković, Z.; Ristić, G.S.; Jovanović, G.S. Circuit-level simulation of the single event transients in an on-chip single event latchup protection switch. J. Electron. Test. 2015, 31, 275–289. [Google Scholar] [CrossRef]

| Laser Wavelength | Typical Pulse Width | Beam Spot Size | Maximum Energy | Scanning Step Size | Repetition Rate | Energy Error Range |

|---|---|---|---|---|---|---|

| 1064 nm | 20 ps | 3 μm | 3 mJ | 5 μm | 1–10 kHz | <1% (8 h) |

| Number | Data (24 Bits) | Function |

|---|---|---|

| 1 | 22909C | Used to initialize the configuration register, ADC power-on self-calibration, unipolar input, the gain of 1, sampling channel of 2, first notch frequency of 100.16 Hz, the cut-off frequency of 26.2 Hz |

| 2 | C2909C | Enter the ZSCR read and write mode |

| 3 | E2909C | Enter FSCR read and write mode |

| 4 | 39E000 | ZSCR initialization data |

| 5 | 5E7000 | FSCR initialization data |

| Configuration Bits (24 bits) | Function | Flip Effect |

|---|---|---|

| 0~11 | Set the ADC filter cut-off frequency, the position of the first notch of the filter, and the data rate of the device. | Filter cut-off frequency and slew rate change |

| 12 | Input polarity setting, 0: Bipolar, 1: Unipolar | Input signal polarity changes |

| 13 | Burn-Out Current, 0: Off, 1: On | Unobservable |

| 14 | Output Compensation Current, 0: Off, 1: On | Unobservable |

| 15 | Output data word length setting, 0: 16-Bits, 1: 24-Bits | Not observed |

| 16 | Power-Down mode, 0: Normal Operation, 1: Power-Down | No data output |

| 17 | Sampling channel setting, 0: AIN1, 1: AIN2 | The sampling channel changes |

| 18–20 | Gain setting, (1, 2, 4, 8, 16, 32, 64, or 128) | Signal gain changes |

| 21–23 | Mode setting, can be set to normal, self-calibration, system calibration, background calibration, and other working modes | Work mode changes |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Mai, Z.; Zhu, X.; Li, H.; Han, J.; He, T. Experiment Study of Single Event Functional Interrupt in Analog-to-Digital Converters Using a Pulsed Laser. Electronics 2023, 12, 2774. https://doi.org/10.3390/electronics12132774

Mai Z, Zhu X, Li H, Han J, He T. Experiment Study of Single Event Functional Interrupt in Analog-to-Digital Converters Using a Pulsed Laser. Electronics. 2023; 12(13):2774. https://doi.org/10.3390/electronics12132774

Chicago/Turabian StyleMai, Ziqi, Xiang Zhu, Hongwei Li, Jianwei Han, and Tao He. 2023. "Experiment Study of Single Event Functional Interrupt in Analog-to-Digital Converters Using a Pulsed Laser" Electronics 12, no. 13: 2774. https://doi.org/10.3390/electronics12132774