# Article Survey of Reliability Research on 3D Packaged Memory

Shuai Zhou <sup>1,2</sup>, Kaixue Ma <sup>1,\*</sup>, Yugong Wu <sup>1</sup>, Peng Liu <sup>2,\*</sup>, Xianghong Hu <sup>2</sup>, Guojian Nie <sup>2</sup>, Yan Ren <sup>2</sup>, Baojun Qiu <sup>2</sup>, Nian Cai <sup>3,\*</sup>, Shaoqiu Xu <sup>3</sup> and Han Wang <sup>3</sup>

- <sup>1</sup> School of Microelectronics, Tianjin University, Tianjin 300072, China; zhoushuai@tju.edu.cn (S.Z.)

- <sup>2</sup> China Electronic Product Reliability and Environmental Testing Research Institute, Guangzhou 510610, China

- <sup>3</sup> School of Information Engineering, Guangdong University of Technology, Guangzhou 510006, China

- \* Correspondence: makaixue@uestc.edu.cn (K.M.); liupeng@ceprei.com (P.L.); cainian@gdut.edu.cn (N.C.)

**Abstract:** As the core carrier of information storage, a semiconductor memory device is a basic product with a large volume that is widespread in the integrated circuit industry. With the rapid development of semiconductor manufacturing processes and materials, the internal structure of memory has gradually shifted from a 2D planar packaging structure to a 3D packaging structure to meet industry demands for high-frequency, high-speed, and large-capacity devices with low power consumption. However, advanced 3D packaging technology can pose some reliability risks, making devices prone to failure, especially when used in harsh environmental conditions, including temperature changes, high temperature and humidity levels, and mechanical stress. In this paper, the authors introduce the typical structure characteristics of 3D packaged memory; analyze the reasons for device failure caused by stress; summarize current research methods that utilize temperature, mechanical and hygrothermal theories, and failure models; and present future challenges and directions regarding the reliability research of 3D packaged memory.

Keywords: 3D packaging; memory; environmental load; reliability; review

Citation: Zhou, S.; Ma, K.; Wu, Y.; Liu, P.; Hu, X.; Nie, G.; Ren, Y.; Qiu, B.; Cai, N.; Xu, S.; et al. Survey of Reliability Research on 3D Packaged Memory. *Electronics* **2023**, *12*, 2709. https://doi.org/10.3390/ electronics12122709

Academic Editors: Francis Balestra and Gerard Ghibaudo

Received: 12 May 2023 Revised: 10 June 2023 Accepted: 13 June 2023 Published: 17 June 2023

**Copyright:** © 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https:// creativecommons.org/licenses/by/ 4.0/).

# 1. Introduction

A memory circuit, as an important component of an integrated circuit, is the most widely used, basic, general-purpose integrated circuit. It plays an extremely important role in the semiconductor industry. According to the principle of whether stored data are lost following power failure, memory can be divided into two categories: volatile memory and non-volatile memory. Volatile memory mainly includes DRAM and SRAM, and non-volatile memory includes EEPROM, EPROM, PROM, NOR FLASH, and NAND FLASH. With the rapid development of semiconductor manufacturing processes and materials, the internal structure of memory has gradually shifted from 2D planar packaging structures to 3D packaging structures. Well-known memory manufacturers, such as Samsung Electronics, Micron, and SK hynix, have further improved the performance of memory devices via the use of 3D packaging technologies, such as PoP (package on package) [1–3], CoC (Chipon-Chip) [4–6], WLP (Wafer Level Package) [7–9], TSV (through-silicon via) [10–12], and Embedded Substrate [13–15], meeting the industry demands for high-frequency, high-speed, and large-capacity devices with low power consumption.

This review first introduces the structural characteristics of different 3D packaged memories. We then analyze the reasons for typical stresses that lead to failures in 3D packaged memory systems and the corresponding thermal, mechanical, and hygrothermal theories. Additionally, this review summarizes solder–joint fatigue life prediction models, focusing on their theoretical bases, applications, advantages, and disadvantages. Next, this review summarizes the research results of memory systems with CoC and PoP structures under mechanical stress, temperature stress, and hygrothermal stress loadings. Finally, we suggest future directions for researching the reliability of 3D packaged memories. This review suggests building a comprehensive research platform to facilitate software and

hardware integration, establishing multi-dimensional simulation models, fully combining simulation results with experimental results to improve the accuracy of predictions, and conducting experimental research in high-stress environments to fully understand the applicability and limitations of memory devices.

#### 2. 3D Packaging Structure of Memory

The feature size of the traditional Moore's Law approaches the physical limits of what semiconductor technology is able to withstand, and simply reducing the feature size of 2D packaging is no longer a feasible way to meet market demands and develop new technologies. As products that adhere to Moore's Law, three-dimensional packages have become a strong contender for the development of new technology. Three-dimensional packaging mainly comprises a vertical interconnection of multi-layer structures in the Z direction, stacking multiple chips or two-dimensional packages to achieve a higher assembly density, higher system performance, and a greater number of I/O pins [16,17]. There are two main ways to formulate a 3D packaging structure: 3D CoC (ChIP-on-Chip) and 3D PoP (package on package).

## 2.1. CoC (ChIP-on-Chip) Structure

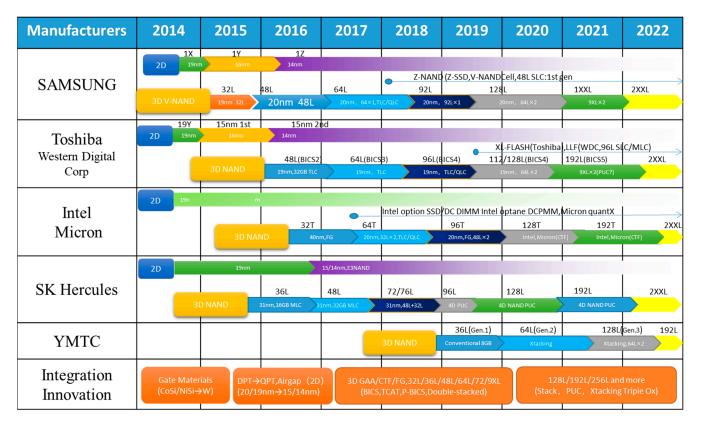

The standard way to increase memory capacity is to stack the same type of memory chips in the same package and interconnect them using wire bonding (WB) and throughsilicon via (TSV). Importantly, 3D NAND constitutes the most common 3D submarket in the industry and is most typically representative of CoC structures. Its layer-stacking technology can increase density by adding storage unit layers in a vertical direction [18,19]. The number of stacked layers is the most intuitive performance indicator in 3D NAND products. Thus, producing more than 200 layers of 3D NAND products has become a new goal for leading international memory manufacturers [20,21]. Compared to microprocessors, NAND production has improved processing limitations and led to the exploration of new ways of continuing to implement Moore's Law. As early as 2014, Toshiba and SanDisk launched the first batch of NAND chips with 15 nm process technology [22,23], some of the smallest flash memory chips produced at that time, indicating that 2D NAND was approaching its processing limit. Since then, 3D NAND has become the preferred technology in the NAND industry due to its increased capacity and reduced costs, driven by manufacturers such as Samsung Electronics and Micron. Samsung Electronics, SK hynix, and Micron successively released 128-layer TLC 3D NAND devices in 2019 [24–26] and 176-layer TLC 3D NAND devices in 2020 [27,28]. In 2020, Kioxia released a 112-layer 3D NAND [29]. YANGTZE MEMORY in China has maintained a similar pace as international manufacturers, releasing a 64-layer 3D NAND in 2019 and bypassing a 96-layer [30] 3D NAND to launch a 128-layer 3D NAND in 2020 [31], which then became widely established in Xtacking architecture. Figure 1 shows a 3D NAND roadmap [32].

The internal structure of CoC packaging is mainly interconnected via two processes: WB (wire bonding) and TSV (through-silicon via), which are described below.

## 2.1.1. WB Interconnecting Structure

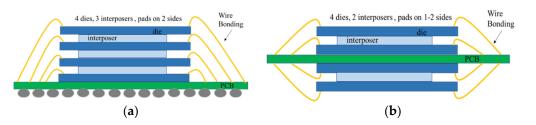

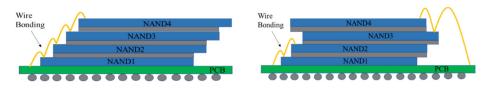

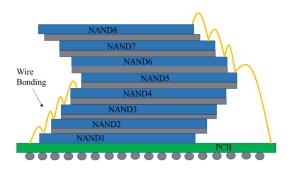

A 3D NAND device with a WB process can be approximately divided into the following five typical CoC structures [19]. (1) Spacer CoC structure: A passive silicon wafer is added between two chips with the same area as a spacer to form an overhang structure between the upper and lower layers of chips, leaving enough space for wire bonding to a solder pad (Figure 2a). However, using a spacer increases the height of the memory device, which affects its assembly density. (2) Double-sided spacer CoC structure: Chips and spacers are mounted on both sides of the PCB (Figure 2b) to reduce the negative impact of the spacer on the height of the device. However, this leads to more complex chip design, especially in the solder pad area. (3) Stair-shaped CoC structure: Chips with the same area are mounted without spacers and sequentially bonded with an insulating adhesive (Figure 3). This structure ensures the mechanical reliability of the chips, since their non-overlapping area is minimal compared to their length. Thus, the overall mechanical strength is not affected, and the top-layer chip will not exceed the overall center of mass. However, all solder pads must be located on the same side of the package, increasing the area on the opposite side of the solder pads. (4) Snake-shaped CoC structure: As another optimization solution for stair-shaped CoC structure, the overall size can be significantly reduced due to double-sided chip mounting (Figure 4). (5) Hybrid interconnecting process CoC structure: This CoC structure is similar to stair-shaped and snake-shaped structures but different in the interconnection direction of the upper and lower layers of the chips (front mounting and back mounting). The CoC structure is achieved by combining wire bonding and flip–chip interconnection or by using flip–chip interconnection alone (Figure 5).

Figure 1. Three-dimensional NAND roadmap from TechInsights.

Figure 2. Stack structure: (a) Standard die stacking; (b) flipped die stacking.

Figure 3. Staircase die stacking.

Figure 4. Double-stair die stacking

**Figure 5.** Double-stair die stacking: (a) top chip bonding and flip–chip solder ball interconnection; (b) inverted solder ball interconnection; (c) bottom chip bonding and flip–chip solder ball interconnection.

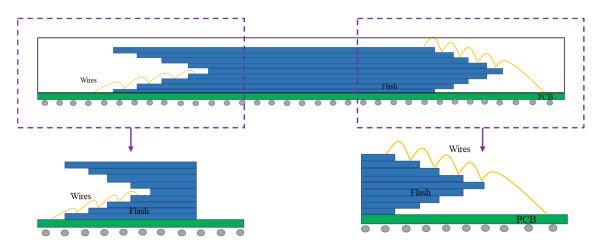

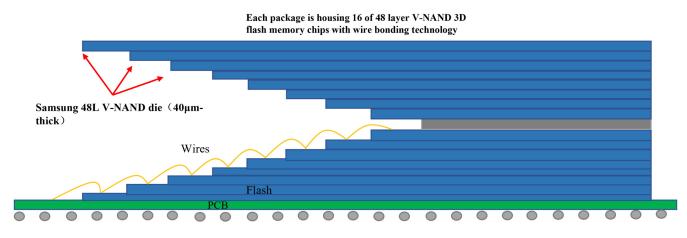

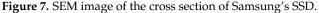

Figure 6 is a cross section of Samsung's 3D NAND device manufactured for the Apple iPhone, with a package thickness including a substrate of only 0.93 mm, a CoC height of 670  $\mu$ m, and a chip thickness ranging from 55 to 70  $\mu$ m, with the thickest chip located at the bottom [33]. Figure 7 shows Samsung's solid-state drive (SSD), in which 16-layer and 48-layer V-NAND 3D flash memory chips are stacked using wiring bonding technology; each chip is only 40  $\mu$ m thick and is stacked on an organic packaging substrate [33].

Figure 6. 3D NAND chips with CoC structures made via the WB process.

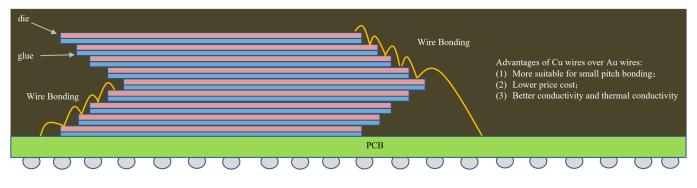

In the early days, the lead material in the WB process was mainly Au wire. However, due to the high cost of Au wire, and with the development of bonding technology for Cu and Al wire [34] (Figure 8), over 50% of the Au wire in the CoC interconnect structure has gradually changed to Cu, Al, and even Ag wire [35–37].

However, in traditional WB processes, it is necessary to maintain the ladder-like CoC structure of the memory chips and the bonding pad area on the packaging substrate after the 3D NAND memory chips are stacked into a ladder shape. Therefore, the number of stacked memory chips is limited, which indicates that storage capacity is restricted.

Figure 8. Characteristics of wire-bonding materials.

#### 2.1.2. TSV Interconnection Structure

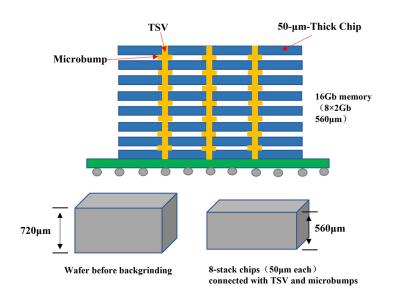

To further adhere to Moore's Law, TSV technology has become a driving force for the development of 3D NAND products. The vertically stacked memory chips are electrically interconnected to each other via filling them with conductive materials, such as copper, tungsten, or polysilicon, or using metal-metal bonding to achieve silicon via holes. The bottom layer of the memory chip is connected to the packaging substrate via a metallized wiring layer and solder. Since there is no demand for interconnections with the bonding pad of the packaging substrate, the number of stacked memory chips can be increased. Compared with traditional WB, TSV technology has fewer restrictions, and it can further reduce signal delay and parasitic capacitance/inductance, achieve a low power consumption and high transmission rate, increase bandwidth, and realize product miniaturization. Although TSV technology has these advantages, it reduces the wafer area utilization and relative processing time of 3D NAND devices. Samsung Electronics used TSV and microbumps to release a 16 Gb memory (including eight pieces of 2 Gb memory chips) in 2006. The thickness of this stacked chip was 560  $\mu$ m, smaller than the traditional 720  $\mu$ m chip at that time. The stacked chips can either be NAND chips or DRAM chips [34], as shown in Figure 9.

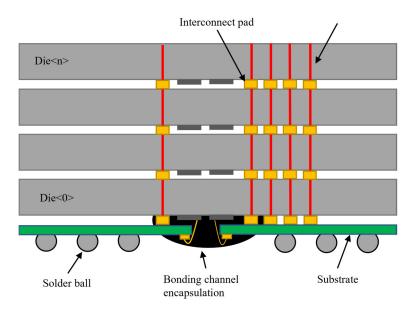

In 2015, Toshiba released its first NAND product based on Bit Cost Scalable (BiCS) architecture, which was manufactured using a 48-layer stacked 3D NAND process combined with TSV technology. Although the number of stacked chips is maintained at 8 or 16 layers, the product was capable of providing a single capacity of 512 GB or 1 TB, indicating that the capacity of a single chip was 512 Gbit (64 GB) [19], as shown in Figure 10.

Figure 9. Samsung's memory chip stack.

Figure 10. Die stacking using TSV technology.

## 2.2. Package-Stacking Structure

Package stacking is an effective solution to the challenges involved with gradually reducing the size, cost, signal interference, and delays of chip devices. It also contributes to the low power consumption, high-speed information processing capacity, and large storage capacity of chips, which can improve interconnection efficiency and bandwidth. Package stacking can be divided into two main types: PiP (package-in-package) [38] and PoP (package-on-package) [39]. PoP is a 3D packaging technology that stacks two known good dies together. Since both the bottom logic device and the top memory device follow JEDEC's electrical and mechanical standards, this standardized design enables different manufacturers to quickly design and produce products that are compatible with each other, achieving efficient package-stacking combinations. As a new packaging technology, PoP achieves a higher number of vertically stacked single (or various types of) devices on the basis of existing, compatible, standard surface mount technology, which can increase PCB assembly density and reduce production costs. Thus, it is rapidly becoming the preferred packaging method for many core components of smart portable electronic products, such as mobile phones, desktop computers, and smart watches. PoP technology was used in several Apple iPhones, from the iPhone 1 in 2007 to the iPhone 13 in 2021. In the Apple iPhone 12, the A14 processor made from a TSMC current sheet is stacked with Micron LPDDR4X SDRAM [40]. The widespread application of PoP technology has brought tremendous demand for PoP packaging devices. In 2021, global sales of high-end smartphones increased by 24% compared to those in the previous year, with a year-on-year increase of 7%. This strong market demand has further driven the continuous innovation and development of PoP technology.

#### 2.2.1. PoP Structure

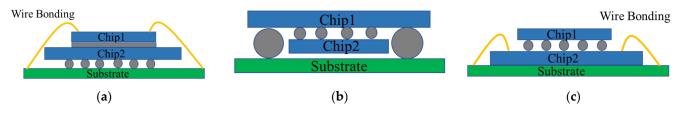

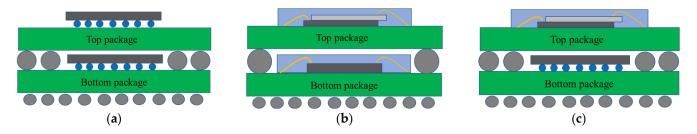

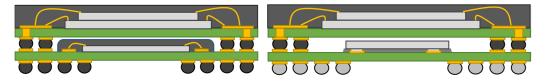

According to different interconnection modes inside the top and bottom stacked devices, PoP packaging can be divided into three typical structures: WB (wire bonding), flip–chip interconnection, and WB and flip–chip interconnection [41], as shown in Figure 11.

**Figure 11.** PoP structure: (**a**) WB (wire bonding); (**b**) flip–chip interconnection; (**c**) WB and flip–chip interconnection.

First-generation PoP technology typically integrates a baseband or application processor device and uses either a center gate mold or an exposed flip–chip die structure. A top single or combination memory package typically uses a peripheral two-row array of solder balls for stacking or the memory interface, using a ball diameter and pitch sufficient to provide a stacking clearance on the center mold or FC die [42], as shown in Figure 12.

Figure 12. First-generation PoP stacked structures.

Nokia and Amkor played key roles in the development of the first generation of PoP technology and reported early research on this technology at the 2003 ECTC conference [43]. ST Microelectronics was an early adopter of PoP for both memory systems and mobile processors. The background and history of the commercialization of first-generation PoP technology are summarized in a June 2007 article written by Smith and published in *Semiconductor International* [42].

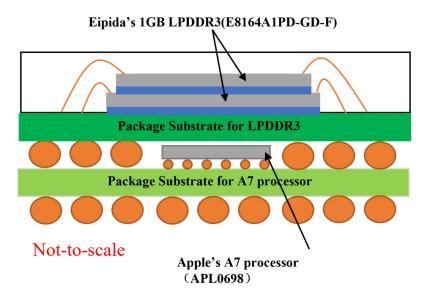

Due to the vertical soldering interconnection between the two layers of PoP packaging, the Z direction is fully utilized to further reduce circuit PCB area to achieve a high packaging density. Moreover, a single packaging body can realize multiple functions. Figure 13 shows a typical application of a logic device and a memory device combination in a PoP package used in the Apple iPhone 5s [44]. The top package is a 1 GB LPDD3 RAM chip (11 mm × 7.8 mm) developed by Elpida (now Micron), which is internally interconnected using wire bonding via three rows of 456 solder balls in the FBGA (fine-pitch ball grid array) package substrate. The bottom package is a 64-bit A7 processor chip (10 mm × 10 mm), which is interconnected through  $38 \times 34 = 1292$  solder ball bumps on the packaging substrate.

**Figure 13.** Top-view and cross-sectional view of PoP chip (for mobile DRAM and application processor (A7)) inside an iPhone 5s.

PoP packaging technology has been continuously developed and improved over the past decade in several different aspects. (1) Stricter control of warpage [45,46]: Due to the decreasing proportion of the packaging shell to the chip size (increasing in area) and the further improvement of system integration, warpage has become a more prominent issue and thus needs to be controlled. (2) More advanced interconnection methods: To reduce signal interference and transmission delay, traditional WB has gradually been replaced by flip–chip and copper pillar technologies. (3) Continuous reduction in structural size [47]: Firstly, the spacing between interconnections has been continuously reduced. Specifically, the spacing between the bottom packaging solder balls has been reduced to 0.5–0.2 mm, and the spacing between the top solder balls has gradually been reduced from 0.65 mm to 0.4 mm [48]. Secondly, the thickness of each layer of packaging material has been continuously reduced. The thicknesses of the substrate, EMC (epoxy molding compound), and the chip have been reduced from 0.3 mm to 0.13 mm, from 0.28 mm to 0.15 mm, and to below 0.1 mm, respectively.

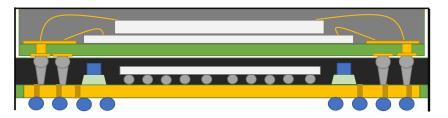

Driven by the above trends, Amkor successively developed PSfcCSP (Package-Stackable Flip Chip Chip Scale Package) and TMV (Through-Mold-Via) technologies (as shown in Figure 14) [49] based on the traditional PSvfBGA (Package-Stackable Very Thin Fine Pitch BGA) technology [50].

Figure 14. PoP assembled using TMV technology.

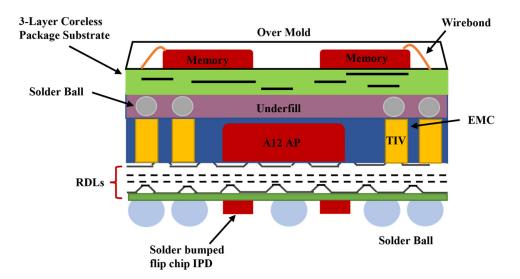

TMV technology can penetrate molding compounds at the upper and lower interconnection welding points in a through-hole via, with the welding column vertically connected to the upper and lower packages for interconnection. The technology can not only reduce packaging warpage via plastic packaging materials but also further reduce the interconnection spacing between upper and lower solder balls by relying on the support and spacing of plastic packaging. The development of advanced, next-generation FOWLP (Fan-Out Wafer-Level Package) technology [51] has fully addressed the shortcomings of the above technologies and been gradually applied in PoP packaging [44] (as shown in Figure 15). This technology often uses a rewiring layer on both sides of the package and a through-hole via to penetrate the plastic fan-out area at the package edge, reducing the package thickness to approximately 0.25 mm. Meanwhile, a high-density encapsulated interface technology with a pitch of less than 0.4 mm is applied to place multiple chips inside the package side by side, and to reduce the package spacing to about 0.15 mm. Ultra-thin PoP modules with a size of less than  $12 \times 12$  mm and a height of less than 1.0 mm can be obtained using this technology.

Figure 15. TSMC/Apple's PoP for their AP A12 with InFO-WLP.

#### 2.2.2. PiP Structure

PiP (package in package) is a 3D packaging technology, also known as cube packaging technology, in which several known good devices are stacked in the same packaging cavity via a vertical welding interconnection. The manufacturer, 3D-Plus Ltd. (Versailles, France), has applied PiP technology to develop a radiation-resistant, large-capacity, and high-reliability 3D PiP memory for Galileo Program and other aerospace and aviation applications [52]. In 2001, it passed assessments by the ESA (European Space Agency), the CNES (Centre National d'Études Spatiales), NASA (National Aeronautics and Space Administration), and GSFC (Goddard Space Flight Center), with typical reliability test items shown in Tables 1 and 2 [53].

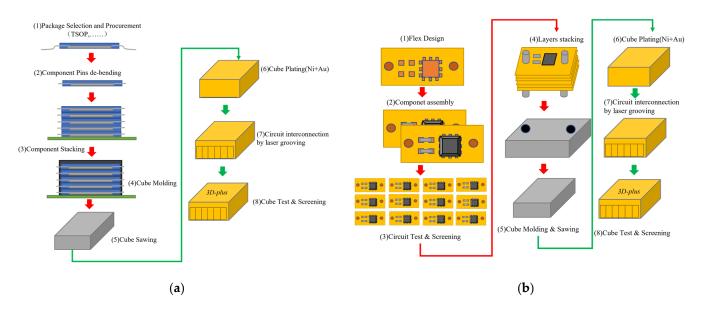

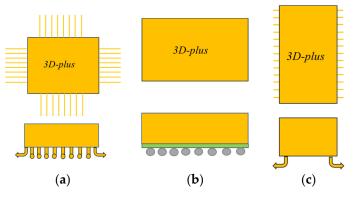

The following technical process is shown in Figure 16. First, n-layer multi-device stacking and molding are carried out on two-dimensional packaging memory devices that have passed the test. Epoxy resin is then used for the casting mold, and the trim is cut off after the epoxy resin curing. After that, the packaging shell is sequentially electroplated, interconnected using laser grooves, surface coated, and pin molded. Finally, a large-capacity 3D PiP memory is formed [54,55]. The packaged 3D memory has a variety of packaging forms, such as SOP, QFP, and BGA (as shown in Figures 17 and 18) [56,57]. This is mainly due to other types of internal encapsulated devices and the demand for different numbers of I/O devices.

| No. | Test Items                                | Test Method                                                                   | Remarks                                                                                                    |

|-----|-------------------------------------------|-------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| 1   | Thermal cycles under vacuum               | 10 <sup>-6</sup> Torr<br>10 Cycles –40 °C/+70 °C, 2 °C/min,<br>1 h par palier | /                                                                                                          |

| 2   | Electrical tests                          | Electrical tests at -55 °C/+25<br>°C/+125 °C                                  | /                                                                                                          |

| 3   | Thermal cycles                            | 500 cycles<br>—55 °C/+125 °C<br>10 °C/mn, 15 mn par palier                    | External visual inspection<br>and electrical tests<br>-55 °C/+25 °C/+125 °C<br>at 100, 300, and 500 cycles |

| 4   | Temperature and<br>humidity<br>under bias | 1000 h<br>+85 °C and 85% RH                                                   | External visual inspection<br>and electrical tests<br>-55 °C/+25 °C/+125 °C<br>at 240, 500, and 1000 h     |

| 5   | Life test or high-temperature<br>storage  | 2000 h<br>+125 °C                                                             | External visual inspection<br>and electrical tests<br>-55 °C/+25 °C/+125 °C<br>at 500, 1000, and 2000 h    |

| 6   | Power cycling                             | 30,000× ON/OFF<br>120 s ON (+110 °C)<br>60 s OFF (+40 °C)                     | External visual inspection<br>and electrical tests<br>-55 °C/+25 °C/+125 °C<br>at 15 K and 30 K O/O cycles |

Table 1. ESA and CNES test plan (part).

Table 2. NASA GSFC Test Plan (part).

| No. | Test Items                                | Test Method                                                            | Remarks         |

|-----|-------------------------------------------|------------------------------------------------------------------------|-----------------|

| 1   | Thermal conditioning                      | +125 °C, 48 h                                                          | /               |

| 2   | Voltage conditioning                      | +125 °C, 320 h                                                         | /               |

| 3   | Thermal characterization                  | 14 steps of 20 °C between $-55$ °C to 125 °C                           | /               |

| 4   | Temperature and<br>humidity<br>under bias | 620 h<br>+85 °C and 85% RH                                             | C-SAM and X-ray |

| 5   | Mechanical shock                          | MIL-STD-883 Method 2002<br>200 G, 0.5 ms                               | /               |

| 6   | Sine vibration                            | MIL-STD-202 Condition A<br>10 G to 22.5 G                              | /               |

| 7   | Random vibration                          | MIL-STD-883 Method 2026<br>Condition E (16.4 G)<br>Condition B (7.3 G) | /               |

This type of 3D PiP memory has strong anti-vibration and impact resistance, because the internal laminated units are fixed with epoxy resin. The surface of the packaging shell is plated with Ni/Au, with thicknesses of 1–2  $\mu$ m for the gilded layer and 3–5  $\mu$ m for the nickel plating layer. This metal plating can effectively reduce the invasion of water vapor or other harmful gases into the package. Moreover, the operating temperature range of this product can reach up to -55–125 °C, which is far larger than that of industrial/commercial 3D packaging memory products. In addition, its anti-radiation indicators, such as TID (total ionizing dose), SEL (Single-Event Latchup), and SEU (Single-Event Upset), also meet the requirements of relevant space missions, such as NASA's Rover and China Aerospace

Chang'e-5. Therefore, the 3D PiP memory developed by 3D-Plus Ltd. (Versailles, France) is widely used in various high-reliability fields.

Figure 16. Manufacturing process: (a) TSOP stacking process; (b) flex stacking process.

**Figure 17.** The manufacturing of a 3D memory package for a satellite: (**a**) stack of 6 QFPs with QFP I/Os; (**b**) stack of 4 BGAs with BGA I/Os; (**c**) stack of 4 SOPs with SOP I/Os.

3D PLUS 3DSP21020 Comvuter Module embedding the ATMEL TSC21020F Floating Point DSP + SRAM, SDRAM, FLASH and PROM Memories + CO processors FPGAs + for Space Application

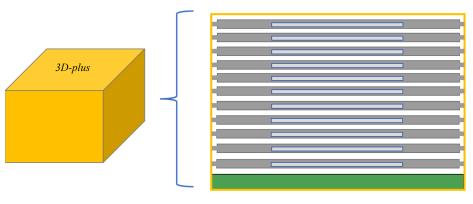

Figure 18. A 3D PLUS 3DSP21020 computer module (showing 11 integrated layers).

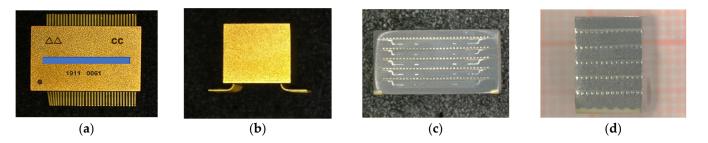

In addition to 3D-Plus Ltd. (Versailles, France), O.C.E Technology Ltd. (Dublin, Ireland) and Orbita Aerospace Ltd. (Zhuhai, China) have also developed similar memory products for high-reliability applications. For example, Orbita Aerospace Ltd. (Zhuhai, China) developed a 128 K  $\times$  40 EEPROM (electrically erasable programmable read-only memory), which is composed of a lead frame layer and five chip layers. Specifically, external connection pins are arranged on the lead frame layer, and a memory device of the same type (128 M  $\times$  8 bit) is stacked on each chip layer. Five CSs (chip selects) of the internal device are simultaneously connected to an external pin of the chip, and other control and address signals are interconnected with each other and then to the external pin of the chip. Five sets of 8-bit data lines are led out independently. Finally, after the gilded connecting lines on the external surface are encapsulated and cut, the chip layer of the built-in device and the pin wiring of the lead frame layer are connected into a 3D-packaging 128 K  $\times$  40 bits SOP64-pin memory module. Its typical structural features are shown in Figures 19 and 20.

**Figure 19.** A 128 K  $\times$  40 EEPROM device: (a) front morphology; (b) lateral morphology; (c) slice section in X direction; (d) slice section in Y direction.

Figure 20. A 128 K  $\times$  40 EEPROM device: (a) internal structure; (b) 5-layer stacking.

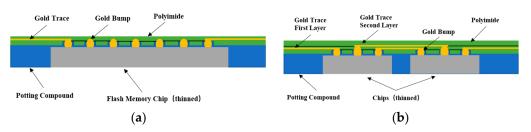

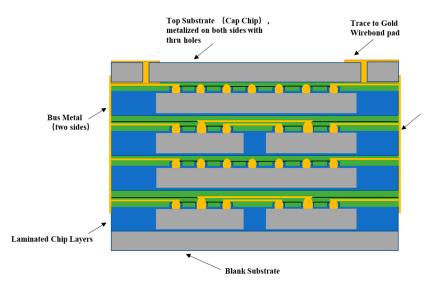

For 3D memory modules encapsulated with epoxy resin, the NEO-stacking technology developed by Irvine Sensors Corporation can be used to stack chips of different sizes and types layer by layer [55] (as shown in Figure 21). The chip bumps (input/output ports) are rewired to both sides of the module through metallized film on known good devices. A passivation layer is deposited on the surface of the chips with polyimide, and then the chips are thinned and cut. After that, the multi-layer chips are stacked with adhesive and then pressed between the top and bottom ceramic substrates (aluminum oxide) [55], as shown in Figure 22. The rewired input/output ports are exposed on both sides of the lapping and polishing stack structure, and then the electroless plating process is used to form a coating (Cu/Ni/Au) on the stack structure. Finally, laser grooving is used to realize the electrical interconnection between the interior and the package or substrate [58].

Figure 21. NEO layer of Irvine sensors: (a) single die; (b) two dies.

Figure 22. Cube created from stack of NEO layers.

## 3. Failure Reason Analysis of 3D Packaging Memory

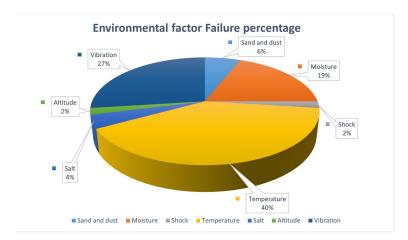

During manufacturing and usage, 3D packaged memory modules are usually subjected to environmental stresses, such as thermal stress, mechanical stress, and hygrothermal stress. They are also exposed to cosmic radiation if used in space. According to the statistics from The Electronic Failure Analysis Handbook, 40% of the electronic component failures are caused by temperature changes, 27% by vibration, 19% by moisture, 6% by sand and dust, 4% by salt, 2% by shock, and 2% by altitude [59]. As shown in Figure 23, among the four factors affecting the reliability of electronic components, temperature, and vibration account for 69% of failures. The typical failure modes of electronic components under environmental stress are shown in Table 3.

Figure 23. Distribution of failure categories of electronic components.

| Typical Environmental Stress | Test Item                           | Typical Failure Mode                                                                                                                                   |

|------------------------------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

|                              | High temperature<br>Low temperature | Functional performance failure, material degradation.<br>Functional performance failure, material degradation.                                         |

| Temperature stress           | Thermal shock                       | Functional performance failure, mark shedding, shell coating fading, delamination.                                                                     |

|                              | Temperature cycling                 | Functional performance failure, mark shedding, shell coating fading, delamination.                                                                     |

|                              | Steady damp heat                    | Mark shedding, corrosion, functional performance failure, delamination, etc.                                                                           |

| Hygrothermal stress          | Pressure cooker                     | Mark shedding, pin breakage, internal filler precipitation, corrosion, functional performance failure, delamination, etc.                              |

|                              | Shock                               | Pin fracture or crack, ceramic body fracture or crack, cover<br>plate leakage, glass insulator crack, bonding wire fracture or<br>collapse, etc.       |

| Mechanical stress            | Vibration                           | Pin fracture, ceramic body fracture or crack, cover plate<br>leakage, glass insulator crack, bonding wire fracture or<br>collapse, etc.                |

|                              | Constant acceleration               | Functional performance failure, chip detachment, bonding<br>wire lead detachment or collapse, cover plate leakage, shell<br>fracture or cracking, etc. |

Table 3. The typical failure modes of electronic components under environmental stress.

## 3.1. The Influence of Thermal Stress on Reliability

Thermal stress usually refers to the change in thermal load caused by welding and ambient temperature. As most packaging materials are composed of multiple different materials, the differences in thermal expansion coefficients among the substrate, lead, chip, and epoxy resin of the device will cause thermal expansion and contraction, corresponding to the thermal expansion coefficient between different materials. However, due to the external packaging constraints or internal deformation coordination requirements, this cannot occur freely, and internal thermal strain produces delamination or cracks in the device [60,61]. In the interconnected structure of a 3D packaging memory device, in addition to the thermal expansion mismatch between adjacent materials, the internal stress and microstructure of the chip bump and solder joint are prone to changes under an environment of periodic alternating high–low-temperature or extreme-temperature gradients. This will lead to the accumulation of stress and strain inside the device, ultimately causing cracks or thermal fatigue failure in the solder joints [62,63].

## 3.2. The Influence of Mechanical Stress on Reliability

Mechanical stress usually refers to dynamic loads such as dropping, constant acceleration, vibration, and shock, which can lead to mechanical damage, such as the cracking and brittle fracture of products. Especially for electronic equipment components in aerospace fields such as space launch vehicles, missiles, and aircrafts, sine vibration during the launch process can reach up to 20 g [64]. Whether the structure and material strength of the device can withstand mechanical stress without damage and failure is a key factor affecting its reliability. Meanwhile, the 3D packaged memory mounted on the PCB or the substrate is subjected to vibration loads when vibration acts on the PCB, causing it to undergo a large bending dynamic deformation and exerting great mechanical cyclic stress on the interconnected solder joints. This mechanical stress will lead to mechanical damage and the fracture of the solder balls. For PoP memory, the vibration load acting on the PoP package can cause a large relative displacement between the upper and lower ends of the bottom solder ball, which makes the bottom solder ball bear the cyclic tensile stress of stretch–shrink mechanisms, similar to the spring oscillator. This tensile stress will lead to fatigue damage of the bottom solder ball [65]. It is noted that when the package is subjected to both dynamic and thermal loads, their interactions can accelerate crack propagation, greatly reducing the service life of the products.

#### 3.3. The Influence of Hygrothermal Stress on Reliability

Industrial/commercial 3D packaging memory devices are mainly made from molding compounds, whereas aerospace or military 3D packaging memory devices are mainly made from metal or ceramic materials. Molding compounds are more hygroscopic than metal or ceramic materials; therefore, moisture has a greater impact on industrial/commercial 3D packaging memory devices and can change the distribution of thermal stress in these devices. Moreover, process-induced defects can make moisture more likely to enter the inside of the device via the small cracks forming along the device pins or the interface between the substrate and the plastic package. In particular, a high temperature will accelerate the penetration of moisture. Thus, moisture is one of the main reasons that plastic packaging devices were banned in early aerospace equipment. Generally, these devices are prone to galvanic cell corrosion and electromigration, which will potentially cause functional failures, such as short-circuit and open-circuit failures [66]. From a local perspective, moisture reduces the adhesive strength of various material interfaces, making interlayer delamination or cracking more likely to occur. Furthermore, the moisture inside the device can be converted into steam pressure during high-heat treatments (such as baking and reflow soldering), causing the generation of gas-induced cracks [67].

## 4. Reliability Theories for 3D Packaging Memory

A large number of studies address the reliability of 3D packaged memory devices based on the effects of thermal stress, hygrothermal stress, and mechanical stress.

## 4.1. Theories of Hygrothermal Stress on Reliability

Studies of hygrothermal stress mainly focus on moisture diffusion and wet stress distribution [68–70].

#### 4.1.1. Moisture Diffusion

Moisture mainly enters the interior of the device package via a diffusion mechanism. Diffusion flux is defined as the material flow per unit of area passing vertically in a specific direction in unit time. Based on the relationship between diffusion flux and time, diffusion can be classified as steady state (unchanging with time) or unsteady state (changing with time). In 1855, A. Fick proposed Fick's First Law, which states that the diffusion flux per unit area perpendicular to the diffusion direction is proportional to the concentration gradient at that point [71], formulated as follows:

$$J = -D\frac{dC}{dx} \tag{1}$$

where *J*, *D*, *C*, and *x* denote diffusion flux (kg/m<sup>2</sup>·s), diffusion coefficient (m<sup>2</sup>/s), concentration of the diffusate (kg/m), and diffusion distance, respectively. dC/dx is the concentration gradient of the diffusate. The negative sign indicates that the diffusion direction is opposite to the concentration gradient. In other words, diffusion occurs upon movement from a high-concentration area to a low-concentration area. The diffusion coefficient *D* is an important physical quantity that describes the diffusion rate and is equivalent to the diffusion flux when the concentration gradient is 1. The larger the value of *D*, the faster the diffusion.

However, Fick's First Law is only applicable to steady-state diffusion situations where the diffusion flux does not change with time [71]. In fact, the diffusate concentration changes with time during the diffusion process, and most diffusion processes occur under unsteady conditions, where  $dC/dx \neq 0$ . In order to study unsteady diffusion, Fick's

Second Law [71] was derived based on the theory of diffusion concentration equilibrium, formulated as follows:

$$\frac{\partial C}{\partial t} = \frac{\partial}{\partial x} \left( D \frac{\partial C}{\partial x} \right) \tag{2}$$

where *C* is the diffusate concentration, which is also the distribution function of moisture concentration related to the spatial location (x, y, z) and time *t*, i.e., C = C(x, y, z, t). For three-dimensional diffusion problems, Fick's Second Law is formulated as follows:

$$\frac{\partial C}{\partial t} = \frac{\partial}{\partial x} \left( D_x \frac{\partial C}{\partial x} \right) + \frac{\partial}{\partial y} \left( D_y \frac{\partial C}{\partial y} \right) + \frac{\partial}{\partial z} \left( D_z \frac{\partial C}{\partial z} \right)$$

(3)

Since  $D_{xx} = D_{yy} = D_{zz} = D$  for the isotropic material, Equation (3) can be simplified as follows:

$$\frac{\partial C}{\partial t} = D\left(\frac{\partial^2 C}{\partial x^2} + \frac{\partial^2 C}{\partial y^2} + \frac{\partial^2 C}{\partial z^2}\right) \tag{4}$$

Due to various hygrometric coefficients of different materials, *C* at the junction of materials is discontinuous [72,73]. The concept of relative humidity  $W = C/C_{sat}$  ( $C_{sat}$  is saturated humidity) is commonly employed in research [74]; it is continuous at the junction of materials and follows Fick's Second Law. Thus, Equation (4) is transformed as follows:

$$\frac{\partial W}{\partial t} = D\left(\frac{\partial^2 W}{\partial x^2} + \frac{\partial^2 W}{\partial y^2} + \frac{\partial^2 W}{\partial z^2}\right)$$

(5)

Since moisture diffusion and heat conduction share similar characteristics and follow the same mathematical control equations, temperature and thermal conductivity in the heat transfer equation correspond to moisture concentration and diffusion coefficients in moisture diffusion, respectively. Their analogous relationship [74] is shown in Table 4 [74]. Therefore, a thermal analysis module in finite element software can be used to analyze moisture diffusion, which can be used to calculate the moisture diffusion distribution of the device packaging model. This calculated moisture diffusion distribution can be applied as a moisture load to a packaging model to measure the distribution of moisture stress.

Table 4. Thermal humidity correspondence relationship in moisture diffusion analysis.

| Characteristic         | Heat Diffusion                          | <b>Research Conclusion</b>                                            |

|------------------------|-----------------------------------------|-----------------------------------------------------------------------|

| Variable               | Temperature                             | Relative humidity (W)                                                 |

| Conductivity           | $\lambda (W \cdot m^{-1} \cdot K^{-1})$ | $D \cdot C_{sat} (\text{kg} \cdot \text{s}^{-1} \cdot \text{m}^{-1})$ |

| Specific heat capacity | $c (J \cdot kg^{-1} \cdot K^{-1})$      | $C_{sat}$ (kg·m <sup>-3</sup> )                                       |

## 4.1.2. Moisture Stress Distribution

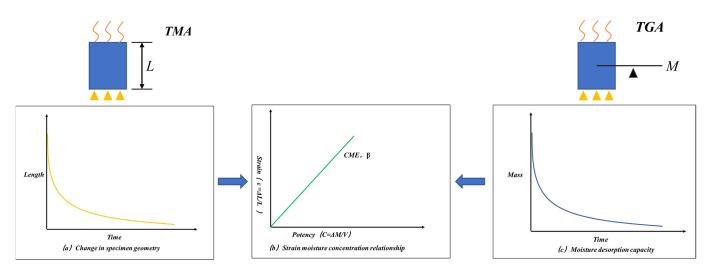

Generally, it is believed in the industry that water molecules absorbed by polymer materials exist in two forms [75]. One is in a free state, where free water molecules exist in the micropores of polymer materials. The other is the bound state, where hydrogen bonds are formed between the water molecular chain and polymer molecular chain in order to bind water molecules. Ardebili et al. identified two distinct modes of moisture absorbed in epoxy-like polymer materials using NMR spectroscopy [76]. Liu et al. confirmed hydrogen bonding between internal water molecules and epoxy resin by analyzing the infrared spectrum of epoxy resin in a high-temperature and high-humidity experiment [77]. Wong et al. analyzed the moisture expansion of polymer materials under the same test conditions for two identical products using a TMA (thermal mechanical analyzer) and TGA (thermal gravimetric analyzer). In order to measure the moisture absorption parameters of the fillers under a packaging molding compound together, two identical samples were pre-treated under the same humidity/temperature conditions in the experiment and then placed in a high-temperature furnace for high-temperature desorption. During the process,

TGA was used to measure the loss of sample mass, whereas TMA was used to measure changes in sample geometry. Then, a relationship diagram was drawn between the strain and moisture concentration. The linear relationship between the two is known as the moisture expansion coefficient of materials [78]. In other words, the slope in Figure 24 refers to the moisture expansion coefficient  $\beta$  of polymer materials. The slope in Figure 24 represents the coefficient of moisture expansion (CME) of the polymer material, formulated as follows:

$$=\frac{\varepsilon}{C}$$

(6)

where *C* is the moisture concentration in the polymer material, and  $\varepsilon$  is the dependent variable of the sample. Wong et al. further verified Equation (6) according to experimental data and found that temperature *T* has no significant effect on the *CME* [79].

β

Therefore, after the moisture diffusion of a device is measured using finite element thermal analysis, the moisture stress distribution can be calculated via the *CME* and moisture diffusion coefficient *D* of the device material.

## 4.2. Theories of the Effect of Thermal Stress on Reliability

Studies on thermal stress mainly focus on the temperature field and thermal stress, whose goal is to calculate the temperature field and other thermal physical parameters of a system or component [80].

#### 4.2.1. Temperature Field

The temperature field refers to the overall distribution of temperature at all points in a material system in space (or within an object), which is a quantity field expressed by the quantity function of spatial coordinates (x, y, z) and time t as follows [80]:

$$T = f(x, y, z, t) \tag{7}$$

Equation (7) describes a three-dimensional non-steady-state (transient) temperature field, and thus three-dimensional non-steady-state (transient) heat conduction occurs in this temperature field. A steady-state temperature field is a temperature field that does not change with time, i.e., T = T(x, y, z), with three-dimensional steady-state heat conduction. For one- and two-dimensional temperature fields, a steady-state temperature field can be expressed as T = f(x) and T = f(x, y), respectively, and a non-steady-state temperature field can be expressed as T = f(x, t) and T = f(x, y, t), respectively.

In order to determine the temperature field within an object, a general equation for the temperature field, i.e., a differential equation of heat conduction, is required based on energy conservation, formulated as follows:

$$pc\frac{\partial T}{\partial t} = \frac{\partial}{\partial x}\left(k_x\frac{\partial T}{\partial x}\right) + \frac{\partial}{\partial y}\left(k_y\frac{\partial T}{\partial y}\right) + \frac{\partial}{\partial z}\left(k_z\frac{\partial T}{\partial z}\right) + q_v \tag{8}$$

where *p* and *c* are the density (kg/m<sup>3</sup>) and specific heat capacity (J/kg·K), respectively.  $k_x$ ,  $k_y$ , and  $k_z$  are the thermal conductivities (W/m·K) in the *x*, *y*, and *z* directions, respectively.  $q_v$  is the heating rate (W/s) of the internal heat source. If there is no internal heat source within the object, Equation (8) can be rewritten as follows:

$$pc\frac{\partial T}{\partial t} = \frac{\partial}{\partial x}\left(k_x\frac{\partial T}{\partial x}\right) + \frac{\partial}{\partial y}\left(k_y\frac{\partial T}{\partial y}\right) + \frac{\partial}{\partial z}\left(k_z\frac{\partial T}{\partial z}\right)$$

(9)

Currently, the temperature field of a 3D packaging memory device can be formulated as a function achieved via finite element analysis, including the differential equation of heat conduction, boundary conditions, and initial conditions.

#### 4.2.2. Thermal Stress

When the temperature of an object changes, thermal stress occurs due to the mutual constraints between the object and other objects that cannot freely expand or contract, or between different parts within the object. This is a type of stress caused by non-external forces, with temperature changes and constraints as its fundamental causes. The constraints can be classified into external deformation constraints, mutual deformation constraints, and internal deformation constraints. The internal structure of a 3D packaged memory is composed of chips, bonding wires, bumps, solder balls, substrates, and epoxy resin. Due to their different coefficients of thermal expansion, they are mutually constrained to each other as a whole device. When the device temperature changes, thermal stress will inevitably occur within the device. Stress is generated when thermal deformation cannot freely occur due to constraints or uneven temperature changes in various components of the device. Therefore, the device cannot completely expand and contract in a free manner, resulting in thermal stress due to the mismatch of thermal expansion coefficients of various materials, the uneven temperature transfer of the device, as well as its internal and external constraints. This linear strain can be regarded as the initial strain of the device. The equivalent nodal load (i.e., temperature load) can be calculated according to the initial strain. The nodal displacement induced by the thermal deformation can be obtained for thermal stress by solving the stress equation. Additionally, the comprehensive stress involving thermal stress can be achieved via a combination of the equivalent nodal load and other load terms. The thermal stress  $\sigma$  is described as follows [81]:

$$\sigma = D(\varepsilon - \varepsilon_0) \tag{10}$$

where *D* is the elastic matrix determined by the elastic constant of element material,  $\varepsilon_0$  is the current temperature strain, and  $\varepsilon_0$  is the initial temperature strain. For three-dimensional problems,  $\varepsilon_0$  is:

$$\varepsilon_0 = \alpha \left( \emptyset - \emptyset_0 \right) [111000]^T \tag{11}$$

where  $\alpha$  is the linear expansion coefficient of the material.  $\emptyset$  and  $\emptyset_0$  are the current/initial temperature fields of the structure, respectively. Thus, the principle of virtual displacement can be formulated as follows [80]:

$$\int_{v} (\delta \varepsilon^{T} \sigma - \delta u^{T} \overline{f}) - \int_{S_{\sigma}} \delta u^{T} \overline{T} dS = 0$$

<sup>(12)</sup>

The minimum potential energy for the thermal stress problem is formulated as follows [80]:

$$\Pi_{p}(u) = \int_{\Omega} \left( \frac{1}{2} \varepsilon^{T} D \sigma - \varepsilon^{T} D \varepsilon_{0} - u^{T} f \right) d\Omega - \int_{\Gamma_{\sigma}} u^{T} \overline{T} d\Gamma$$

(13)

After the solution domain  $\Omega$  is performed by finite element discretization, the finite element equation can be obtained from  $\prod_{p} (u) = 0$  as follows:

K

$$a = P \tag{14}$$

where *K*, *a*, and *P* are the element node force matrix, node displacement, and node temperature load, respectively. Thus, temperature load caused by temperature change is formulated as follows:

$$P = P_f + P_T + P_{\varepsilon_0} \tag{15}$$

where  $P_f$  and  $P_T$  are the load terms caused by volume load and surface load, respectively.  $P_{\varepsilon 0}$  is the load term caused by temperature strain, formulated as follows:

$$P_{\varepsilon_0} = \sum_e \int_{\Omega} B^T D\varepsilon_0 d\Omega \tag{16}$$

## 4.3. Theories of Mechanical Stress on Reliability

The intrinsic characteristics (intrinsic frequency and vibration mode) of product structure are fundamental for dynamic research and analysis [82]. Mode analysis is carried out to obtain the intrinsic characteristics of product structure, such as intrinsic frequency and vibration mode, through which the relative changes in the positions of structural components under a vibration load can be calculated to determine the stress and response of the structure under a vibration load [82]. In practical engineering, mode analysis is commonly used for fixture analysis to avoid resonance. In research on mechanical stress, the known excitation force is applied to a product, which is the potential mechanical stress encountered in the operating environment and mainly entails random vibration, sinusoidal vibration, shock, and drop.

The response is measured to determine the dynamic characteristics of the product structure, such as the mode vector, damping, and frequency response. Compared with mode analysis, which focuses on the intrinsic characteristics of mechanical stress that are unaffected by external loads, the analysis of mechanical stress is closely related to external loads. A 3D PoP memory (PoP structure) device is a popular 3D packaged memory, which is commonly studied in the excitation modes of random vibration, sinusoidal vibration, and drop-induced shock.

#### 4.3.1. Random Vibration

Random vibration refers to the motion in which the vibration rule can only be measured using probability and statistical methods instead of definite functions (sine and step) [83,84]. Due to the excitation load of random vibrations that cannot be expressed by a definite time function, the power spectral density function is often used to describe this excitation in engineering [85,86]. Random vibration analysis is employed to analyze the dynamic response of the structure under random vibration loads. The input for random vibration is the PSD (power spectral density) function, indicating the energy distribution of random vibration excitation loads at different frequencies. The corresponding output is the PSD response curve and the root mean square value of the response of a sampling point in the normal distribution interval and in each direction. In real applications, the vibration response characteristics of a product structure are generally evaluated via the comparison of root mean square values of input and output accelerations. The PSD function for random vibration is generally formulated as follows:

$$S(f) = \int_{-\infty}^{+\infty} R(\tau) e^{-j2\pi f\tau} d\tau$$

(17)

where *f* is the frequency,  $\tau$  is the time difference between any two points during the process of random vibration, and *R*( $\tau$ ) is the autocorrelation function of random vibration. Moreover, its PSD function and autocorrelation function can be used to form a pair of Fourier transform formulae as follows:

$$R(\tau) = \frac{1}{2\pi} \int_{-\infty}^{+\infty} S(f) e^{jf\tau} df$$

(18)

The autocorrelation function is used to describe the similarity degree of a random vibration process x(t) at different moments, formulated as follows:

$$R(\tau) = \lim_{T \to \infty} \frac{1}{T} \int_0^{+\infty} x(t) x(t+\tau) dt$$

(19)

The PSD function reflects the energy distribution of random vibrations in the frequency domain, involving unilateral and bilateral PSD functions. However, since negative frequencies do not exist in engineering, the bilateral PSD function has no intuitive physical significance at a negative frequency. Therefore, only a unilateral PSD function needs to be considered.

## 4.3.2. Sinusoidal Vibration

Sinusoidal vibration refers to a periodic reciprocating motion in which vibration parameters can be described using the sine function of the actual independent variables, also known as simple harmonic motion. Sinusoidal vibration analysis is used to analyze the dynamic response of harmonic loads to products. The input of sinusoidal vibration analysis is usually the acceleration amplitude of harmonic load in various frequency ranges, and the output is the corresponding acceleration–amplitude response curve. By comparing the acceleration–amplitude curves for the input and the output values, the response characteristics of the structure under sinusoidal vibration can be evaluated [87]. Since the sinusoidal vibration is a simple harmonic vibration, the instantaneous displacement signal of the particle from the equilibrium position can be described as a time-varying function when the particle vibrates in a sinusoidal manner along a straight line. Assuming that displacement (X) is a function of time t, the displacement amplitude of sinusoidal vibration can be formulated as follows:

$$X = Asin(\omega t + \varphi) \tag{20}$$

where *A*,  $\omega$ , and  $\varphi$  are the displacement amplitude, angular frequency, and initial phase. If the initial phase  $\varphi = 0$ , then:

Х

y

$$K = Asin(\omega t) \tag{21}$$

After Equation (21) is differentiated, the corresponding velocity and acceleration can be obtained as follows:

$$\dot{X} = \omega A \cos \omega t = \omega A \sin \left( \omega t + \frac{\pi}{2} \right)$$

(22)

$$\ddot{X} = \omega^2 A sin\omega t = \omega^2 A sin(\omega t + \pi)$$

<sup>(23)</sup>

As indicated in Equations (22) and (23), the velocity and acceleration signals for the vibrating particles are 90° and 180° ahead of the corresponding displacement signals, respectively. The velocity value is numerically proportional to the displacement, with the direction toward the displacement origin.

Assuming that the acceleration (*g*) is a function of time *t*, the acceleration of sinusoidal vibration can be formulated as follows:

$$g = g_0 sin(\omega t + \varphi) \tag{24}$$

where  $g_0$  is the peak acceleration. If  $\varphi = 0$ , then:

$$g = g_0 sin\omega t \tag{25}$$

4.3.3. Drop-Induced Shock

When the product drops in free fall, its kinetic energy is mainly converted into thermal energy generated by friction, as well as the elastic and plastic strain energy of the product shell and internal components. Drop-induced shock analysis is mainly used to study the dynamic response and stress state of the product during the entire drop-induced shock analysis [88]. From the perspective of dynamics, the velocity before drop-induced shock depends on the drop height, formulated as follows:

$$V_b = \sqrt{2gh} \tag{26}$$

where  $V_b$ , g, and h are the acceleration before drop-induced shock, gravitational acceleration, and drop height, respectively.

According to the momentum theorem, we can write the following:

$$-mV_a - mV_b = -\int_0^1 mG(t)dt$$

(27)

where  $V_a$  is the velocity after drop-induced shock, G(t) is the shock acceleration at time t, T is the shock duration, and m is the mass of the shock platform. Without other energy losses,  $V_a$  is proportionate to the velocity  $V_b$  before rebound, formulated as follows:

$$V_a = c V_b \tag{28}$$

where *c* is the resilience coefficient, whose value is between 0 and 1.

By substituting Equation (28) into Equation (27), we can write the following:

$$-mcV_{ab} - mV_b = -\int_0^T mG(t)dt$$

<sup>(29)</sup>

$$V_b = \frac{1}{1+c} \int_0^T mG(t)dt \tag{30}$$

By substituting Equation (30) into Equation (26), the shock energy of the whole drop process can be obtained as follows:

$$A = \int_{0}^{T} mG(t)dt = (1+c)\sqrt{2gh}$$

(31)

#### 5. Typical Models for Fatigue Life Prediction of Solder Joint

As a key part of various interconnected components of 3D packaged memory devices, a solder joint is used for electrical and mechanical connection, as well as a heat dissipation channel for the chip, whose reliability largely influences the quality of the product. When a solder joint is subjected to stresses, such as temperature cycle, vibration, and impact, strain accumulation can occur due to the mismatch of thermal expansion coefficients and different elastic moduli of various structural materials. This accumulated strain will result in the initial crack or new crack of the solder joint, causing it to continuously expand until fracture occurs, eventually leading to device failure [89]. Therefore, failure analysis and reliability research on solder joints is of great significance for 3D packaged memory devices. Nowadays, appropriate models for fatigue life prediction are widely studied after the stress–strain and energy density of solder joints of the device under environmental stresses are analyzed via finite element analysis [90,91]. In terms of various failure types of solder joints, fatigue life prediction models for solder joints are usually divided into four different categories based on plastic deformation, creep deformation, fracture mechanics,

and energy. These models reflect the fatigue law of solder joints with different perspectives and accuracies and are for different applications that are suitable for fatigue life prediction under different stress conditions or failure types [92–94].

#### 5.1. Fatigue Life Prediction Models of Solder Joints Based on Plastic Deformation

The representative life prediction models based on plastic deformation include the Coffin–Manson, Engelmaier, Soloman, and Norris–Landzberg models. These models are widely used to predict the low-cycle fatigue failure of solder joints due to cyclic plastic deformation, where stress–strain curves are generally plastic stress–strain curves. However, when these models are used for fatigue life prediction, they are easily affected by cycle frequency, the thermal expansion coefficient of chip packaging material, and stress type [95,96].

#### 5.1.1. Coffin–Manson Model

The Coffin–Manson equation is the most commonly used life prediction model based on plastic deformation [97]. However, it ignores the effects of time and temperature on solder joint life. Based on the generalized fatigue damage law of metal materials [98], it is mainly applicable to low-cycle fatigue analysis caused by temperature loads [99] and is formulated as follows:

$$\frac{\Delta \varepsilon_p}{2} = \varepsilon_{f'} \left( 2N_f \right)^c \tag{32}$$

where  $\varepsilon_{f'}$ ,  $\Delta \varepsilon_p$ , c, and  $N_f$  are the fatigue toughness coefficients, plastic strain range, fatigue toughness index, and number of failure cycles, respectively.

#### 5.1.2. Engelmaier Model

The Engelmaier model modifies the Coffin–Manson model to improve its effectiveness [100]. However, although it considers the influence of thermal cycle frequency and temperature on fatigue life, it does not consider the creep effect of solder joints [101,102]. Therefore, it is mainly applicable in situations where there are large differences between thermal expansion coefficients and the dominant shear stress–strain, formulated as follows:

$$N_f = \frac{1}{2} \left( \frac{\Delta \gamma}{2\varepsilon_{f'}} \right)^{\frac{1}{c}}$$

(33)

$$c = -0.442 - 6 \times 10^{-4} T_m + 1.74 \times 10^{-2} \ln(1+f)$$

(34)

where  $\Delta \gamma$ , *f*, and  $T_m$  are the range of shear strain, frequency of the thermal cycle, and average temperature of the thermal cycle, respectively.

The Engelmaier model can be widely used to predict the low-cycle fatigue failure of solder joints due to repeated plastic deformation. The involved stress–strain is mainly the plastic stress–strain. However, it is easily affected by cycle frequency, the thermal expansion coefficient of the chip packaging material, and stress type.

#### 5.2. Fatigue Life Prediction Models of Solder Joints Based on Creep Deformation

Under high, low, or cyclic temperature conditions, creep effects related to loading time occur in solder joints. In microelectronic packages, for example, creep effects occur when the operating temperature of the solder joint exceeds half of the melting point of the SN-based lead-free solder. However, due to the complexity of the creep mechanism (creep, plastic, and elastic deformations overlap with each other in the creep process [103]), the model has limited accuracy in describing the creep process and ignores the influence of plastic strain [104].

#### 5.2.1. Knecht-Fox Model

The Knecht–Fox model is a creep fatigue model based on the matrix dislocation theory [105], in which the solder microstructure is related to the creep shear strain range of the matrix. The model can be formulated as follows:

$$N_f = \frac{C}{\Delta \gamma_{mc}} \tag{35}$$

where  $N_f$ , C, and  $\Delta \gamma_{mc}$  are the number of failure cycles, the material constant related to the microstructure of the solder, and the creep stress amplitude of the matrix, respectively.

#### 5.2.2. Syed Model

The Syed model considers steady-state creep as the main cause of the thermal fatigue failure of solder joints, taking into account the cyclic creep fatigue life caused by varying and repeated stresses under a single creep mechanism [106,107]. The model can be formulated as follows:

$$N_f = \left(C' * \varepsilon_{acc}\right)^{-1} \tag{36}$$

where  $\varepsilon_{acc}$  and C' are the creep strain accumulated in each cycle and constant reciprocal of creep ductility, respectively.

Equation (36) can be transformed into the energy density model as follows:

$$N_f = (W' * w_{acc})^{-1}$$

(37)

where  $w_{acc}$  and W' are the creep strain energy density accumulated in each cycle and the creep strain energy density at failure, respectively.

The Knecht–Fox model is a matrix creep model applicable to all packaging types, and the Syed model is a cumulative creep strain energy model mainly applicable to PBGA and SMD packaging. However, both models ignore the effect of plastic strain on solder joints during the temperature cycle, and plastic strain has a significant impact on the fatigue life of solder joints. This significantly limits the ability of the two models to predict the fatigue life of solder joints in electronic packaging.

## 5.3. Fatigue Life Prediction Models of Solder Joints Based on Fracture Mechanics

The Paris model and the *J*-integral model are representative fracture-mechanics-based models for the fatigue life prediction of solder joints [108]. Based on the fracture parameters, these models can predict fatigue life by calculating the damage caused by the accumulation and propagation of cracks. They consider the effects of strain energy dissipation and structural damage on fatigue life and establish a power relationship between the crack growth rate and the stress intensity factor. They are usually used under linear elastic fracture conditions and are only applicable to stable crack growth in fatigue tests.

## 5.3.1. Paris Model

The Paris model combines fatigue with fracture mechanics and uses stress intensity factors to describe the stress field strength at the crack tip, in which the stress intensity factor is considered the main cause of crack growth. The model can be formulated as follows:

$$\frac{d_a}{d_N} = C'' \left(\Delta k\right)^{n'} \tag{38}$$

$$\Delta k = k_{max} - k_{min} \tag{39}$$

where  $\frac{d_a}{d_N}$  is the crack growth rate. *N*, *a*, and  $\Delta k$  are the number of failure cycles, crack length, and amplitude of the stress intensity factor in each stress cycle, respectively.  $k_{max}$  and  $k_{min}$  are the maximal and minimal stress intensity factors in a load cycle, respectively.

C'' and n' are material constants, which are related to environmental factors, such as the temperature, humidity, medium, and loading frequency.

#### 5.3.2. J-Integral Model

The *J*-integral model uses the *J*-integral as a mechanical control parameter. It mainly addresses cyclic plastic strain and is formulated as follows:

$$\frac{d_a}{d_N} = c_1 (\Delta J)^{m_1} \tag{40}$$

$$\Delta J = \frac{S_p}{B(W-a)} f(a, W) \tag{41}$$

where  $c_1$  and  $m_1$  are material constants, and  $S_p$  is the area of the load–displacement curve in the case of a closed crack. *B* and *W* are the thickness and width of the sample, respectively. f(a, W) is a geometric function determined by *a* and *W*.

## 5.4. Fatigue Life Prediction Models of Solder Joints Based on Energy

The fatigue life prediction models based on energy mainly calculate the strain energy or strain energy density of each cycle according to the stress–strain hysteresis energy of solder joints in order to predict their fatigue life. There are two main methods to achieve this. One method is to directly predict fatigue life using empirical equations, such as those in the Akay model. The other method is to first predict the number of cycles when a solder joint initiates a crack and then calculate the crack growth rate according to fracture mechanics and the number of cycles when the crack growth causes the failure of the entire solder joint. Finally, these two values can be added together to obtain the fatigue life of a solder joint. The Darveaux model is representative of this second method.

## 5.4.1. Akay Model

The Akay model establishes the relationship between the average number of cycles in failure and the total strain energy, but it can only predict the cycle life at the time of solder joint crack initiation [109]. It is mostly used to predict the package in the form of a wired frame, which is formulated as follows:

$$N_f = \left(\frac{\Delta \overline{W_{total}}}{W_0}\right)^{1/k} \tag{42}$$

where  $\Delta W_{total}$  is the total strain energy, and  $W_0$  and k are material constants.

#### 5.4.2. Darveaux Model

Under the conditions of thermal stress or mechanical stress, the Darveaux model describes the relationship between the physical constants of solder joints and their actual life cycle based on the stress, strain, or energy between solder joints [110]. The fatigue process can be divided into two stages, namely, steady-state and nonlinear acceleration. In the steady-state stage, fatigue crack propagation occurs at a constant speed. In the nonlinear acceleration stage, the mechanical behavior of solder joints rapidly deteriorates. The Darveaux model is widely used for SnPb solder joint components and is suitable for the damage caused by crack initiation and propagation. However, there are many correlation coefficients in this model. Moreover, most solder joint failures occur only when the crack propagates to a certain extent, rather than when solder joints are completely broken [111]. These two factors limit the Darveaux model's applications. The model can be formulated as follows:

$$N_0 = K_1 (\Delta W_{ave})^{\kappa_2} \tag{43}$$

$$\frac{d_a}{d_N} = K_3 (\Delta W_{ave})^{k_4} \tag{44}$$

$$N_s = N_0 + \frac{a}{d_a/d_N} \tag{45}$$

where  $N_s$ ,  $N_0$ ,  $\Delta W_{ave}$ , and a are the characteristic life cycles of interconnected solder joints, the number of crack initiation cycles, the average inelastic strain energy density accumulated in each cycle, and the characteristic fracture length, respectively.  $\frac{d_a}{d_N}$  represents the crack growth rate.  $K_1$ ,  $K_2$ ,  $K_3$ , and  $K_4$  are the coefficients obtained via the experiments and are related to crack propagation, finite element model structure, solder joint connections, and substrate material thickness, respectively.

#### 6. Studies on the Reliability of 3D Packaged Memory

Packaging reliability is vitally important to ensure the normal operation of an entire electronic system. Studies on the reliability of 3D packaged memory devices are often carried out using a test analysis, finite element simulation analysis, or another comprehensive method. In the test analysis, device defects in reliability are simulated by environmental stress tests, and then the failure mode and mechanism for the device with defects are analyzed using various instruments and equipment. Common tests include mechanical tests (such as vibration, shock, and drop), thermal stress tests (such as temperature cycle and thermal shock), life tests (such as steady-state life and aging), hygrothermal stress tests (such as a steady-state hygrothermal test, highly accelerated steady-state hygrothermal test, and pressure cooker test), and space radiation resistance tests (such as dose rate reversal, dose rate induction locking, and electric dose). Relevant test standards and conditions can refer to several standards, including GJB548, GJB150, GB/T 2423, MIL-STD-202, MIL-STD-750, MIL-STD-883, JEDEC, and IPC. Typical reliability test items are shown in Table 5.

| Test Type       | Test Items          | <b>Typical Conditions</b>                                                                       | Purpose                                                                                                                                                                                                                                                                                                  |

|-----------------|---------------------|-------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | Temperature cycling | Method 1010 test condition C<br>-65-+150 °C,<br>Transfer time: 1 min, dwell time:<br>10 min     | This test is conducted to determine the resistance of a component to high- and low-temperature extremes and the effect of alternate exposures to these extremes.                                                                                                                                         |

| Thermal test    | Thermal shock       | Method 1011 test condition C<br>-65-+150 °C,<br>Transfer time: 10 s, dwell time:<br>2 min       | The purpose of this test is to determine the<br>resistance of the component to sudden<br>exposure to extreme changes in<br>temperature and the effect of alternate<br>exposures to these extremes.                                                                                                       |

| Mechanical test | Random vibration    | Method 2026 test condition E<br>20 (m/s <sup>2</sup> ) <sup>2</sup> /Hz, 169.1 m/s <sup>2</sup> | This test is conducted to determine the<br>ability of the microcircuit to withstand th<br>dynamic stress exerted by random<br>vibration applied between upper and low<br>frequency limits in order to simulate the<br>vibrations experienced in various service<br>field environments.                   |

|                 | Mechanical shock    | Method 2002 test condition D<br>49,000 m/s <sup>2</sup> , 0.3 ms                                | The shock test is intended to determine the<br>suitability of devices for use in electronic<br>equipment. They may be subjected to<br>moderately severe shocks as a result of<br>suddenly applied forces or abrupt change<br>in motion caused by rough handling,<br>transportation, or field operations. |

Table 5. Typical reliability test items.

|               | Table 5. Cont.      |                                                         |                                                                                                                                                                                                                                                                |

|---------------|---------------------|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Test Type     | Test Items          | Typical Conditions                                      | Purpose                                                                                                                                                                                                                                                        |

| Humidity test | Moisture resistance | Method 1004 test<br>80–100% RH, 10 continuous<br>cycles | The moisture resistance test is performed<br>for the purpose of rapidly evaluating the<br>resistance of component parts and<br>constituent materials to the deteriorative<br>effects of high-humidity and -heat<br>conditions typical of tropical environments |

| Life test     | Steady-state life   | Method 1005 test condition B<br>+125 °C, 1000 h         | The steady-state life test is performed to<br>demonstrate the quality or reliability of<br>devices subjected to specific conditions<br>over an extended time period.                                                                                           |

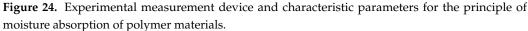

Finite element simulation analysis [112] is a method that uses computer-based finite element simulations to accurately identify defects in the devices and to optimize their designs. Meanwhile, it can also effectively simulate the stress distribution of the device in various environments, such as moisture distribution or thermal stress distribution. ABAQUS, ANSYS, and NASTRAN are commonly used finite element software programs in microelectronic packaging simulation analysis [113–115]. Finite element analysis fundamentally consists of preprocessing, simulation modeling, solving, and post-processing (Figure 25), in which material parameters and selected models are important for simulation accuracy.

Figure 25. Finite element modeling flow for electronic components.

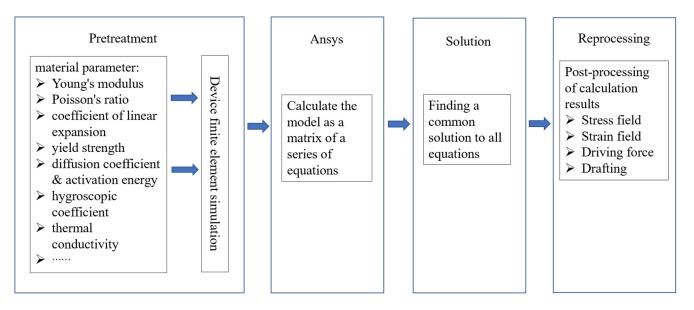

The comprehensive method combines finite element analysis and test analysis, in which the former provides theoretical guidance for the test, which can then be used to verify and improve the simulated model. The analysis flow of the comprehensive method is shown in Figure 26.

## 6.1. The Reliability of PoP Memory under Thermal Stress

The thermal expansion coefficients of various materials in the package of PoP memory vary greatly, causing delamination or cracks to emerge inside the device due to the thermal strain induced by the change in thermal load. Especially under periodic high- and lowtemperature alternation or extreme-temperature-gradient environments, the internal stress and microstructure of the chip solder joints inside the PoP memory are prone to change. With the passage of the time cycle, stress–strain accumulation will eventually lead to failures, such as solder joint cracks, package cracking, and delamination.

Figure 26. Analysis flow of the combination of test analysis and finite element analysis.

Zhang et al. [116] utilized temperature cycling loading (0–125 °C) and the Coffin– Manson model to analyze PoP packaging, indicating that the maximal accumulated inelastic hysteretic energy occurred in solder balls in the bottom FBGA (fine-pitch ball grid array) structure. In the FBGA structure, the thermal fatigue cracks originate from two symmetrical corners of the solder balls. The thermal fatigue damage in the outer array rapidly evolved into the inner array. By analyzing the failure data of solder balls, a thermal fatigue failure rule was defined, in which the critical failure probability was about 80%.

Wang Yang [117] carried out environment tests using off-line coupled temperature cycling and temperature shock on Amkor's 14 mm  $\times$  14 mm and 15 mm  $\times$  15 mm PoP devices, obtaining strain values for the top chip and the bottom solder joints. Their results show a periodic variation in strain and stresses were mainly concentrated on the solder joints and chip. The maximal stress of the bottom chip was greater than that of the top chip. The stresses of the bottom solder joints were greater than those of the top solder joints on the whole, where the maximal value emerged in the corner of the outermost bottom solder joints.