Review

# Compact SPAD-Based Pixel Architectures for Time-Resolved Image Sensors

Matteo Perenzoni 1,\*, Lucio Pancheri 2 and David Stoppa 1

- <sup>1</sup> Integrated Radiation and Image Sensors, Fondazione Bruno Kessler, Trento 38123, Italy; stoppa@fbk.eu

- Department of Industrial Engineering, University of Trento, Trento 38123, Italy; lucio.pancheri@unitn.it

- \* Correspondence: perenzoni@fbk.eu; Tel.: +39-0461-314-533

Academic Editor: Edoardo Charbon

Received: 7 March 2016; Accepted: 16 May 2016; Published: 23 May 2016

Abstract: This paper reviews the state of the art of single-photon avalanche diode (SPAD) image sensors for time-resolved imaging. The focus of the paper is on pixel architectures featuring small pixel size ( $<25~\mu m$ ) and high fill factor (>20%) as a key enabling technology for the successful implementation of high spatial resolution SPAD-based image sensors. A summary of the main CMOS SPAD implementations, their characteristics and integration challenges, is provided from the perspective of targeting large pixel arrays, where one of the key drivers is the spatial uniformity. The main analog techniques aimed at time-gated photon counting and photon timestamping suitable for compact and low-power pixels are critically discussed. The main features of these solutions are the adoption of analog counting techniques and time-to-analog conversion, in NMOS-only pixels. Reliable quantum-limited single-photon counting, self-referenced analog-to-digital conversion, time gating down to 0.75 ns and timestamping with 368 ps jitter are achieved.

Keywords: single-photon avalanche diode; SPAD; time-resolved imaging; time-gating photon counting

## 1. Introduction

Solid-state image sensors with nanosecond and sub-nanosecond timing resolution are needed in applications such as optical ranging, fluorescence microscopy and Raman spectroscopy [1–3]. Research is moving in two main directions: on the one hand lock-in pixels with high shutter efficiencies and high frequency operation are already used in 3D Time-of-Flight cameras [4]. On the other hand, time-resolved pixels based on single-photon avalanche diodes (SPADs) appear more and more a feasible and competitive perspective.

The last years have seen CMOS SPAD-based sensors enter the consumer market with products based on single-pixel detectors or small arrays. For imaging applications, however, the requirements are much more demanding and several technological challenges still need to be tackled. In addition to device optimization, the use of SPADs in image sensors imposes additional requirements such as yield, uniformity of breakdown voltage and photon detection efficiency (PDE), reduction of optical cross-talk and minimization of guard rings.

Several challenges also need to be solved with respect to the readout electronics. Storing the timing information at the pixel level requires either fast time-gating or in-pixel time-tagging. In addition, especially for large arrays, the pixels should store timing information on multiple photons, to reduce the bandwidth needed for the array readout. These operations should be performed with a minimum area overhead in order to maintain a small pixel pitch and a good fill factor.

As happened in CMOS image sensor development, the first proof-of-concept designs have exploited standard CMOS processes [5–8]. Although not optimized in many respects, CMOS proved to be a good platform to test the feasibility of time-resolved image sensors at the architectural level. As the focus passes from proof-of-concept to applications, the optimization of fabrication technologies

is unavoidable. Currently, the possibilities for commercial exploitation of CMOS SPAD arrays are increasing and new companies are entering the field, proposing solutions based on customized technologies [9]. Optimized single-photon image sensors will not only be appealing for time-resolved imaging, but also for low-light level imaging, for example in security and scientific applications.

This paper reviews the work on SPAD pixel arrays in the recent years, focusing on pixel architectures suitable for the realization of large pixel arrays. Section 2 presents an overview of the main SPAD characteristics, with particular attention to array integration challenges. In Section 3, several pixel architectures are analyzed and discussed. Finally, a roadmap for future developments is traced.

## 2. SPADs in CMOS Technologies

#### 2.1. SPAD Structure

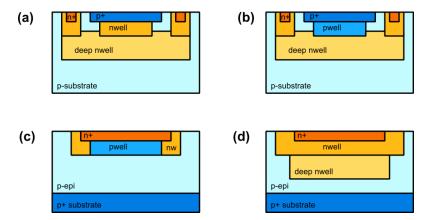

Since their first proof-of-concept in the early 2000s, CMOS SPAD detectors have been integrated in many technology nodes, using both standard, High Voltage or CIS processes. Most of the devices demonstrated so far are based on a p+/nwell junction, which is intrinsically isolated from the p-type substrate [10–12]. While the guard ring can be implemented in different ways, the most common embodiments use a deep nwell to separate the guard ring from the substrate. Different guard ring solutions are reviewed in [13].

The immediate advantage of this configuration is the possibility of accessing both the anode and cathode, and thus the direct coupling to the readout electronics operating at low voltage. To obtain the structure in Figure 1a, only an additional deep-nwell implantation is needed in addition to the layers typically available in a standard CMOS. A higher red and NIR sensitivity can be obtained with a deeper junction, for example a pwell/deep-nwell, as shown in Figure 1b [12,14].

**Figure 1.** Cross sections of different CMOS SPAD devices (a) p+/nwell; (b) pwell/deep-nwell; (c) n+/pwell; (d) deep-nwell/p-epi/p+ sub.

N-in-p device structures have been proposed, with the active junction based on a or n+/pwell junction or a deep-nwell/p-epi/p+sub (Figure 1c,d) [15,16]. The last options potentially offer an increased photon detection efficiency (PDE) in the red and NIR spectral region, but require a quenching resistor at the high voltage node and a capacitive decoupling of the readout circuit. Their use in a pixel is thus not straightforward.

#### 2.2. Figures of Merit

The excellent timing resolution, in the picosecond range, is one of the main advantages of SPAD devices. It has been demonstrated that even unoptimized processes can lead to devices having a jitter of few tens of ps FWHM [17]. One of the key factors to minimize the device jitter is the reduction of

photo-carrier diffusion towards the high-field region. To this extent, p+/nwell structures typically feature a very low jitter, as the diffusion tail is often reduced to a minimum, while the jitter is larger in pwell/deep-nwell devices [14,18].

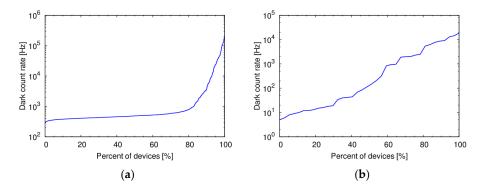

The dark count rate (DCR) is usually the most important source of noise in SPADs, since its fluctuations set the minimum detectable light signal. In a SPAD array, even though all the devices are nominally equal, DCR can have an enormous variability, spanning several orders of magnitude (Figure 2). What is really important in arrays is therefore not the DCR of a single device, but the whole distribution. If small SPADs are considered, two common types of distribution are typically found. A first case where most of the devices have a similar DCR, while a small percentage have large value, as shown in Figure 2a. It is not infrequent to find distributions where a plateau does not exist, as in Figure 2b. The different behaviors can be explained by considering the dominant sources of DCR for different SPAD structures.

**Figure 2.** Dark Count Rate distribution of SPADs fabricated in different CMOS process technologies (a)  $0.35 \mu m$  High Voltage with  $130-\mu m^2$  active area [19]; (b)  $0.7 \mu m$  High Voltage with  $100-\mu m^2$  active area [11].

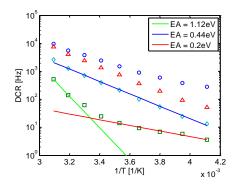

Some insight on the origin of DCR can be obtained by analyzing its temperature dependence. Figure 3 shows the DCR temperature dependence of four devices with the same area, representative of the behavior of a whole distribution. The three SPADs with high DCR have an activation energy lower than  $E_G/2$ , indicating the presence of trap-assisted tunneling. For the SPAD with low DCR, the activation energy has a transition between  $E_G$  and 0.2 V as the temperature decreases. In this device, DCR is dominated by injection of minority carriers from the neutral regions at high temperatures, and from tunneling at low temperatures. The relative weight between the different components determine the shape of the DCR distribution. If the devices are small and the amount of contaminants is low, DCR will mostly be dominated by minority carrier injection or band-to-band tunneling, and will be very uniform. If, on the contrary, the amount of contaminants is relatively high, the distribution will not show a plateau.

Figure 3. DCR temperature dependence for 10-µm diameter SPADs in 150 nm standard CMOS.

The integration of SPADs in deep submicron technology nodes has several obvious advantages. On one hand, being an intrinsically digital device, the possibility of introducing in-pixel dense digital readout electronics such as counters or TDCs is appealing. On the other hand, it is increasingly clear that a doping profile customization is absolutely needed to obtain detectors with acceptable performance in advanced nodes. The first attempts to fabricate SPADs in unmodified 90 and 65 nm processes have led to devices with very high DCR, mainly due to tunneling [15]. In fact, the well doping concentration steadily increases with device scaling. As a general consideration, SPADs integrated in standard processes with no process modifications have hardly an optimized DCR.

A customization of the doping profiles is required to optimize the SPAD characteristics. On the one hand, DCR can be reduced by carefully tuning the electric field profile in the avalanche region [20], so as to minimize the contribution of tunneling. This is also an advantage if the device needs to be cooled, as the absence of tunneling provides a more efficient DCR reduction with decreasing temperature. In fact, once the doping profiles are optimized for tunneling reduction, the device DCR is mainly due to the contamination by heavy metals. Using both excellent starting material and a clean production line, as in most CIS processes, is fundamental for the production of low-noise devices. The use of advanced imaging processes, in fact, can lead to devices having good characteristics both regarding PDE and DCR, as was demonstrated in a few cases [14,21].

The electric field profile affects the PDE through the optimization of avalanche triggering probability. In a graded profile the breakdown probability reaches very large values at smaller voltages than in step profile junction with similar breakdown voltages [18]. A good PDE at low excess bias can thus be obtained by combining a graded profile with an optimized optical stack, which is readily available in a CIS process [14].

Afterpulsing is a source of correlated noise, and in time resolved applications it can lead to measurement distortions if it is not minimized. Since its origin lies in the presence of deep trapping centers, the quality of the process can also contribute to its reduction. In addition, a careful design of the quenching circuit, ensuring a minimum stray capacitance and fast avalanche extinction, helps keeping afterpulsing under control. In general, in small CMOS devices, the total afterpulsing rate can be maintained at acceptable levels with a few tens ns hold-off time [11,14,22]. One notable exception to this general observation is a 0.35 HV processes, which has a long tails and needs a hold-off time of 100s ns [23]. This peculiar behavior, limited to a single 0.35 HV process has been reported by several authors, but the reason of the long afterpulsing tail has not yet been completely understood.

Optical cross-talk is a critical parameter in SPAD arrays, arising from the emission of optical photons during an avalanche event [24]. Measurements on dense p+/nwell SPAD arrays have shown that cross-talk rates can be as high as a few percent for nearest neighbor devices if the fill factor is in the order of 70% [25]. For optimal performance, therefore, cross-talk should be minimized by introducing deep trench isolation, as currently done in silicon photomultiplier by most manufacturers [26].

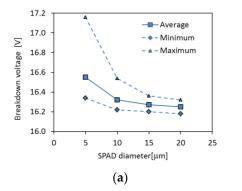

## 2.3. Uniformity

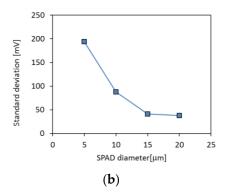

The uniformity of breakdown voltage is of paramount importance for the integration of SPAD image sensors, since all the SPADs are biased at the same voltage. Non-uniformities in the order of 100 mV can be tolerated if SPADs are operated at excess bias voltages of a few volts. A good uniformity of PDE along the pixel array is also required in image sensors. Experimental investigations on 150 nm CMOS SPADs have shown that breakdown voltage non-uniformity is larger in small devices, reaching values in the order of 1 V for 5-µm diameter SPADs, while 10-µm devices have a peak-to-peak non-uniformity lower than 0.5 V and in larger ones it is in the order of 100 mV (Figure 4). The effect of device size is also visible in the average breakdown voltage. The trend is toward a decreasing average breakdown voltage with device area. Surprisingly, however, once the avalanche has been triggered, the PDE results very uniform in all the tested detectors, with non-uniformities lower than 1% [27].

Sensors **2016**, 16, 745 5 of 12

**Figure 4.** Measured breakdown voltage as a function of SPAD diameter. Measurements were done on 150-nm CMOS SPADs [27]. (a) Breakdown voltage distribution; (b) breakdown voltage non-uniformity (standard deviation).

#### 2.4. Layout

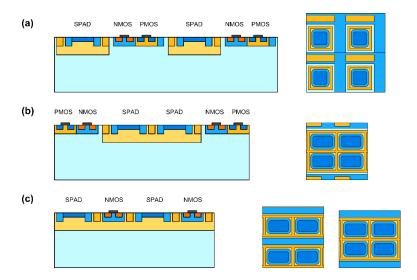

High fill factor pixel arrays can be obtained only with a careful minimization of guard ring and of the area occupied by in-pixel readout electronics. Deep-nwell sharing between different SPADs and between SPADs and electronic readout circuits can be used to effectively increase the device packing and therefore to help shrinking pixel size [28]. If every SPAD has a separate deep-nwell, as in Figure 5a, the bias can be applied either at the anode or at the cathode, and quenching circuitry can be connected to the other terminal. In the second case, the total device capacitance will be lower, but the distance between different devices should be maintained large enough to avoid punch through between the deep nwells. This layout solution was used in the early proof-of-concept arrays with large pitch and small fill factor [5,29].

**Figure 5.** Cross section and  $4 \times 4$  pixel layout of (a) SPADs integrated in separate deep nwell; (b) SPADs sharing the same deep nwell; (c) SPADs and NMOS transistors sharing the same deep nwell.

Deep-nwell sharing can be exploited to reduce the dead area at the borders of the deep nwell, as shown in Figure 5b. With deep-nwell sharing, first proposed in [11] the cathode of all SPADs are in common and the quenching should be performed at the anode side. Densely-packed SPAD arrays can be easily obtained using currently available technologies if digital readout circuits are placed outside the deep nwell. High fill factors, limited only by the device guard ring, have been demonstrated, although the detectors were confined in arrays including only a few lines of SPADs [30–33].

The packing desity can be further increased if the readout n-type MOSFETs are included in the same deep nwell with the SPADs, as in Figure 5c. In this case, the pwell with the MOSFETs must be biased at a voltage close to the one applied to SPAD anode, and thus the breakdown voltage of the pwell/deep-nwell junction should be high enough to avoid early brekdown problems. The main disadvantage of this solution, which has been adopted in [19,34–37], is that p-type transistors cannot be used inside the pixel electronics.

#### 3. Compact Pixels for Time-Resolved Imaging

The realization of photon-counting or time-stamping function within a given time window is straightforward with digital logic when using SPADs, since they provide a digital output. Although the fully digital solution meets the requirements of robustness and ease of implementation, the area occupation of the circuitry becomes extremely large. This is in contrast with the application field of this class of imagers, which is typically fluorescence lifetime imaging microscopy (FLIM), where also good spatial resolution and high efficiency are needed, driving towards small pixels with high fill factor.

## 3.1. Pixel Architectures

In order to keep the area small, analog solutions have been employed [19,35–38] by making use of analog counters and time-to-analog converters. The main techniques enabling a small pixel pitch are the implementation of the pixel circuitry using NMOS only so as to avoid nwells, the reuse of transistors for different purposes, a simple active-pixel readout with source follower and selection switch, and almost minimum-sized NMOS and capacitors, often making use of parasitic capacitances as storage nodes.

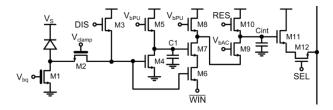

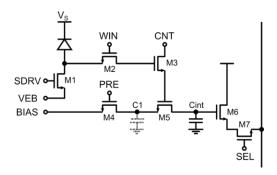

In [19] a pixel pitch of 25  $\mu$ m with a 20.8% fill-factor was demonstrated in a 0.35  $\mu$ m CMOS technology thanks to extensive use of analog techniques. The pixel schematic is depicted in Figure 6: the front-end is composed by a quenching transistor M1 and a clamp M2 which limits the voltage swing, and a disabling transistor M3. The gating circuit implements a pulse shortener by performing a logic AND between the SPAD pulse and its delayed and inverted companion, transmitting the WINn pulse to the analog counter. The latter signal defines the gating window, so when disabled ( $\overline{WIN}$  = 1) no pulse is generated. The analog counter then discharges the integration capacitance by an amount proportional to the pulse width. This architecture reaches a gating window width down to 1 ns, but can also accommodate larger integration time, operating as a global shutter photon-counting pixel. Moreover, it can operate multiple gating cycles for a relatively long time, limited only by the charge leakage of the analog memory (hundreds of milliseconds): indeed, thanks to the decoupling effect of M7, the repeated activation of the  $\overline{WIN}$  signal does not cause an output swing reduction due to charge injection.

**Figure 6.** Time-gated pixel with analog counter, enabling gating windows from  $\approx 1$  ns up to several hundreds of milliseconds [19].

The main issue of this pixel structure is the non-uniformity of the counting step in the array, which is driven by many mismatch constraints: the resulting pulse width of the gating circuit, mismatch of integration capacitances, distribution of the gating window signal, mismatch of the current limiter M9.

In order to limit it to the measured value of 11.9%, non-minimum sized transistors have been used in the critical signal path although an unprecedented fill-factor was obtained.

Concerning the minimum time-gating, the precision for very small windows is limited by the pulse shortener: indeed, when a SPAD event occurs during the opening or closing of the gating window, the pulse may be sliced by the WINn signal and therefore a reduced step is recorded in the integration capacitance.

A strong reduction of the number of transistors per pixel has been achieved in [35] by replacing the gating circuitry with a single NMOS performing both clamping and time-gating. As shown in Figure 7, the SPAD is passively quenched and the pulse transmission can be inhibited by M2. The analog counter performs a controlled discharge of the integration capacitor through M5 and M6. The time gating performed by this circuit can only be coarse, meaning that it has to be larger than the dead time of the SPAD (typ. 10–100 ns) in order to have predictable voltage steps at the analog counter. Indeed, differently from the previous architecture, there is no pulse shortener and the full SPAD pulse has to be transmitted to the analog counter. Some small injection contribution is expected to impact on the output signal swing, due to WIN coupling through the gate-drain capacitance of M5 to the integration capacitor. Non-uniformities in this scheme are determined by mismatch between integration capacitors, current limiting transistor M6 but also differences in SPAD breakdown voltage and dead-time which change the shape of the pulse. Remarkable fill-factor of 26.8% in a 8-µm pitch is achieved in a 130 nm CIS technology. An on-chip 1-bit digital conversion has been implemented so as to achieve a fast single photon oversampled imager.

**Figure 7.** Analog counting pixel with coarse time gating for windows width larger than the SPAD dead time (*i.e.*, >10 ns) [35].

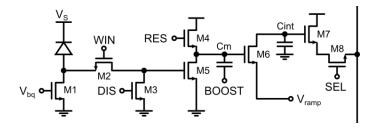

Extensive reuse of transistors and a deferred counting technique has been implemented in [36] in order to further reduce the transistor count and at the same time allow for precise and short gating windows. This has been achieved at the expense of generality: in this implementation, no continuous integration is possible, but only periodic excitation/gating schemes are allowed. As shown in Figure 8 the frontend is composed by a switch M1 acting both as precharge and disable with independent gate and source voltages, while M2 clamps and samples the SPAD pulse. The main difference with respect to the previous schemes is that, due to the repetitive nature of the measurement, the counting operation is performed after the sampling of the SPAD state in the observation window. Again, counting is performed by subtracting a controlled amount of charge from an integration capacitor.

The deferred counting scheme makes the counting step independent from the SPAD pulse nature, width, and position within the gating time window, achieving sharp window edges down to 200 ps rise/fall time and 750 ns minimum gating window width. This advantage was exploited using almost minimum-sized transistors in order to obtain a pixel pitch of 15  $\mu$ m and 21% fill-factor. At the same time, a self-referenced column-wise analog to digital conversion cancels the residual non-uniformity of 15.7% by using the very same pixel as a ramp generator for a single-slope ADC.

As a drawback, this scheme does not allow for more than one pulse to be counted for a single excitation/gating cycle, which is actually not a limitation when the gating window has to be smaller than the dead-time of a SPAD. For example, typical FLIM decay times fall within the range 1–10 ns, typically smaller than the SPAD recharge time. Another limitation is given by the fact that even if no

events are recorded, the deferred counter is stimulated with the digital signals, and therefore charge is injected and accumulated, reducing the available output voltage swing thus limiting the dynamic range to few hundreds of counted photons between each readout.

Figure 8. Analog time-gated pixel with transistor reuse and deferred analog counting [36].

Another function suitable for compact SPAD imaging arrays is the photon timestamping by using time-to-analog converters (TAC). In [38] a fairly complex TAC with in pixel digital conversion of the analog value was presented, but finally achieving a low fill-factor of 1% in a 50-µm pitch. Optimization of the area occupation can surely be improved by moving the conversion off-pixel, as described in [37]. With an approach similar to the analog photon counting described in the previous paragraphs, TAC circuitry can also be implemented using only NMOS transistors.

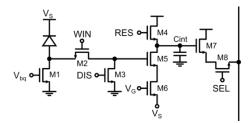

In Figure 9 the schematic shows a frontend with a standard passive quenching with disabling circuitry, driving a dynamic memory composed by M4 and M5. Whenever a SPAD pulse occurs, the memory is fully discharged, sampling onto the storage capacitor the present reference voltage fed to the whole array, representing time in the analog domain. This solution virtually eliminates many of the non-uniformity sources affecting analog counters: among remaining issues impacting uniformity and linearity, there are leakage from the storage capacitor and proper distribution of the fast-varying reference signal to the whole array. A remarkable 20% fill-factor in a 8  $\mu$ m pitch pixel is achieved, with an overall jitter of 368 ps rms.

Figure 9. Compact NMOS-only TAC-based pixel [38].

### 3.2. Analysis and Comparison

The time-gated analog counters presented in [19] and [36] can be directly compared as they perform a very similar operation, with the main difference that the deferred counting scheme of [36] does not allow long integration time with global shutter.

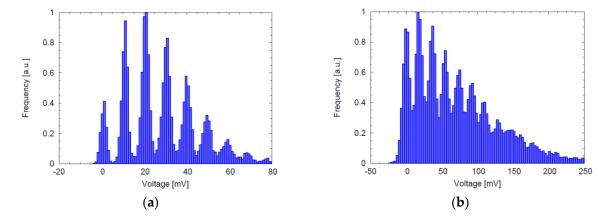

As a first comparison, the analog photon counting may be addressed: by selecting a single pixel and recording the output analog values, it is possible to reconstruct an histogram showing the characteristic peaks corresponding to the detection of 0, 1, 2, ..., photons. As shown in Figure 10, both histograms show clearly the single photon detection resolution, but Figure 10a highlights a better noise performance with almost isolated peaks. The higher noise visible in Figure 10b is due to the smaller in-pixel capacitance values used for the analog counting, leading to larger kTC noise contribution.

In both cases, the kTC noise is repeatedly accumulated during the charge transfer, and progressively confuses individual photon peaks; anyway, this occurs when the shot noise is already the dominant noise source [36].

**Figure 10.** Pixel analog output histograms for the analog counting pixels of [19] and [36], depicted in (a) and (b), respectively.

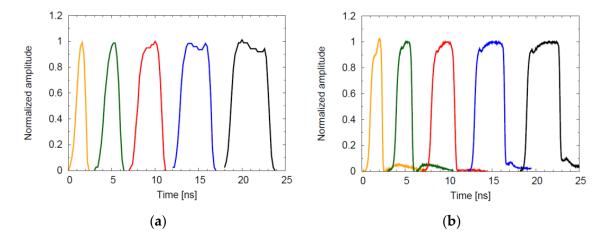

A second comparison can be made by exciting the sensor with a short laser pulse, in this case a 70-ps FWHM laser, progressively increasing the relative delay. The analog output then follows the shape of the gating window performed by the pixel. In Figure 11 this measurement has been repeated for windows width of approximately 1, 2, 3, 4, 5 ns; in both cases, the different window widths have been programmed to the internal logic which is stabilized against variations using a locked control loop with a reference clock. In this case it can be observed that edges of gating windows are better defined in Figure 11b: the motivation lays in the technique used to start and close the windows, avoiding the use of a monostable.

**Figure 11.** Time-gating windows for different widths for the analog counting pixels of [19] and [36], depicted in (a) and (b), respectively.

Table 1 summarizes the main parameters of all the analyzed SPAD image sensors, in particular for what concerns their compactness, size, and timing performance.

|                | [19]           | [35]               | [36]                                        | [37]               |

|----------------|----------------|--------------------|---------------------------------------------|--------------------|

| Process        | 0.35 μm HV     | 0.13 μm CIS        | 0.35 μm HV                                  | 0.13 μm CIS        |

| Supply         | 3.3 V          | 1.2 V              | 3.3 V                                       | 1.2 V              |

| Array size     | $32 \times 32$ | $320 \times 240$   | $160 \times 120$                            | $256 \times 256$   |

| Pixel pitch    | 25 μm          | 8 μm               | 15 μm                                       | 8 μm               |

| Fill-factor    | 20.8%          | 26.8%              | 21%                                         | 20%                |

| NMOS per pixel | 12T + 2C       | 8T + 1C            | 7T+1C                                       | 8T + 2C            |

| Timing         | Gating >1.1 ns | Gating > 10 ns     | Gating $> 0.75$ ns                          | TAC > 0.37  ns     |

| Interface      | Analog         | Analog/Digital 1 b | Analog/Digital 8 b                          | Analog/Digital 2 b |

| Consumption    | 33 mW          | 69.5 mW            | 20.6 mW <sup>a</sup><br>157 mW <sup>b</sup> | n.a.               |

Table 1. Comparison between recent compact analog-based SPAD sensors for time-resolved imaging.

#### 4. Discussion and Conclusions

The way towards high-resolution single-photon image sensors with timing capabilities (either implementing time-gating or time-stamping pixels) has to be pursued through two parallel approaches: on one side the optimization of the device, and on the other side with area-efficient circuit topologies.

The device optimization will inevitably go through the use of specialized process options, as already happened to conventional CIS processes. Indeed, SPAD devices will surely benefit from CIS (clean) processes with custom profile, which will enable reduction of tunneling and optimization of photon detection probability [39]. Additional modules, such as deep trench isolation in order to reduce cross talk, especially for deep-junction SPADs, will also improve the performance in densely packed arrays.

As far as pixel circuits is concerned, they must employ area-efficient analog and all-NMOS topologies in order to exploit shared nwell SPAD layout, passive quenching, transistors reuse, and possibly self-referenced conversion for increased reliability and readout speed in perspective of high-resolution imagers.

Finally, in the near future SPAD-based imagers could definetely take advantage of the advent of 3D-stacked fabrication technologies exploiting the co-integration of specialized CIS back-side illuminated sensing layer with deep-submicron digital CMOS. BSI-compatible SPADs offer higher sensitivity in the NIR region that combined with the stacking on advanced digital CMOS technologies will enable the realisation of pixel pitches in the order of a few micrometers and high fill factor [40,41]. At the same time efficient processing of the generated data flow will still be possible. These features, not only will drastically improve the performance of SPAD-based range cameras, but will open the way to new applications that are now dominated by other detector technologies, such as high dynamic range, high sensitivity and high speed intensity cameras.

**Author Contributions:** The authors equally contributed in the preparation of the manuscript text while L. Pancheri and M. Perenzoni drew most of the figures (equally).

Conflicts of Interest: The authors declare no conflict of interest.

#### References

- 1. Aull, B.; Loomis, A.; Young, D. Geiger-mode avalanche photodiodes for three-dimensional imaging. *Linc. Lab. J.* **2002**, *13*, 335–350.

- 2. Lakowicz, J.R. Principles of Fluorescence Spectroscopy, 3rd ed.; Springer US: Boston, MA, USA, 2006.

- 3. Kostamovaara, J.; Tenhunen, J.; Kögler, M.; Nissinen, I.; Nissinen, J.; Keränen, P. Fluorescence suppression in Raman spectroscopy using a time-gated CMOS SPAD. *Opt. Express* **2013**, *21*, 31632–31645. [CrossRef] [PubMed]

- 4. Remondino, F.; Stoppa, D. TOF Range-Imaging Cameras; Springer: Heidelberg, Germany, 2013; Volume 68121.

<sup>&</sup>lt;sup>a</sup> Analog readout mode; <sup>b</sup> Digital readout mode.

5. Niclass, C.; Rochas, A.; Besse, P.-A.; Charbon, E. Design and characterization of a CMOS 3-D image sensor based on single photon avalanche diodes. *IEEE J. Solid State Circuits* **2005**, *40*, 1847–1854. [CrossRef]

- 6. Stoppa, D.; Pancheri, L.; Scandiuzzo, M.; Gonzo, L.; Betta, G.-F.D.; Simoni, A. A CMOS 3-D Imager Based on Single Photon Avalanche Diode. *IEEE Trans. Circuits Syst. I Regul. Pap.* **2007**, *54*, 4–12. [CrossRef]

- 7. Niclass, C.; Favi, C.; Kluter, T.; Gersbach, M.; Charbon, E. A 128 × 128 single-photon image sensor with column-level 10-bit time-to-digital converter array. *IEEE J. Solid State Circuits* **2008**, 43, 2977–2989. [CrossRef]

- 8. Guerrieri, F.; Tisa, S.; Tosi, A.; Zappa, F. Two-Dimensional SPAD Imaging Camera for Photon Counting. *IEEE Photonics J.* **2010**, *2*, 759–774. [CrossRef]

- 9. Mori, M.; Sakata, Y.; Usuda, M.; Yamahira, S.; Kasuga, S.; Hirose, Y.; Kato, Y.; Tanaka, T. A 1280 × 720 single-photon-detecting image sensor with 100 dB dynamic range using a sensitivity-boosting technique. In Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 31 January–4 February 2016; pp. 120–121.

- 10. Rochas, A.; Gani, M.; Furrer, B.; Besse, P.A.; Popovic, R.S.; Ribordy, G.; Gisin, N. Single photon detector fabricated in a complementary metal-oxide-semiconductor high-voltage technology. *Rev. Sci. Instrum.* 2003, 74, 3263–3270. [CrossRef]

- 11. Pancheri, L.; Stoppa, D. Low-Noise CMOS single-photon avalanche diodes with 32 ns dead time. In Proceedings of the 37th European Solid State Device Research Conference, Munich, Germany, 11–13 September 2007; pp. 362–365.

- 12. Pancheri, L.; Stoppa, D. Low-noise single photon avalanche diodes in 0.15 μm CMOS technology. In Proceedings of the 41th European Solid State Device Research Conference, Helsinki, Swedish, 12–16 September 2011; pp. 179–182.

- 13. Dalla Betta, G.-F.; Pancheri, L.; Stoppa, D.; Henderson, R.; Richardson, J. Avalanche Photodiodes in Submicron CMOS Technologies for High-Sensitivity Imaging. In *Advances in Photodiodes*; Dalla Betta, G.-F., Ed.; InTech: Vienna, Austria, 2011; pp. 225–248.

- 14. Richardson, J.A.; Webster, E.A.G.; Grant, L.A.; Henderson, R.K. Scaleable Single-Photon Avalanche Diode Structures in Nanometer CMOS Technology. *IEEE Trans. Electron. Devices* **2011**, *58*, 2028–2035. [CrossRef]

- 15. Karami, M.A.; Yoon, H.J.; Charbon, E. Single-photon avalanche diodes in sub-100 nm standard CMOS technologies. In Proceedings of the International Image Sensor Workshop, Hokkaido, Japan, 8–11 June 2011.

- 16. Webster, E.A.G.; Grant, L.A.; Henderson, R.K. A High-Performance Single-Photon Avalanche Diode in 130-nm CMOS Imaging Technology. *IEEE Electron. Device Lett.* **2012**, *33*, 1589–1591. [CrossRef]

- 17. Tisa, S.; Guerrieri, F.; Zappa, F. Variable-load quenching circuit for single-photon avalanche diodes. *Opt. Express* **2008**, *16*, 2232–2244. [CrossRef] [PubMed]

- 18. Pancheri, L.; Stoppa, D.; Dalla Betta, G.-F. Characterization and Modeling of Breakdown Probability in Sub-Micrometer CMOS SPADs. *IEEE J. Sel. Top. Quantum Electron.* **2014**, *20*, 328–335. [CrossRef]

- 19. Pancheri, L.; Massari, N.; Stoppa, D. SPAD image sensor with analog counting pixel for time-resolved fluorescence detection. *IEEE Trans. Electron. Devices* **2013**, *60*, 3442–3449. [CrossRef]

- 20. Ghioni, M.; Gulinatti, A.; Rech, I.; Zappa, F.; Cova, S. Progress in Silicon Single-Photon Avalanche Diodes. *IEEE J. Sel. Top. Quantum Electron.* **2007**, *13*, 852–862. [CrossRef]

- 21. Villa, F.; Bronzi, D.; Zou, Y.; Scarcella, C.; Boso, G.; Tisa, S.; Tosi, A.; Zappa, F.; Durini, D.; Weyers, S.; *et al.* CMOS SPADs with up to 500 μm diameter and 55% detection efficiency at 420 nm. *J. Mod. Opt.* **2014**, *61*, 102–115. [CrossRef]

- 22. Niclass, C.; Soga, M. A miniature actively recharged single-photon detector free of afterpulsing effects with 6 ns dead time in a 0.18 μm CMOS technology. In Proceedings of the 2010 International Electron Devices Meeting, San Francisco, CA, USA, 6–8 December 2010; pp. 14.3.1–14.3.4.

- 23. Stoppa, D.; Mosconi, D.; Pancheri, L.; Gonzo, L. Single-Photon Avalanche Diode CMOS Sensor for Time-Resolved Fluorescence Measurements. *IEEE Sens. J.* **2009**, *9*, 1084–1090. [CrossRef]

- 24. Rech, I.; Ingargiola, A.; Spinelli, R.; Labanca, I.; Marangoni, S.; Ghioni, M.; Cova, S. Optical crosstalk in single photon avalanche diode arrays: A new complete model. *Opt. Express* **2008**, *16*, 8381–8394. [CrossRef] [PubMed]

- Xu, H.; Pancheri, L.; Braga, L.H.C.; Dalla Betta, G.-F.; Stoppa, D. Crosstalk Characterization of Single-photon Avalanche Diode (SPAD) Arrays in CMOS 150 nm Technology. *Procedia Eng.* 2014, 87, 1270–1273. [CrossRef]

- 26. Piemonte, C.; Acerbi, F.; Ferri, A.; Gola, A.; Paternoster, G.; Regazzoni, V.; Zappala, G.; Zorzi, N. Performance of NUV-HD Silicon Photomultiplier Technology. *IEEE Trans. Electron. Devices* **2016**, *63*, 1–6. [CrossRef]

27. Pancheri, L.; Dalla Betta, G.-F.; Campos Braga, L.H.; Xu, H.; Stoppa, D. A single-photon avalanche diode test chip in 150 nm CMOS technology. In Proceedings of the 2014 International Conference on Microelectronic Test Structures (ICMTS), Udine, Italy, 24–27 March 2014; pp. 161–164.

- 28. Henderson, R.K.; Webster, E.A.G.; Walker, R.; Richardson, J.A.; Grant, L.A. A 3 × 3, 5 µm pitch, 3-transistor single photon avalanche diode array with integrated 11 V bias generation in 90 nm CMOS technology. In Proceedings of the 2010 International Electron Devices Meeting, San Francisco, CA, USA, 6–8 December 2010; pp. 14.2.1–14.2.4.

- 29. Veerappan, C.; Richardson, J.; Walker, R.; Li, D.-U.; Fishburn, M.W.; Maruyama, Y.; Stoppa, D.; Borghetti, F.; Gersbach, M.; Henderson, R.K.; *et al.* A 16 0 × 128 single-photon image sensor with on-pixel 55 ps 10 b time-to-digital converter. In Proceedings of the 2011 IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 20–24 February 2011; pp. 312–314.

- 30. Pancheri, L.; Stoppa, D. A SPAD-based pixel linear array for high-speed time-gated Fluorescence Lifetime Imaging. In Proceedings of the ESSCIRC 2009—35th European Solid-State Circuits Conference, Athens, Greece, 14–18 September 2009; pp. 428–431.

- 31. Niclass, C.; Ito, K.; Soga, M.; Matsubara, H.; Aoyagi, I.; Kato, S.; Kagami, M. Design and characterization of a 256 × 64-pixel single-photon imager in CMOS for a MEMS-based laser scanning time-of-flight sensor. *Opt. Express* **2012**, 20, 11863–11881. [CrossRef] [PubMed]

- 32. Braga, L.H.C.; Gasparini, L.; Grant, L.; Henderson, R.K.; Massari, N.; Perenzoni, M.; Stoppa, D.; Walker, R. A Fully Digital 8 × 16 SiPM Array for PET Applications With Per-Pixel TDCs and Real-Time Energy Output. *IEEE J. Solid State Circuits* **2014**, 49, 301–314. [CrossRef]

- 33. Perenzoni, M.; Perenzoni, D.; Stoppa, D. A 64 × 64-pixel digital silicon photomultiplier direct ToF sensor with 100 M photons/s/pixel background rejection and imaging/altimeter mode with 0.14% precision up to 6 km for spacecraft navigation and landing. In Proceedings of the 2016 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 31 January–4 February 2016; pp. 118–119.

- 34. Burri, S.; Maruyama, Y.; Michalet, X.; Regazzoni, F.; Bruschini, C.; Charbon, E. Architecture and applications of a high resolution gated SPAD image sensor. *Opt. Express* **2014**, 22, 17573–17589. [CrossRef] [PubMed]

- 35. Dutton, N.A.W.; Gyongy, I.; Parmesan, L.; Gnecchi, S.; Calder, N.; Rae, B.R.; Pellegrini, S.; Grant, L.A.; Henderson, R.K. A SPAD-Based QVGA Image Sensor for Single-Photon Counting and Quanta Imaging. *IEEE Trans. Electron. Devices* **2015**, *63*, 189–196. [CrossRef]

- 36. Perenzoni, M.; Massari, N.; Perenzoni, D.; Gasparini, L.; Stoppa, D. A 160 × 120 Pixel Analog-Counting Single-Photon Imager with Time-Gating and Self-Referenced Column-Parallel A/D Conversion for Fluorescence Lifetime Imaging. *IEEE J. Solid State Circuits* **2016**, *51*, 155–167.

- 37. Parmesan, L.; Dutton, N.A.W.; Caldery, N.J.; Krstaji, N.; Holmes, A.J.; Grant, L.A.; Henderson, R.K. A 256 × 256 SPAD array with in-pixel Time to Amplitude Conversion for Fluorescence Lifetime Imaging Microscopy. In Proceedings of the International Image Sensors Workshop 2015, Vaals, The Netherlands, 8–11 June 2015.

- 38. Stoppa, D.; Borghetti, F.; Richardson, J.; Walker, R.; Grant, L.; Henderson, R.K.; Gersbach, M.; Charbon, E. A 32 × 32-pixel array with in-pixel photon counting and arrival time measurement in the analog domain. In Proceedings of the ESSCIRC 2009, Athens, Greece, 14–18 September 2009; pp. 204–207.

- 39. Bronzi, D.; Villa, F.; Tisa, S.; Tosi, A.; Zappa, F. SPAD Figures of Merit for Photon-Counting, Photon-Timing, and Imaging Applications: A Review. *IEEE Sens. J.* **2016**, *16*, 3–12. [CrossRef]

- 40. Kondo, T.; Takemoto, Y.; Kobayashi, K.; Tsukimura, M.; Takazawa, N.; Kato, H.; Suzuki, S.; Aoki, J.; Saito, H.; Gomi, Y.; *et al.* A 3D stacked CMOS image sensor with 16Mpixel global-shutter mode and 2 M pixel 10000 fps mode using 4 million interconnections. In Proceedings of the 2015 Symposium on VLSI Circuits (VLSI Circuits), Kyoto, Japan, 17–19 June 2015; pp. C90–C91.

- 41. Aull, B.F.; Schuette, D.R.; Young, D.J.; Craig, D.M.; Felton, B.J.; Warner, K. A Study of Crosstalk in a 256 × 256 Photon Counting Imager Based on Silicon Geiger-Mode Avalanche Photodiodes. *IEEE Sens. J.* **2015**, *15*, 2123–2132. [CrossRef]

© 2016 by the authors; licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC-BY) license (http://creativecommons.org/licenses/by/4.0/).