Application of CMOS Technology to Silicon Photomultiplier Sensors

Abstract

:1. Introduction

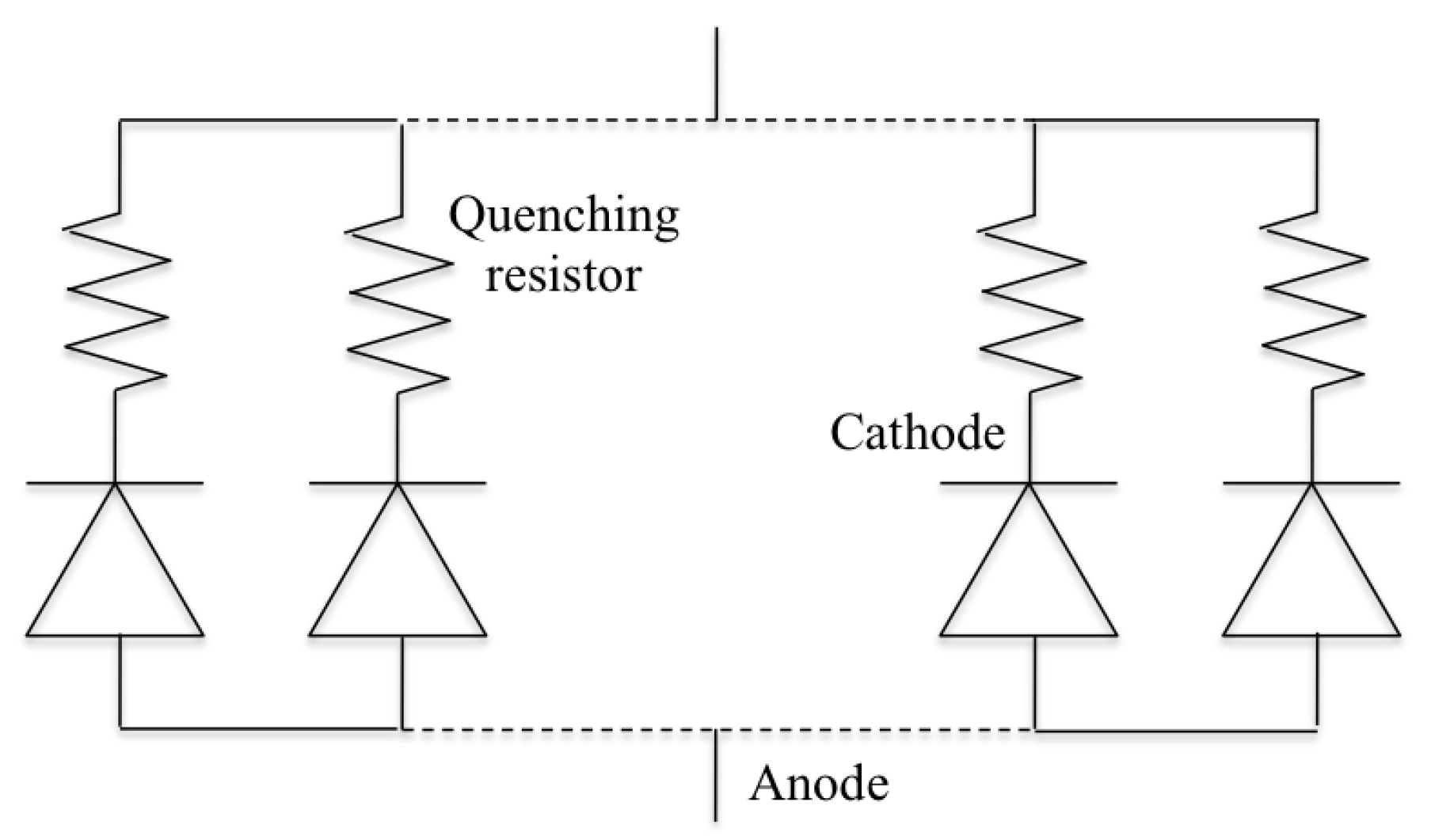

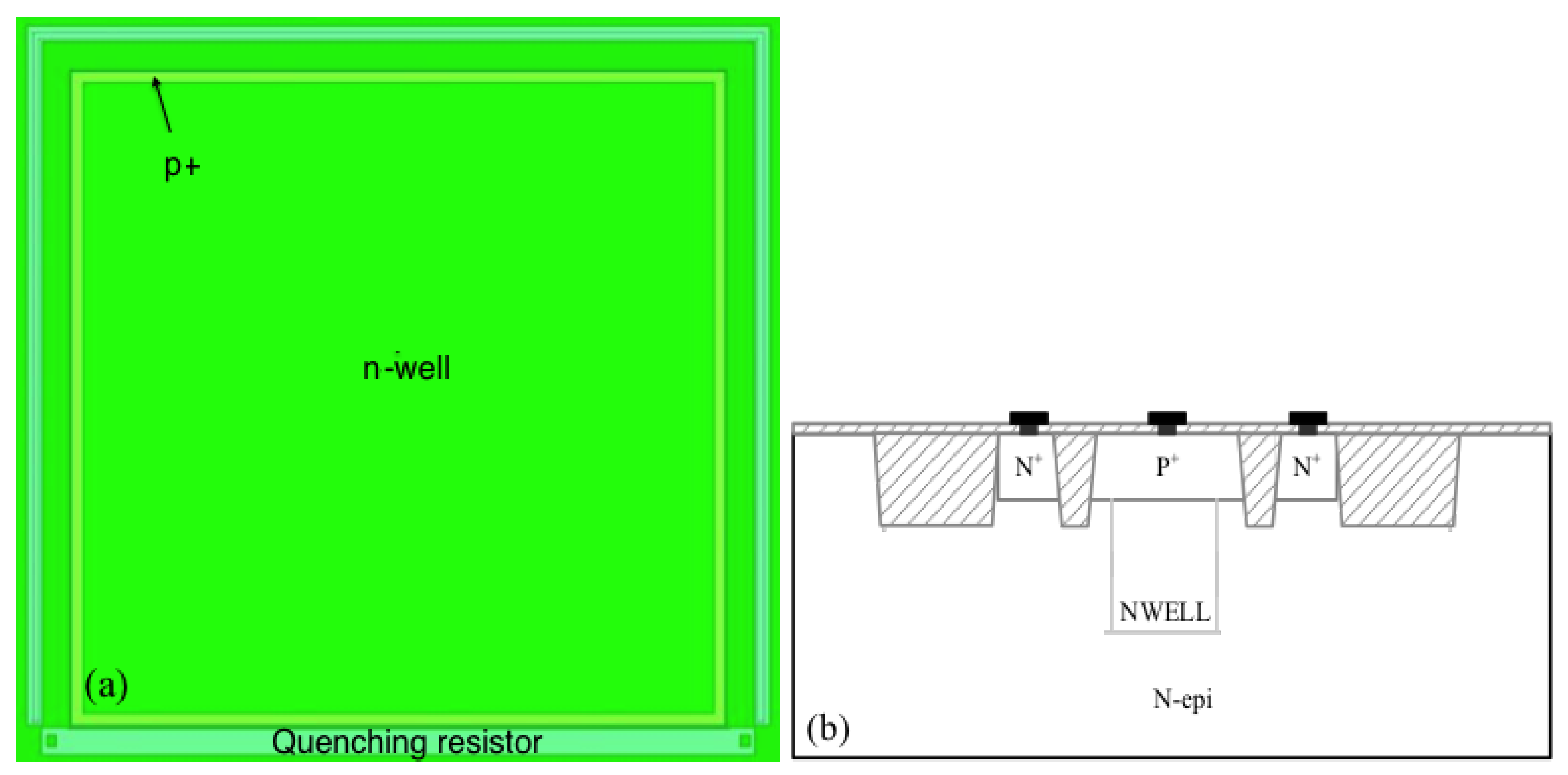

2. Materials and Methods

2.1. Simulation of SiPM

2.2. Fabrication of SiPM

3. Characterization Results

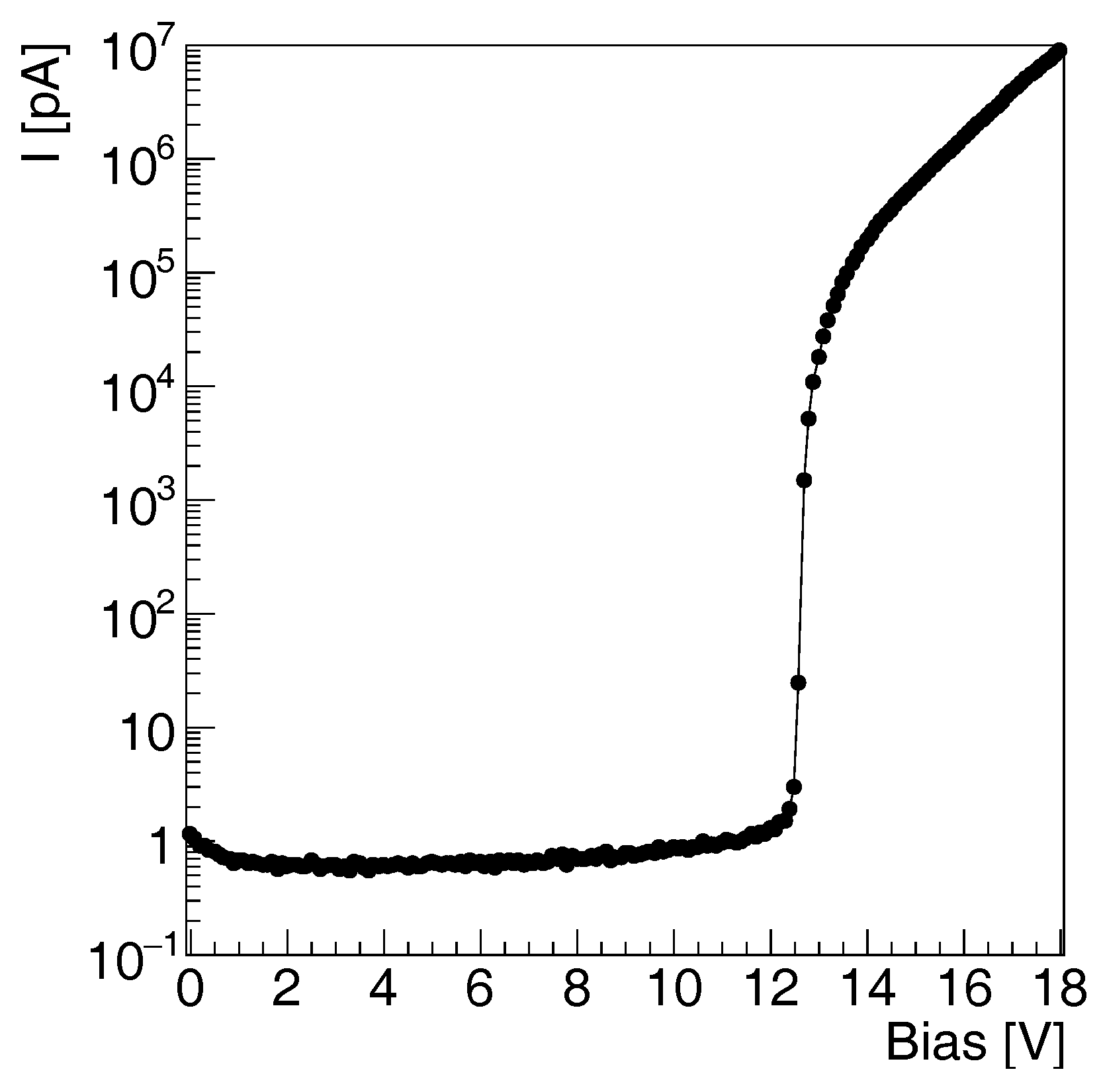

3.1. Static Characterization

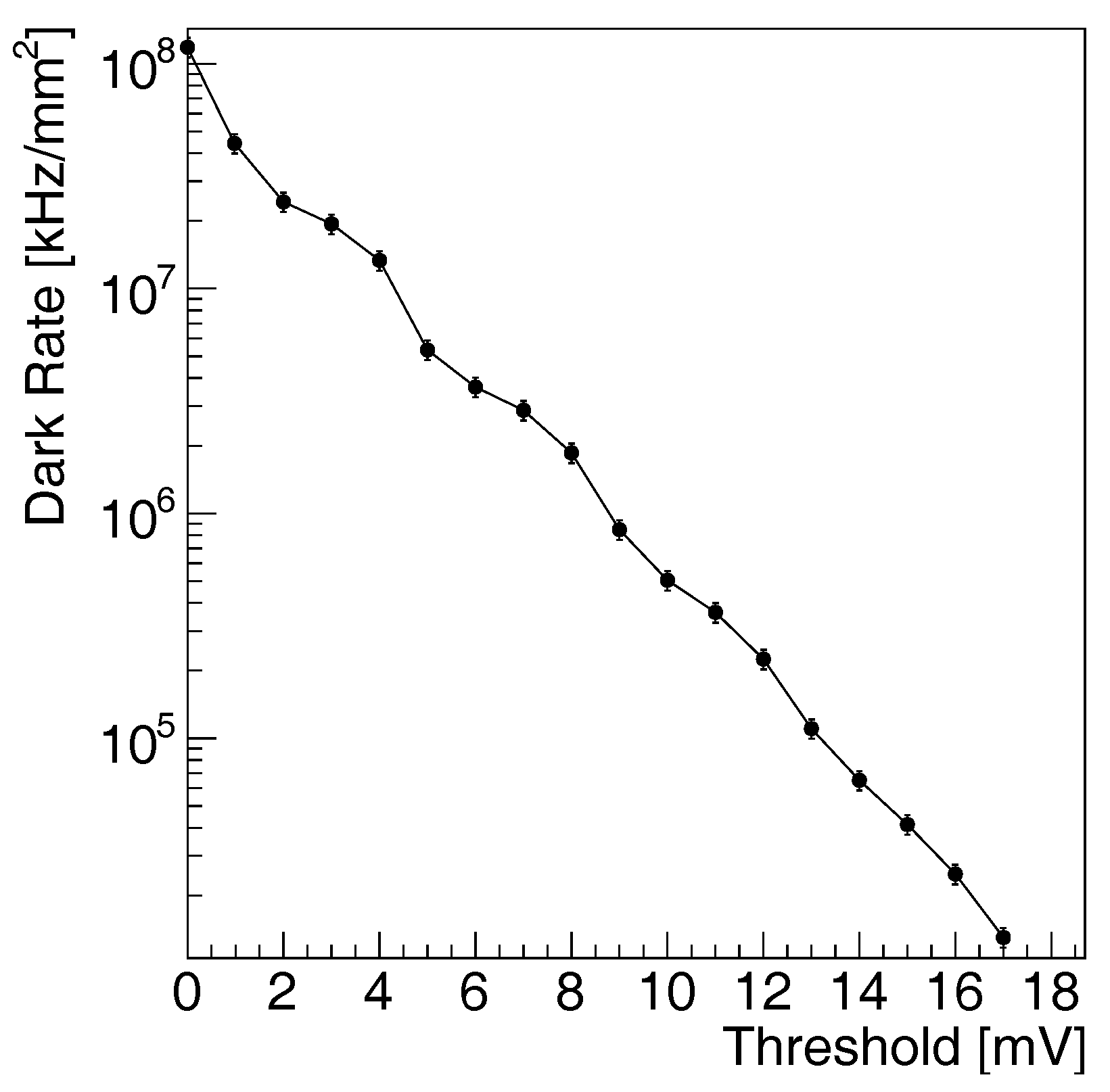

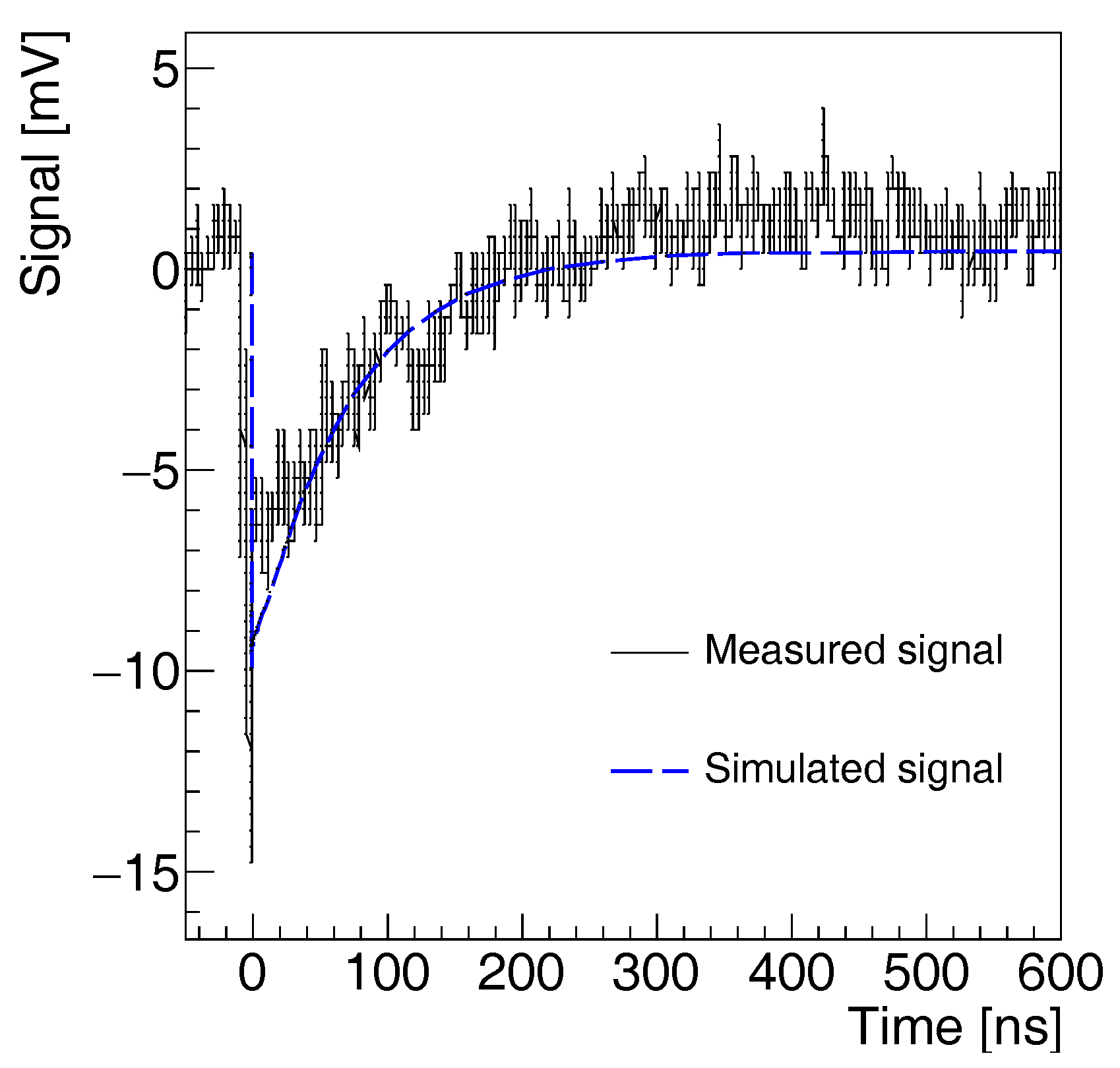

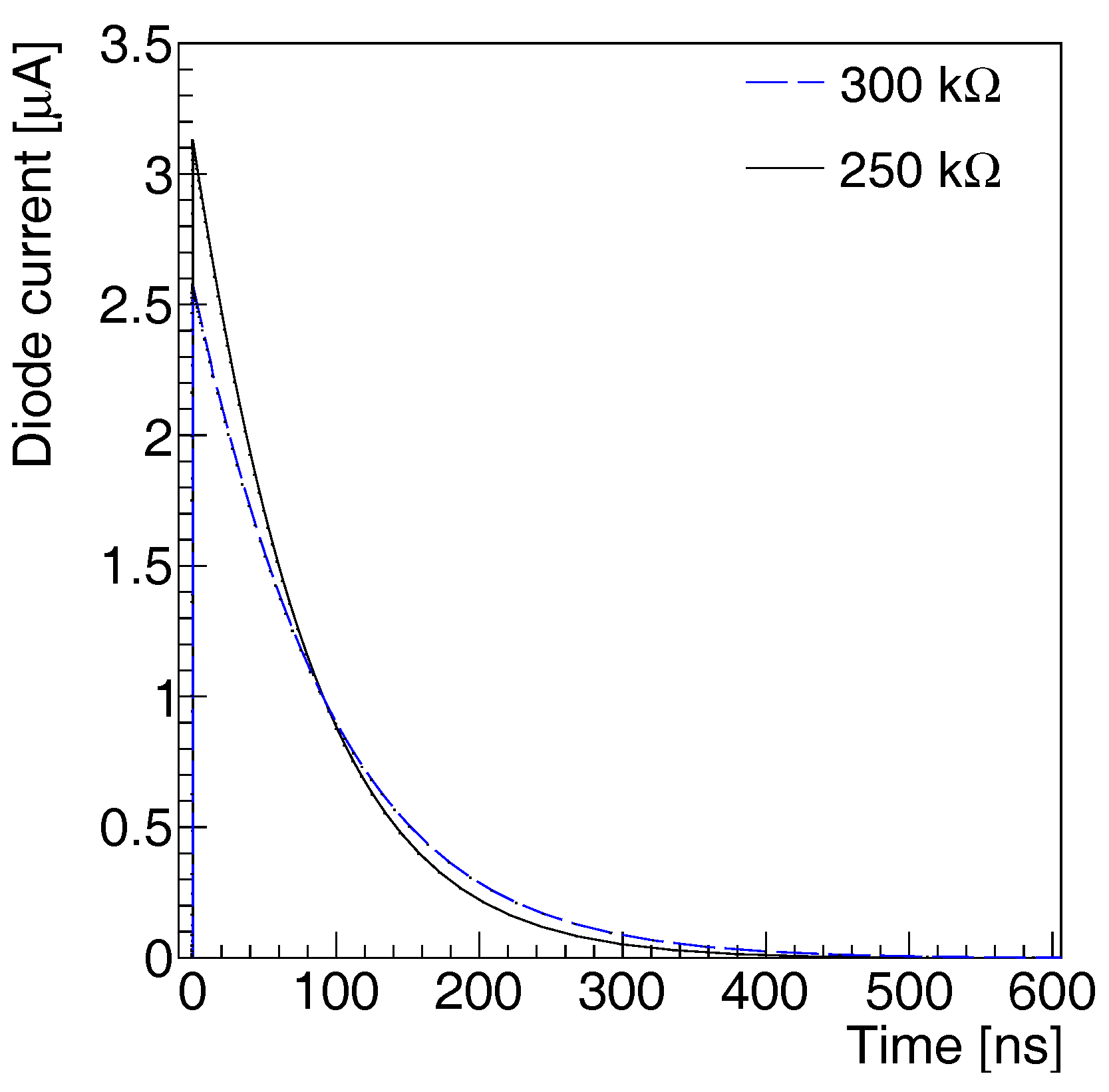

3.2. Dynamic Characterization

3.2.1. Noise Study

3.2.2. Light Study

4. Conclusions

Acknowledgments

Author Contributions

Conflicts of Interest

Abbreviations

| BV | Breakdown Voltage |

| GF | GLOBALFOUNDRIES |

| GR | Guard Ring |

| HRP | High Resistance Polysilicon |

| MRS | Metal Resistor Semiconductor |

| OPTO | Optical coupling module |

| PDE | Photon Detection Efficiency |

| QDC | Charge Digital Converter |

| SiPM | Silicon Photomultiplier |

| SPAD | Single Photon Avalanche Diode |

| STI | Shallow Trench Isolation |

References

- Gasanov, A.; Golovin, V.; Sadygov, Z.Y.; Yusipov, N.Y. Avalanche photodetector based on metal-resistive-layer semiconductor structures. Pisma V Zhurnal Tekh. Fiz. 1988, 14, 706–709. [Google Scholar]

- Shushakov, D.A.; Shubin, V.E. New Solid State Photomultiplier. In Proceedings of the Optoelectronic Integrated Circuit Materials, Physics, and Devices, Bellingham, WA, USA, 24 April 1995; pp. 544–554. [Google Scholar]

- Sadygov, Z. Avalanche Detector. Russian Patent RU 2102820, 10 October 1996. [Google Scholar]

- Golovin, M.; Akindinov, A.; Grigorev, E.; Martemyanov, A.; Polozov, P. New results on mrs apds. Nucl. Instrum. Methods A 1997, 387, 231–234. [Google Scholar]

- Saveliev, V.; Golovin, V. Silicon avalanche photodiodes on the base of metal-resistor-semiconductor (mrs) structures. Nucl. Instrum. Methods A 2000, 442, 223–229. [Google Scholar] [CrossRef]

- Buzhan, P.; Dolgoshein, B.; Ilyin, A.; Kantserov, V.; Kaplin, V.; Karakash, A.; Pleshko, A.; Popova, E.; Smirnov, S.; Volkov, Y. An advanced study of silicon photomultiplier. ICFA Instrum. Bull. 2001, 21, 28–41. [Google Scholar]

- Piemonte, C.; Battiston, R.; Boscardin, M.; Dalla Betta, G.-F.; Del Guerra, A.; Dinu, N.; Pozza, A.; Zorzi, N. Characterization of the first prototypes of silicon photomultiplier fabricated at itc-irst. IEEE Trans. Nucl. Sci. 2007, 54, 236–244. [Google Scholar] [CrossRef]

- Stewart, A.; Saveliev, V.; Bellis, S.; Herbert, D.; Hughes, P.; Jackson, J. Performance of 1 mm2 silicon photomultiplier. IEEE J. Quant. Electron. 2008, 44, 157–164. [Google Scholar] [CrossRef]

- Ghassemi, A.; Sato, K.; Kobayashi, K. MPPC; Hamamatsu Technical Note. KAPD9005E01; Hamamatsu Photonics: Hamamatsu, Japan, 2017. [Google Scholar]

- Nolet, F.; Rhéaume, V.-P.; Parent, S.; Charlebois, S.A.; Fontaine, R.; Pratte, J.-F. A 2d proof of principle towards a 3D digital SiPM in HV CMOS with low output capacitance. IEEE Trans. Nucl. Sci. 2016, 63, 2293–2299. [Google Scholar] [CrossRef]

- Cova, S.; Lacaita, A.; Ghioni, M.; Ripamonti, G.; Louis, T. 20 ps timing resolution with single-photon avalanche diodes. Rev. Sci. Instrum. 1989, 60, 1104–1110. [Google Scholar] [CrossRef]

- Villa, F.; Bronzi, D.; Zou, Y.; Scarcella, C.; Boso, G.; Tisa, S.; Tosi, A.; Zappa, F.; Durini, D.; Weyers, S. CMOS SPADs with up to 500 μm diameter and 55% detection efficiency at 420 nm. J. Mod. Opt. 2014, 61, 102–115. [Google Scholar] [CrossRef]

- D’Ascenzo, N.; Saveliev, V. The new photo-detectors for high energy physics and nuclear medicine. In Photodiodes-Communications, Bio-Sensings, Measurements and High-Energy Physics; InTech: Rijeka, Croatia, 2011. [Google Scholar]

- Patti, R.S. Three-dimensional integrated circuits and the future of system-on-chip designs. Proc. IEEE 2006, 94, 1214–1224. [Google Scholar] [CrossRef]

- Vilella, E.; Alonso, O.; Dieguez, A. 3D integration of geiger-mode avalanche photodiodes aimed to very high fill-factor pixels for future linear colliders. Nucl. Instrum. Methods Phys. Res. Sect. A Accel. Spectrometers Detect. Assoc. Equip. 2013, 731, 103–108. [Google Scholar] [CrossRef]

- D’Ascenzo, N.; Marrocchesi, P.; Moon, C.; Morsani, F.; Ratti, L.; Saveliev, V.; Navarro, A.S.; Xie, Q. Silicon avalanche pixel sensor for high precision tracking. J. Instrum. 2014, 9, C03027. [Google Scholar] [CrossRef]

- Pancheri, L.; Ficorella, A.; Brogi, P.; Collazuol, G.; Dalla Betta, G.-F.; Marrocchesi, P.; Morsani, F.; Ratti, L.; Savoy-Navarro, A.; Sulaj, A. First demonstration of a two-tier pixelated avalanche sensor for charged particle detection. IEEE J. Electron Devices Soc. 2017, 5, 404–410. [Google Scholar] [CrossRef]

- Fischer, P.; Armbruster, T.; Blanco, R.; Ritzert, M.; Sacco, I.; Weyers, S. A dense spad array with full frame readout and fast cluster position reconstruction. In Proceedings of the IEEE Nuclear Science Symposium and Medical Imaging Conference (NSS/MIC), Seattle, WA, USA, 8–15 November 2014. [Google Scholar]

- Izhaky, N.; Morse, M.T.; Koehl, S.; Cohen, O.; Rubin, D.; Barkai, A.; Sarid, G.; Cohen, R.; Paniccia, M.J. Development of CMOS-compatible integrated silicon photonics devices. IEEE J. Sel. Top. Quant. Electron. 2006, 12, 1688–1698. [Google Scholar] [CrossRef]

- Lee, M.-J.; Rucker, H.; Choi, W.-Y. Effects of guard-ring structures on the performance of silicon avalanche photodetectors fabricated with standard CMOS technology. IEEE Electron Device Lett. 2012, 33, 80–82. [Google Scholar] [CrossRef]

- Lee, M.-J.; Choi, W.-Y. Effects of parasitic resistance on the performance of silicon avalanche photodetectors in standard CMOS technology. IEEE Electron Device Lett. 2016, 37, 60–63. [Google Scholar] [CrossRef]

- Sul, W.-S.; Oh, J.-H.; Lee, C.-H.; Cho, G.-S.; Lee, W.-G.; Kim, S.-D.; Rhee, J.-K. Guard-ring structures for silicon photomultipliers. IEEE Electron Device Lett. 2010, 31, 41–43. [Google Scholar]

- Niclass, C.; Rochas, A.; Besse, P.-A.; Charbon, E. Toward a 3-D camera based on single photon avalanche diodes. IEEE J. Sel. Top. Quant. Electron. 2004, 10, 796–802. [Google Scholar] [CrossRef]

- Rochas, A.; Gosch, M.; Serov, A.; Besse, P.; Popovic, R.; Lasser, T.; Rigler, R. First fully integrated 2-D array of single-photon detectors in standard CMPS technology. IEEE Photonics Technol. Lett. 2003, 15, 963–965. [Google Scholar] [CrossRef]

- Tisa, S.; Zappa, F.; Labanca, I. On-chip detection and counting of single-photons. In Proceedings of the IEEE International Electron Devices Meeting on IEDM Technical Digest, Washington, DC, USA, 5–7 December 2005; pp. 815–818. [Google Scholar]

- Stoppa, D.; Pancheri, L.; Scandiuzzo, M.; Gonzo, L.; Dalla Betta, G.-F.; Simoni, A. A cmos 3-d imager based on single photon avalanche diode. IEEE Trans. Circuits Syst. 2007, 54, 4–12. [Google Scholar] [CrossRef]

- Niclass, C.; Rochas, A.; Besse, P.-A.; Charbon, E. Design and characterization of a CMOS 3-D image sensor based on single photon avalanche diodes. IEEE J. Solid-State Circuits 2005, 40, 1847–1854. [Google Scholar] [CrossRef]

- Stoppa, D.; Pancheri, L.; Scandiuzzo, M.; Malfatti, M.; Pedretti, G.; Gonzo, L. A single-photon-avalanche-diode 3D imager. In Proceedings of the 31st European Solid-State Circuits Conference, Grenoble, France, 12–16 September 2005; pp. 487–490. [Google Scholar]

- Rochas, A.; Gani, M.; Furrer, B.; Besse, P.; Popovic, R.; Ribordy, G.; Gisin, N. Single photon detector fabricated in a complementary metal-oxide-semiconductor high-voltage technology. Rev. Sci. Instrum. 2003, 74, 3263–3270. [Google Scholar] [CrossRef]

- Bérubé, B.-L.; Rhéaume, V.-P.; Parent, S.; Maurais, L.; Therrien, A.C.; Charette, P.G.; Charlebois, S.A.; Fontaine, R.; Pratte, J.-F. Implementation study of single photon avalanche diodes (spad) in 0.8μm HV CMOS technology. IEEE Trans. Nucl. Sci. 2015, 62, 710–718. [Google Scholar] [CrossRef]

- Pancheri, L.; Stoppa, D. Low-noise CMOS single-photon avalanche diodes with 32 ns dead time. In Proceedings of the 37th European Solid State Device Research Conference, Munich, Germany, 11–13 September 2007; pp. 362–365. [Google Scholar]

- Habib, M.H.U.; McFarlane, N. A perimeter gated single photon avalanche diode based silicon photomultiplier as optical detector. In Proceedings of the 2015 IEEE 58th International Midwest Symposium on Circuits and Systems (MWSCAS), Fort Collins, CO, USA, 2–5 August 2015; pp. 1–4. [Google Scholar]

- Gu, J.; Habib, M.H.U.; McFarlane, N. Perimeter gated single photon avalanche diodes: An information theoretic assessment. IEEE Photon. Technol. Lett. 2016, 28, 701–704. [Google Scholar] [CrossRef]

- Niclass, C.; Sergio, M.; Charbon, E. A Single Photon Avalanche Diode Array Fabricated in 0.35 μM CMOS and Based on an Event-Driven Readout for TCSPC Experiments; SPIE Optics East: Boston, MA, USA, 2006. [Google Scholar]

- Niclass, C.; Favi, C.; Kluter, T.; Monnier, F.; Charbon, E. Single-photon synchronous detection. IEEE J. Solid-State Circuits 2009, 44, 1977–1989. [Google Scholar] [CrossRef]

- Tisa, S.; Guerrieri, F.; Tosi, A.; Zappa, F. 100 kframe/s 8 bit monolithic single-photon imagers. In Proceedings of the 2008 38th European Solid-State Device Research Conference, Edinburgh, UK, 15–19 September 2008; pp. 274–277. [Google Scholar]

- Tisa, S.; Guerrieri, F.; Zappa, F. Variable-load quenching circuit for single-photon avalanche diodes. Opt. Express 2008, 16, 2232–2244. [Google Scholar] [CrossRef] [PubMed]

- Stoppa, D.; Mosconi, D.; Pancheri, L.; Gonzo, L. Single-photon avalanche diode cmos sensor for time-resolved fluorescence measurements. IEEE Sens. J. 2009, 9, 1084–1090. [Google Scholar] [CrossRef]

- Arbat, A.; Trenado, J.; Gascon, D.; Vilá, A.; Comerma, A.; Garrido, L.; Diéguez, A. High voltage vs. High integration: A comparison between CMOS technologies for SPAD cameras. In Proceedings of the SPIE Optics and Photonics, San Diego, CA, USA, 19–23 August 2010; Volume 7780. [Google Scholar]

- Niclass, C.; Favi, C.; Kluter, T.; Gersbach, M.; Charbon, E. A 128×128 single-photon image sensor with column-level 10-bit time-to-digital converter array. IEEE J. Solid-State Circuits 2008, 43, 2977–2989. [Google Scholar] [CrossRef]

- Vilella, E.; Alonso, O.; Montiel, A.; Vilá, A.; Diéguez, A. A low-noise time-gated single-photon detector in a HV-CMOS technology for triggered imaging. Sens. Actuators A Phys. 2013, 201, 342–351. [Google Scholar] [CrossRef]

- Nissinen, I.; Nissinen, J.; Lansman, A.; Hallman, L.; Kilpela, A.; Kostamovaara, J.; Kogler, M.; Aikio, M.; Tenhunen, J. A sub-ns time-gated CMOS single photon avalanche diode detector for raman spectroscopy. In Proceedings of the 2011 European Solid-State Device Research Conference, Helsinki, Finland, 12–16 September 2011; pp. 375–378. [Google Scholar]

- Schwinger, A.; Brockherdea, W.; Hostickaa, B.J.; Vogta, H. CMOS SiPM with integrated amplifier. In Proceedings of the SPIE OPTO, San Francisco, CA, USA, 16 February 2017; p. 101001A. [Google Scholar]

- Zou, Y.; Villa, F.; Bronzi, D.; Tisa, S.; Tosi, A.; Zappa, F. Planar CMOS analog SiPMs: Design, modeling, and characterization. J. Mod. Opt. 2015, 62, 1693–1702. [Google Scholar] [CrossRef] [Green Version]

- Vilella, E.; Diéguez, A. A gated single-photon avalanche diode array fabricated in a conventional CMOS process for triggered systems. Sens. Actuators A Phys. 2012, 186, 163–168. [Google Scholar] [CrossRef]

- Jradi, K.; Pellion, D.; Ginhac, D. Design, characterization and analysis of a 0.35 μm CMOS SPAD. Sensors 2014, 14, 22773–22784. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Finkelstein, H.; Hsu, M.J.; Esener, S.C. Sti-bounded single-photon avalanche diode in a deep-submicrometer cmos technology. IEEE Electron Device Lett. 2006, 27, 887–889. [Google Scholar] [CrossRef]

- Faramarzpour, N.; Deen, M.J.; Shirani, S.; Fang, Q. Fully integrated single photon avalanche diode detector in standard cmos 0.18-μm technology. IEEE Trans. Electron Devices 2008, 55, 760–767. [Google Scholar] [CrossRef]

- Vornicu, I.; Bandi, F.N.; Carmona-Galán, R.; Rodríguez-Vázquez, Á. A CMOS digital SiPM with focal-plane light-spot statistics for DOI computation. IEEE Sens. J. 2017, 17, 632–643. [Google Scholar] [CrossRef]

- Pancheri, L.; Stoppa, D. Low-noise single photon avalanche diodes in 0.15 μm CMOS technology. In 2011 Proceedings of the European Solid-State Device Research Conference, Helsinki, Finland, 12–16 September 2011; pp. 179–182. [Google Scholar]

- Richardson, J.A.; Grant, L.A.; Henderson, R.K. Low dark count single-photon avalanche diode structure compatible with standard nanometer scale cmos technology. IEEE Photonics Technol. Lett. 2009, 21, 1020–1022. [Google Scholar] [CrossRef]

- Gersbach, M.; Maruyama, Y.; Trimananda, R.; Fishburn, M.W.; Stoppa, D.; Richardson, J.A.; Walker, R.; Henderson, R.; Charbon, E. A time-resolved, low-noise single-photon image sensor fabricated in deep-submicron CMOS technology. IEEE J. Solid-State Circuits 2012, 47, 1394–1407. [Google Scholar] [CrossRef]

- Henderson, R.K.; Richardson, J.; Grant, L. Reduction of band-to-band tunneling in deep-submicron cmos single photon avalanche photodiodes. In Proceedings of the International Image Sensor Workshop (IISW 2009), Bergen, Norway, 22–28 June 2009; pp. 26–28. [Google Scholar]

- Niclass, C.; Gersbach, M.; Henderson, R.; Grant, L.; Charbon, E. A single photon avalanche diode implemented in 130-nm CMOS technology. IEEE J. Sel. Top. Quant. Electron. 2007, 13, 863–869. [Google Scholar] [CrossRef]

- Arbat, A. Towards A Froward Tracker Detector Based on Geiger Mode Avalanche Photodiodes for Future Linear Colliders. Ph.D. Thesis, Department Electronics, University Barcelona, Barcelona, Spain, 2010. [Google Scholar]

- Karami, M.A.; Gersbach, M.; Yoon, H.-J.; Charbon, E. A new single-photon avalanche diode in 90 nm standard CMOS technology. Opt. Express 2010, 18, 22158–22166. [Google Scholar] [CrossRef] [PubMed]

- Webster, E.A.; Richardson, J.A.; Grant, L.A.; Renshaw, D.; Henderson, R.K. A single-photon avalanche diode in 90-nm CMOS imaging technology with 44% photon detection efficiency at 690 nm. IEEE Electron Device Lett. 2012, 33, 694–696. [Google Scholar] [CrossRef]

- Durini, D.; Paschen, U.; Schwinger, A.; Spickermenn, A. Silicon based single-photon avalanche diode (SPAD) technology for low-light and high speed applications. In Photodetectors; Nabet, B., Ed.; Elsevier: Tokyo, Japan, 2016; pp. 345–371. [Google Scholar]

- SILVACO. Available online: www.silvaco.com (accessed on 22 September 2017).

- Shockley, W.; Read, W., Jr. Statistics of the recombinations of holes and electrons. Phys. Rev. 1952, 87, 835–842. [Google Scholar] [CrossRef]

- Fossum, J.; Lee, D. A physical model for the dependence of carrier lifetime on doping density in nondegenerate silicon. Solid-State Electron. 1982, 25, 741–747. [Google Scholar] [CrossRef]

- Selberherr, S. Analysis and Simulation of Semiconductor Devices; Springer Science & Business Media: Berlin, Germany, 2012. [Google Scholar]

- Caughey, D.; Thomas, R. Carrier mobilities in silicon empirically related to doping and field. Proc. IEEE 1967, 55, 2192–2193. [Google Scholar] [CrossRef]

- Slotboom, J.; De Graaff, H. Measurements of bandgap narrowing in si bipolar transistors. Solid-State Electron. 1976, 19, 857–862. [Google Scholar] [CrossRef]

- D’Ascenzo, N.; Saveliev, V.; Xie, Q. Design and test of SiPM structures in CMOS technology. In Proceedings of the 2016 4th International Conference on Photonics, Optics and Laser Technology (PHOTOPTICS), Rome, Italy, 27–29 Feberuary 2016; pp. 1–8. [Google Scholar]

- MiniCircuits. Available online: www.minicircuits.com (accessed on 22 September 2017).

- Datasheet of the SensL MicroC Series. 2015. Available online: http://sensl.com/downloads/ds/DS-MicroCseries.pdf (accessed on 22 September 2017).

- D’Ascenzo, N.; Saveliev, V.; Wang, L.; Xie, Q. Analysis of photon statistics with silicon photomultiplier. J. Instrum. 2015, 10, C08017. [Google Scholar] [CrossRef]

- Finocchiaro, P.; Pappalardo, A.; Cosentino, L.; Belluso, M.; Billotta, S.; Bonanno, G.; Di Mauro, S. Features of silicon photo multipliers: Precision measurements of noise, cross-talk, afterpulsing, detection efficiency. IEEE Trans. Nucl. Sci. 2009, 56, 1033–1041. [Google Scholar] [CrossRef]

- Chmill, V.; Garutti, E.; Klanner, R.; Nitschke, M.; Schwandt, J. On the characterisation of SiPMs from pulse-height spectra. Nucl. Instrum. Methods Phys. Res. Sect. A Accel. Spectrometers Detect. Assoc. Equip. 2017, 854, 70–81. [Google Scholar] [CrossRef]

| Techn. | Pixel | Typical | Gain | Dark Count | Cross-talk | PDE |

|---|---|---|---|---|---|---|

| Node | Size | Operation | @typ. bias | @410 nm | ||

| (nm) | (m) | (V) | (KHz/mm) | (%) | (%) | |

| 800 [10] | 2500 | 15 (estimated) | ||||

| 800 [30] | 2500 | 20 | ||||

| 800 [30] | 2500 | 25 | ||||

| 800 [30] | 2500 | 25 | ||||

| 500 [32] | 484 | <120 | 15 (estimated) | |||

| 350 [41] | 2000 | 2.6 | 1.5 | |||

| 350 [44] | 2500 | 503 | 33.5 | 34 | ||

| 350 [43] | 913 | 2 | ||||

| 350 [18] | 3185.47 | 75–100 | ||||

| 180 | 2500 | 40 | 1.3 | |||

| 180 [49] | 1024 | 4 | ||||

| 130 [15] | 324,900 | |||||

| SensL [67] | 100–2500 | 30–100 | <2 | 40 | ||

| Hamamatsu [9] | 625–10,000 | 500 | 40 |

© 2017 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

D’Ascenzo, N.; Zhang, X.; Xie, Q. Application of CMOS Technology to Silicon Photomultiplier Sensors. Sensors 2017, 17, 2204. https://doi.org/10.3390/s17102204

D’Ascenzo N, Zhang X, Xie Q. Application of CMOS Technology to Silicon Photomultiplier Sensors. Sensors. 2017; 17(10):2204. https://doi.org/10.3390/s17102204

Chicago/Turabian StyleD’Ascenzo, Nicola, Xi Zhang, and Qingguo Xie. 2017. "Application of CMOS Technology to Silicon Photomultiplier Sensors" Sensors 17, no. 10: 2204. https://doi.org/10.3390/s17102204