Nanometric Integrated Temperature and Thermal Sensors in CMOS-SOI Technology

Abstract

:1. Introduction

2. Temperature and Thermal Sensors

- A non-thermal signal is transduced into a heat flow.

- The heat flow is converted, within the thermal signal domain, into a temperature difference.

- The temperature difference is transduced into an electric signal with a temperature sensor.

3. Thermal Characterization

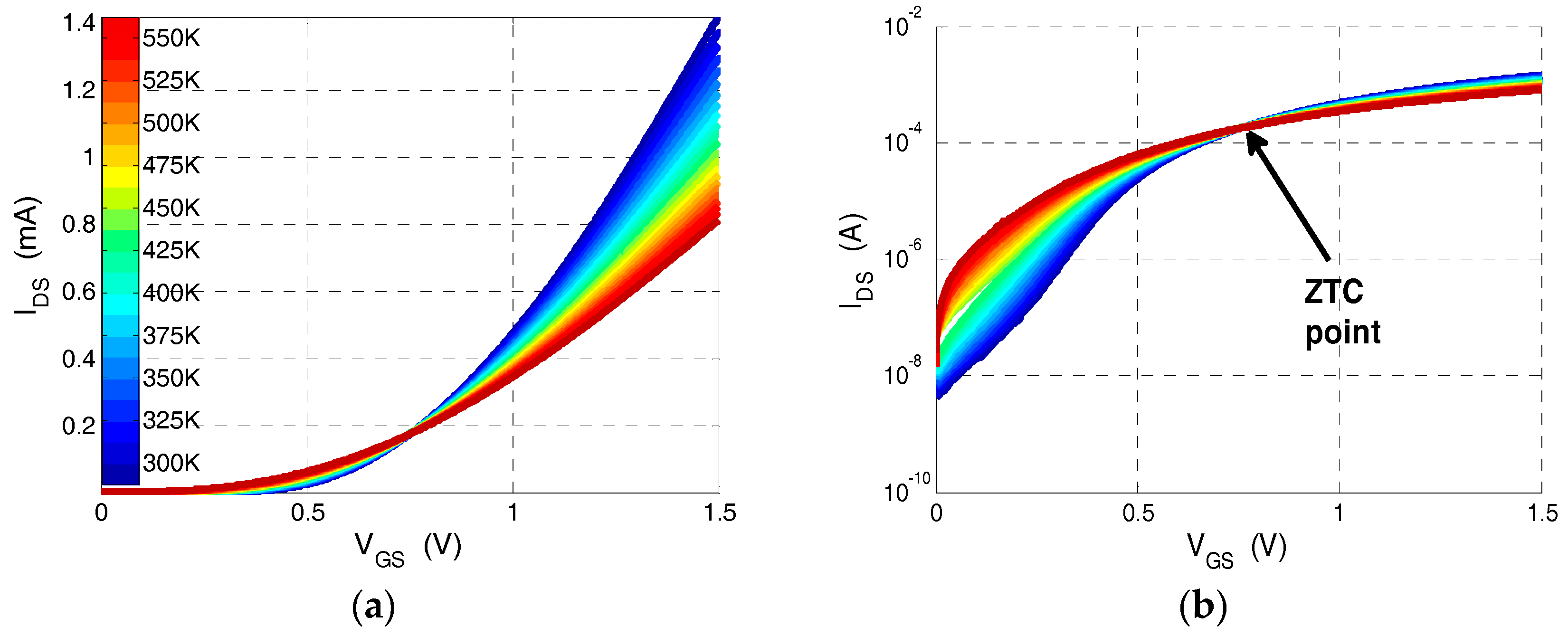

3.1. MOSFET Transistor

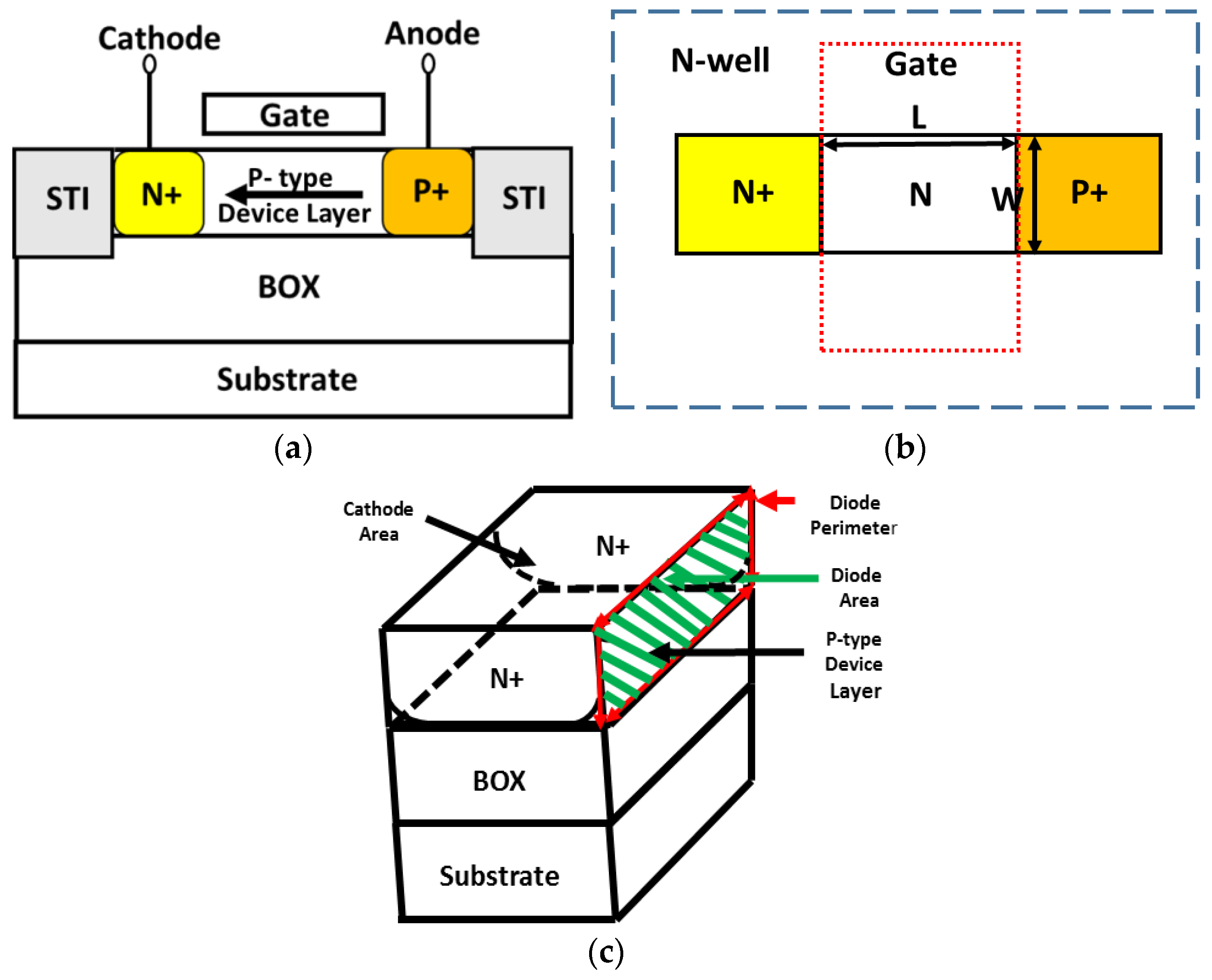

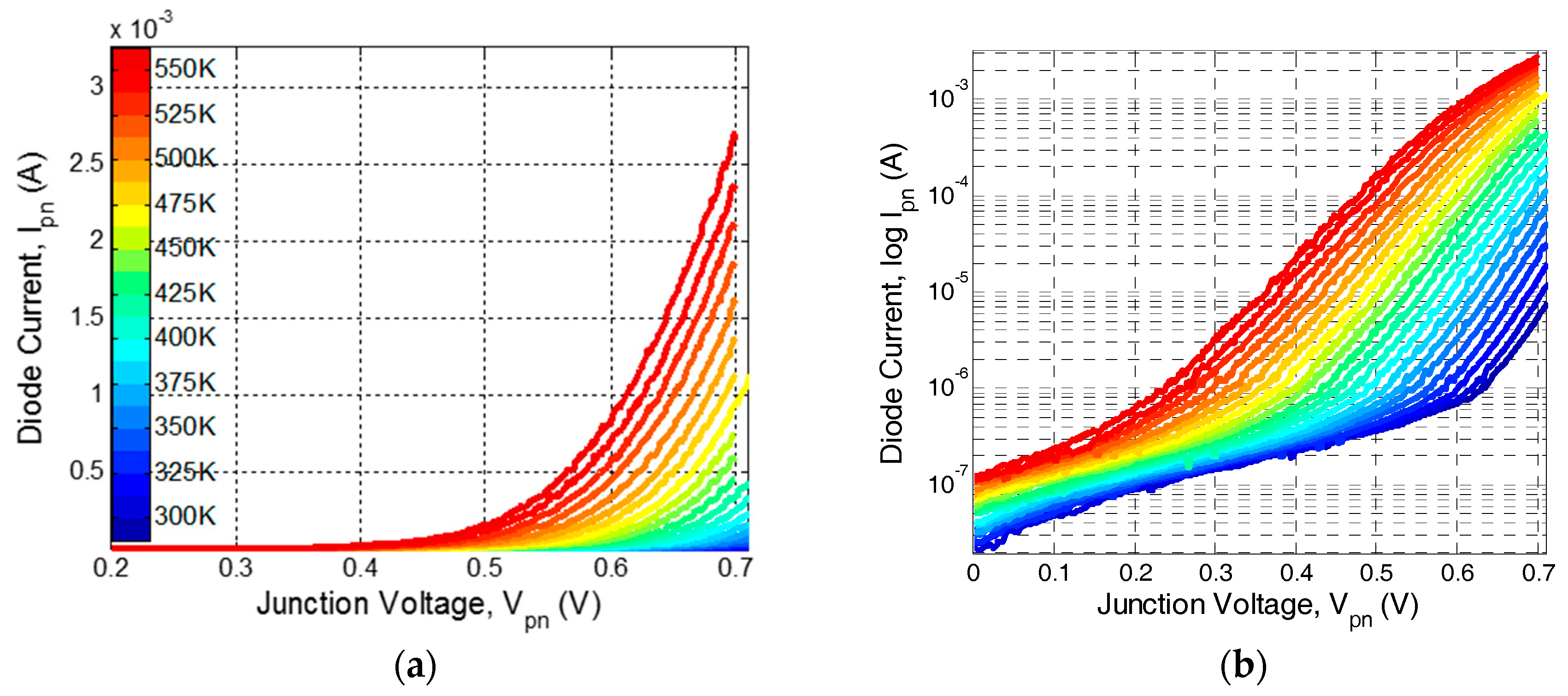

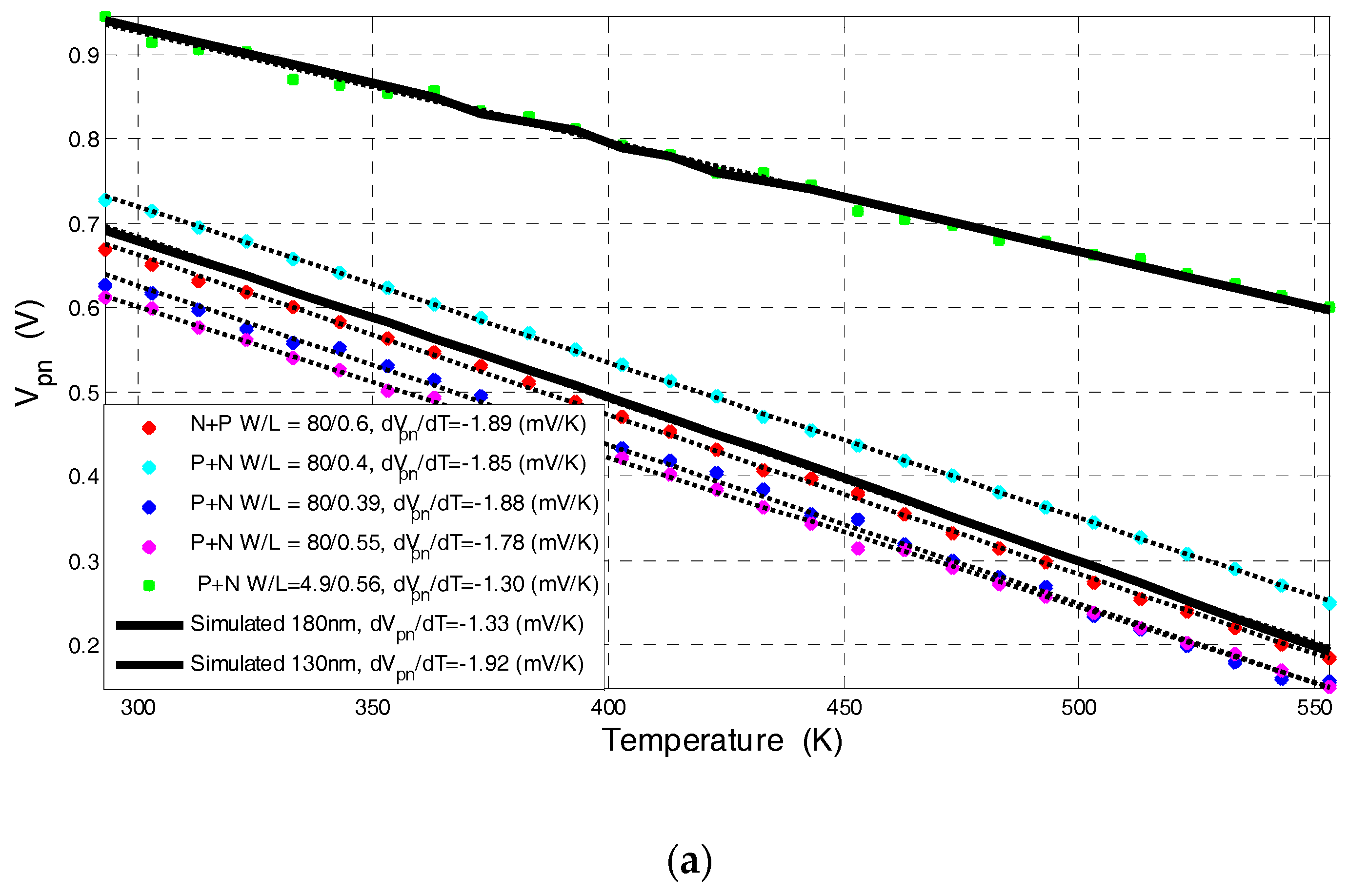

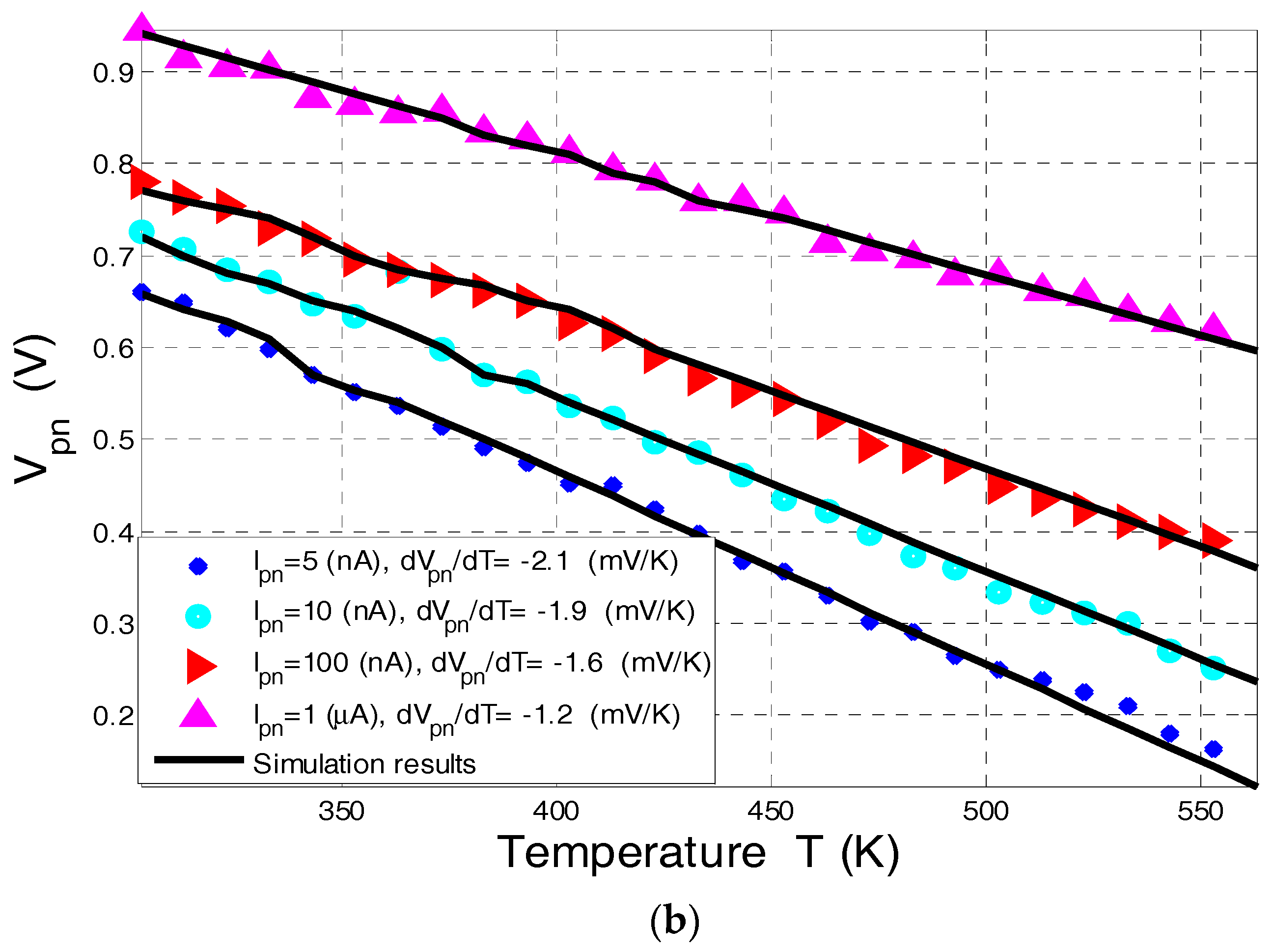

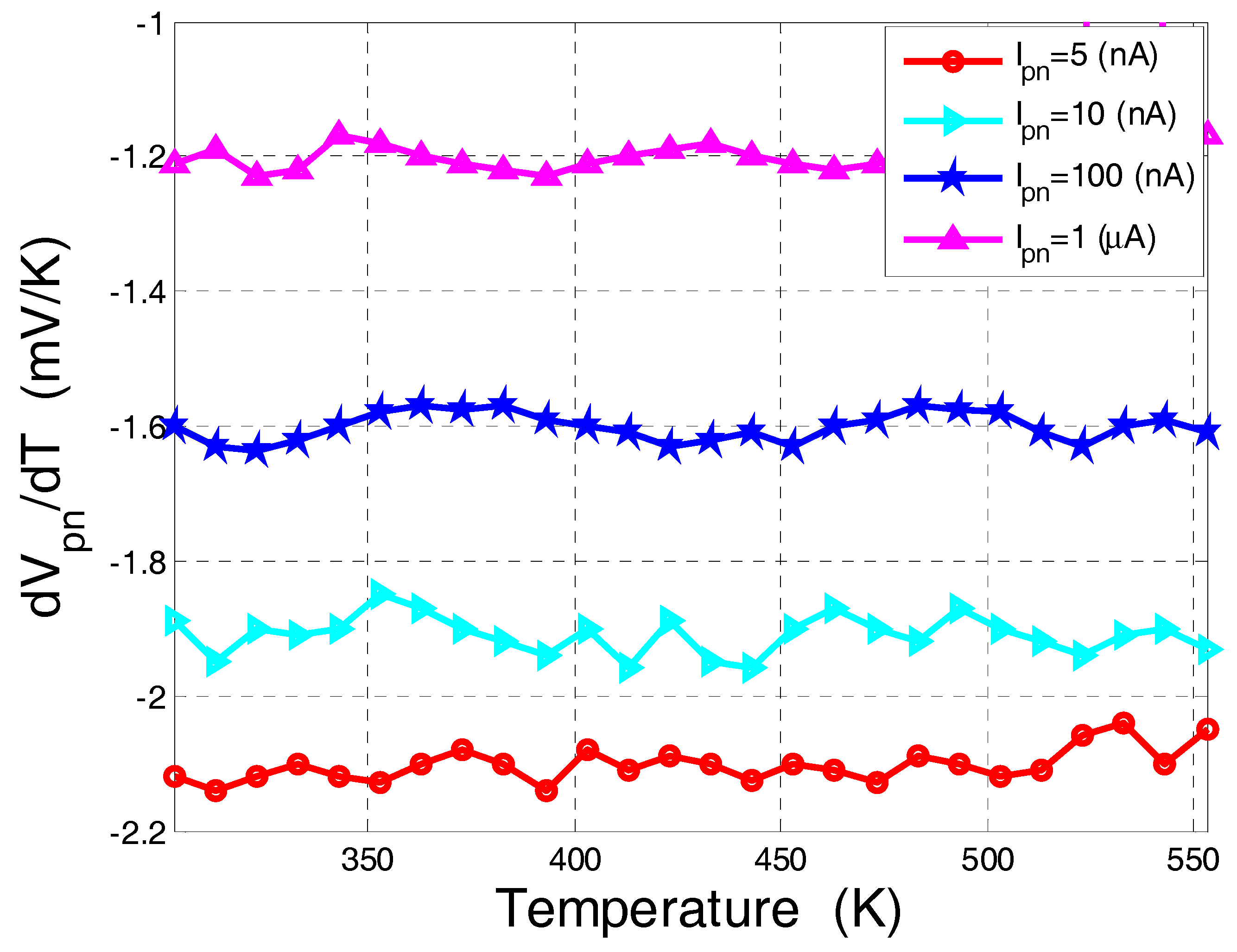

3.2. Lateral Diode

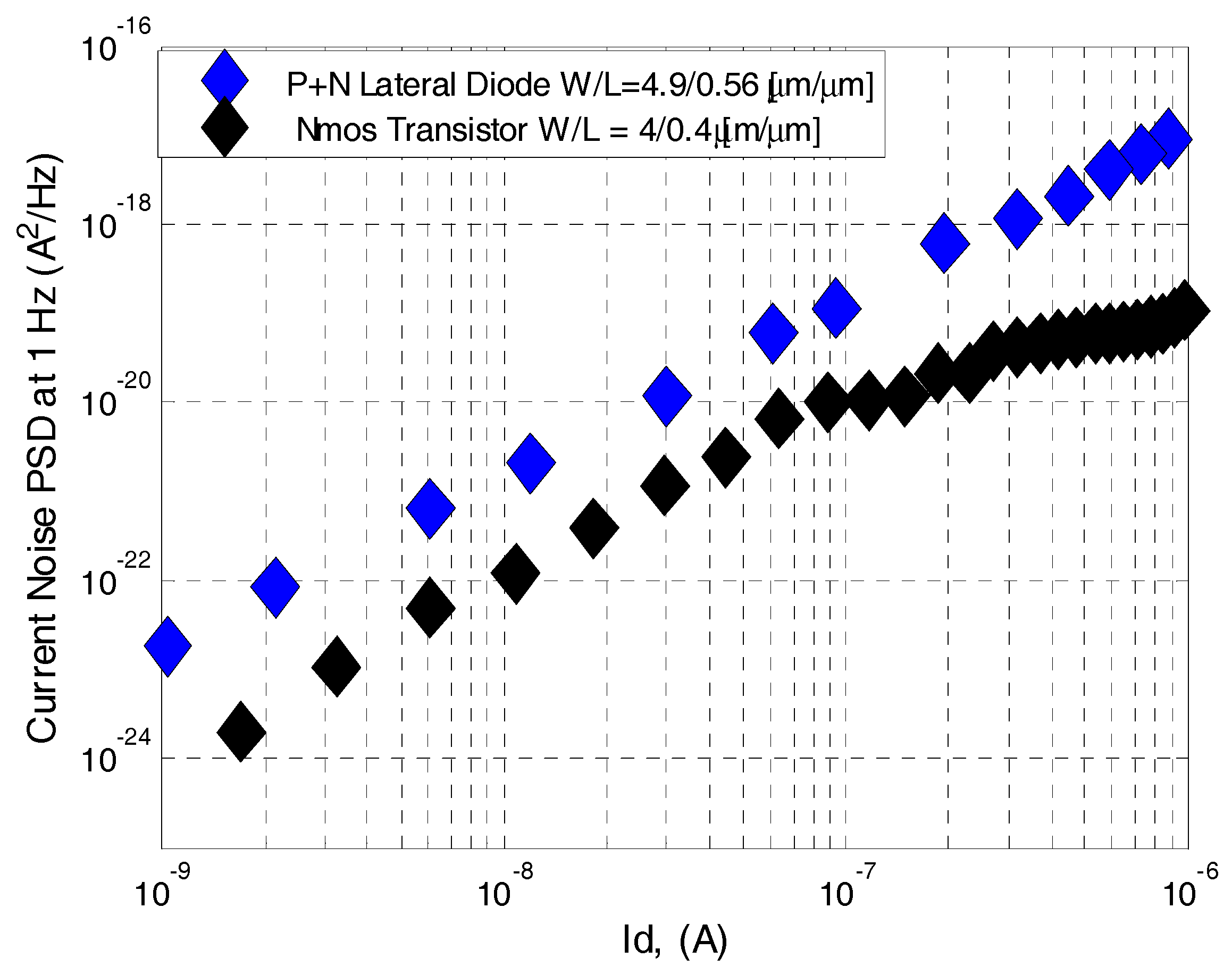

4. Noise Characterization

5. Conclusions

Acknowledgments

Author Contributions

Conflicts of Interest

References

- Gianesello, F.; Giry, A.; Richard, O.; Bon, O.; Boret, S.; Blanchet, F.; Boissonnet, L.; Touret, P.; Cathelin, A.; Belot, D.; et al. Opportunity and Perspectives of using Advanced High Resistivity SOI CMOS technology for the Integration of MultiStandard RF Front-End. In Proceedings of the IEEE Power Amplifier Symposium, San Diego, CA, USA, 19 January 2009. [Google Scholar]

- François, B.; Reynaert, P. Highly Linear Fully Integrated Wideband RF PA for LTE-Advanced in 180-nm SOI. IEEE Trans. Microw. Theory Tech. 2015, 63, 649–658. [Google Scholar] [CrossRef]

- Ali, K.B.; Neve, C.R.; Gharsallah, A.; Raskin, J.-P. RF Performance of SOI CMOS Technology on Commercial 200-mm Enhanced Signal Integrity High Resistivity SOI Substrate. IEEE Trans. Electron Devices 2014, 61, 722–728. [Google Scholar] [CrossRef]

- Kim, J.; Dabag, H.; Asbeck, P.; Buckwalter, J.F. Q-Band and WBand Power Amplifiers in 45-nm CMOS SOI. IEEE Trans. Microw. Theory Tech. 2012, 60, 1870–1877. [Google Scholar] [CrossRef]

- Svetlitza, A.; Blank, T.; Stolyarova, S.; Brouk, I.; Shefi, S.B.; Nemirovsky, Y. CMOS-SOI-MEMS Thermal Antenna and Sensor for Uncooled THz Imaging. IEEE Trans. Electron Devices 2016, 63, 1260–1265. [Google Scholar] [CrossRef]

- Nemirovsky, Y.; Svetlitza, A.; Brouk, I.; Stolyarova, S. Nanometric CMOS-SOI-NEMS Transistor for Uncooled THz Sensing. IEEE Trans. Electron Devices 2013, 60, 1575–1583. [Google Scholar] [CrossRef]

- Gitelman, L.; Stolyarova, S.; Bar-Lev, S.; Gutman, Z.; Ochana, Y.; Nemirovsky, Y. CMOS-SOI-MEMS transistor for uncooled IR Imaging. IEEE Trans. Electron Devices 2009, 56, 1935–1942. [Google Scholar] [CrossRef]

- Saraf, T.; Brouk, I.; Shefi, S.B.; Unikovski, A.; Blank, T.; Radhakrishnan, P.K.; Nemirovsky, Y. CMOS-SOI-MEMS Uncooled Infrared Security Sensor with Integrated Readout. IEEE J. Electron Devices Soc. 2016, 4, 155–162. [Google Scholar] [CrossRef]

- Pradeep, K. Exploring the Nano-Scale Self-Heating Mechanisms in SOI/Bulk MOS Device; Master Thesis Report; École Polytechnique Fédérale de Lausanne (EPFL): Lausanne, Switzerland, 2015. [Google Scholar]

- Monga, U.; Aghassi, J.; Siprak, D.; Sedlmeir, J.; Hanke, C.; Kubrak, V.; Heinrich, R.; Fjeldly, T.A. Impact of self-heating in SOI FinFETs on analog circuits and inter-die variability. IEEE Electron Device Lett. 2011, 32, 249–251. [Google Scholar] [CrossRef]

- Chen, J.-H.; Helmi, S.R.; Pajouhi, H.; Sim, Y.; Mohammadi, S. A Wideband RF Power Amplifier in 45-nm CMOS SOI Technology With Substrate Transferred to AlN. IEEE Trans. Microw. Theory Tech. 2012, 60, 4089–4096. [Google Scholar] [CrossRef]

- IBM CSOI7RF. Available online: http://www.mosis.com/vendors/ view/ibm/7rfsoi/ (accessed on 20 October 2014).

- STM H9SOIFEM. Available online: http://www.st.com/content/st_com/en/about/innovation-technology/H9SOIFEM.html (accessed on 25 September 2016).

- Pertijs, M.A.P.; Meijer, G.C.M.; Huijsing, J.H. Precision temperature measurement using CMOS substrate PNP transistors. IEEE Sens. J. 2004, 4, 294–300. [Google Scholar] [CrossRef]

- Pertijs, M.A.P.; Niederkorn, A.; Ma, X.; McKillop, B.; Bakker, A.; Huijsing, J.H. A CMOS smart temperature sensor with an inaccuracy of ±0.5 °C from −50 °C to 120 °C. IEEE J. Solid-State Circuits 2005, 40, 454–461. [Google Scholar] [CrossRef]

- Mohtashim, M.; Ibraheem, H.; Suhail, A.; Andrea De, L.; Florin, U. Silicon diode temperature sensors—A review of applications. Sens. Actuators A 2015, 232, 63–74. [Google Scholar]

- Souri, K.; Souri, K.; Makinwa, K. A 40 μW CMOS Temperature Sensor with an Inaccuracy of ±0.4 °C (3σ) from −55 °C to 200 °C. In Proceedings of the ESSCIRC, Bucharest, Romania, 16–20 September 2013; pp. 221–224. [Google Scholar]

- Székely, V.; Márta, C.; Kohári, Z.; Rencz, M. CMOS sensors for on-line thermal monitoring of VLSI circuits. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 1997, 5, 270–276. [Google Scholar] [CrossRef]

- Chen, P.; Chen, C.; Tsai, C.; Lu, W. A time-to-digital-converter based CMOS smart temperature sensor. IEEE J. Solid-State Circuits. 2005, 40, 1642–1648. [Google Scholar] [CrossRef]

- Santra, S.; Guha, P.K.; Haque, M.S.; Ali, S.Z.; Udrea, F. Si diode temperature sensor beyond 300 °C. In Proceedings of the CAS 2007 International Semiconductor Conference, Sinaia, Romania, 15 October–17 September 2007; pp. 415–418. [Google Scholar]

- De Luca, A.; Pathirana, V.; Ali, S.Z.; Udrea, F. Silicon on insulator thermodiode with extremely wide working temperature range. In Proceedings of the 17th International Conference on Solid-State Sensors, Actuators and Microsystems and Eurosensors XXVII, Barcelona, Spain, 16–20 June 2013; pp. 1911–1914. [Google Scholar]

- De Luca, A.; Pathirana, V.; Ali, S.Z.; Dragomirescu, D.; Udrea, F. Experimental, analytical and numerical investigation of non-linearity of SOI diode temperature sensors at extreme temperatures. Sens. Actuators A 2015, 222, 31–38. [Google Scholar] [CrossRef]

- Sumita, S.; Prasanta, K.G.; Syed Zeeshan, A.; Ibraheem, H.; Florin, U. Silicon on insulator diode temperature sensor–A detailed analysis for ultra-high temperature operation. IEEE Sens. J. 2010, 10, 997–1003. [Google Scholar]

- Malits, M.; Corcos, D.; Svetlitza, A.; Elad, D.; Nemirovsky, Y. Thermal Performance of CMOS-SOI Transistors from Weak to Strong Inversion. IEEE Instrum. Meas. Mag. 2012, 15, 28–34. [Google Scholar] [CrossRef]

- Berkeley Short-channel IGFET Model (BSIM). Available online: http://www-device.eecs.berkeley.edu/bsim/ (accessed on 20 February 2017).

- Fikos, G.; Siskos, S. Low-Voltage Low-Power Accurate CMOS Vt Extractor. IEEE Trans. Circuit Syst. II 2001, 48, 626–628. [Google Scholar] [CrossRef]

- Nemirovsky, Y.; Corcos, D.; Brouk, I.; Nemirovsky, A.; Chaudhry, S. 1/f Noise in advanced CMOS transistors. IEEE Instrum. Meas. Mag. 2011, 14, 14–22. [Google Scholar] [CrossRef]

| Technology (nm) | Device | Area (µm2) | Maximum Sensitivity (mV/K) | Accuracy (K) | (A2/Hz) | Calibration |

|---|---|---|---|---|---|---|

| 180 | Transistor | 2 | −1.2 | 3 | Not needed | |

| Diode | 3 | −2.1 | 6 | Needed | ||

| 130 | Transistor | 50 | −1 | 1 | Not needed | |

| Diode | 45 | −2 | 4 | Needed |

© 2017 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Malits, M.; Nemirovsky, Y. Nanometric Integrated Temperature and Thermal Sensors in CMOS-SOI Technology. Sensors 2017, 17, 1739. https://doi.org/10.3390/s17081739

Malits M, Nemirovsky Y. Nanometric Integrated Temperature and Thermal Sensors in CMOS-SOI Technology. Sensors. 2017; 17(8):1739. https://doi.org/10.3390/s17081739

Chicago/Turabian StyleMalits, Maria, and Yael Nemirovsky. 2017. "Nanometric Integrated Temperature and Thermal Sensors in CMOS-SOI Technology" Sensors 17, no. 8: 1739. https://doi.org/10.3390/s17081739