Key Processes of Silicon-On-Glass MEMS Fabrication Technology for Gyroscope Application

Abstract

:1. Introduction

2. Concept and Process Exploitation

2.1. CMP Process for Silicon

2.1.1. Details of the CMP Process

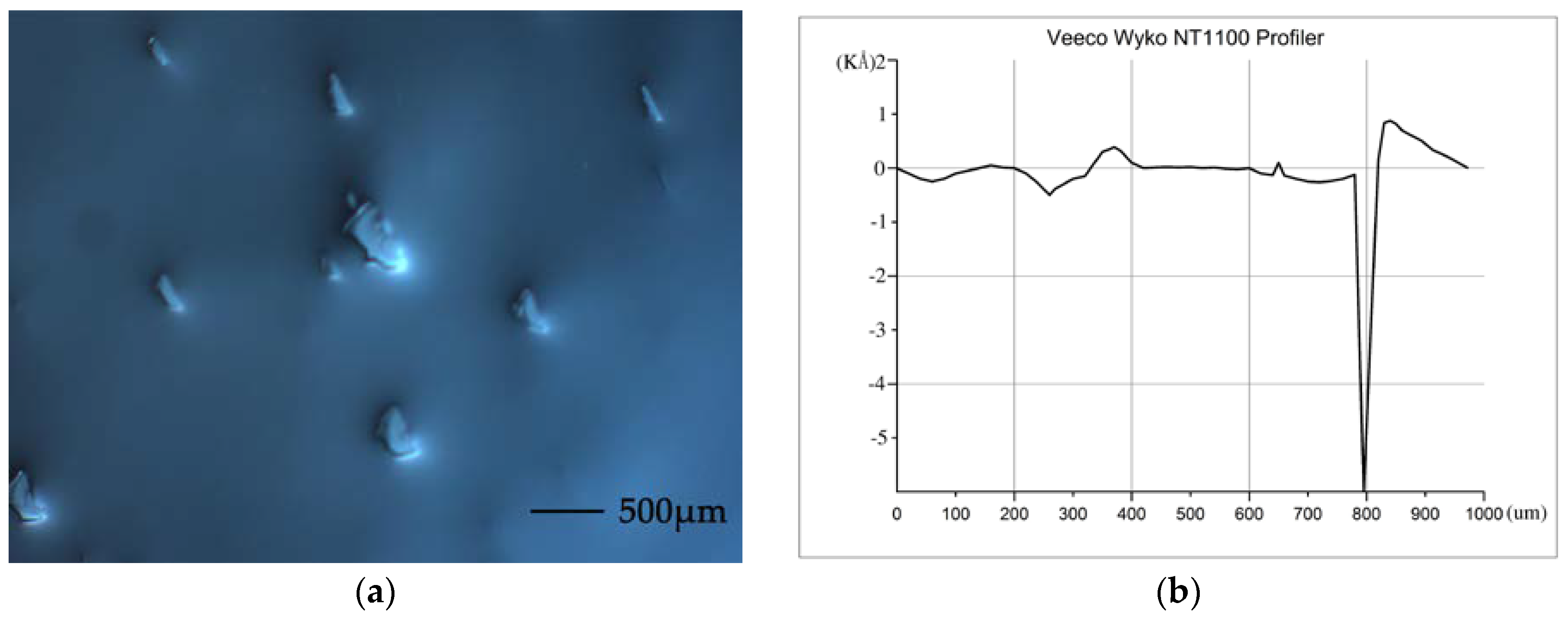

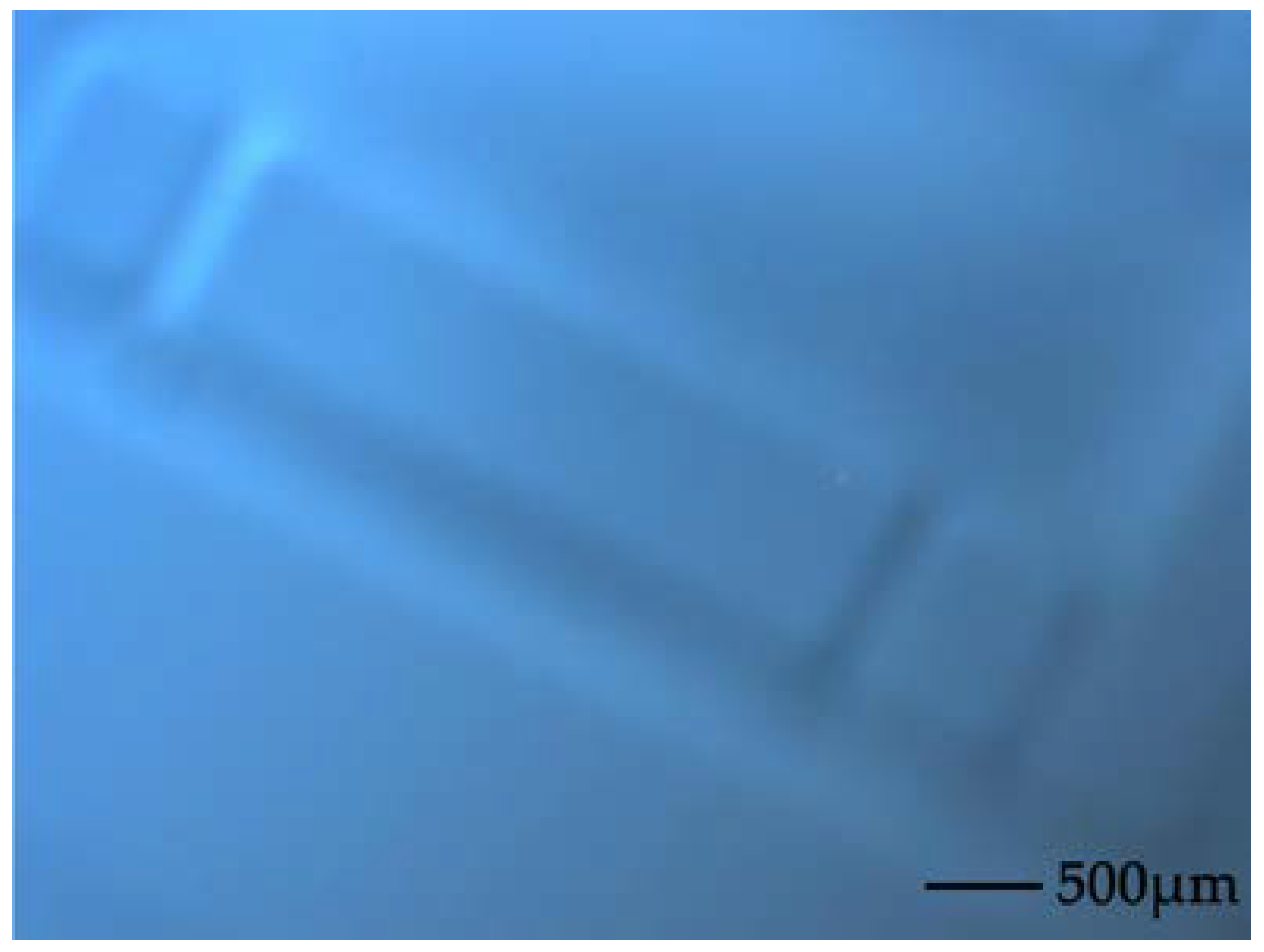

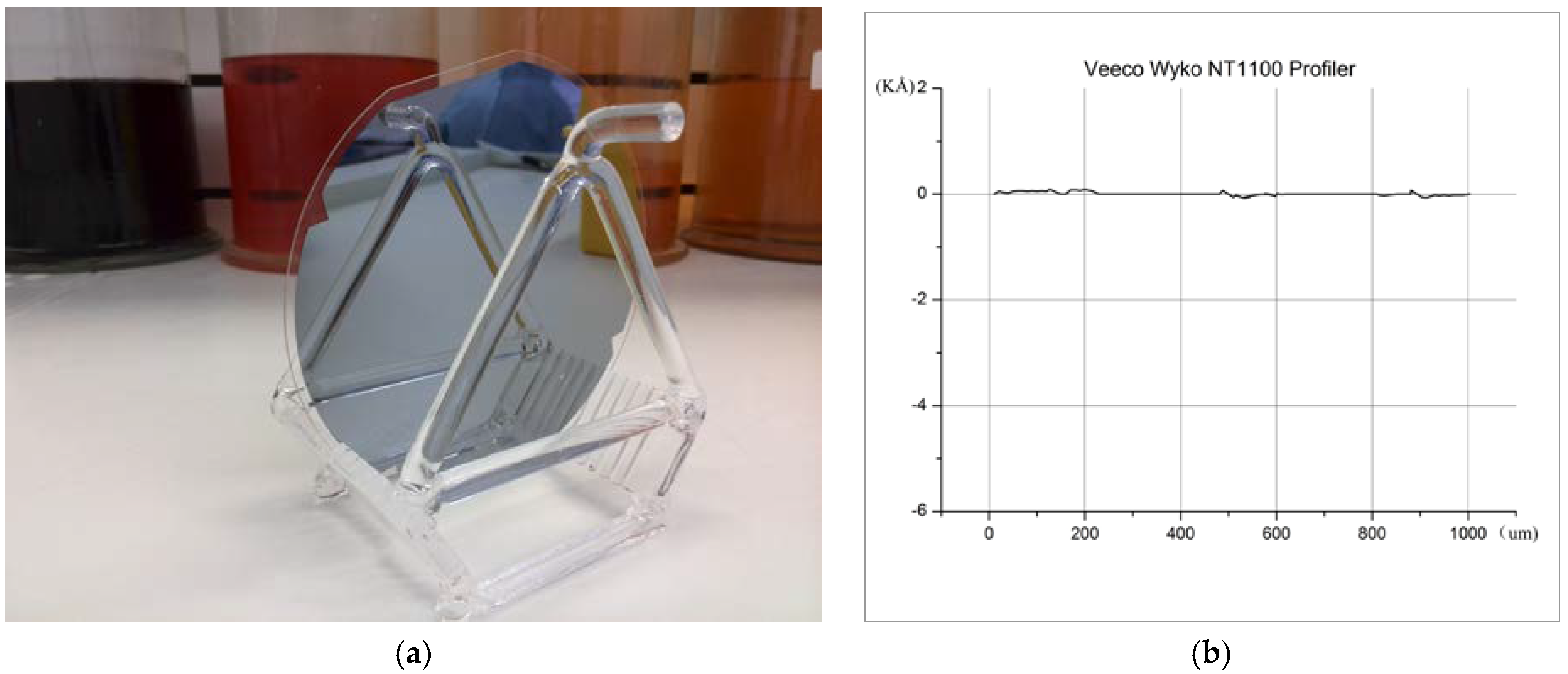

2.1.2. The Results of the CMP Process

2.2. DRIE Process for Silicon

2.2.1. Details of the DRIE Process

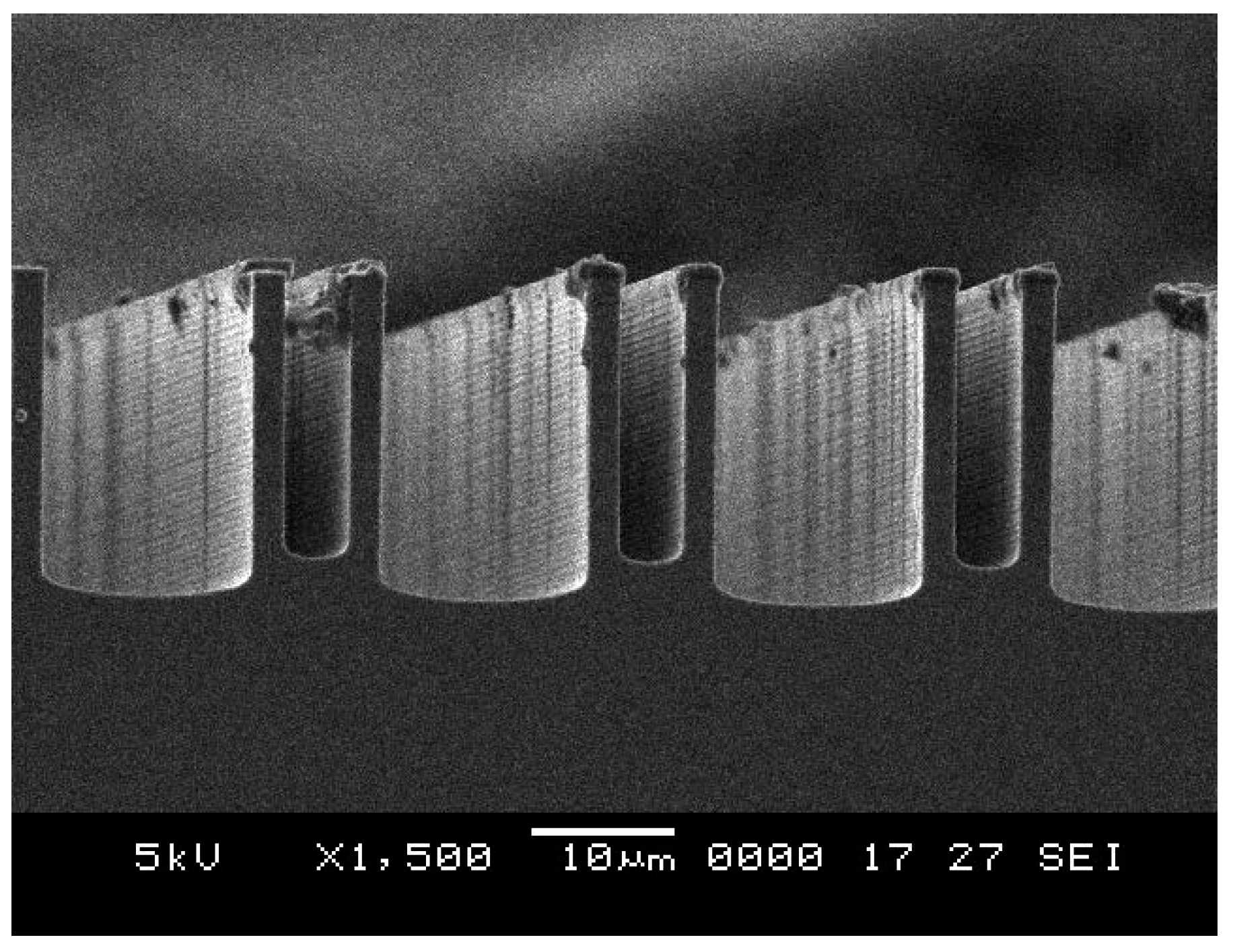

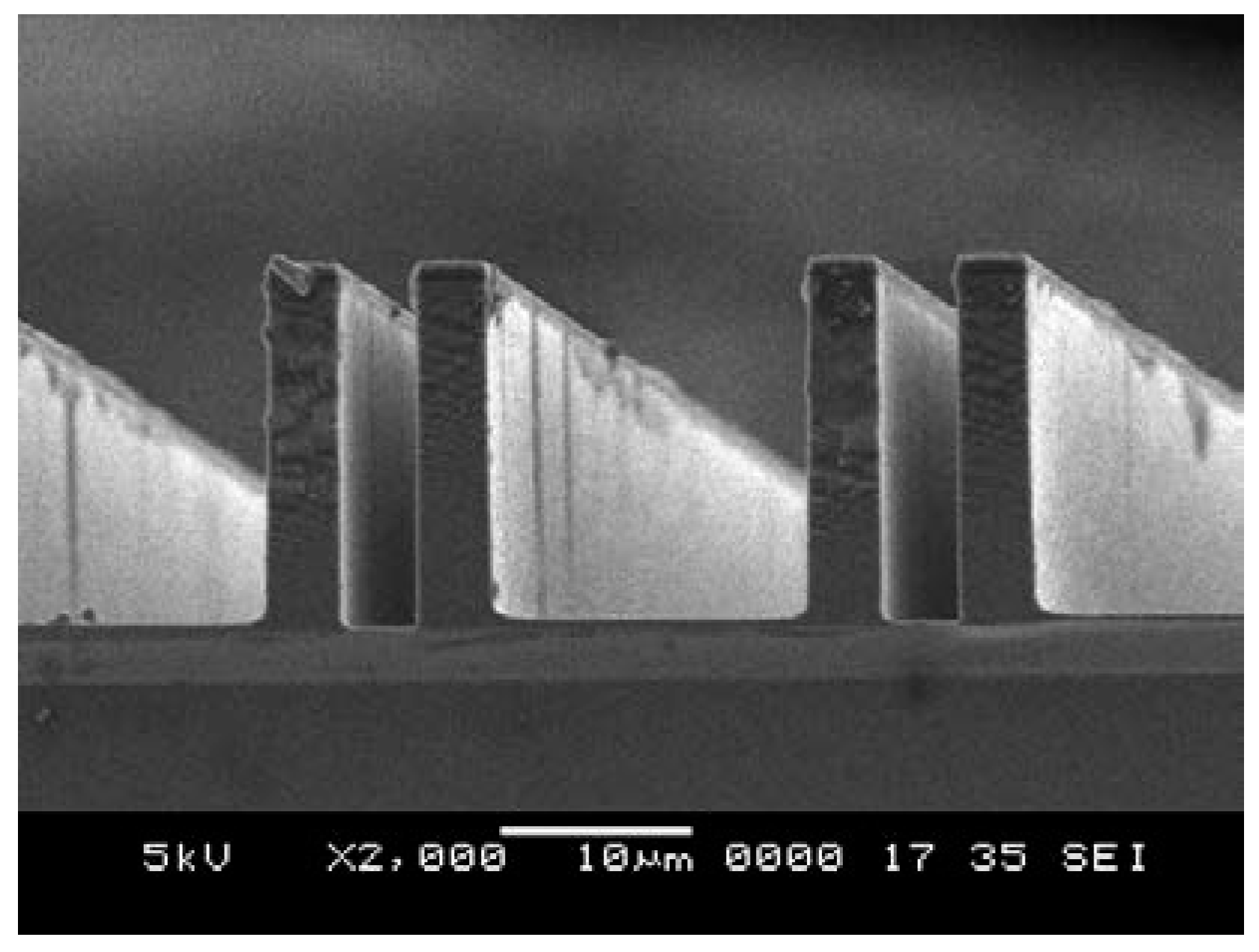

2.2.2. The Results of the DRIE Process

3. Applications

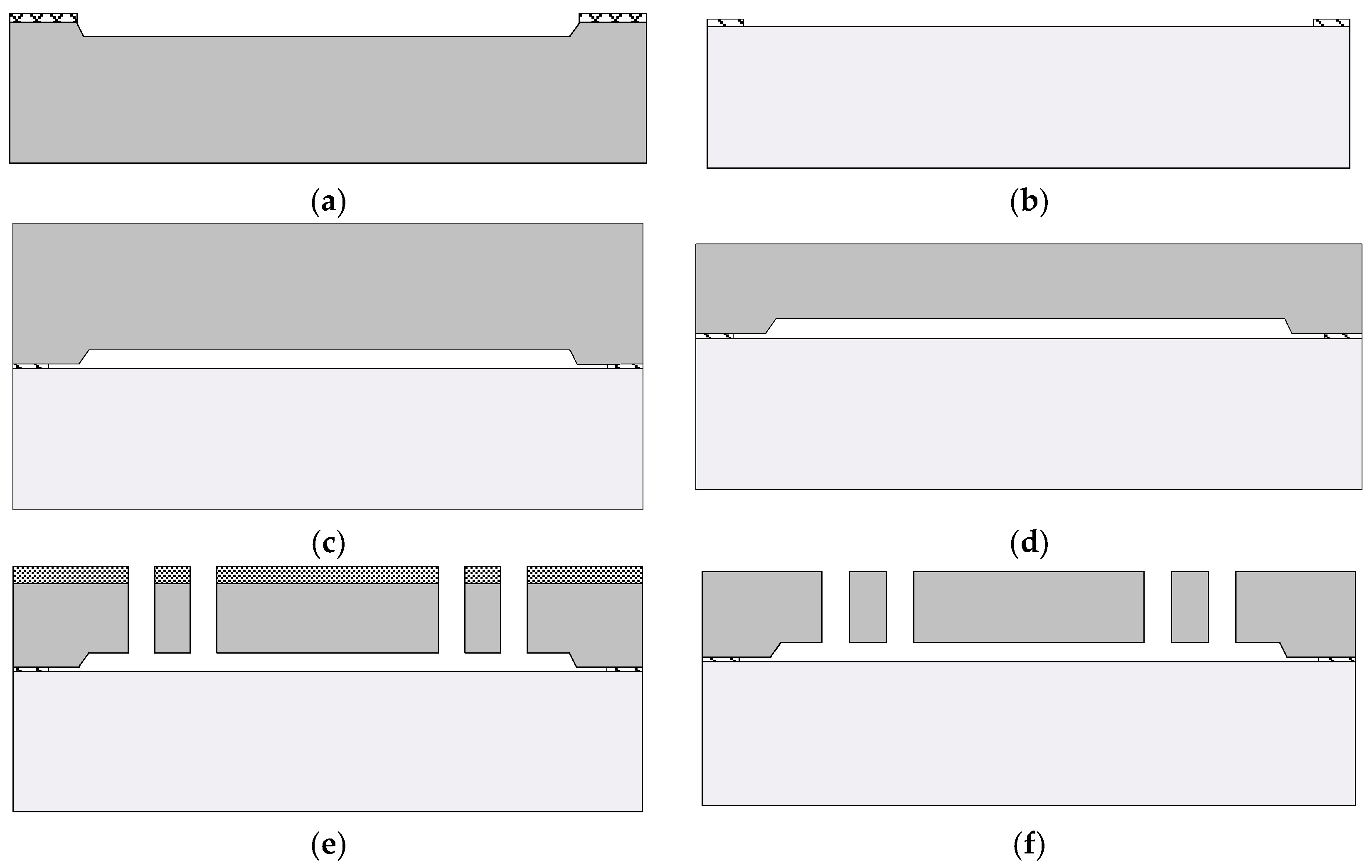

3.1. Fabrication of Micro Gyroscope

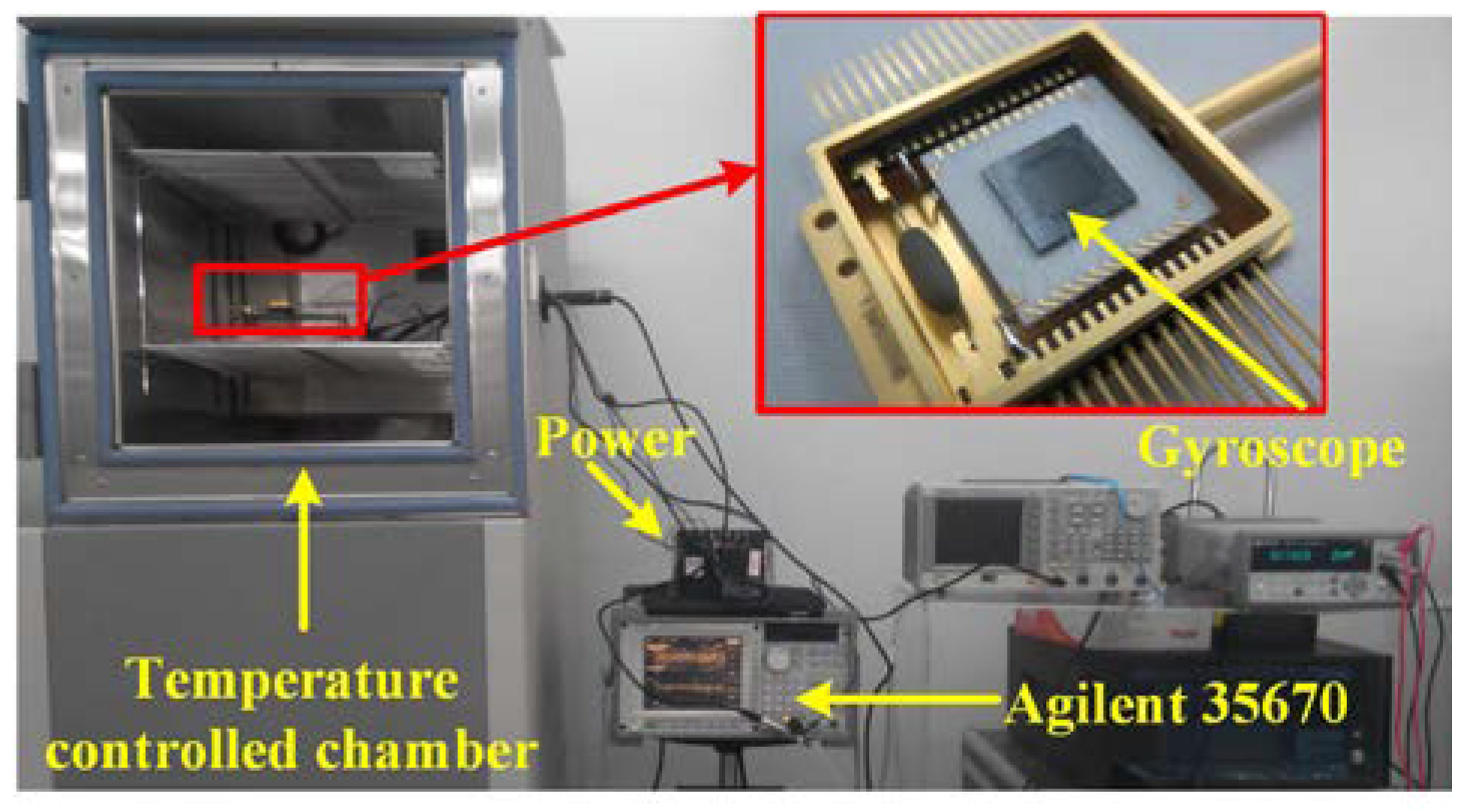

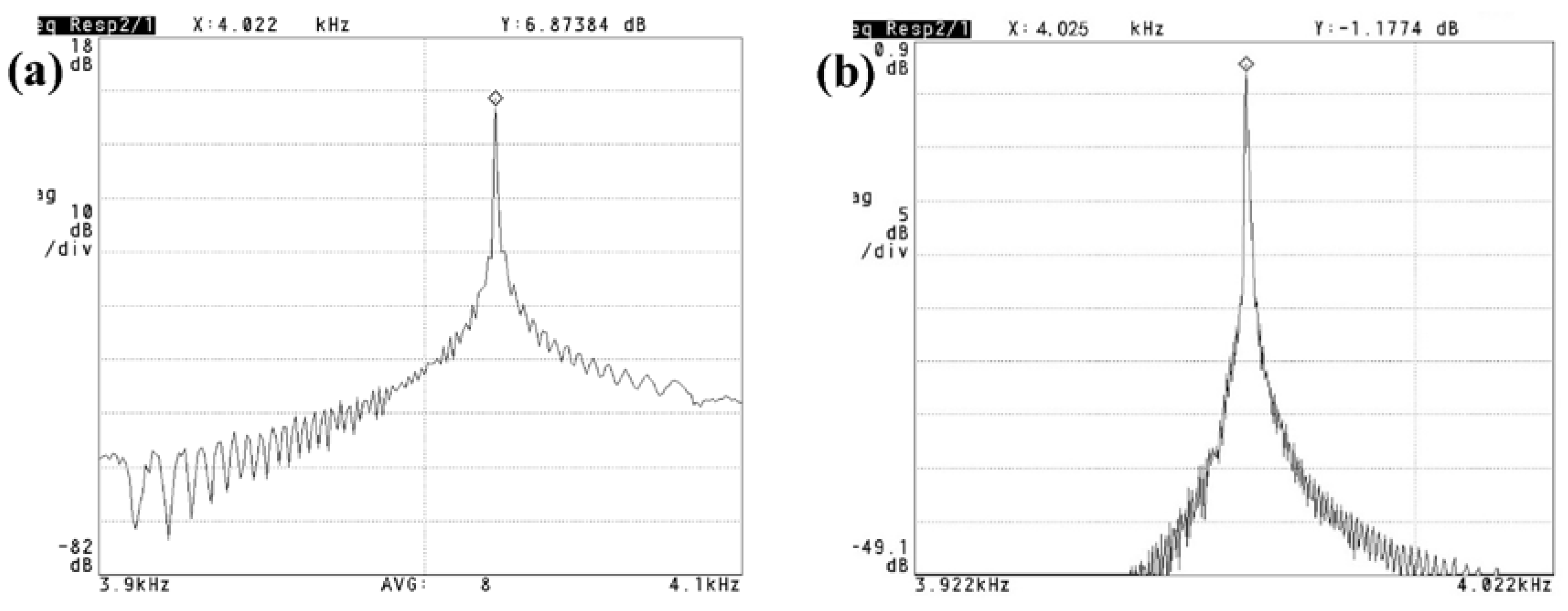

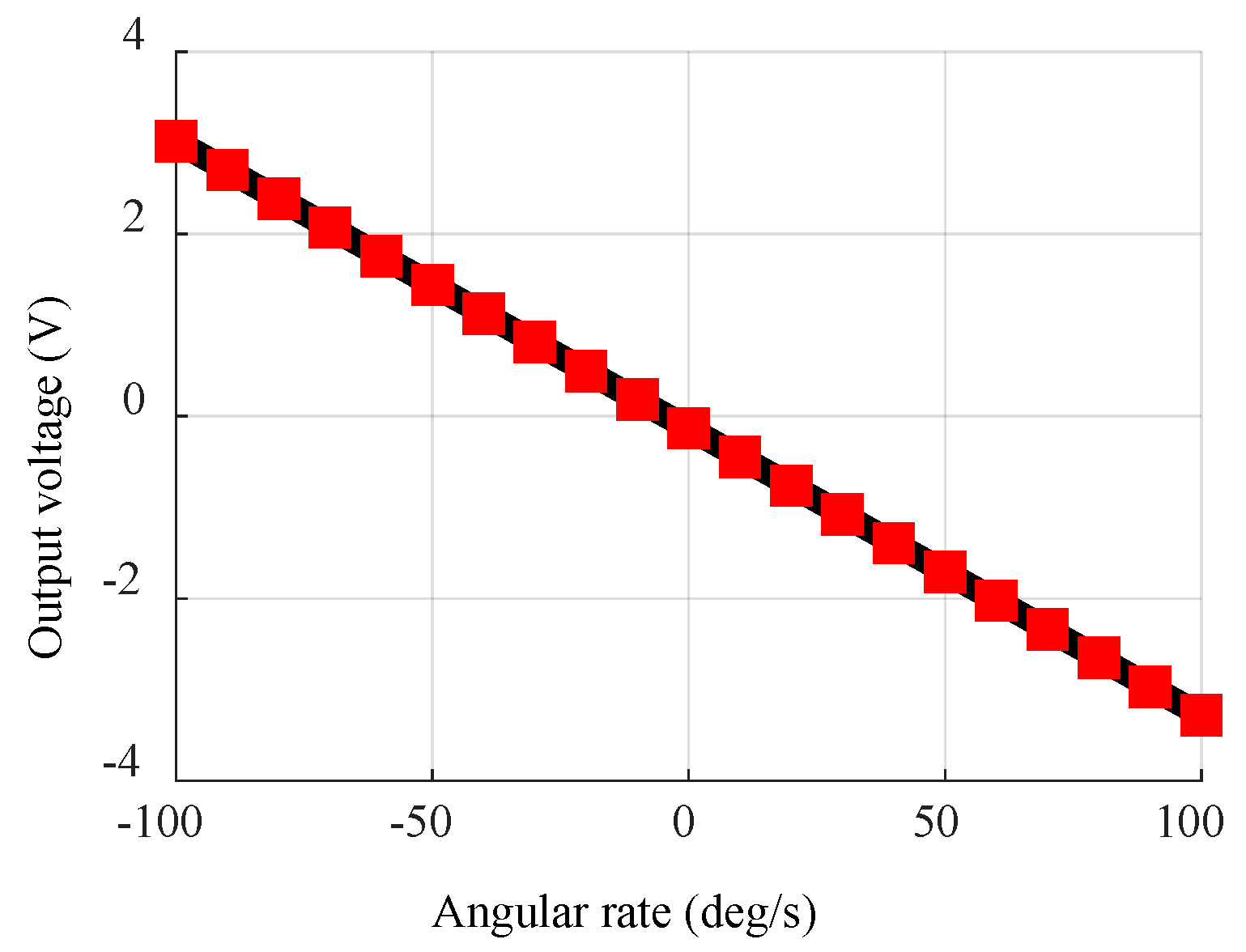

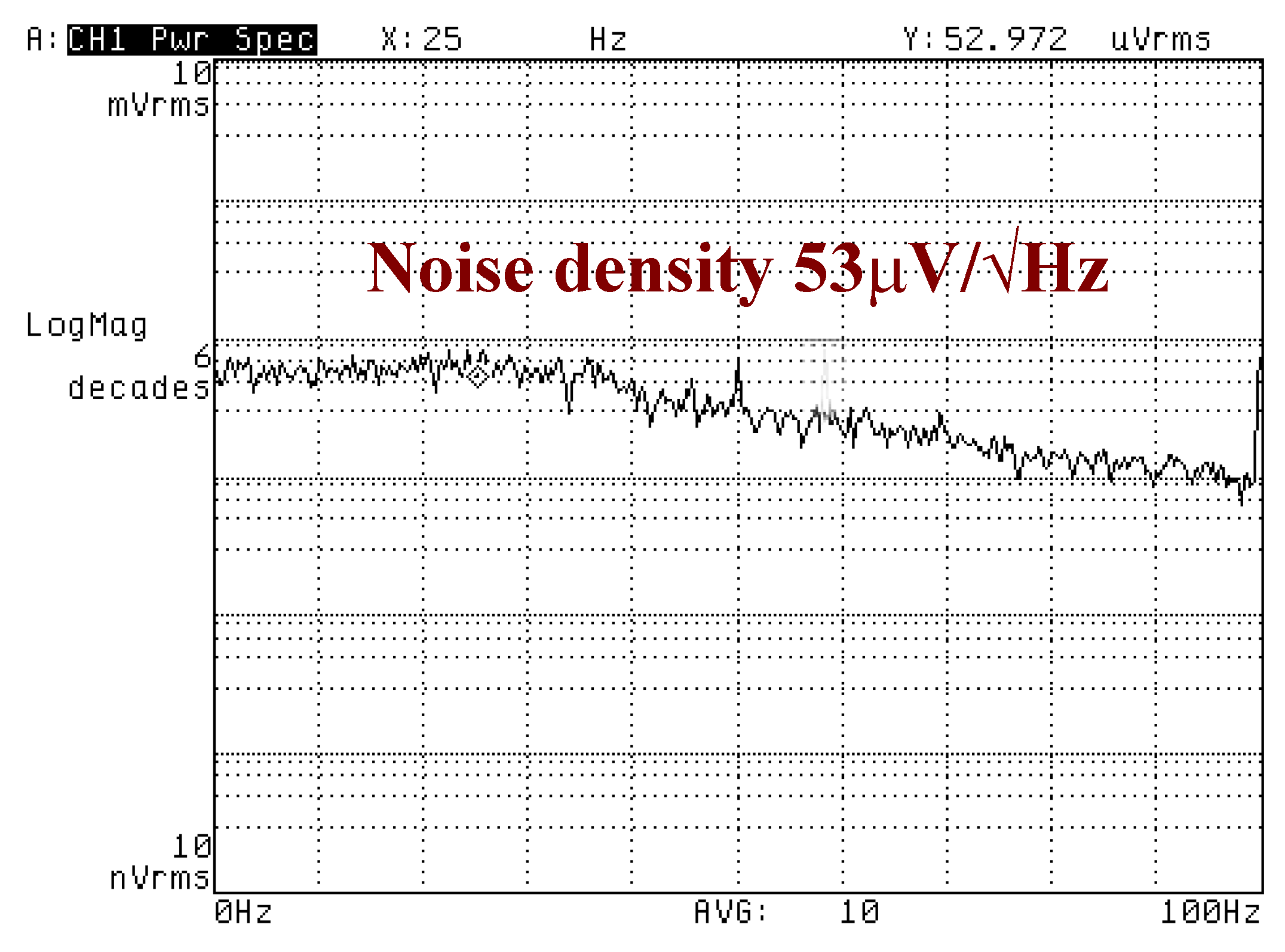

3.2. Test of the Fabricated Micro Gyroscope

4. Conclusions

Acknowledgments

Author Contributions

Conflicts of Interest

References

- Cui, F.; Liu, W.; Chen, W.; Zhang, W.; Wu, X. Design, fabrication and levitation experiments of a micromachined electrostatically suspended six-axis accelerometer. Sensors 2011, 12, 11206–11234. [Google Scholar] [CrossRef] [PubMed]

- Mansoor, M.; Haneef, I.; Akhtar, S.; Rafiq, M.A.; De Luca, A.; Ali, S.Z.; Udrea, F. An SOI CMOS-Based Multi-Sensor MEMS Chip for Fluidic Applications. Sensors 2016, 16, 1608. [Google Scholar] [CrossRef] [PubMed]

- Tez, S.; Aykutlu, U.; Torunbalci, M.M.; Akin, T. A bulk-micromachined three-axis capacitive MEMS accelerometer on a single die. J. Microelectromech. Syst. 2015, 24, 1264–1274. [Google Scholar] [CrossRef]

- Bagolini, A.; Ronchin, S.; Bellutti, P.; Chistè, M.; Verotti, M.; Belfiore, N.P. Fabrication of novel MEMS microgrippers by deep reactive ion etching with metal hard mask. J. Microelectromech. Syst. 2017, 26, 926–934. [Google Scholar] [CrossRef]

- Kim, K.H.; Kim, S.C.; Park, K.Y.; Yang, S.S. DRIE fabrication of notch-free silicon structures using a novel silicon-on-patterned metal and glass wafer. J. Micromech. Microeng. 2011, 21, 045018. [Google Scholar] [CrossRef]

- Balucani, M.; Belfiore, N.P.; Crescenzi, R.; Verotti, M. The development of a MEMS/NEMS-based 3 DOF compliant micro robot. In Proceedings of the 2010 IEEE 19th International Workshop on Robotics in Alpe-Adria-Danube Region (RAAD), Budapest, Hungary, 24–26 June 2010; pp. 173–179. [Google Scholar]

- Sampath, P.K.; Muhamad, B.S.K.; Ng, L.K.; Ranganathan, N. Development of multiple-step SOI DRIE process for superior notch reduction at buried oxide. Adv. Mater. Res. 2011, 254, 148–151. [Google Scholar] [CrossRef]

- Ding, H.T.; Yang, Z.C.; Yan, G.Z. A dual-purpose method to enhance heat transfer and prevent notching effect in deep reactive ion etching. Acta Electron. Sin. 2010, 38, 1201–1204. [Google Scholar]

- Merzsch, S.; Steib, F.; Wasisto, H.S.; Stranz, A.; Hinze, P.; Weimann, T.; Peiner, E.; Waag, A. Production of vertical nanowire resonators by cryogenic-ICP-DRIE. Microsyst. Technol. 2014, 20, 759–767. [Google Scholar] [CrossRef]

- Yu, J.-C.; Zhou, Z.-F.; Su, J.-L.; Xia, C.-F.; Zhang, X.-W.; Wu, Z.-Z.; Huang, Q.-A. Three-Dimensional Simulation of DRIE Process Based on the Narrow Band Level Set and Monte Carlo Method. Micromachines 2018, 9, 74. [Google Scholar] [CrossRef]

- Forsberg, M. Effect of process parameters on material removal rate in chemical mechanical polishing of Si (100). Microelectron. Eng. 2005, 77, 319–326. [Google Scholar] [CrossRef]

- Zhou, J.; Shen, Q.; Xie, J.B.; Cao, P.P.; Yuan, W.Z. Energy dissipation contribution modeling of vibratory behavior for silicon micromachined gyroscope. Shock Vib. 2018, in press. [Google Scholar]

- Ko, H.C.; Baca, A.J.; Rogers, J.A. Bulk quantities of single-crystal silicon micro-/nanoribbons generated from bulk wafers. Nano Lett. 2006, 6, 2318–2324. [Google Scholar] [CrossRef] [PubMed]

- Kim, C.H.; Kim, Y.K. Prevention method of a notching caused by surface charging in silicon reactive ion etching. J. Micromech. Microeng. 2004, 15, 358–361. [Google Scholar] [CrossRef]

- Tan, Y.; Zhou, R.; Zhang, H.; Lu, G.; Li, Z. Modeling and simulation of the lag effect in a deep reactive ion etching process. J. Micromech. Microeng. 2006, 16, 2570–2575. [Google Scholar] [CrossRef]

- Shen, Q.; Li, H.; Kang, H.; Yuan, W.Z.; Hang, H.L. Bias contribution modeling for a symmetrical micromachined Coriolis vibratory gyroscope. IEEE Sens. J. 2016, 16, 723–733. [Google Scholar] [CrossRef]

- Ding, H.; Liu, X.; Lin, L.; Chi, X.; Cui, J.; Kraft, M.; Yang, Z.; Yan, G. A High-Resolution Silicon-on-Glass Axis Gyroscope Operating at Atmospheric Pressure. IEEE Sens. J. 2010, 10, 1066–1074. [Google Scholar] [CrossRef]

- Yang, J.C.; Oh, D.W.; Lee, G.W.; Song, C.L.; Kim, T. Step height removal mechanism of chemical mechanical planarization (CMP) for sub-nano-surface finish. Wear 2010, 268, 505–510. [Google Scholar] [CrossRef]

- Alper, S.E.; Temiz, Y.; Akin, T. A compact angular rate sensor system using a fully decoupled silicon-on-glass MEMS gyroscope. J. Microelectromech. Syst. 2008, 17, 1418–1429. [Google Scholar] [CrossRef]

- Sonmezoglu, S.; Alper, S.E.; Akin, T. An automatically mode-matched MEMS gyroscope with wide and tunable bandwidth. J. Microelectromech. Syst. 2014, 23, 284–297. [Google Scholar] [CrossRef]

- Ma, Z.; Jiang, C.; Yuan, W. A triple-layer protection process for high-aspect-ratio silicon micromachining by DRIE of SOI substrates. J. Micromech. Microeng. 2012, 22, 055028. [Google Scholar] [CrossRef]

- Cao, H.; Li, H.; Kou, Z.; Shi, Y.; Tang, J.; Ma, Z.; Shen, C.; Liu, J. Optimization and experimentation of dual-mass MEMS gyroscope quadrature error correction methods. Sensors 2016, 16, 71. [Google Scholar] [CrossRef] [PubMed]

- Dixit, P.; Miao, J. Effect of SF6 flow rate on the etched surface profile and bottom grass formation in deep reactive ion etching process. J. Phys. Conf. Ser. 2006, 34, 577. [Google Scholar] [CrossRef]

| Process | Powder | Thickness of the Silicon [μm] | Ra [nm] | ||||

|---|---|---|---|---|---|---|---|

| Center | Primary | Secondary | Left | Right | Average | ||

| Lapping | 20 μm Al2O3 | 256 | 254 | 251 | 253 | 254 | 85.04 |

| 9 μm Al2O3 | 204 | 204 | 204 | 204 | 203 | 79.29 | |

| Polishing | 3 μm cerium oxide | 202 | 203 | 203 | 202 | 203 | 8.19 |

| SF1 | 201 | 200 | 201 | 201 | 201 | 1.13 | |

| Recipe | Etching/Passivation (s) | Pressure (mTorr) | Average Etching Rate (μm/min) |

|---|---|---|---|

| a | 6/5 | 43 | 4.67 |

| b | 8/10 | 35 | 3.23 |

| c | 8/10 | 30 | 2.56 |

| Etch | Passivate | ||

|---|---|---|---|

| SF6 flow rate (sccm) | 180 | C4F8 flow rate (sccm) | 120 |

| O2 flow rate (sccm) | 20 | ||

| Coil power (w) | 800 | Coil power (w) | 800 |

| Platen power (w) | 20 | Platen power (w) | 0 |

| Cycle time (s) | 8 | Cycle time (s) | 10 |

| Pressure (mTorr) | 30 | ||

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Ma, Z.; Wang, Y.; Shen, Q.; Zhang, H.; Guo, X. Key Processes of Silicon-On-Glass MEMS Fabrication Technology for Gyroscope Application. Sensors 2018, 18, 1240. https://doi.org/10.3390/s18041240

Ma Z, Wang Y, Shen Q, Zhang H, Guo X. Key Processes of Silicon-On-Glass MEMS Fabrication Technology for Gyroscope Application. Sensors. 2018; 18(4):1240. https://doi.org/10.3390/s18041240

Chicago/Turabian StyleMa, Zhibo, Yinan Wang, Qiang Shen, Han Zhang, and Xuetao Guo. 2018. "Key Processes of Silicon-On-Glass MEMS Fabrication Technology for Gyroscope Application" Sensors 18, no. 4: 1240. https://doi.org/10.3390/s18041240