Design and Fabrication Technology of Low Profile Tactile Sensor with Digital Interface for Whole Body Robot Skin

Abstract

:1. Introduction

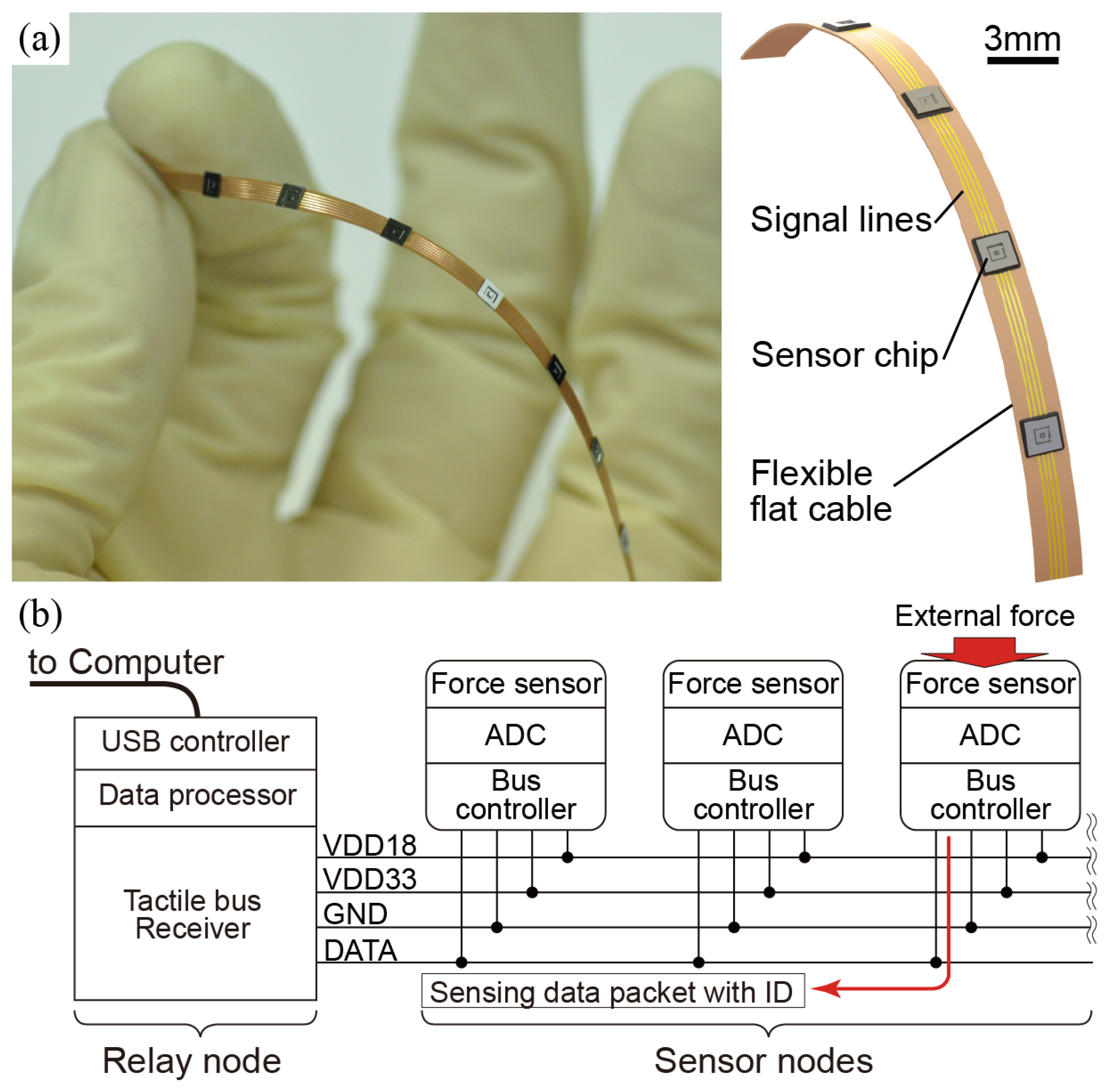

2. Design of Tactile Sensor

2.1. Package and Device Structure

2.2. Quasi Linear Force Transducer

2.3. Overview of the ASIC

3. Fabrication Process

3.1. Through Silicon Groove (TSG) Technology

3.2. Polymer Processing and Wafer Bonding

3.3. Detail of the Fabrication Process

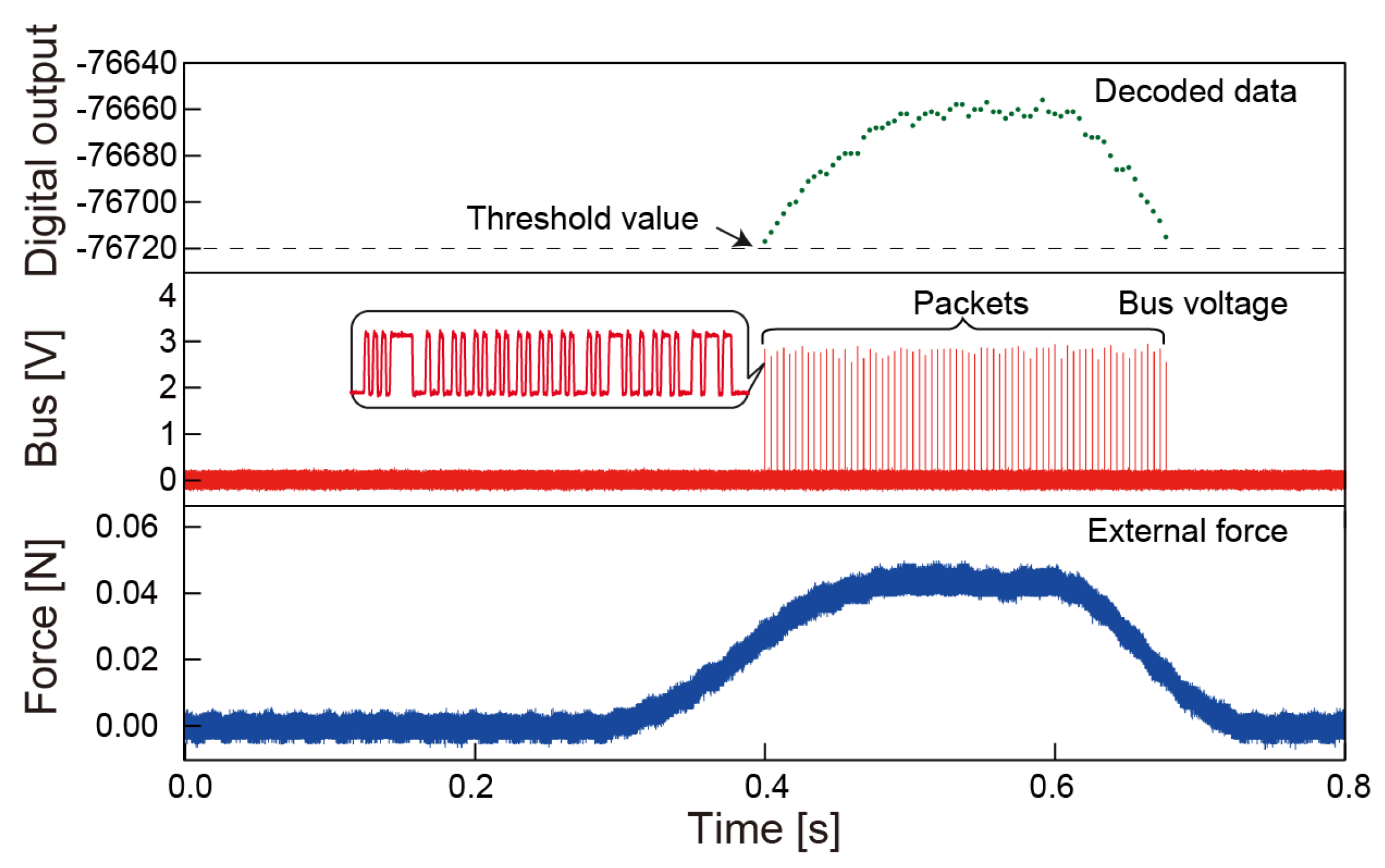

4. Evaluation of a Tactile Sensor

5. Conclusions

Author Contributions

Acknowledgments

Conflicts of Interest

References

- Lee, M.H.; Nicholls, H.R. Review Article Tactile sensing for mechatronics—A state of the art survey. Mechatronics 1999, 9, 1–31. [Google Scholar] [CrossRef]

- Yousef, H.; Boukallel, M.; Althoefer, K. Tactile sensing for dexterous in-hand manipulation in robotics—A review. Sens. Actuators A Phys. 2011, 167, 171–187. [Google Scholar] [CrossRef]

- Asano, S.; Muroyama, M.; Bartley, T.; Nakayama, T.; Yamaguchi, U.; Yamada, H.; Hata, Y.; Nonomura, Y.; Tanaka, S. 3-Axis fully-integrated surface-mountable differential capacitive tactile sensor by CMOS flip-bonding. In Proceedings of the IEEE 29th International Conference on Micro Electro Mechanical Systems, Shanghai, China, 24–28 January 2016; pp. 850–853. [Google Scholar]

- Suzuki, Y.; Fukushi, H.; Muroyama, M.; Hata, Y.; Nakayama, T.; Chand, R.; Hirano, H.; Nonomura, Y.; Funabashi, H.; Tanaka, S. 300 μm Deep through silicon via in laser-ablated CMOS multi-project wafer for cost-effective development of integrated MEMS. In Proceedings of the IEEE 30th International Conference on Micro Electro Mechanical Systems, Las Vegas, NV, USA, 22–26 January 2017; pp. 744–748. [Google Scholar] [CrossRef]

- Hata, Y.; Suzuki, Y.; Muroyama, M.; Nakayama, T.; Nonomura, Y.; Chand, R.; Hirano, H.; Omura, Y.; Fujiyoshi, M.; Tanaka, S. Fully-integrated, fully-differential 3-axis tactile sensor on platform LSI with TSV-based surface-mountable structure. In Proceedings of the Transducers 2017, Kaohsiung, Taiwan, 18–22 June 2017; pp. 500–503. [Google Scholar] [CrossRef]

- Makihata, M.; Tanaka, S.; Muroyama, M.; Matsuzaki, S.; Yamada, H.; Nakayama, T.; Yamaguchi, U.; Mima, K.; Nonomura, Y.; Fujiyoshi, M.; et al. Integration and packaging technology of MEMS-on-CMOS capacitive tactile sensor for robot application using thick BCB isolation layer and backside-grooved electrical connection. Sens. Actuators A Phys. 2012, 188, 103–110. [Google Scholar] [CrossRef]

- Esashi, M.; Tanaka, S. Stacked Integration of MEMS on LSI. Micromachines 2016, 7, 137. [Google Scholar] [CrossRef]

- Bryzek, J.; Flannery, A.; Skurnik, D. Integrating microelectromechanical systems with integrated circuits. IEEE Instrum. Meas. Mag. 2014, 7, 51–59. [Google Scholar] [CrossRef]

- Fischer, A.C.; Forsberg, F.; Lapisa, M.; Bleiker, S.J.; Stemme, G.; Roxhed, N.; Niklaus, F. Integrating MEMS and ICs. Microsyst. Nanoeng. 2015, 1, 1–16. [Google Scholar] [CrossRef]

- Jourdain, A.; Moor, P.D.; Baert, K.; Wolf, I.D.; Tilmans, H.A.C. Mechanical and electrical characterization of BCB as a bond and seal material for cavities housing (RF-) MEMS devices. J. Micromech. Microeng. 2005, 15, 89–96. [Google Scholar] [CrossRef]

- Töpper, M.; Fischer, T.; Baumgartner, T.; Reichl, H. A comparison of thin film polymers for wafer level packaging. In Proceedings of the 60th Electronic Components and Technology Conference (ECTC), Las Vegas, NV, USA, 1–4 June 2010; pp. 769–776. [Google Scholar] [CrossRef]

- Muroyama, M.; Makihata, M.; Tanaka, S.; Kojima, T.; Nakayama, T.; Yamaguchi, U.; Yamada, H.; Nonomura, Y.; Funabashi, H.; Hata, Y.; et al. Tactile Sensor Network System with CMOS-MEMS Integration for Social Robot Applications. In Proceedings of the Smart Systems Integration International Conference and Exhibition, Vienna, Austria, 26–27 March 2014; pp. 181–188. [Google Scholar]

- Makihata, M.; Muroyama, M.; Nakano, Y.; Tanaka, S.; Nakayama, T.; Yamaguchi, U.; Yamada, H.; Nonomura, Y.; Funabashi, H.; Hata, Y.; et al. A 1.7 mm3 MEMS-on-CMOS tactile sensor using human-inspired autonomous common bus communication. In Proceedings of the 17th International Conference on Solid-State Sensors, Actuators and Microsystems (TRANSDUCERS EUROSENSORS XXVII), Barcelona, Spain, 16–20 June 2013; pp. 2729–2732. [Google Scholar] [CrossRef]

- Motoyoshi, M. Through-silicon via (TSV). Proceed. IEEE 2009, 97, 43–48. [Google Scholar] [CrossRef]

- Hirano, H.; Rasly, M.; Kaushik, N.; Esashi, M.; Tanaka, S. Particle Removal without Causing Damage to MEMS Structure. IEEJ Trans. Sens. Micromach. 2013, 133, 157–163. [Google Scholar] [CrossRef]

- Niklaus, F.; Kumar, R.J.; McMahon, J.J.; Yu, J.; Lu, J.-Q.; Cale, T.S.; Gutmann, R.J. Adhesive wafer bonding using partially cured benzocyclobutene for three-dimensional integration. J. Electrochem. Soc. 2006, 153, G291–G295. [Google Scholar] [CrossRef]

- Oberhammer, J.; Niklaus, F.; Stemme, G. Selective wafer-level adhesive bonding with benzocyclobutene for fabrication of cavities. Sens. Actuators A Phys. 2003, 105, 297–304. [Google Scholar] [CrossRef]

- Makihata, M.; Tanaka, S.; Muroyama, M.; Matsuzaki, S.; Yamada, H.; Nakayama, T.; Yamaguchi, U.; Mima, K.; Nonomura, Y.; Fujiyoshi, M.; et al. Adhesive wafer bonding using a molded thick benzocyclobutene layer for wafer-level integration of MEMS and LSI. J. Micromech. Microeng. 2011, 21, 85002–85008. [Google Scholar] [CrossRef]

- Pal, P.; Sato, K.; Gosalvez, M.A.; Shikida, M. Study of rounded concave and sharp edge convex corners undercutting in CMOS compatible anisotropic etchants. J. Micromech. Microeng. 2007, 17, 2299–2307. [Google Scholar] [CrossRef]

| Process | Process Details | |

|---|---|---|

| Spin coating | CYCLOYENE3000-63 3000 rpm × 2 time | |

| BCB Coating | Soft Baking | Hotplate 130 C for 5 min |

| Half-curing | 220 C for 1 h in N environment | |

| Polishing | Slurry | Water 800 mL + 4g + Triton X-100 2 mL |

| Pressure | 25 kPa | |

| Rotation speed | 20 rpm | |

| Polishing pad | UltraPol (Buehler, Lake Bluff, IL, USA) | |

| Conditioning of polishing pad | 6 h with dummy sample with BCB | |

| Polishing rate | 0.75 m/min | |

| Cleaning | Water polishing | 10 min |

| Wax removal | Ethanol soaking up to 5 min | |

| TSV with Deep RIE [4,5] | LTCC Interposer [3] | This Work | |

|---|---|---|---|

| Demonstrated TSV | 4/5 | 10 | 20 |

| Device thickness | 650 m | 660 m | 300 m |

| Bonding method | Au-Au bonding | Au-Au bonding | BCB bonding |

| Parasitic capacitance | not reported | 3.2 pF | 1.33 pF |

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Makihata, M.; Muroyama, M.; Tanaka, S.; Nakayama, T.; Nonomura, Y.; Esashi, M. Design and Fabrication Technology of Low Profile Tactile Sensor with Digital Interface for Whole Body Robot Skin. Sensors 2018, 18, 2374. https://doi.org/10.3390/s18072374

Makihata M, Muroyama M, Tanaka S, Nakayama T, Nonomura Y, Esashi M. Design and Fabrication Technology of Low Profile Tactile Sensor with Digital Interface for Whole Body Robot Skin. Sensors. 2018; 18(7):2374. https://doi.org/10.3390/s18072374

Chicago/Turabian StyleMakihata, Mitsutoshi, Masanori Muroyama, Shuji Tanaka, Takahiro Nakayama, Yutaka Nonomura, and Masayoshi Esashi. 2018. "Design and Fabrication Technology of Low Profile Tactile Sensor with Digital Interface for Whole Body Robot Skin" Sensors 18, no. 7: 2374. https://doi.org/10.3390/s18072374