Article

# Design and Fabrication of CMOS Microstructures to Locally Synthesize Carbon Nanotubes for Gas Sensing

Avisek Roy <sup>1,\*</sup>, Mehdi Azadmehr <sup>1</sup>, Bao Q. Ta <sup>1</sup>, Philipp Häfliger <sup>2</sup> and Knut E. Aasmundtveit <sup>1</sup>

- Department of Microsystems, University of South-Eastern Norway, 3184 Borre, Norway; Mehdi.Azadmehr@usn.no (M.A.); Bao.Ta@usn.no (B.Q.T.); Knut.Aasmundtveit@usn.no (K.E.A.)

- Department of Informatics, University of Oslo, 0373 Oslo, Norway; hafliger@ifi.uio.no

- \* Correspondence: Avisek.Roy@usn.no

Received: 15 August 2019; Accepted: 6 October 2019; Published: 8 October 2019

**Abstract:** Carbon nanotubes (CNTs) can be grown locally on custom-designed CMOS microstructures to use them as a sensing material for manufacturing low-cost gas sensors, where CMOS readout circuits are directly integrated. Such a local CNT synthesis process using thermal chemical vapor deposition (CVD) requires temperatures near 900 °C, which is destructive for CMOS circuits. Therefore, it is necessary to ensure a high thermal gradient around the CNT growth structures to maintain CMOS-compatible temperature (below 300 °C) on the bulk part of the chip, where readout circuits are placed. This paper presents several promising designs of CNT growth microstructures and their thermomechanical analyses (by ANSYS Multiphysics software) to check the feasibility of local CNT synthesis in CMOS. Standard CMOS processes have several conductive interconnecting metal and polysilicon layers, both being suitable to serve as microheaters for local resistive heating to achieve the CNT growth temperature. Most of these microheaters need to be partially or fully suspended to produce the required thermal isolation for CMOS compatibility. Necessary CMOS post-processing steps to realize CNT growth structures are discussed. Layout designs of the microstructures, along with some of the microstructures fabricated in a standard AMS 350 nm CMOS process, are also presented in this paper.

**Keywords:** carbon nanotube; local CNT synthesis; CMOS–CNT integration; microstructures; microheater; CMOS-compatible temperature

## 1. Introduction

Nanomaterials are a popular research topic as sensing materials for various sensing applications [1–3], including gas detection [4–8], due to their compact size [9], high sensitivity [10], low operating temperatures [11], low power consumption [12], etc. Among different nanomaterials, carbon nanotubes (CNTs) offer a very high surface-to-volume ratio [13], as well as exceptional material properties, including mechanical strength [14], metallic or semiconducting electrical conductivity [15], and high thermal conductivity [16] that facilitates CNTs in diverse applications [17–21]. Electrical properties of CNTs are easily influenced during interaction with different gas molecules [10], making these carbon-based nanomaterials an excellent candidate for ultra-sensitive gas sensing. Moreover, functional materials such as Pd and Pt can be deposited on CNTs [22] to enhance their sensitivity and selectivity to various gases, such as NO<sub>2</sub>, NH<sub>3</sub>, CO and O<sub>2</sub> [23,24]. A CNT-based gas sensor can have small form factor, while it can sense gases even at low concentration exposure at room temperature. Such a sensor is beneficial to numerous applications, including in the food-packaging industry, where the freshness of the food can be monitored by sensing released gases due to food degradation.

Sensors **2019**, 19, 4340 2 of 22

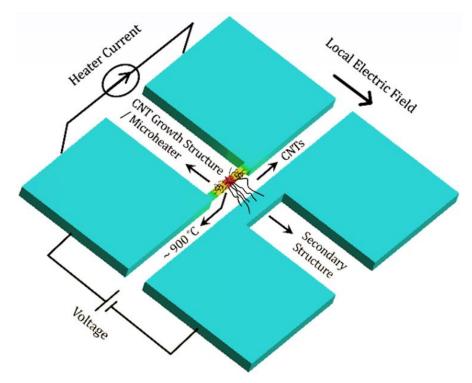

To utilize the functionalities of CNTs in smart gas-sensing applications, high-quality, low-noise CMOS front-end circuits are required for signal conversion and processing. A compact gas sensor containing CNTs as sensing material and CMOS readout circuits needs a standard process for direct CNT–CMOS integration. CNTs were already directly synthesized on MEMS structures, as demonstrated by Englander et al. [25], back in 2003. A similar approach can be used to grow CNTs on CMOS structures [26]. Figure 1 illustrates the process of local CNT synthesis on microstructures. The CNT growth structure (microheater) is locally heated by joule heating to generate temperatures in the region of 900 °C. A pre-deposited thin catalyst layer (iron in our process) on the microheater breaks into nanoparticles at such high temperatures, while a carbon-containing precursor gas enters the chemical vapor deposition (CVD) chamber. CNTs start to grow on the microheater when the precursor gas interacts with the catalyst nanoparticles. An electric field set between the CNT growth structure and another neighboring microstructure guides the growing CNTs toward that nearby secondary microstructure. A circuit containing CNTs as variable resistor is formed once the CNTs land on the secondary microstructure. Such a system can potentially work as a gas sensor, since the change in CNT electrical properties can be monitored upon exposure to certain gases.

Figure 1. Concept illustration of local carbon nanotubes (CNT) synthesis on microstructures.

CNT–MEMS integration acts as a model system for CNT–CMOS integration. CMOS and MEMS technologies have clear similarities, but demonstration of direct CNT integration in CMOS involves a more complex process than in MEMS. Alternatively, CMOS chips can be assembled with CNT–MEMS to demonstrate the ultimate goal of a single chip with sensing and signal-processing capability. However, MEMS–CMOS assembly adds cost and processing steps, which are not compatible with low-cost mass production.

The main challenge for directly growing CNTs in CMOS chips is the high contrast in temperature, since CNT synthesis using our localized CVD process needs around 900 °C, whereas CMOS circuits are at risk to be degraded at temperatures above 300–400 °C [27–29]. Therefore, it is important to grow the CNTs locally and keep the CNT growth microstructures thermally isolated. In MEMS, CNTs are directly synthesized on a suspended microstructure by local resistive heating during the CVD process [25,30,31]. However, industrial CMOS fabrication platforms do not allow fabricating

Sensors **2019**, 19, 4340 3 of 22

suspended structures. For full or partial suspension of any CMOS microstructures, post-processing steps need to be introduced on the CMOS chips.

CNTs can also be synthesized separately at a high temperature and then transferred to the microsystem for integration. Since the CNTs are grown separately, the high temperature requirement for the growth along with other post-growth processes, such as purification or chemical modification, does not have any restrictions in this technique. Among post-growth CNT integration schemes, liquid deposition methods, including dielectrophoresis (DEP) [32] and dip coating [33], are well-known. In general, liquid suspension techniques lack good bonding between the substrate and the nanostructures, and there are possibilities of contamination and sacrificing electrical properties during the protracted process steps [34]. They also often suffer from issues related to non-uniform CNT assembly and misalignment [32,35]. Therefore, it is challenging to realize a reliable and repeatable technique of transferring and assembling CNTs to the microsystem.

In a recent work, Hills et al. [36] proposed a manufacturing methodology for CNTs which combines processing and circuit design techniques to overcome the major challenges related to liquid deposition methods for CNT integration in CMOS. However, the complex nature of this work on CNFET-based digital circuits requires defining a dedicated CMOS fabrication process involving materials such as Pt, Ti for metal layers and SiO<sub>x</sub>, HfO<sub>x</sub> for PMOS and NMOS passivation layers [36], which are not common is standard CMOS processes. In the case of the DEP process, it provides better alignment and uniformity, but usually has low throughput and requires additional complex metallization steps to achieve better electrical contact between the nanotubes and the electrodes [37]. Seichepine et al. [32] developed CNT integration in CMOS by DEP method with high yield, where 80% of the electrode pairs in the 1024 array of devices only have 1–5 CNT connections per electrode pair; however, these CMOS chips still required extensive metallization post-processing [38]. Local CNT synthesis ensures CNTs with excellent structural quality, but the CMOS-compatible temperature is the main restriction in this integration process [32], and that is what we aim to solve in our approach of CMOS–CNT integration.

The CNT growth structures in CMOS can be fabricated using the polysilicon and metal interconnecting layers. Aluminum (Al) and copper (Cu) are commonly used for metallization in standard CMOS technology [39,40]. These metals, however, are not suitable to serve as microheaters (CNT growth structures) in their original form due to low electrical resistivity and high thermal conductivity. Moreover, aluminum melts at around 660 °C, which is far less than the required 900 °C CNT synthesis temperature. Therefore, we have investigated different binary alloys containing Al or Cu that have material properties suitable for our application. Nickel (Ni) turned out to be the most suitable alloying material for both Al and Cu.

We designed several microstructures suitable for CNT synthesis, using the compatible materials (polysilicon, Al–Ni, and Cu–Ni alloys) in CMOS and performed thermomechanical analyses with the Multiphysics simulation software, ANSYS. Most of these designs involve partially suspended microstructures to balance mechanical stability and high thermal isolation. A few designs involve fully suspended microstructures or no suspension at all. The simulation results presented in this paper show the feasibility of reaching CNT synthesis temperature by local resistive heating, while keeping safe temperatures on the chip for the CMOS circuits. As a result, we also designed a CMOS chip containing different CMOS microstructures with the purpose of local CNT synthesis, and the chips were fabricated using a standard AMS 350 nm CMOS process. Layout designs of some of these CMOS microstructures, as well as optical micrographs of these fabricated structures, are presented in this paper.

## 2. Design Approach for CNT Growth Structures in CMOS

To grow CNTs in CMOS chips by thermal CVD process, a microheater as CNT growth structure is required that can locally generate a hotspot of  $\sim\!800\text{--}900$  °C. Therefore, we have investigated the materials commonly used in standard CMOS processes to design efficient microheaters. It is essential to keep the CMOS circuits at a safe temperature, below 300 °C, when the microheater produces the CNT

Sensors **2019**, 19, 4340 4 of 22

synthesis temperature; hence, the design approach to maintain the CMOS-compatible surrounding temperature is also discussed.

#### 2.1. Materials for CMOS Microheaters

The local CNT synthesis temperature was generated by joule heating in the simulations, where an electrical current is passed through a conductor to produce the heat. In our study, we were only considering conduction as a medium of heat transfer, neglecting convection and radiation due their minimal effect in micro scale compared to conduction. The nature of convection can be realized by Rayleigh number (Ra), where higher value of Ra indicates more influence of convective heat transfer, and it was shown that Ra decreases significantly for microscopic structures compared to macroscopic structures; thereby, the effect of convection becomes negligible at the micro level [41]. It was also derived that the heat loss on microstructures due to thermal radiation is less than 1%, even for temperature as high as 1000 °C [41]. Therefore, the dissipated electrical power in resistive heating can be converted to heat by Fourier's law of heat conduction. We have previously derived an equation for a rectangular heater [42], where the maximum temperature (*T*) at the center can be expressed as Equation (1):

$$T = T_0 + \frac{I^2 l^2 \rho}{8w^2 t^2 k} \tag{1}$$

where  $T_0$  is ambient temperature, I is the current through the microheater,  $\rho$  is electrical resistivity, k is thermal conductivity, and l, w, and t are length, width, and thickness of the microheater, respectively.

Materials for microheaters to grow CNTs should have high electrical resistivity ( $\rho$ ) for efficient heating and low thermal conductivity (k) to reduce heat loss in the surroundings. In terms of material parameters, the ratio  $\rho/k$  is an important factor in achieving high temperature on the microheaters by resistive heating. This ratio is proportional to the maximum temperature on the microheater, as shown in Equation (1); hence, a higher value of this ratio is desirable.

Standard CMOS technologies offer several metal interconnect layers comprising Al or Cu, along with conductive polysilicon layers. The melting point of Al is much lower than CNT synthesis temperature, and  $\rho/k$  ratio for both Al and Cu are very low for effective resistive heating. Therefore, we investigated several binary alloy options for both Al and Cu. Alloys provide higher electrical resistivity and lower thermal conductivity than the native form of the involved metals, so higher  $\rho/k$  ratio can be obtained. Polysilicon has a very high melting point, as well as high  $\rho/k$  ratio, making it the most suitable material in CMOS for our microheater application. AMS 350 nm CMOS process uses two polysilicon layers, one polysilicon layer (poly-1) being thicker than the other (poly-2) [43]. A thinner polysilicon layer (poly-2) results in higher electrical resistivity and can also be mechanically beneficial for suspended microstructures, due to less residual stress compared to thicker structures [44].

In a previous study, we showed Cu–Ni alloy to be the best-suited microheater material among other Cu alloys [42]. It should be noted from Equation (1), microheater thickness square ( $t^2$ ) is inversely proportion to microheater temperature, and thickness of the microheater depends on the alloy composition. Although a 40% Cu–60% Ni composition (at.%) has higher  $\rho/k$  ratio, the lower microheater thickness of 70% Cu–30% Ni alloy makes it a more efficient material in this application. A comparison of the relevant material properties (at CNT growth temperature) of copper and its suitable alloys are presented in Table 1.

**Table 1.** Comparison between material properties of Cu and relevant Cu–Ni alloys [45,46].

| Metal Alloy<br>(Composition, at.%) | Melting Point (°C) | Electrical<br>Resistivity, ρ<br>(×10 <sup>-8</sup> Ωm) | Thermal<br>Conductivity, k<br>(Wm <sup>-1</sup> K <sup>-1</sup> ) | Ratio, ρ/k<br>(×10 <sup>-8</sup> Ωm <sup>2</sup> W <sup>-1</sup> K) |

|------------------------------------|--------------------|--------------------------------------------------------|-------------------------------------------------------------------|---------------------------------------------------------------------|

| Cu                                 | 1080               | 8.5                                                    | 340                                                               | 0.025                                                               |

| Cu-Ni (40%/60%)                    | 1200               | 54.5                                                   | 49.3                                                              | 1.105                                                               |

| Cu-Ni (70%/30%)                    | 1150               | 39                                                     | 60.5                                                              | 0.645                                                               |

Sensors **2019**, 19, 4340 5 of 22

In this study, we investigated suitable aluminum alloys for designing metal microheaters since we have designed and fabricated our CMOS chip in AMS 350 nm CMOS process, which offers aluminum metal layers. It should be noted that Al melts at a far lower temperature ( $\sim$ 660 °C) than the required CNT growth temperature ( $\sim$ 900 °C). Several compositions of Al–Ni alloys, however, have a melting point higher than 900 °C. Based on the material properties, tri-nickel aluminide (Ni<sub>3</sub>Al) is the most suitable aluminum alloy for realizing metal microheaters in the AMS 350 nm CMOS process. A comparison of the relevant material properties (at CNT growth temperature) of aluminum and its suitable alloys are presented in Table 2.

| Metal Alloy<br>(Composition, at.%) | Melting Point (°C) | Electrical<br>Resistivity, ρ<br>(×10 <sup>-8</sup> Ωm) | Thermal<br>Conductivity, k<br>(Wm <sup>-1</sup> K <sup>-1</sup> ) | Ratio, ρ/k<br>(×10 <sup>-8</sup> Ωm <sup>2</sup> W <sup>-1</sup> K) |

|------------------------------------|--------------------|--------------------------------------------------------|-------------------------------------------------------------------|---------------------------------------------------------------------|

| Al                                 | 650                | 10.5                                                   | 200                                                               | 0.053                                                               |

| Al-Ni (50%/50%)                    | 1680               | 10                                                     | 72                                                                | 0.139                                                               |

| Ni <sub>3</sub> Al (75%/25%)       | 1400               | 73                                                     | 36                                                                | 2.028                                                               |

**Table 2.** Comparison between material properties of Al and relevant Al–Ni alloys [45–48].

Ni<sub>3</sub>Al alloy has excellent mechanical strength and wear-resistance at high temperatures [49]. The features of this alloy are well-suited for high-temperature applications, such as promising applications in aircraft engines as structural bulk material [50] and MEMS applications (such as micro-actuators) as thin foils [51,52]. This intermetallic phase also has a potential application in microchemical systems as catalysts (microreactors) [52,53].

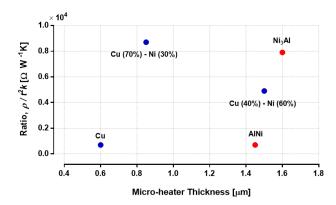

In Equation (1), length (l) and width (w) of the microheater are defined by our design; current (l) is a variable during the joule heating process, and the heater thickness (t) and material properties ( $\rho$ , k) are CMOS-process-dependent parameters. The ratio  $\rho/t^2k$  from the equation is directly proportional to the maximum microheater temperature. Although the value of this ratio depends on the CMOS process, it is modified for the metal microheaters when they are transformed into alloys. Therefore, we plotted this ratio in Figure 2 for five different potential materials from Tables 1 and 2. The values of  $\rho$  and k are taken at CNT synthesis temperature. Thickness of the alloys are calculated based on a 0.6  $\mu$ m thick Al or Cu layer, where atomic weights and mass densities of the associated materials are taken into account. A higher value of the ratio  $\rho/t^2k$  corresponds to a more efficient microheater, allowing room for reducing the l/w ratio to achieve mechanically more robust designs for suspended heaters. Based on the plot in Figure 2, Cu (70%)–Ni (30%) and Ni<sub>3</sub>Al alloys are the most suitable metallic microheater materials among the available options in CMOS for the CNT synthesis application.

The choice between metal and polysilicon microheaters should be based on suitability in CMOS post-processing, although polysilicon has significantly better material properties in terms of using them as microheaters for local CNT synthesis. The metal options are CMOS-process-dependent. Cu–Ni (70%–30%) is the preferred alloy composition if CMOS metal layers are made of Cu, whereas Ni<sub>3</sub>Al alloy is suitable as the microheater material in case Al is used in the metallization layer for the CMOS process. Among the polysilicon options, a thinner polysilicon layer with higher electrical resistivity is more efficient as a microheater.

Sensors **2019**, 19, 4340 6 of 22

**Figure 2.** Influential ratio  $(\rho/t^2k)$  for maximum microheater temperature plotted against total microheater thickness associated with the material.

## 2.2. CMOS-Compatible Chip-Surface Temperature

High temperature (~800–900 °C) is necessary to grow CNTs of small diameter (below 10 nm), which ensures aligning of those CNTs by local electric field [54,55] so that they can be suspended between the two microstructures. Therefore, the microstructure/microheater for synthesizing CNTs needs to produce a local hot region of 900 °C. Even if the synthesis temperature is generated by local resistive heating, the entire chip-surface temperature rises higher than the CMOS-compatible temperature due to thermal conduction, since the microstructures in CMOS are surrounded by dielectric layer. Hence, the target is to achieve high enough thermal gradient around the microheater so that CMOS transistors can reside at safe temperatures.

Maximum thermal gradient around the microheaters can be reached by completely etching the dielectric layer underneath those growth structures; however, the microheaters would suffer from undesirable mechanical deformation. Therefore, it is beneficial to keep some dielectric layer underneath the microheaters as a mechanical support. Having dielectric support underneath also means a heat conduction path to the bulk of the chip. It is trade-off between achieving a high thermal gradient and the keeping mechanical integrity of the microheater. So, our goal is to under-etch a sufficient amount of dielectric to get the required thermal isolation for maintaining CMOS-compatible temperatures, while avoiding destructive microheater deformation.

It is important to note that the high microheater temperature is only required for growing CNTs. Therefore, the concern of compatible temperatures for CMOS transistors is limited to the duration of the one-time CNT synthesis process, which takes around 5 min. The CNT-based sensor can operate at room temperature during gas-sensing operation.

### 3. Thermal Analysis of CMOS Microstructures

We designed several microheaters using the available materials in the standard CMOS process and performed thermoelectric and thermomechanical simulations using Multiphysics simulation software, ANSYS. All microheaters are mechanically stable according to the thermomechanical analysis; however, in practice, the stability of suspended microheaters is significantly affected by the wet etching process. Most of the designed microheaters are partially suspended, meaning a limited amount of the dielectric layer stays underneath the heaters. The simulated models also have a bulk silicon layer and a chip-packaging material layer below the dielectric layer. Room temperature is considered in the bottom surface of the package material as a boundary condition, which is a practical assumption if a heat sink is used during the process. The silicon substrate will be in direct contact with a heat sink if the CNT synthesis process is carried out at the wafer-level during a potential high-volume production, which will further facilitate in maintaining CMOS-compatible temperature.

We have previously worked on thermomechanical simulations of Cu–Ni and polysilicon microheaters [42,56]. However, in the later stage, we chose a standard AMS 350 nm CMOS technology

Sensors **2019**, 19, 4340 7 of 22

to design and fabricate the microstructures (detailed in Section 4), which uses aluminum as the interconnecting metal layers. Therefore, in this article, we investigated Al-based alloys suitable for our application, which is reported in Section 2.1, and, consequently, the simulations of the Ni<sub>3</sub>Al alloy microheaters are presented in this section. During the CMOS chip design stage, we also found that our previous partially suspended microheater (PSM)-design approaches [42,56] would have some challenges in post-processing and CNT growth, which are discussed in Section 5.3. Hence, we used new PSM-design approaches to overcome those challenges and performed thermal simulations on polysilicon and Cu–Ni microheaters, accordingly. These new simulation results of the mentioned microheaters are also presented in this section.

## 3.1. Polysilicon Microheaters

The polysilicon microheaters are designed with two different layers: poly-1 and poly-2. In the simulations, the considered sheet resistances of poly-1 and poly-2 are  $\sim$ 6  $\Omega$ /sq and  $\sim$ 18  $\Omega$ /sq, respectively. The fabricated polysilicon microheaters presented in Section 4.2 have  $\sim$ 10  $\Omega$ /sq and  $\sim$ 50  $\Omega$ /sq sheet resistances for poly-1 and poly-2, respectively. The conservative sheet-resistance values in the simulation mean the fabricated CMOS microstructures should provide better performance as heaters compared to the simulation results. All polysilicon heaters are simulated with 0.85  $\mu$ m thickness, even though their actual thickness in a CMOS process will be 3–4 times lower. Therefore, the polysilicon heaters will have higher resistance in practice, which is beneficial for resistive heating. In the FEM simulations, higher polysilicon thickness helps to reduce the number of elements for meshing and, consequently, limits the processing time of each simulation.

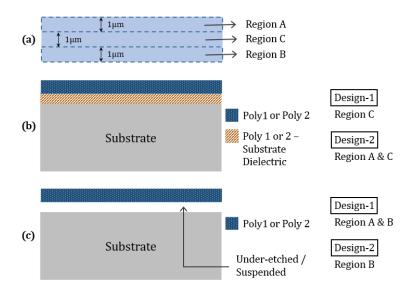

## 3.1.1. Polysilicon Microheaters with Limited Under-Etching

The microheaters can be partially suspended along their entire length; Figure 3 reveals the suspended and non-suspended areas. Figure 3a illustrates the microheater surface area, which was divided into three regions. We have presented two PSM designs in this section, where region C is non-suspended and region B is suspended in both designs. A cross-sectional illustration of non-suspended and suspended microheater areas is shown in Figure 3b,c, respectively. The non-suspended regions have a dielectric layer underneath that mechanically supports the microheater.

The designed polysilicon PSMs are 30  $\mu$ m long and 3  $\mu$ m wide, giving around 60 and 180  $\Omega$  resistance to poly-1 and poly-2 heaters, respectively, when they reach the CNT synthesis temperature. In these models, both region A and B are suspended, keeping dielectric support in region C for design-1, while only region A is suspended for design-2. In design-2, region B can be blocked from under-etching by putting a mask using the top metal layers of the CMOS design on one side of the microheater, as detailed in Section 5.3.

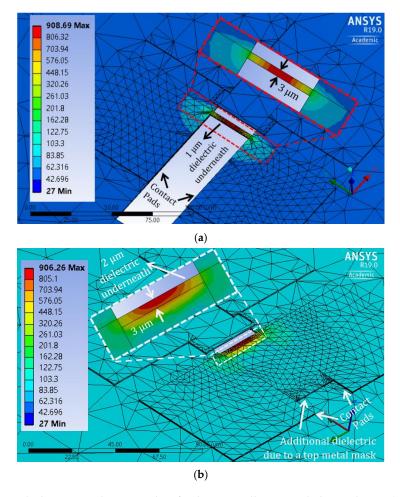

Figure 4 shows the thermal simulation results for both designs, where poly-1 was used as the heater material. The microheaters locally generate the required CNT synthesis temperature in their centers. Design-1 (Figure 4a) achieves a high thermal gradient around the heater due to the 1  $\mu m$  dielectric etching on both sides (region A and B) of the 3  $\mu m$  wide heater, leaving 1  $\mu m$  wide dielectric in the middle (region C). Design-2 (Figure 4b) has a 1  $\mu m$  wide suspension on one side of the heater (region B), leaving a 2  $\mu m$  wide dielectric layer (region A and C) underneath the heater. Suspended microheater regions produce a higher thermal gradient around them. Therefore, the microheater in design-2 has lower thermal isolation than the microheater in design-1. Moreover, since a top metal layer blocks heater under-etching on one side (region A), the dielectric layer will remain in the blocked region near that side of the heater, as indicated in Figure 4b, creating more heat-conduction paths. Even with lower thermal isolation of the heater, the average surrounding surface temperature in design-2 is near 100 °C. Therefore, both poly-1 PSM designs maintain the CMOS-compatible temperature in the chip, while producing a local hotspot for CNT synthesis. From a mechanical viewpoint, design-2 is

Sensors 2019, 19, 4340 8 of 22

more preferable over design-1, as it involves less dielectric etching underneath the heater. In terms of power consumption, design-1 (~35 mW) is more efficient than design-2 (~80 mW).

**Figure 3.** Partially suspended polysilicon microheater design illustrations. (a) Microheater surface area; (b) cross-sectional view of non-suspended region, and (c) cross-sectional view of suspended region.

**Figure 4.** Thermal–electric simulation results of poly-1 partially suspended microheater (PSM) designs: (a) design-1 and (b) design-2.

Sensors **2019**, 19, 4340 9 of 22

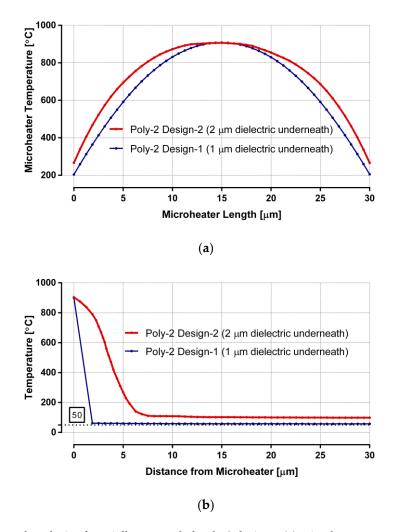

The plots in Figure 5 show the thermal-simulation results of poly-2 microheaters for both design-1 and design-2. Temperatures along the length of the heaters are plotted in Figure 5a. The graphs form parabolic shapes (as predicted by Equation (1)) with the maximum temperature (~900 °C) at the center of the heaters, while CMOS-compatible temperatures are reached even at both ends of the heaters. The power requirements for these heaters are similar to the corresponding poly-1 designs. Plots in Figure 5b indicate the temperature drops when moving away from the heaters. High thermal gradient around the heaters is apparent in the plots. Surface temperature in design-1 reaches ~50 °C, within 25  $\mu$ m away from the heater, achieving an average thermal gradient of 34 °C per micrometer around the heater. In design-2, the surface temperature becomes ~100 °C, within 25  $\mu$ m away from the heater, indicating an average thermal gradient of 32 °C per micrometer around the heater.

**Figure 5.** Thermal analysis of partially suspended poly-2 designs: (a) microheater temperature along its length; (b) temperature distribution from the center of the heater to the surrounding surface.

## 3.1.2. Non-Suspended and Fully Suspended Polysilicon Microheaters

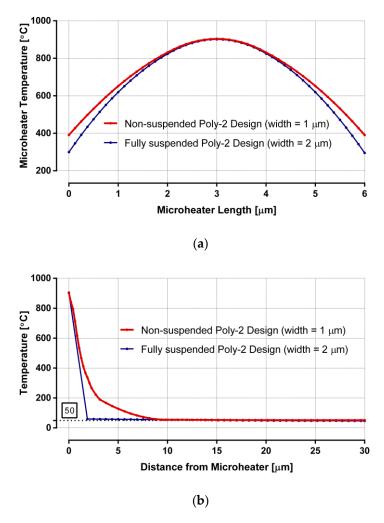

Two polysilicon microheaters were modelled with a reduced length of 6  $\mu$ m for simulating non-suspended and fully suspended designs. The widths of the non-suspended and fully suspended designs are 1 and 2  $\mu$ m, respectively. In the case of the non-suspended design, reduced surface area of the microheater means less of a heat-conduction path through the dielectric layer. The reduced length for a fully suspended microheater offers lower risk of deformation. Although it may still suffer from buckling and stiction, the width of this design was extended to 2  $\mu$ m for improving mechanical

steadiness. At around 900 °C, resistances of fully suspended and non-suspended designs are ~55 and ~110  $\Omega$ , respectively.

These microheaters are only designed with poly-2 layer since it has higher electrical resistivity among the polysilicon options. Thermal responses of both non-suspended and fully suspended designs are plotted in Figure 6. Plots in Figure 6a present the temperatures of the heaters, both having a 2  $\mu$ m long region in the center, where the heaters reach more than 800 °C, an optimum region to grow low-diameter CNTs. Plots in Figure 6b show that the average surrounding chip temperature reaches far below CMOS-compatible temperature for both designs. Both designs have a very high thermal gradient around the heaters, indicated by the sharp temperature decrease. They also have a similar power requirement of ~20 mW. The non-suspended heater is a clear favorite among these designs, as it avoids mechanical deformation and does not require any dielectric under-etching steps during the CMOS post-processing.

**Figure 6.** Thermal analysis of non-suspended and fully suspended poly-2 designs: (a) microheater temperature along its length; (b) temperature distribution from the center of the heater to the surrounding surface.

## 3.2. Tri-Nickel Aluminide (Ni<sub>3</sub>Al) Microheaters

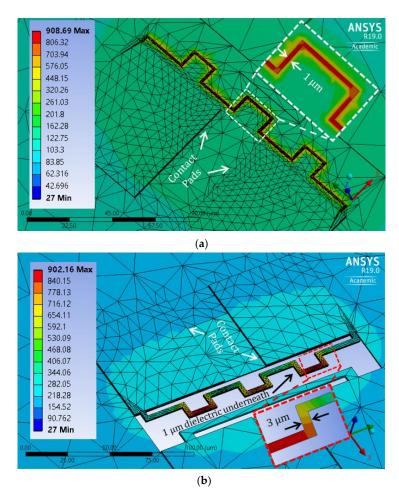

For the standard CMOS process with Al metallization, microheaters were designed and simulated using tri-nickel aluminide (Ni $_3$ Al). Figure 7 shows the thermal simulation results for both non-suspended and partially suspended designs. Around a 1  $\mu$ m thick layer of Ni needs to be deposited on a 0.6  $\mu$ m thick Al layer to obtain the Ni $_3$ Al phase, considering the atomic weights and

mass densities of Ni, Al, and Ni $_3$ Al. Therefore, these microheaters are designed with a 1.6  $\mu$ m thickness. The width of non-suspended design in Figure 7a is 1  $\mu$ m, whereas PSM (with limited under-etching along the length, similar to design-1 from previous section) in Figure 7b has a 3  $\mu$ m width. PSMs with a greater width would yield higher mechanical stability in the under-etched design, while lower width of the non-suspended design results in less heat conduction on the substrate.

**Figure 7.** Thermal–electric simulation results of Ni<sub>3</sub>Al designs: (a) non-suspended and (b) partially suspended.

For efficient resistive heating, the microheaters need sufficiently high resistance. Hence, the length of the metal heater designs was extended to ~240  $\mu m$  for increasing heater resistance. The PSM design had ~15  $\Omega$  room temperature resistance, which goes above 35  $\Omega$  at the CNT synthesis temperature due to increase in Ni<sub>3</sub>Al resistivity at the elevated temperature. The non-suspended design has a 3-times-higher heater resistance due to a 3-times-lower width. The non-suspended design (Figure 7a) produces a chip surface temperature above 300 °C, due to lack of thermal isolation of the heater. This post-processing temperature is not suitable for CMOS circuits. However, the partially suspended design (Figure 7b) has sufficient thermal isolation for the heater, resulting in a CMOS-compatible surrounding temperature of ~200 °C. It requires around 350 and 150 mW power for the non-suspended and partially suspended microheaters, respectively, to generate the CNT synthesis temperature.

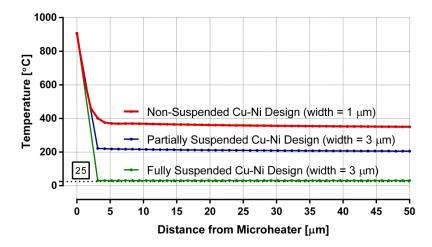

#### 3.3. Cupronickel (Cu-Ni) Microheaters

Cu–Ni microheaters were designed and simulated for the CMOS processes that use Cu as interconnecting metal. Material properties of 70% Cu–30% Ni alloy composition is used for the heaters. Considering the atomic weights and mass densities of Cu and Ni, the heaters are modelled with

a 0.85  $\mu$ m thickness. Depositing 0.25  $\mu$ m thick Ni on top of a 0.6  $\mu$ m thick Cu layer is suitable for achieving 70% Cu–30% Ni binary alloy composition upon annealing. The length and width of the heaters in both non-suspended and partially suspended designs are kept same as the Ni<sub>3</sub>Al microheater designs. Heater resistances of Cu–Ni designs are also similar to the Ni<sub>3</sub>Al heaters, as sheet resistances of both Cu–Ni and Ni<sub>3</sub>Al heaters are alike at near CNT synthesis temperature.

Microheater temperatures, along with the surrounding surface temperatures, are plotted for non-suspended, partially suspended, and fully suspended Cu-Ni designs in Figure 8. All these heaters have a local hot region of ~900 °C for growing CNTs, and the temperature starts to drop when moving away from the heaters. The non-suspended design reaches a CMOS-incompatible surface temperature of ~350 °C, while the PSM design manages to achieve a CMOS-compatible chip surface temperature of ~200 °C. Average surrounding temperature of the fully suspended Cu–Ni design drops down to near room temperature. At 25  $\mu$ m away from the heaters, the average thermal gradients around the non-suspended, partially suspended, and fully suspended Cu–Ni microheaters are 22, 28, and 35 °C per micrometer, respectively. The power requirements of non-suspended and partially suspended designs are similar to the respective Ni<sub>3</sub>Al designs, while the fully suspended heater consumes less than 5 mW of power. Even though the fully suspended heater has the maximum thermal isolation and lowest power consumption, the design is not practically feasible, as it is prone to mechanical deformation. Therefore, PSM is the most suitable among the Cu–Ni designs for our application.

**Figure 8.** Temperature distribution from the center of different cupronickel microheaters to the surrounding surface.

## 4. Fabricated CMOS Microstructures for CNT Synthesis

We selected a standard AMS 350 nm CMOS process to fabricate microstructures for locally synthesizing CNTs. In this CMOS technology, aluminum is used for metallization, and copper is not available. Therefore, aluminum and polysilicon layers were used for designing and fabricating the CNT growth structures. The designed  $3 \text{ mm} \times 3 \text{ mm}$  CMOS chip contains a variety of microstructures, some of which were presented in one of our previous papers [57]. In this article, we present the layout and optical micrograph of the designs relevant to the simulated designs we have presented in Section 3.

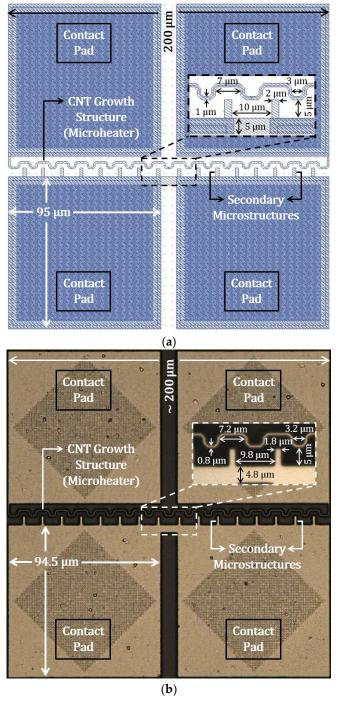

#### 4.1. CNT Growth Structures Using Aluminum Layers

Layout design and optical micrograph of the fabricated aluminum microstructures are presented in Figure 9a,b, respectively. The top metal layer was used for the aluminum designs. In this wave-shaped microheater design, the length of the heater is efficiently increased to over 350  $\mu m$ . The designed width of the heater is 1  $\mu m$ , resulting in a measured resistance of ~50  $\Omega$ . To generate CNT synthesis temperature, Ni needs to be deposited for producing Ni<sub>3</sub>Al binary alloy, which will increase both thickness and electrical resistivity of the microheater. Several rectangular beams are used as secondary

microstructures, which go in between the waves of the microheater for producing a high electric field at the beam tips during the CNT growth process, so that some of the synthesized CNTs can be connected to the secondary structures after being guided by the local electric field. The contact pads for the microstructures have a surface area of 95  $\mu$ m  $\times$  95  $\mu$ m, providing sufficient area for wire bonding. Dimensions measured from the optical micrograph of the fabricated Al microstructures reflect the corresponding dimensions of the layout design.

**Figure 9.** Aluminum CNT growth structures in AMS 350 nm process: (a) layout design and (b) optical micrograph.

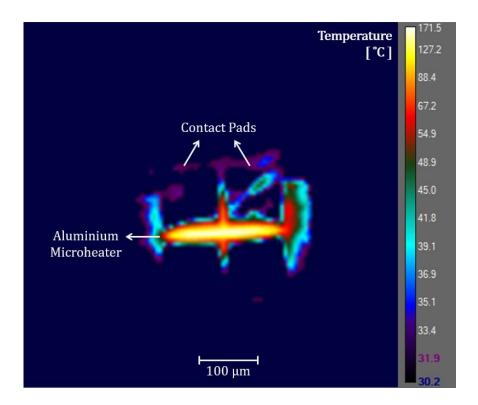

We attempted thermal microscopy of the CMOS microheaters using a high-performance infrared camera, FLIR A6750sc MWIR with a 4X microscopic lens. While the CMOS-chip-surface temperatures

can be measured easily, measuring temperatures on the microheaters was an issue. The camera operates at 3–5  $\mu$ m wavelengths, with the minimum spot pixel size of 3  $\mu$ m  $\times$  3  $\mu$ m. The camera also needs an array of 3  $\times$  3 pixels for an adequate thermal measurement. Hence, the narrowest microstructure dimension needs to be at least ~9  $\mu$ m to obtain acceptable measurements, while most of our microheaters only have ~1  $\mu$ m widths. Therefore, we did not get accurate temperature data for the microheaters, as the obtained temperature values of the microheaters have an average of the heater temperature and surrounding area temperature of the heater.

Figure 10 shows an infrared image of the Al microheater presented in Figure 9. The heater temperature was controlled by joule heating. Although maximum temperature on the microheater appears to be  $\sim$ 170 °C in Figure 10, the actual heater temperature was much higher. This was confirmed since the Al microheater was melted at the region of maximum temperature when the electrical current through the heater was slightly increased. Therefore, we could estimate that the actual temperature on that hottest spot of the aluminum microheater was  $\sim$ 660 °C (melting temperature of Al). The thermal measurement of the surface surrounding the microheater was accurate, which shows a temperature of  $\sim$ 30 °C. Although the temperature measurement on the microheater was not accurate due to resolution limitation, it is still a positive indication that the surrounding CMOS chip area remains at near room temperature while the Al heater reaches near melting temperature. This shows a convincing sign toward the agreement with the thermal simulation results and maintaining CMOS-compatible temperatures on the chip surface when the microheaters would reach CNT growth temperatures.

Figure 10. Thermal micrograph of an aluminum microheater on a CMOS chip.

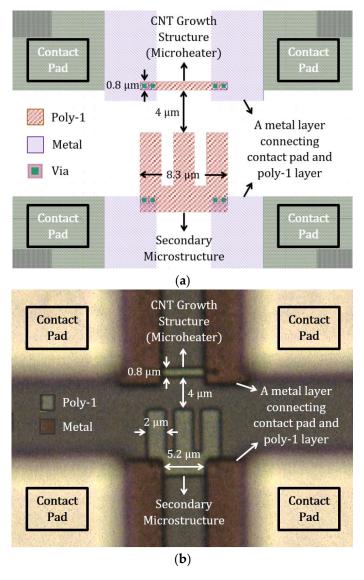

### 4.2. CNT Growth Structures Using Polysilicon Layers

A poly-1 design for local CNT synthesis application is shown in Figure 11. The CMOS layout design in Figure 11a illustrates all the comprised layers where the vias provide access to metal layers for the polysilicon structures. The extended metal layer aids in designing an 8.3  $\mu$ m long heater, while keeping a 15  $\mu$ m distance between the contact pads. The microheater is 0.8  $\mu$ m wide and has a measured resistance of ~100  $\Omega$ . The heater and secondary structures are 4  $\mu$ m apart. Dimensions of the microstructure layouts are properly translated to the fabricated polysilicon structures, as seen in

the optical micrograph in Figure 11b. This polysilicon microheater has comparable dimensions to one of the simulated heaters in Section 3.1.2.

**Figure 11.** Poly-1 CNT growth structures in AMS 350 nm process: (a) layout design and (b) optical micrograph.

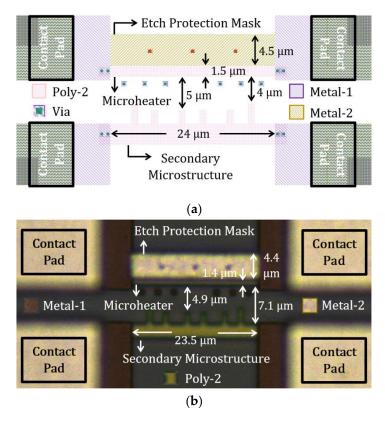

Figure 12a shows the layout of a poly-2 design, and Figure 12b shows the corresponding optical micrograph of the fabricated CMOS microstructures. The design involves a poly-2 layer, two different metal layers, and vias for electrical connection between layers. Some additional vias are purposely placed in front of the microheater to limit dielectric etching in those regions. In this design, a top metal layer (metal-2) was used as an etch protection mask; hence, the dielectric layer underneath that metal layer is not etched. This poly-2 design resembles a simulated model (design-2) from Section 3.1.1, where the heater is only under-etched from the side facing secondary microstructures. The heater is ~25  $\mu m$  long and 1.5  $\mu m$  wide. It has a high measured resistance of ~1 K $\Omega$  due to high poly-2 resistivity. The optical micrograph shows the fabricated microstructures, which were rendered well from the designed CMOS layout.

Sensors 2019, 19, 4340 16 of 22

**Figure 12.** Poly-2 CNT growth structures in AMS 350 nm process: (a) layout design and (b) optical micrograph.

#### 5. Discussion

Our fabricated CMOS chips need to go through several post-processing steps for growing CNTs. The process complexity will vary depending on the microheater design; non-suspended designs are easier to realize than the suspended ones. For the metal microheaters, alloying is an added step, where the process complexity also differs among the two preferred alloy options. Under-etching approaches of different partially suspended microheaters are included in this part. In prior publications from our group, synthesized CNTs on custom-designed PolyMUMPS [30,58] and SOIMUMPS [31,54] microstructures were presented with relevant SEM and S(T)EM analyses. Polysilicon CNT growth structures used in the PolyMUMPS process have good resemblance with CMOS for CNT synthesis process demonstration.

#### 5.1. CMOS Post-Processing to Realize CNT Growth Structures

Necessary CMOS post-processing to synthesize CNTs on a CMOS chip can be divided into two main stages. The initial stage involves etching the dielectric layers for exposing and under-etching the CNT growth structures in CMOS to achieve high thermal isolation around them. In the case of metal microheaters, this stage also includes making relevant binary alloys. The final stage of the post-processing involves depositing a catalyst layer and growing CNTs on the CMOS microstructures by local thermal CVD process.

The metal and polysilicon layers of a standard CMOS chip are covered with a dielectric layer for electrical isolation, and the entire chip surface is covered with passivation layer(s) for protection from surroundings. In CMOS chip design, we can purposely select regions where the passivation layer(s) can be avoided. It enables an exposed top metal layer surrounded by a dielectric layer. Therefore, the CNT growth structures made from the top metal layer will be readily exposed and available for nickel deposition to produce the alloys.

Sensors **2019**, 19, 4340 17 of 22

Nickel can be deposited on the metal tracks (Al or Cu) by evaporation, sputtering, electroplating, or electroless plating. Evaporation and sputtering will need dedicated masks for patterning Ni deposition. Electroless plating can be selective toward deposition on exposed metal tracks, whereas electroplating gives selective deposition on exposed metal tracks that are electrically connected to the electrodes in the electroplating baths. Hence, with an appropriate design, mask-less Ni deposition is possible with plating techniques, where electroplating gives the highest design freedom. Alloying of the Al/Ni bi-layer into homogenous Ni<sub>3</sub>Al is performed through local resistive heating, passing a current through the microheater while in inert atmosphere. The method is similar to that used in the formation of a desired composition of cupronickel alloy.

After the alloying process, the metal microheaters are partially suspended for sufficient thermal isolation during resistive heating. Dry etching by RIE (Reactive Ion Etching) can be performed for anisotropic dielectric etching, followed by a wet etching process to partially release the microheaters. The amount of microheater under-etching depends on the wet etching duration for a specific chemical etchant. Therefore, the required amount of heater suspension can be achieved by controlling the etching duration.

In the case of polysilicon heaters, a thick layer of dielectric is removed by RIE to expose the polysilicon layers. Only this step is required in the initial post-processing stage for non-suspended heaters. However, partially or fully suspended microheaters need an additional step of wet dielectric etching. Even though RIE is anisotropic, it can still cause some heater undercuts, which can be a desirable effect for our application. The wet etching step will no longer be required if the microheaters have sufficient undercuts to obtain required thermal isolation.

Once the CNT growth structures are prepared, a thin catalyst layer ( $\sim$ 5 nm) is deposited in the beginning of the final post-processing stage. Iron or nickel is commonly used as the catalyst material, which can be deposited by thermal evaporation, e-beam evaporation, or sputtering. The thin metal layer transforms into nanoparticles at  $\sim$ 900 °C, during resistive heating of the CNT growth structure in the CVD chamber. CNTs start to grow when a carbon-containing precursor gas released in the chamber interacts with the catalyst nanoparticles.

The mentioned CMOS post-processing steps are needed at the research level since they will be performed on individual CMOS chips. However, those process steps may be included in a dedicated process designed for CNT-to-CMOS integration, which can be carried out in wafer-level fabrication for manufacturing commercially viable CNT-based sensors. Zhou et al. [26] previously demonstrated CNT growth on polysilicon structures in CMOS involving various post-CMOS microfabrication processes that we avoid in our approach, with the vision to incorporate the CNT synthesis process in a CMOS technology at wafer-level.

## 5.2. Tri-Nickel Aluminide vs. Cupronickel Microheaters

Forming a tri-nickel aluminide alloy may be more challenging than cupronickel alloy, because of the native oxide layer on aluminum, with Al having a lower electrochemical potential than Cu. Moreover, during the formation of a Ni<sub>3</sub>Al alloy, undesirable intermetallic alloys (such as Al<sub>3</sub>Ni, Al<sub>3</sub>Ni<sub>2</sub>) with a melting temperature lower than 900 °C could also form. A detailed process development is needed to ensure a final microheater composition compatible with high-temperature operation. A certain flexibility in the composition is allowed, however, as both the Ni and the AlNi phases have even higher melting temperatures than that of Ni<sub>3</sub>Al. For Cu–Ni, the exact composition is not a critical parameter, since Cu and Ni form a solid solution, being completely miscible.

Electrical resistivity to the thermal conductivity ratio ( $\rho/k$ ) of Ni<sub>3</sub>Al is almost twice that of Cu–Ni (70%–30%) at CNT synthesis temperature (~900 °C). A higher  $\rho/k$  ratio is desirable for the efficient resistive heating of microheaters. However, the thickness of a Ni<sub>3</sub>Al microheater is much higher than that of a Cu–Ni (70%–30%) microheater for a specific Al or Cu thickness, which reduces a Ni<sub>3</sub>Al microheater's resistance and, consequently, makes it less efficient for heat generation by resistive

Sensors **2019**, 19, 4340 18 of 22

heating. Considering both alloy formation challenges and material efficiency as a microheater, a CMOS process using Cu for metallization is preferred over the one using Al.

#### 5.3. Under-Etching Approaches for PSMs

Two different PSM designs were presented in Section 3.1.1. Design-1 will have limited under-etching along the length from both sides of the heater, whereas design-2 will be under-etched from one side since the other side has a metal mask for avoiding dielectric etching. Our fabricated polysilicon heater in Figure 11 is suitable for design-1 under-etching approach, and the heater in Figure 12 matches the under-etching strategy for design-2. For both designs, under-etching can be obtained by isotropic wet etching, and the amount of suspension depends on the wet etching duration. Different etching times should be attempted to find the optimum duration for the wet etching process to get the required amount of under-etching. The wet etching process may not even be required if the heaters have undercuts within a desired range during the dry etching process, as discussed in Section 5.1.

No mask is needed for the etching process of design-1, but design-2 has a built-in etch protection mask. A top metal block (interconnect layer in CMOS) is placed on one side of the polysilicon microheater, which will act as mask to protect that side of the heater from etching. Therefore, the dielectric layer beneath that metal block will remain. As a result, during the resistive heating process, heat from the microheater will also conduct to the surroundings through the dielectric from that side, which would contribute in making the chip from design-2 hotter than that from design-1.

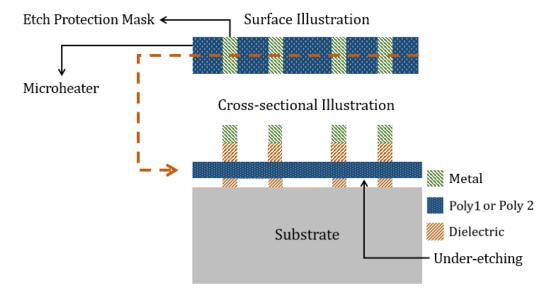

We have previously designed PSMs using selective patterned under-etching [56]. The surface and cross-sectional view of such a design is shown in Figure 13. Patterned microheater under-etching also needs metal blocks as built-in masks, which will have dielectric material beneath them. Therefore, the top surface of the microheater will be covered with dielectric on the areas where metal blocks are placed above them, as seen in the cross-sectional illustration of Figure 13. This would cause further heat conduction through the top dielectric layer when the microheater is activated, making the chip relatively hotter. Moreover, CNTs cannot grow on the microheater surface, which is covered with dielectric. The improved PSM design approaches presented in this paper solve these issues. Although the microheaters with limited under-etching along their length would be more vulnerable to thermomechanical stress compared to heaters with patterned under-etching, the prior etching approach is still preferred from an overall perspective for PSM designs in our CNT synthesis application.

Figure 13. Surface and cross-sectional illustration of a selectively under-etched PSM design.

Sensors 2019, 19, 4340 19 of 22

#### 6. Conclusions and Future Work

We presented several designs of CNT growth microstructures (microheaters) using the materials available in standard CMOS process. Polysilicon is the most suitable material in CMOS to serve as a microheater. The metal options (Al or Cu) need to be alloyed with Ni to produce efficient microheaters for the CNT synthesis application. Tri-nickel aluminide and cupronickel (70% Cu–30% Ni) were chosen as the binary alloys from the investigated materials.

Thermal analyses of the CMOS microheaters show that they can have CNT synthesis temperature ( $\sim$ 900 °C) on their surface, while having a high thermal gradient to achieve a CMOS-compatible temperature (below 300 °C) on the remaining chip area. Most of the designed microheaters need partial suspension to obtain necessary thermal isolation for CMOS compatibility. The heaters should have sufficient under-etching to obtain a high thermal gradient around them, while avoiding significant mechanical deformation.

CNT growth structures were fabricated in a standard AMS 350 nm CMOS process, using aluminum and polysilicon layers. The microstructures are properly realized in the CMOS chip, as seen from the presented layout designs and optical micrographs of the fabricated structures. The CMOS chips are required to undergo several post-processing steps to prepare the microstructures for local CNT synthesis.

The metal microheaters (Al or Cu) on the fabricated CMOS chips are already exposed; thus, they need alloying as an initial post-processing step, followed by partial dielectric under-etching, using dry and wet etching methods. The polysilicon microheaters need to be exposed first by dry etching of dielectrics and may require wet etching for partial suspension if there are insufficient undercuts on the heaters during the RIE process. The wet etching process is also avoided if the non-suspended polysilicon microheaters manage to obtain required thermal isolation. Once the microheaters are prepared, a thin catalyst layer needs to be deposited on the CMOS chip before carrying out the CVD process for growing CNTs on the microheaters in the final post-processing step.

We already have an established process for locally synthesizing CNTs on MEMS growth structures. However, the CNT growth structures in CMOS need additional processing steps, as discussed for enabling them to obtain the CNT synthesis temperature in a CMOS-compatible environment. These post-processing steps are currently being developed in our cleanroom, using the fabricated CMOS chips. Our next goal is to locally grow CNTs on the dedicated microstructures in the custom-designed CMOS chips. Direct CNT–CMOS integration will be established once the CNTs are suspended between the CMOS microstructures, and the CNT-based prototype sensor can be tested for gas sensing.

**Author Contributions:** Conceptualization, K.E.A., A.R., M.A., and B.Q.T.; methodology, A.R.; software (Thermal Simulations), A.R.; software (CMOS Chip Design), A.R., M.A., and P.H.; formal analysis, A.R.; investigation, A.R.; data curation, A.R.; writing—original draft preparation, A.R.; writing—review and editing, K.E.A., A.R., B.Q.T., M.A., and P.H.; validation, K.E.A. and M.A.; visualization, A.R.; supervision, K.E.A., M.A., and P.H.; funding acquisition, K.E.A.

Funding: This research received no external funding.

**Acknowledgments:** The Research Council of Norway is acknowledged for the support to the Norwegian Micro- and Nano-Fabrication Facility, NorFab, project number 245963/F50, and the Norwegian PhD Network on Nanotechnology for Microsystems, Nano-Network, project number 221860/F60.

Conflicts of Interest: The authors declare no conflict of interest.

## References

- 1. Chen, A.; Chatterjee, S. Nanomaterials based electrochemical sensors for biomedical applications. *Chem. Soc. Rev.* **2013**, 42, 5425–5438. [CrossRef] [PubMed]

- 2. Bai, J.; Zhou, B. Titanium Dioxide Nanomaterials for Sensor Applications. *Chem. Rev.* **2014**, *114*, 10131–10176. [CrossRef] [PubMed]

- 3. Putzbach, W.; Ronkainen, J.N. Immobilization Techniques in the Fabrication of Nanomaterial-Based Electrochemical Biosensors: A Review. *Sensors* **2013**, *13*, 4811–4840. [CrossRef] [PubMed]

Sensors **2019**, 19, 4340 20 of 22

4. Jiménez-Cadena, G.; Riu, J.; Rius, F.X. Gas sensors based on nanostructured materials. *Analyst* **2007**, *132*, 1083–1099. [CrossRef] [PubMed]

- 5. Swati, S.; Marc, M. A new approach to gas sensing with nanotechnology. *Philos. Trans. R. Soc. A Math. Phys. Eng. Sci.* **2012**, 370, 2448–2473.

- 6. Abu-Salah, M.K.; Alrokyan, S.A.; Khan, M.N.; Ansari, A.A. Nanomaterials as Analytical Tools for Genosensors. *Sensors* **2010**, *10*, 963–993. [CrossRef] [PubMed]

- 7. Xu, K.; Fu, C.; Gao, Z.; Wei, F.; Ying, Y.; Xu, C.; Fu, G. Nanomaterial-based gas sensors: A review. *Instrum. Sci. Technol.* **2018**, *46*, 115–145. [CrossRef]

- 8. Kumar, S.; Pavelyev, V.; Mishra, P.; Tripathi, N. A review on chemiresistive gas sensors based on carbon nanotubes: Device and technology transformation. *Sensors Actuators A Phys.* **2018**, 283, 174–186. [CrossRef]

- 9. Abraham, J.K.; Philip, B.; Witchurch, A.; Varadan, V.K.; Reddy, C.C. A compact wireless gas sensor using a carbon nanotube/PMMA thin film chemiresistor. *Smart Mater. Struct.* **2004**, *13*, 1045–1049. [CrossRef]

- 10. Kong, J.; Franklin, N.R.; Zhou, C.; Chapline, M.G.; Peng, S.; Cho, K.; Dai, H. Nanotube Molecular Wires as Chemical Sensors. *Science* **2000**, 287, 622–625. [CrossRef]

- 11. Lu, Y.; Li, J.; Han, J.; Ng, H.-T.; Binder, C.; Partridge, C.; Meyyappan, M. Room temperature methane detection using palladium loaded single-walled carbon nanotube sensors. *Chem. Phys. Lett.* **2004**, *391*, 344–348. [CrossRef]

- 12. Sin, M.L.Y.; Chow, G.C.T.; Wong, G.M.K.; Li, W.J.; Leong, P.H.W.; Wong, K.W. Ultralow-Power Alcohol Vapor Sensors Using Chemically Functionalized Multiwalled Carbon Nanotubes. *IEEE Trans. Nanotechnol.* **2007**, *6*, 571–577. [CrossRef]

- 13. Wang, X.; Li, Q.; Xie, J.; Jin, Z.; Wang, J.; Li, Y.; Jiang, K.; Fan, S. Fabrication of Ultralong and Electrically Uniform Single-Walled Carbon Nanotubes on Clean Substrates. *Nano Lett.* **2009**, *9*, 3137–3141. [CrossRef] [PubMed]

- 14. Saito, R.; Dresselhaus, G.; Dresselhaus, M.S. *Physical Properties of Carbon Nanotubes*; Imperial College Press: London, UK, 1998; ISBN 978-1-78326-241-0.

- 15. Martel, R.; Schmidt, T.; Shea, H.R.; Hertel, T.; Avouris, P. Single- and multi-wall carbon nanotube field-effect transistors. *Appl. Phys. Lett.* **1998**, 73, 2447–2449. [CrossRef]

- 16. Kim, P.; Shi, L.; Majumdar, A.; McEuen, P.L. Thermal Transport Measurements of Individual Multiwalled Nanotubes. *Phys. Rev. Lett.* **2001**, *87*, 215502. [CrossRef] [PubMed]

- 17. Baughman, R.H.; Zakhidov, A.A.; de Heer, W.A. Carbon Nanotubes–the Route Toward Applications. *Science* **2002**, 297, 787–792. [CrossRef]

- 18. De Volder, M.F.L.; Tawfick, S.H.; Baughman, R.H.; Hart, A.J. Carbon Nanotubes: Present and Future Commercial Applications. *Science* **2013**, *339*, 535–539. [CrossRef]

- 19. Alamusi; Hu, N.; Fukunaga, H.; Atobe, S.; Liu, Y.; Li, J. Piezoresistive Strain Sensors Made from Carbon Nanotubes Based Polymer Nanocomposites. *Sensors* **2011**, *11*, 10691–10723. [CrossRef]

- 20. Zhu, Z.; Garcia-Gancedo, L.; Flewitt, A.J.; Xie, H.; Moussy, F.; Milne, W.I. A Critical Review of Glucose Biosensors Based on Carbon Nanomaterials: Carbon Nanotubes and Graphene. *Sensors* **2012**, *12*, 5996–6022. [CrossRef]

- 21. Tripathi, N.; Pavelyev, V.; Islam, S.S. Synthesis of carbon nanotubes using green plant extract as catalyst: Unconventional concept and its realization. *Appl. Nanosci.* **2017**, *7*, 557–566. [CrossRef]

- 22. Penza, M.; Rossi, R.; Alvisi, M.; Cassano, G.; Signore, M.A.; Serra, E.; Giorgi, R. Pt- and Pd-nanoclusters functionalized carbon nanotubes networked films for sub-ppm gas sensors. *Sens. Actuators B Chem.* **2008**, 135, 289–297. [CrossRef]

- 23. Qi, P.; Vermesh, O.; Grecu, M.; Javey, A.; Wang, Q.; Dai, H.; Peng, S.; Cho, K.J. Toward Large Arrays of Multiplex Functionalized Carbon Nanotube Sensors for Highly Sensitive and Selective Molecular Detection. *Nano Lett.* **2003**, *3*, 347–351. [CrossRef]

- 24. Nguyen, Q.L.; Phan, Q.P.; Duong, N.H.; Nguyen, D.C.; Nguyen, H.L. Enhancement of NH<sub>3</sub> Gas Sensitivity at Room Temperature by Carbon Nanotube-Based Sensor Coated with Co Nanoparticles. *Sensors* **2013**, *13*, 1754–1762. [CrossRef] [PubMed]

- 25. Englander, O.; Christensen, D.; Lin, L. Local synthesis of silicon nanowires and carbon nanotubes on microbridges. *Appl. Phys. Lett.* **2003**, *82*, 4797–4799. [CrossRef]

- 26. Zhou, Y.; Johnson, J.L.; Ural, A.; Xie, H. Localized Growth of Carbon Nanotubes on CMOS Substrate at Room Temperature Using Maskless Post-CMOS Processing. *IEEE Trans. Nanotechnol.* **2012**, *11*, 16–20. [CrossRef]

Sensors **2019**, 19, 4340 21 of 22

27. Prince, J.; Draper, B.; Rapp, E.; Kronberg, J.; Fitch, L. Performance of Digital Integrated Circuit Technologies at Very High Temperatures. *IEEE Trans. Compon. Hybrids Manuf. Technol.* **1980**, *3*, 571–579. [CrossRef]

- 28. Geis, M.W.; Spector, S.J.; Grein, M.E.; Schulein, R.T.; Yoon, J.U.; Lennon, D.M.; Deneault, S.; Gan, F.; Kaertner, F.X.; Lyszczarz, T.M. CMOS-Compatible All-Si High-Speed Waveguide Photodiodes With High Responsivity in Near-Infrared Communication Band. *IEEE Photonics Technol. Lett.* 2007, 19, 152–154. [CrossRef]

- 29. Nabki, F.; Dusatko, T.A.; Vengallatore, S.; El-Gamal, M.N. Low-Stress CMOS-Compatible Silicon Carbide Surface-Micromachining Technology—Part I: Process Development and Characterization. *J. Microelectromech. Syst.* **2011**, *20*, 720–729. [CrossRef]

- 30. Aasmundtveit, K.E.; Ta, B.Q.; Lin, L.; Halvorsen, E.; Hoivik, N. Direct integration of carbon nanotubes in Si microstructures. *J. Micromech. Microeng.* **2012**, 22, 74006. [CrossRef]

- 31. Haugen, B.T.; Ta, Q.B.; Halvorsen, E.; Hoivik, N.; Aasmundtveit, E.K. Integration of Carbon Nanotubes in Microsystems: Local Growth and Electrical Properties of Contacts. *Materials* **2013**, *6*, 3094–3107. [CrossRef]

- 32. Seichepine, F.; Rothe, J.; Dudina, A.; Hierlemann, A.; Frey, U. Dielectrophoresis–Assisted Integration of 1024 Carbon Nanotube Sensors into a CMOS Microsystem. *Adv. Mater.* **2017**, 29, 1606852. [CrossRef] [PubMed]

- 33. Piloto, C.; Mirri, F.; Bengio, E.A.; Notarianni, M.; Gupta, B.; Shafiei, M.; Pasquali, M.; Motta, N. Room temperature gas sensing properties of ultrathin carbon nanotube films by surfactant-free dip coating. *Sens. Actuators B Chem.* **2016**, 227, 128–134. [CrossRef]

- 34. Timmermans, M.Y.; Grigoras, K.; Nasibulin, A.G.; Hurskainen, V.; Franssila, S.; Ermolov, V.; Kauppinen, E.I. Lithography-free fabrication of carbon nanotube network transistors. *Nanotechnology* **2011**, 22, 65303. [CrossRef]

- 35. Lay, M.D.; Novak, J.P.; Snow, E.S. Simple Route to Large-Scale Ordered Arrays of Liquid-Deposited Carbon Nanotubes. *Nano Lett.* **2004**, *4*, 603–606. [CrossRef]

- 36. Hills, G.; Lau, C.; Wright, A.; Fuller, S.; Bishop, M.D.; Srimani, T.; Kanhaiya, P.; Ho, R.; Amer, A.; Stein, Y.; et al. Modern microprocessor built from complementary carbon nanotube transistors. *Nature* **2019**, 572, 595–602. [CrossRef] [PubMed]

- 37. Xie, H.; Zhou, Y. CMOS-CNT Integration. In *Encyclopedia of Nanotechnology*; Bhushan, B., Ed.; Springer: Heidelberg, Germany, 2012; pp. 449–456. ISBN 978-90-481-9751-4.

- 38. Rothe, J.; Frey, O.; Stettler, A.; Chen, Y.; Hierlemann, A. CMOS chip for electrochemical monitoring of the metabolic activity of biological cells. In Proceedings of the IEEE SENSORS Conference, Taipei, Taiwan, 28–31 October 2012; pp. 1–4.

- 39. Riverola, M.; Vidal-Álvarez, G.; Sobreviela, G.; Uranga, A.; Torres, F.; Barniol, N. Dynamic Properties of Three-Terminal Tungsten CMOS-NEM Relays Under Nonlinear Tapping Mode. *IEEE Sens. J.* **2016**, *16*, 5283–5291. [CrossRef]

- 40. Lakdawala, H.; Zhu, X.; Luo, H.; Santhanam, S.; Carley, L.R.; Fedder, G.K. Micromachined high-Q inductors in a 0.18-/spl mu/m copper interconnect low-k dielectric CMOS process. *IEEE J. Solid-State Circuits* **2002**, *37*, 394–403. [CrossRef]

- 41. Hickey, R.; Sameoto, D.; Hubbard, T.; Kujath, M. Time and frequency response of two-arm micromachined thermal actuators. *J. Micromech. Microeng.* **2003**, *13*, 40–46. [CrossRef]

- 42. Roy, A.; Ender, F.; Azadmehr, M.; Aasmundtveit, K.E. CMOS Micro-Heater Design for Direct Integration of Carbon Nanotubes. *Microelectron. Reliab.* **2017**, *79*, 517–525. [CrossRef]

- 43. Uranga, A.; Teva, J.; Verd, J.; Lopez, J.L.; Torres, F.; Esteve, J.; Abadal, G.; Perez-Murano, F.; Barniol, N. Fully CMOS integrated low voltage 100 MHz MEMS resonator. *Electron. Lett.* **2005**, *41*, 1327–1328. [CrossRef]

- 44. Fang, W.; Wickert, J.A. Post-buckling of micromachined beams. *J. Micromech. Microeng.* **1994**, *4*, 116–122. [CrossRef]

- 45. Ho, C.Y.; Ackerman, M.W.; Wu, K.Y.; Havill, T.N.; Bogaard, R.H.; Matula, R.A.; Oh, S.G.; James, H.M. Electrical resistivity of ten selected binary alloy systems. *J. Phys. Chem. Ref. Data* **1983**, 12, 183–322. [CrossRef]

- 46. Ho, C.Y.; Ackerman, M.W.; Wu, K.Y.; Oh, S.G.; Havill, T.N. Thermal conductivity of ten selected binary alloy systems. *J. Phys. Chem. Ref. Data* **1978**, *7*, 959–1178. [CrossRef]

- 47. Dey, G.K. Physical metallurgy of nickel aluminides. Sadhana 2003, 28, 247–262. [CrossRef]

- 48. Stoloff, N.S. Physical and mechanical metallurgy of Ni3Al and its alloys. *Int. Mater. Rev.* **1989**, *34*, 153–184. [CrossRef]

Sensors **2019**, 19, 4340 22 of 22

49. Deevi, S.C.; Sikka, V.K. Nickel and iron aluminides: An overview on properties, processing, and applications. *Intermetallics* **1996**, *4*, 357–375. [CrossRef]

- 50. Li, S.; Song, J.; Zhou, C.; Gong, S.; Han, Y. Microstructure evolution of NiCoCrAlY overlay coating for Ni3Al based alloy IC6 turbine vane during long term engine test. *Intermetallics* **2005**, *13*, 309–314. [CrossRef]

- 51. Burns, D.E.; Zhang, Y.; Teutsch, M.; Bade, K.; Aktaa, J.; Hemker, K.J. Development of Ni-based superalloys for microelectromechanical systems. *Scr. Mater.* **2012**, *67*, 459–462. [CrossRef]

- 52. Jozwik, P.; Polkowski, W.; Bojar, Z. Applications of Ni(3)Al Based Intermetallic Alloys—Current Stage and Potential Perceptivities. *Materials* **2015**, *8*, 2537–2568. [CrossRef]

- 53. Chun, D.H.; Xu, Y.; Demura, M.; Kishida, K.; Wee, D.M.; Hirano, T. Spontaneous catalytic activation of Ni3Al thin foils in methanol decomposition. *J. Catal.* **2006**, 243, 99–107. [CrossRef]

- 54. Ta, Q.B.; Haugen, B.T.; Hoivik, N.; Halvorsen, E.; Aasmundtveit, E.K. Local Synthesis of Carbon Nanotubes in Silicon Microsystems: The Effect of Temperature Distribution on Growth Structure. *Materials* **2013**, *6*, 3160–3170. [CrossRef] [PubMed]

- 55. Ta, B.Q.; Halvorsen, E.; Hoivik, N.; Aasmundtveit, K.E. Diameter dependency for the electric-field-assisted growth of carbon nanotubes. *Appl. Phys. Lett.* **2013**, *103*, 123102. [CrossRef]

- 56. Roy, A.; Ender, P.; Azadmehr, M.; Ta, B.Q.; Aasmundtveit, K.E. Design considerations of CMOS micro-heaters to directly synthesize carbon nanotubes for gas sensing applications. In Proceedings of the IEEE 17th International Conference on Nanotechnology (IEEE-NANO), Pittsburgh, PA, USA, 25–28 July 2017; pp. 828–833.

- 57. Roy, A.; Azadmehr, M.; Häfliger, P.; Ta, B.Q.; Aasmundtveit, K.E. Direct Synthesis of Carbon Nanotubes in CMOS-Layout of Micro-heaters. In Proceedings of the IEEE 18th International Conference on Nanotechnology (IEEE-NANO), Cork, Ireland, 23–26 July 2018; pp. 1–4.

- 58. Aasmundtveit, K.E.; Ta, B.Q.; Nguyen, Q.-H.; Haugen, T.B.; Hoivik, N.; Halvorsen, E. Local synthesis of carbon nanotubes for direct integration in Si microsystems—design considerations. *Adv. Manuf.* **2013**, *1*, 218–225. [CrossRef]

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).