A Novel Topology of Hybrid HVDC Circuit Breaker for VSC-HVDC Application

Abstract

:1. Introduction

- A topology of HCB based on the thyristor technique is proposed to reduce the realization cost and on-state loss. The bidirectional HCB is designed to interrupt the fault current in both directions by using silicon-controlled rectifier (SCR) devices. The polarity of pre-charged capacitor in the proposed topology is independent on the direction of the fault, which results in the reduction of the interruption time in the case of bidirectional fault current interruption. As a result, it can be used in the VSC-HVDC grid due to lower fault current interruption time. Besides, the proposed topology is capable of the reclosing and rebreaking operations without an auxiliary power supply, which results in the cost reduction.

- A switching control algorithm for the proposed HCB model to operate in different modes, such as normal, breaking, discharging, and reversing modes, is proposed. The algorithm represents sufficiently detailed protection sequence among the operation modes. The closing and opening operations of thyristors and switches detect and control accurately in case of normal and fault conditions.

2. Proposed HCB and Operation Principle

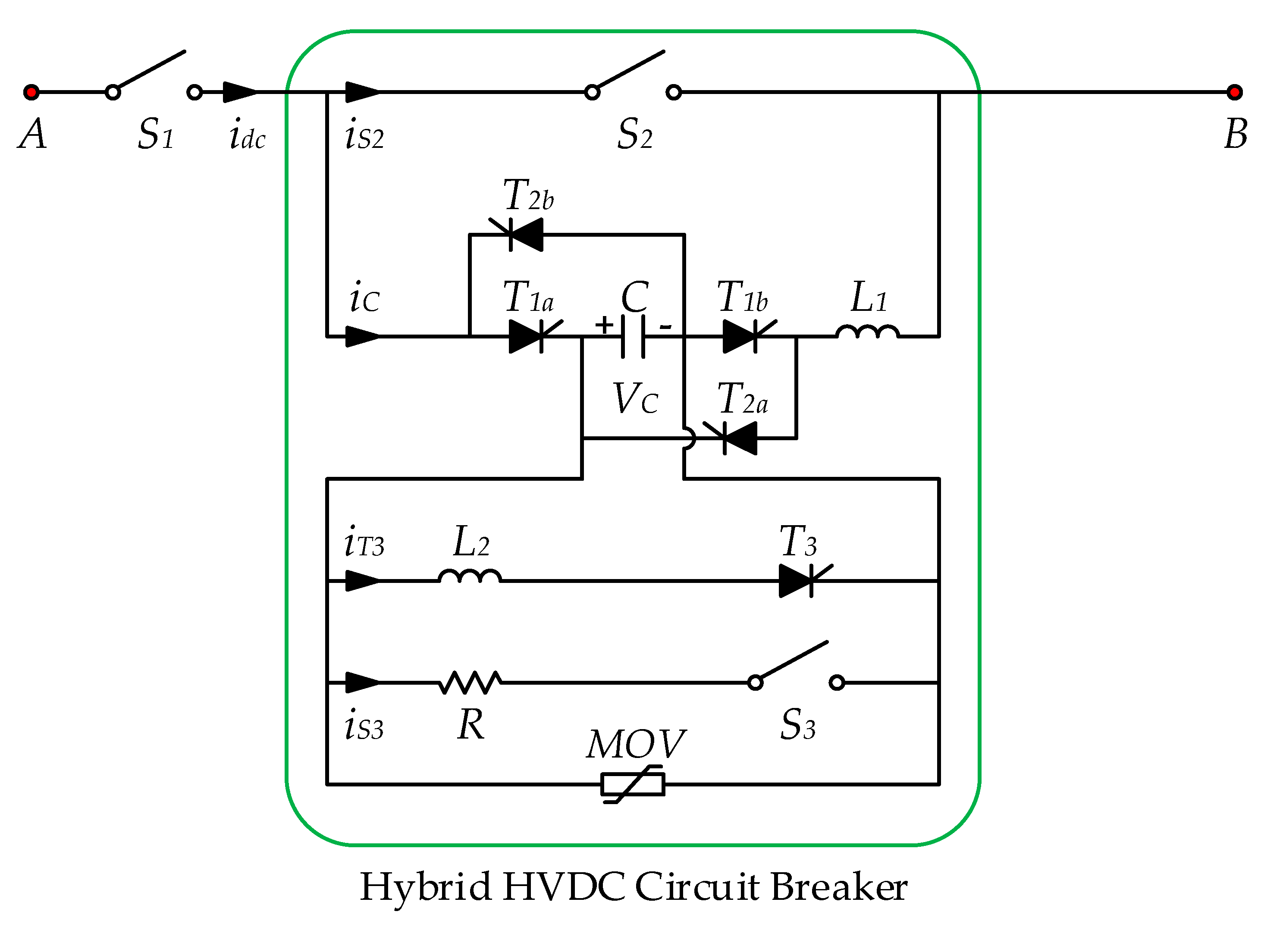

2.1. Configuration of Proposed Topology

2.2. Operation Principle

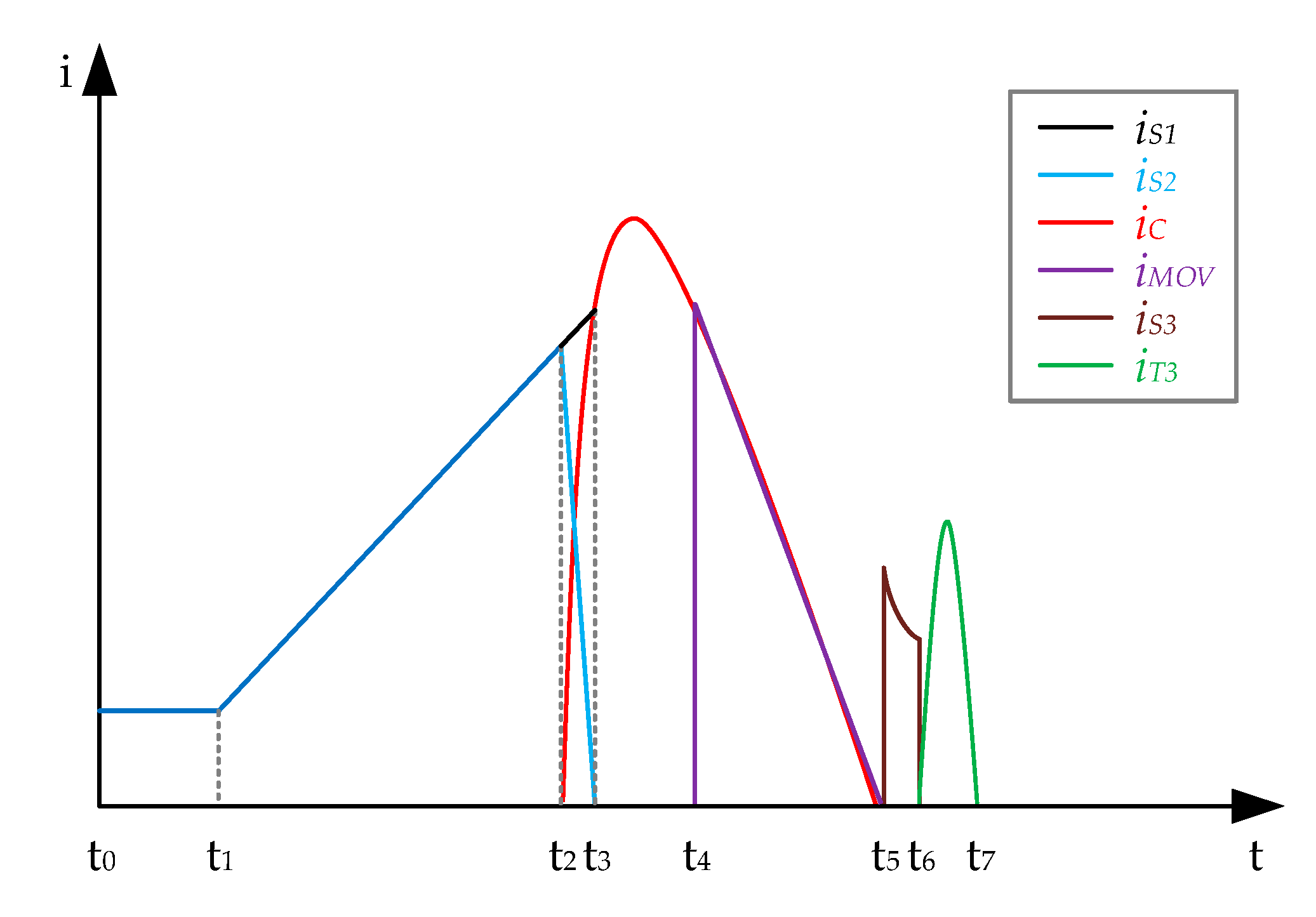

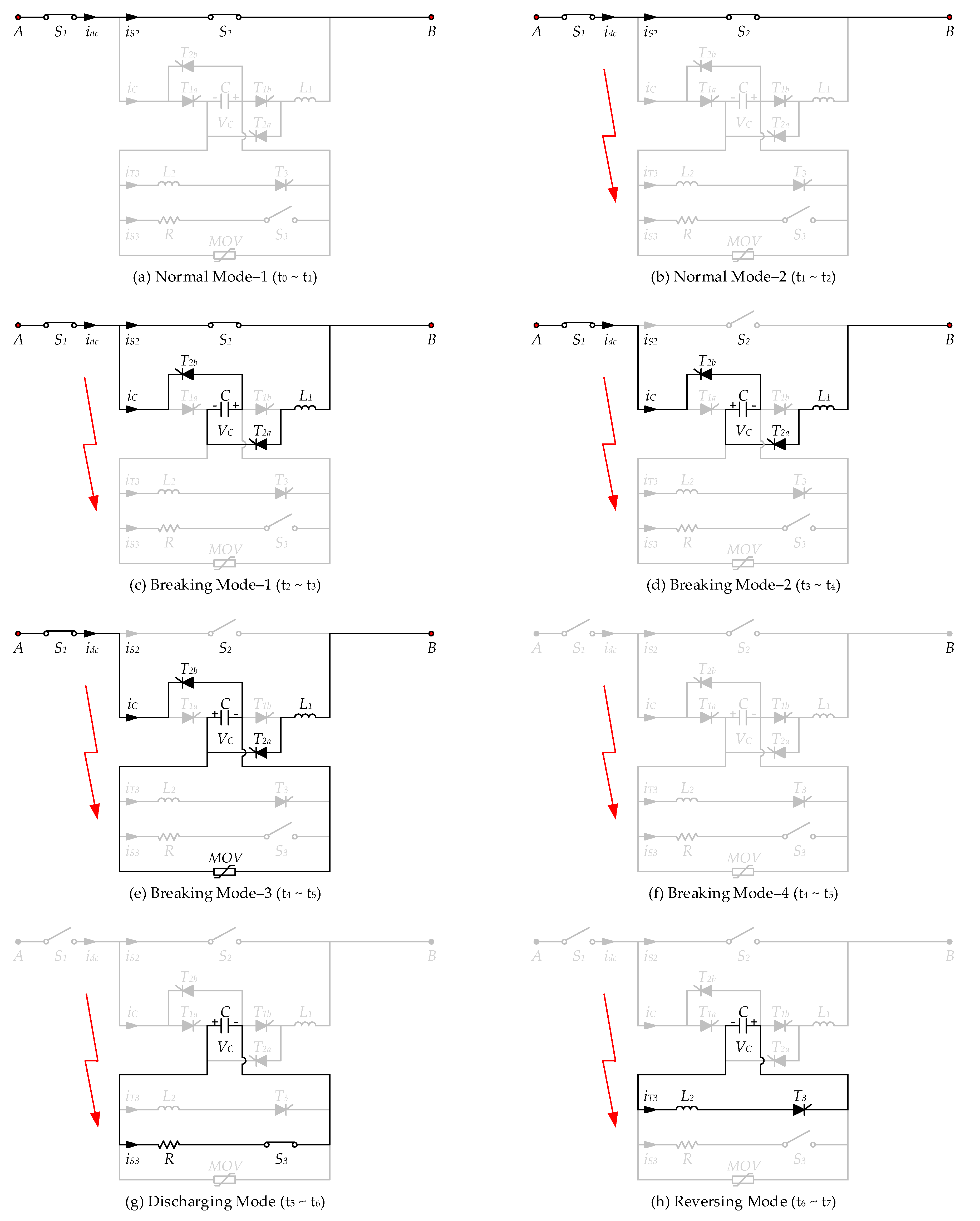

2.2.1. Normal Mode (t0~t2)

2.2.2. Breaking Mode (t2~t5)

2.2.3. Discharging Mode (t5~t6)

2.2.4. Reversing Mode (t6~t7)

2.3. Design Parameters

2.3.1. Design of Auxiliary Branch with L1-C

2.3.2. Design of Auxiliary Branches with R and L2

2.3.3. Design of Energy Absorbing Branch

3. Switching Control Algorithm for Proposed HCB

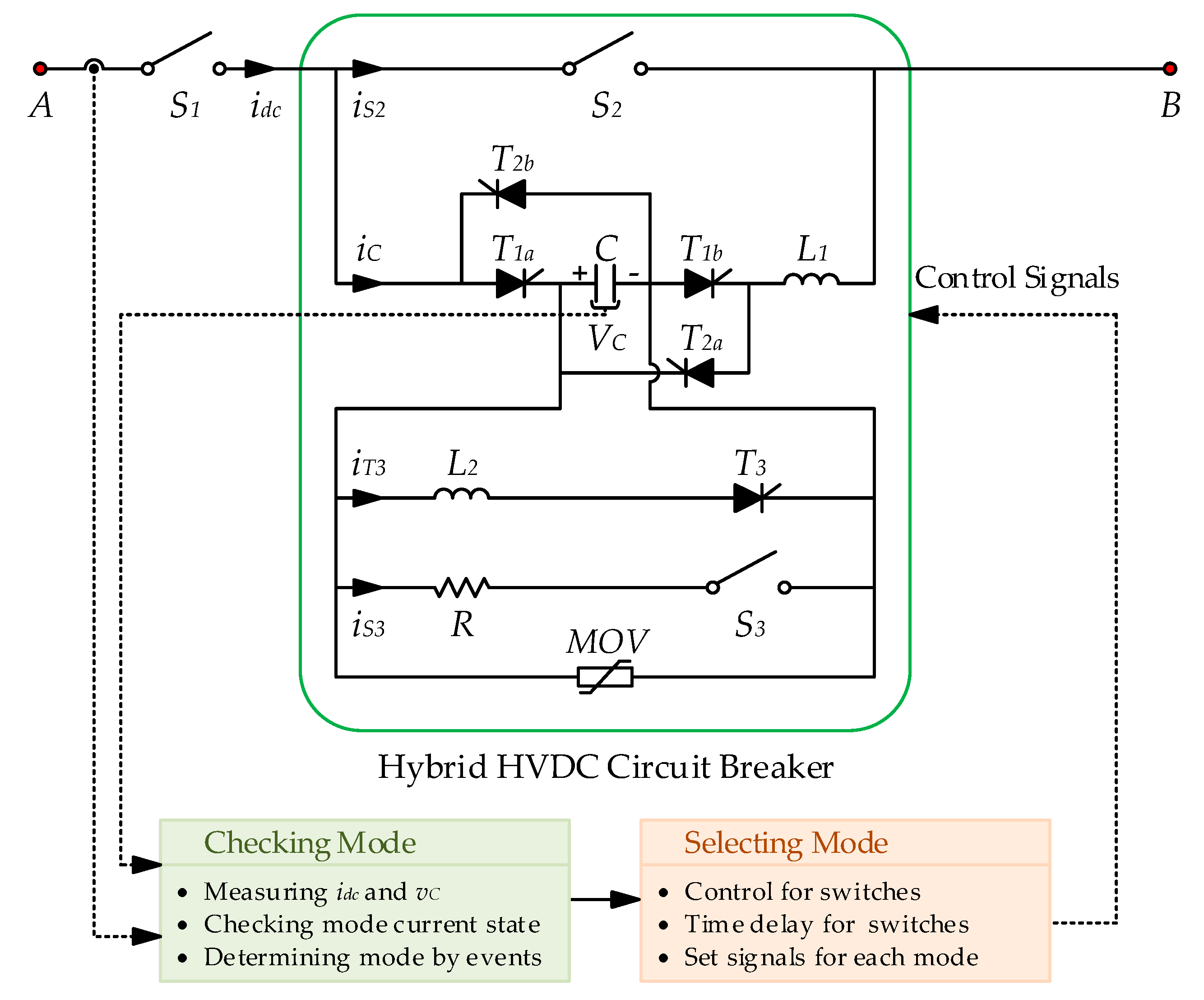

3.1. Outline of the Switching Control Algorithm

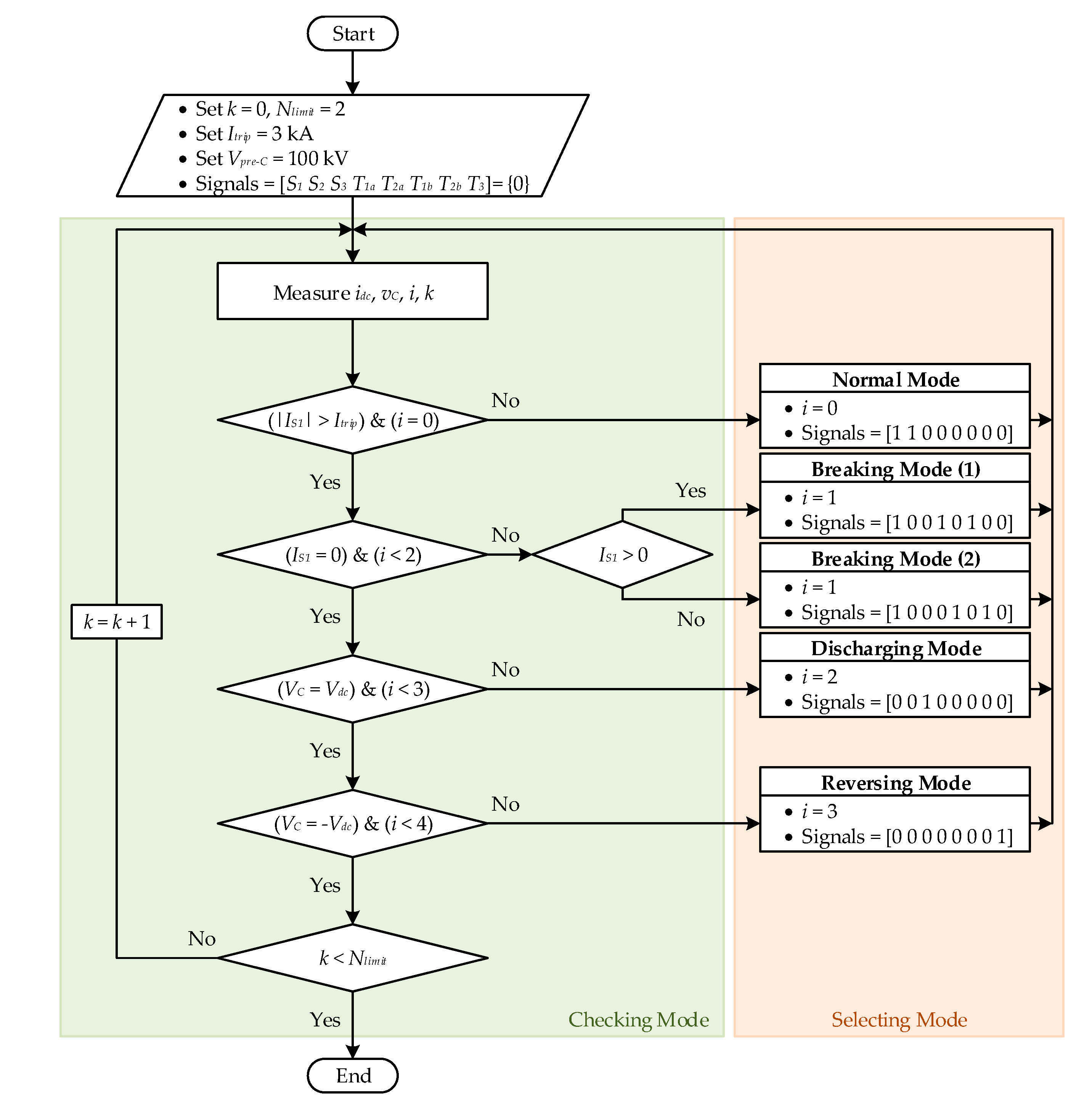

3.2. Flowchart of the Switching Control Algorithm

- Initially, the number of the operation of HCB and the threshold for detecting the fault are determined. After closing HCB in the normal mode, the control system checks the operation mode of the HCB by measuring the DC line current and capacitor voltage.

- If the magnitude of the DC line current is higher than the predefined threshold, the fault is detected and the direction of the fault current is determined (positive or negative). At the same time, the proper breaking mode is selected according to the direction of the fault current. For example, the breaking mode is active by turning on the thyristors (T1a and T1b) for the forward direction and the thyristors (T2a and T2b) for the reverse direction. The breaking mode is kept until the DC line current is dropped to zero.

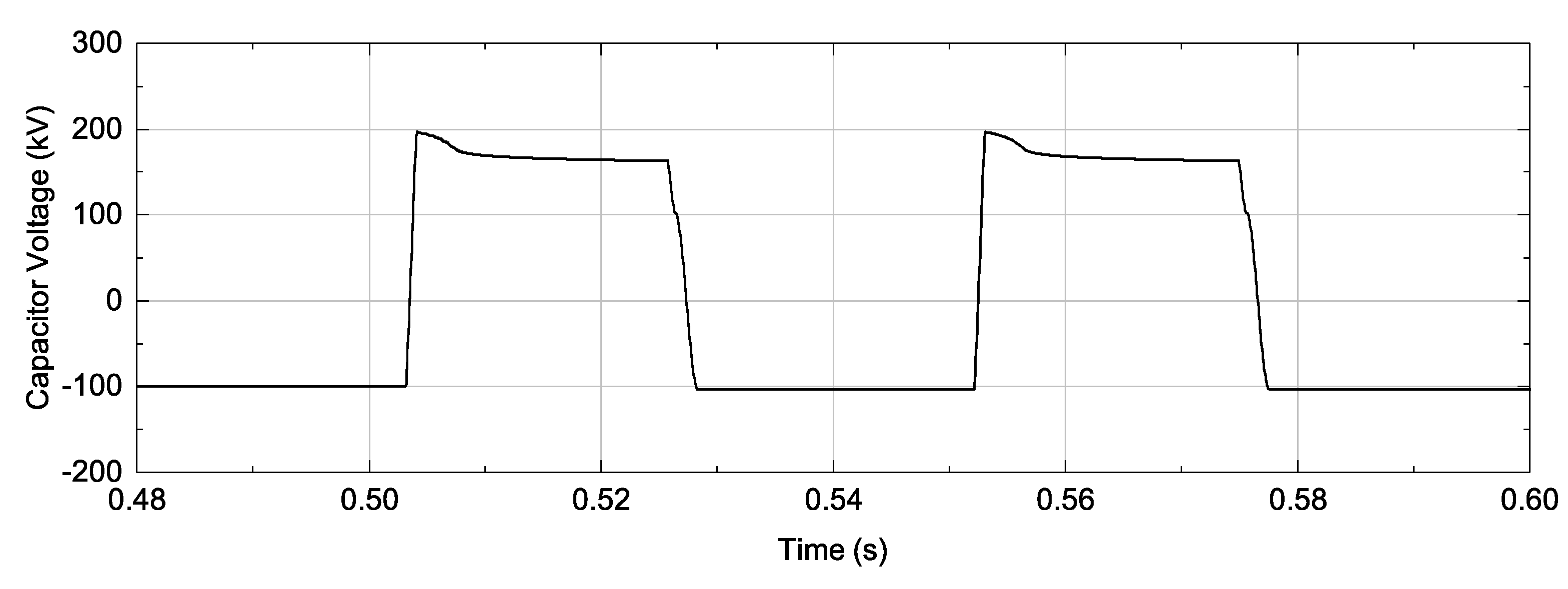

- The DC line can be isolated by the HCB after the breaking mode. Considering the reclosing operation of the HCB, the capacitor voltage is checked whether the magnitude and polarity is same with the pre-charged voltage. If capacitor voltage is not equal to the pre-charged value, the capacitor voltage is controlled by the discharging mode and reversing mode.

- The HCB can be reclosed shortly after the reversing mode is passed. However, the number of the reclosing the HCB can be restricted by operating sequence: open–close/open–close/open (O–CO–CO) [25].

4. Simulation Results

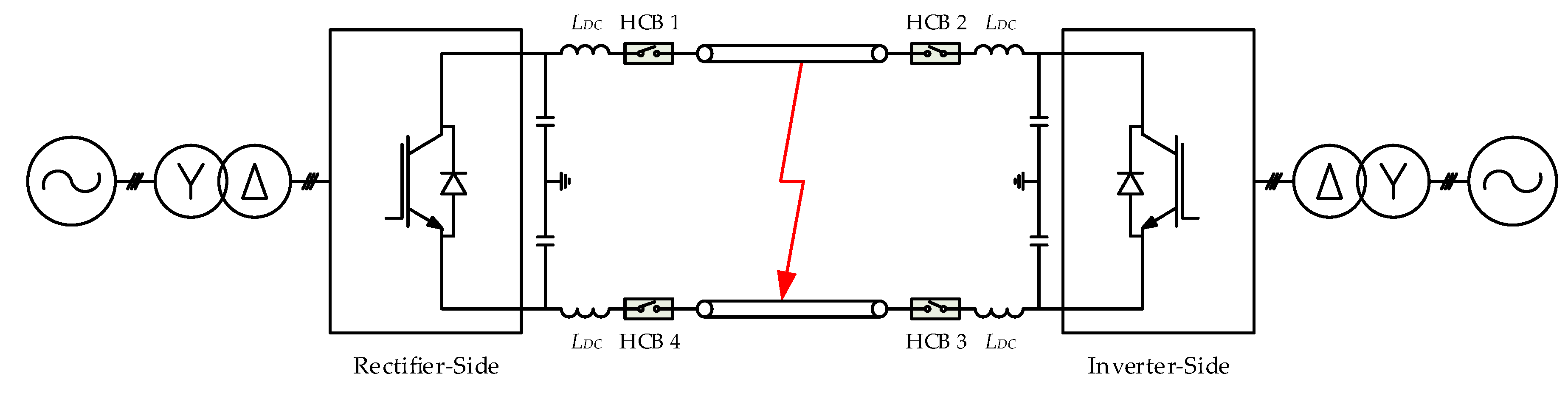

4.1. Test System for Case Studies

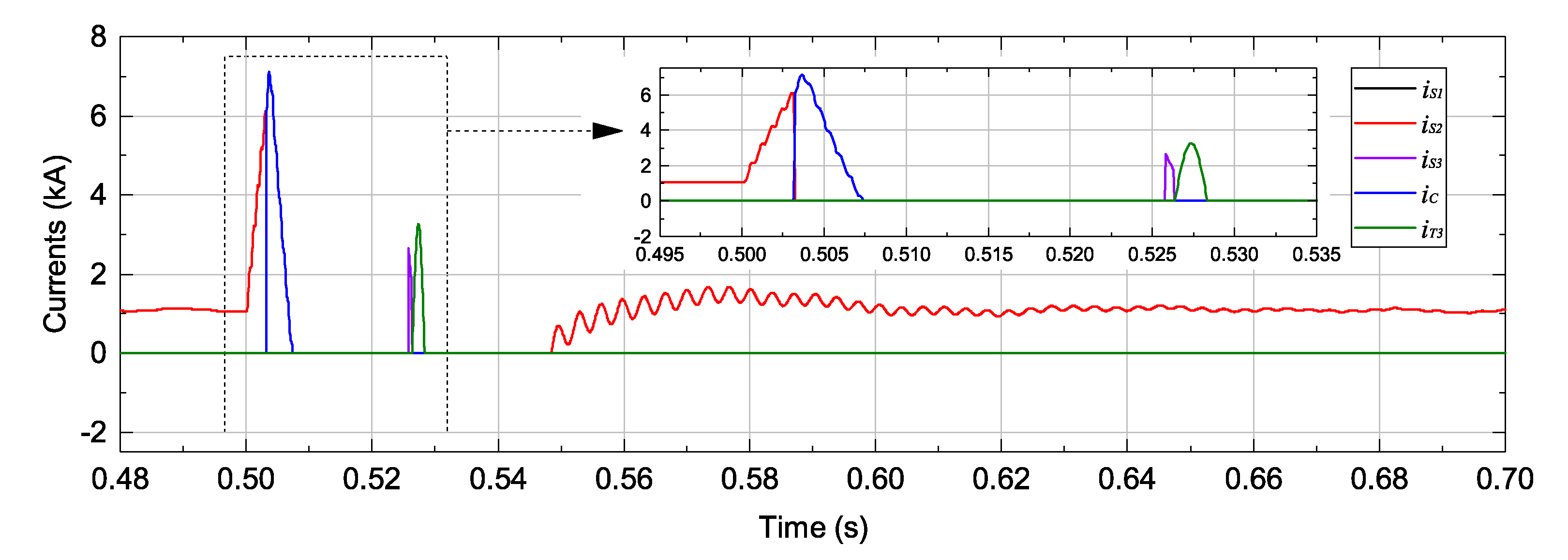

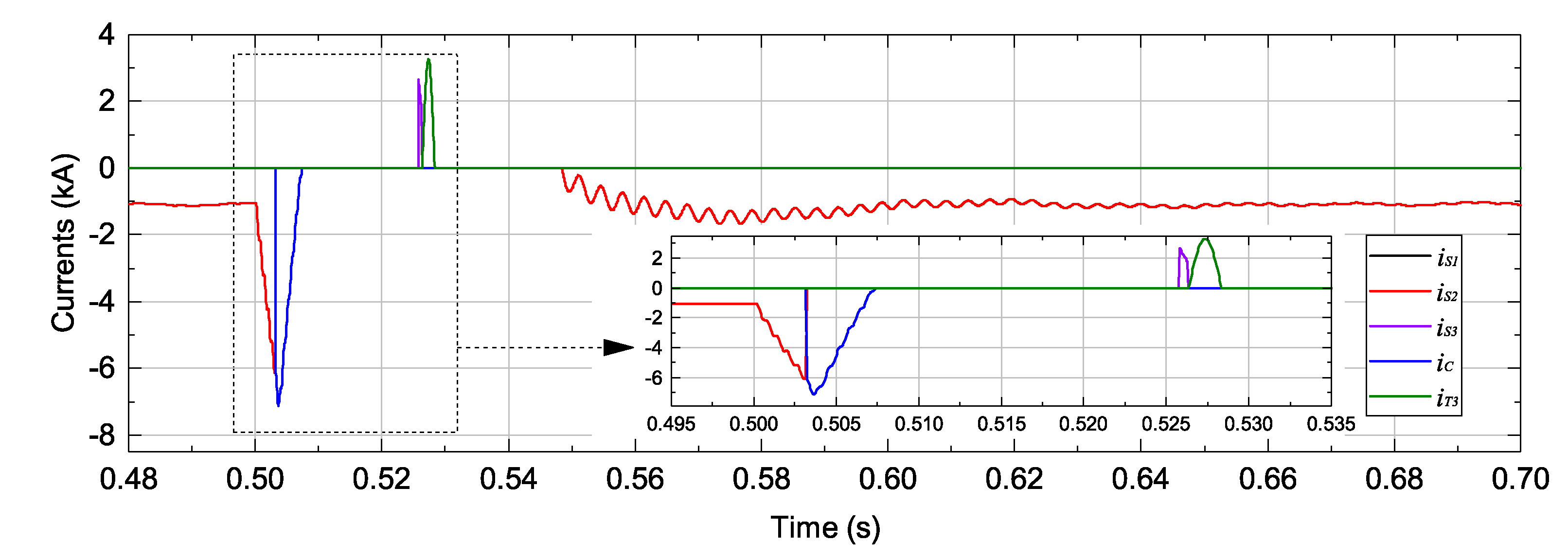

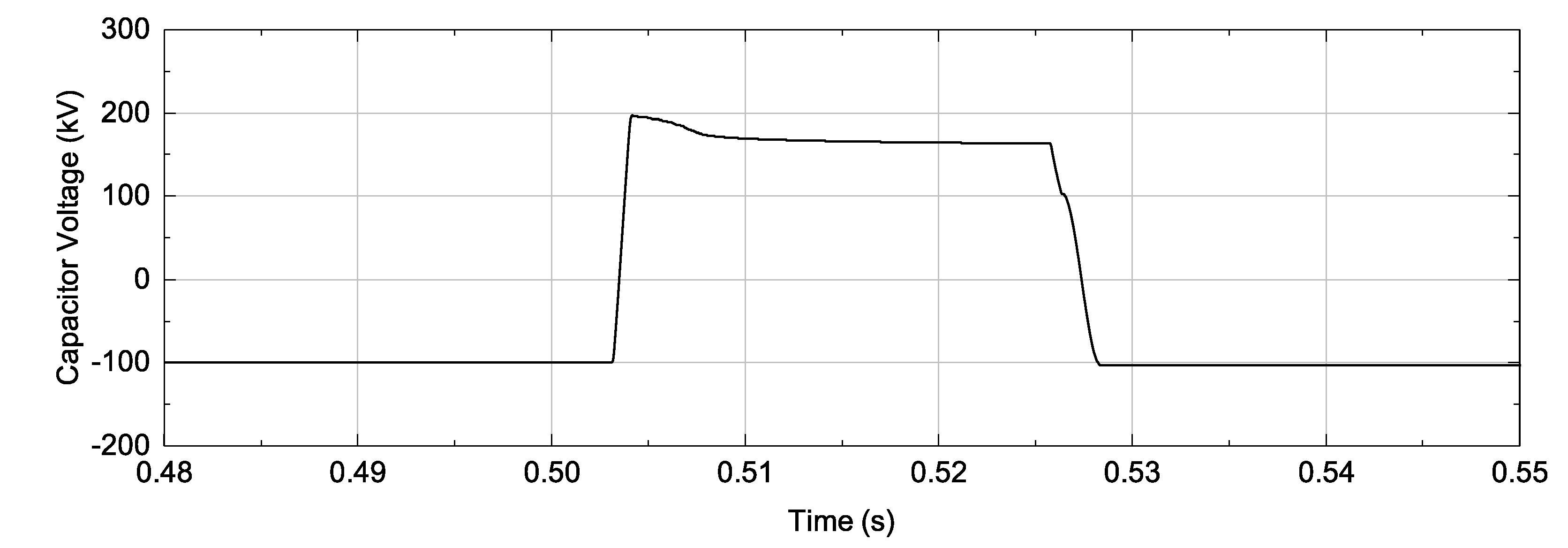

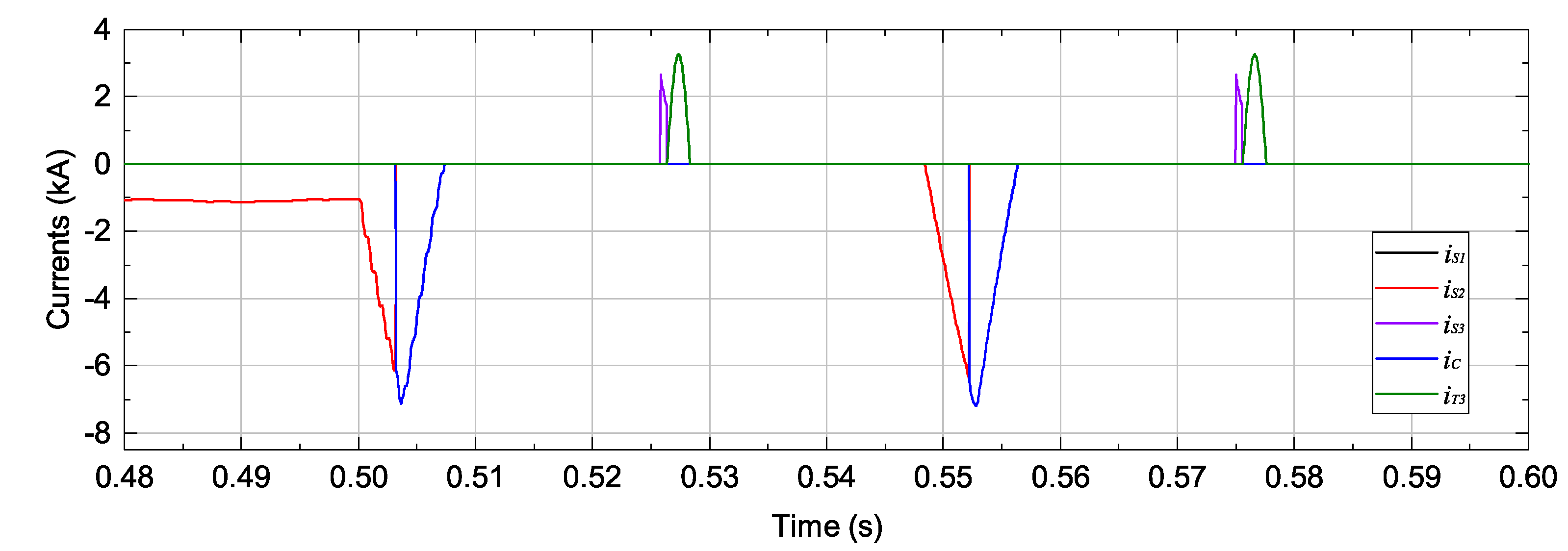

4.2. Temporary Fault on DC Line

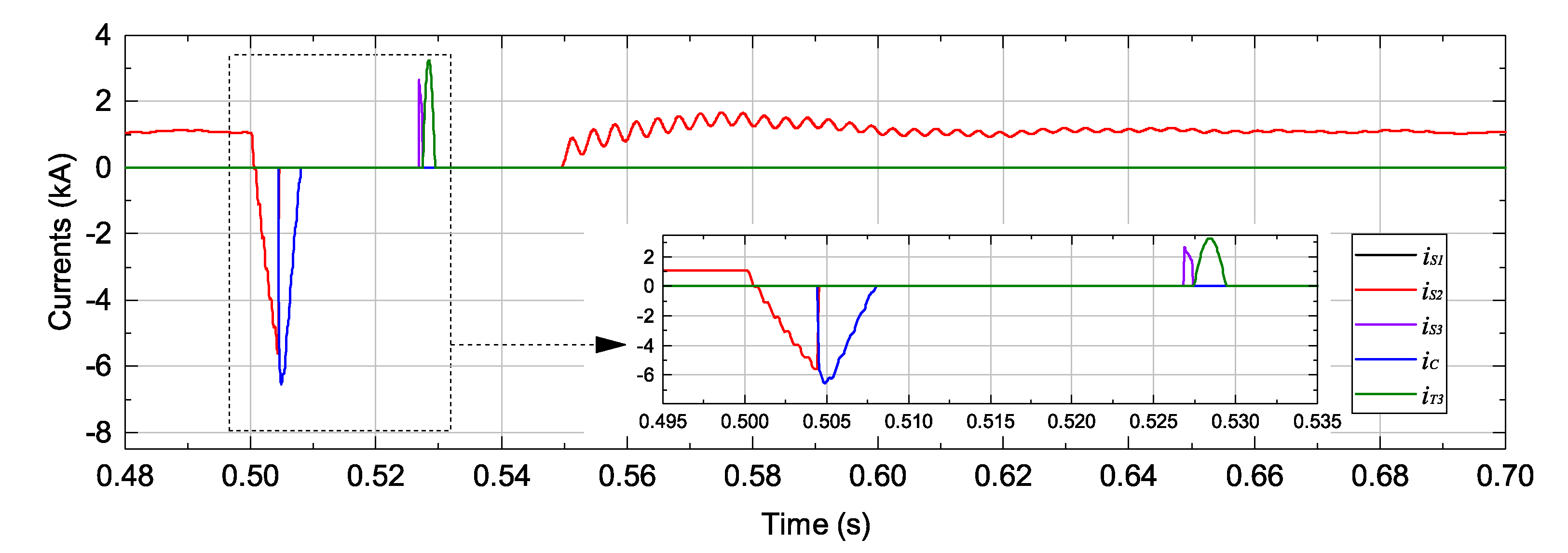

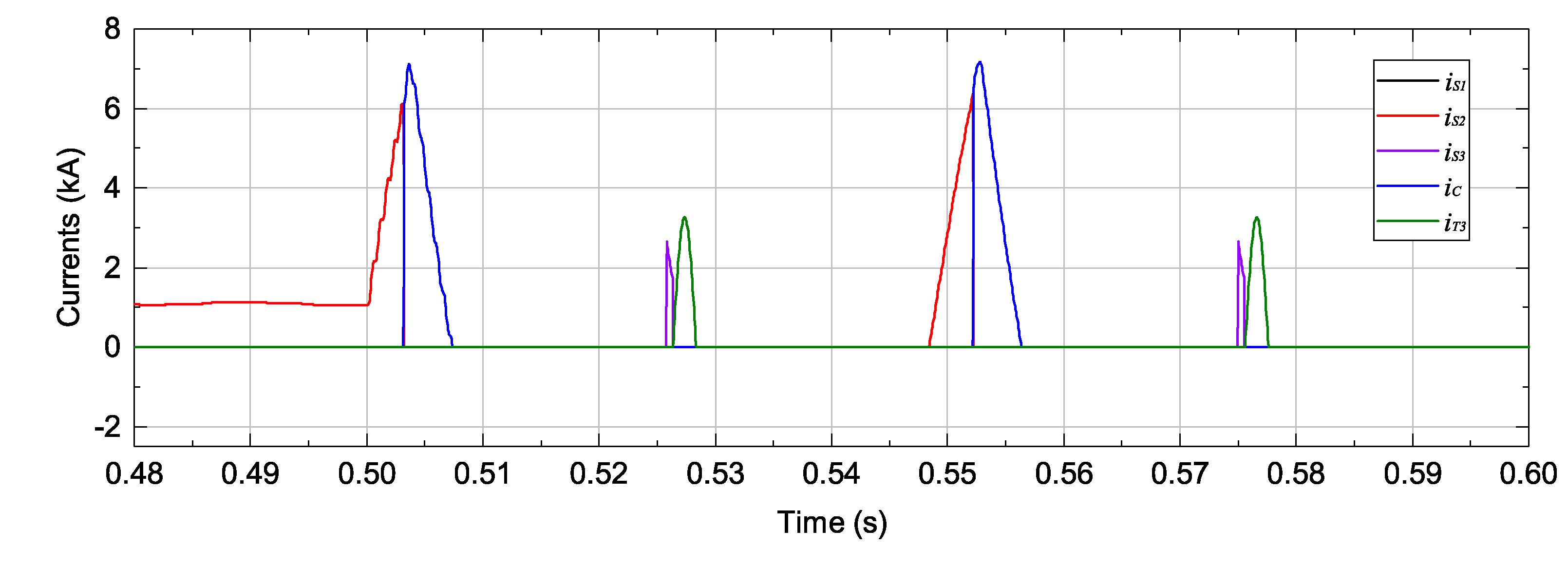

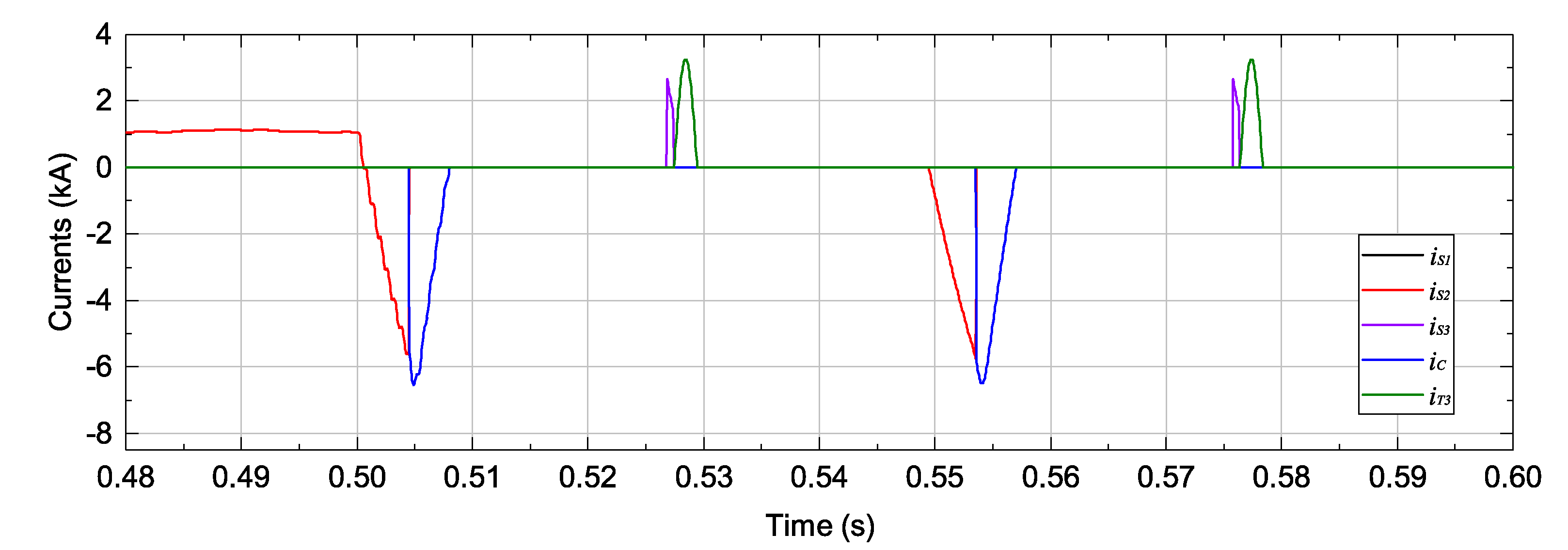

4.3. Permanent Fault on DC Line

5. Conclusions

Acknowledgments

Author Contributions

Conflicts of Interest

References

- Greenwood, A.; Kanngiessner, K.; Lesclae, V.; Margaard, T.; Schultz, W. Circuit breakers for meshed multiterminal HVDC systems. Part I: Introduction DC side substation switching under normal and fault conditions. Electra 1995, 163, 98–122. [Google Scholar]

- Greenwood, A.; Kanngiessner, K.; Lesclae, V.; Margaard, T.; Schultz, W. Circuit breakers for meshed multiterminal HVDC systems. Part II: Switching of transmission lines in meshed MTDC systems. Electra 1996, 164, 62–82. [Google Scholar]

- Bergstrom, L.; Juhlin, L.E.; Liss, G.; Svensson, S. Simulator study of multiiterminal HVDC system performance. IEEE Trans. Power Appl. Syst. 1978, PAS-97, 2057–2066. [Google Scholar] [CrossRef]

- Kanngiesser, K.; Ring, H.; Wess, T. Simulator study on line fault clearing by DC circuit breakers in a meshed MTDC system. In Proceedings of the International Conference on AC and DC Power Transmission, London, UK, 17–20 September 1991; pp. 102–107. [Google Scholar]

- Franck, C.M. HVDC circuit breakers: A review identifying future research needs. IEEE Trans. Power Deliv. 2011, 26, 998–1007. [Google Scholar] [CrossRef]

- Chaffey, G.; Green, T.C. Reduced DC circuit breaker requirement on mixed converter HVDC networks. In Proceedings of the IEEE Eindhoven PowerTech, Eindhoven, The Netherlands, 29 June–2 July 2015; pp. 1–6. [Google Scholar]

- Saad, H.; Peralta, J.; Dennetiere, S.; Mahseredjian, J.; Jatskevich, J.; Martinez, J.; Davoudi, A.; Saeedifard, M.; Sood, V.; Wang, X.; et al. Dynamic averaged and simplified models for MMC-based HVDC transmission systems. IEEE Trans. Power Deliv. 2013, 28, 1723–1730. [Google Scholar] [CrossRef]

- Ekstrom, A.; Hartel, H.; Lips, H.; Schultz, W.; Joss, P.; Holfeld, H.; Kind, D. Design and Testing of an HVDC Circuit Breaker; CIGRE: Paris, France, 1976. [Google Scholar]

- Belda, N.A.; Smeets, R.P.P. Test circuits for HVDC circuit breakers. IEEE Trans. Power Deliv. 2017, 32, 285–293. [Google Scholar] [CrossRef]

- Ahmed, N. Efficient modeling of an MMC-based multiterminal DC system employing hybrid HVDC breakers. IEEE Trans. Power Deliv. 2015, 30, 1792–1801. [Google Scholar] [CrossRef]

- Sano, K.; Takasaki, M. A surgeless solid-state DC circuit breaker for voltage-source-converter-based HVDC systems. IEEE Trans. Ind. Appl. 2014, 50, 2690–2699. [Google Scholar] [CrossRef]

- Asplund, G. HVDC Grid Feasibility Study Working Group b4-52; CIGRE: Paris, France, 2013; pp. 56–65. [Google Scholar]

- Kim, J.Y.; Choi, S.S.; Kim, I.D. A new reclosing and re-breaking DC thyristor circuit breaker for DC distribution applications. J. Power Electron. 2017, 17, 272–281. [Google Scholar] [CrossRef]

- Mokhberdoran, A.; Carvalho, A.; Leite, H.; Silva, N. A review on HVDC circuit breakers. In Proceedings of the 3rd Renewable Power Generation Conference (RPG 2014), Naples, Italy, 24–25 September 2014; pp. 1–6. [Google Scholar]

- Shukla, A.; Demetriades, G.D. A survey on hybrid circuit-breaker topologies. IEEE Trans. Power Deliv. 2015, 30, 627–641. [Google Scholar] [CrossRef]

- Tokoyoda, S.; Sato, M.; Kamei, K.; Yoshida, D.; Miyashita, M.; Kikuchi, K.; Ito, H. High frequency interruption characteristics of VCB and its application to high voltage DC circuit breaker. In Proceedings of the 2015 3rd International Conference on Electric Power Equipment; Switching Technology (ICEPE-ST), Busan, Korea, 25–28 October 2015; pp. 117–121. [Google Scholar]

- Corzine, K.A. A new-coupled-inductor circuit breaker for DC applications. IEEE Trans. Power Electron. 2017, 32, 1411–1418. [Google Scholar] [CrossRef]

- Keshavarzi, D.; Ghanbari, T.; Farjah, E. A Z-source based bidirectional DC circuit breaker with fault current limitation and interruption capabilities. IEEE Trans. Power Electron. 2017, 32, 6813–6822. [Google Scholar] [CrossRef]

- Maqsood, A.; Overstreet, A.; Corzine, K.A. Modified Z-source DC circuit breaker topologies. IEEE Trans. Power Electron. 2016, 31, 7394–7403. [Google Scholar] [CrossRef]

- Mokhberdoran, A.; Carvalho, A.; Silva, N.; Leite, H.; Carrapatoso, A. A new topology of fast solid-state HVDC circuit breaker for offshore wind integration applications. In Proceedings of the 17th European Conference on Power Electronics and Applications (EPE’15 ECCE-Europe), Geneva, Switzerland, 8–10 September 2015; pp. 1–10. [Google Scholar]

- Hafner, J.; Jacobson, B. Proactive hybrid HVDC breakers—A key innovation for reliable HVDC grids. In Proceedings of the Electric Power System of the Future—Integrating Supergrids and Microgrids International Symposium, Bologna, Italy, 13–15 September 2011; pp. 1–9. [Google Scholar]

- Lin, W.; Jovcic, D.; Nguefeu, S.; Saad, H. Modelling of high-power hybrid DC circuit breaker for grid-level studies. IET Power Electron. 2016, 9, 237–246. [Google Scholar] [CrossRef]

- Liu, G.; Xu, F.; Xu, Z.; Zhang, Z.; Tang, G. Assembly HVDC breaker for HVDC grids with modular multilevel converters. IEEE Trans. Power Electron. 2017, 32, 931–941. [Google Scholar] [CrossRef]

- Feng, L. A 320 kV hybrid HVDC circuit breaker based on thyristors forced current zero technique. In Proceedings of the IEEE Applied Power Electronics Conference and Exposition (APEC), Tampa, FL, USA, 26–30 March 2017; pp. 384–390. [Google Scholar]

- Kim, B.C.; Chung, Y.H.; Hwang, H.D.; Mok, H.S. Comparison of inverse current injecting HVDC curcuit breaker. In Proceedings of the 3rd International Conference on Electric Power Equipment–Switching Technology (ICEPE-ST), Busan, Korea, 25–28 October 2015; pp. 501–505. [Google Scholar]

- Khan, U.A. A novel model of HVDC hybrid-type superconducting circuit breaker and its performance analysis for limiting and breaking DC fault currents. IEEE Trans. Appl. Supercond. 2015, 25, 5603009. [Google Scholar] [CrossRef]

- Lee, J.G.; Khan, U.A.; Lee, H.Y.; Lee, B.W. Impact of SFCL on the four types of HVDC circuit breakers by simulation. IEEE Trans. Appl. Supercond. 2016, 26, 5602606. [Google Scholar] [CrossRef]

| Positive Currents | ||||||||

| Modes | S1 | S2 | S3 | T1a | T2a | T1b | T2b | T3 |

| Normal Mode | 1 a | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| Breaking Mode | 1 | 0 | 0 | 1 | 0 | 1 | 0 | 0 |

| Discharging Mode | 0 b | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| Reversing Mode | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| Negative Currents | ||||||||

| Modes | S1 | S2 | S3 | T1a | T2a | T1b | T2b | T3 |

| Normal Mode | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| Breaking Mode | 1 | 0 | 0 | 0 | 1 | 0 | 1 | 0 |

| Discharging Mode | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| Reversing Mode | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| Parameters | Symbol | Specifications |

|---|---|---|

| Capacitor | C | 20 µF |

| Inductance 1 | L1 | 1 mH |

| Inductance 2 | L2 | 20 mH |

| Resistance | R | 60 Ω |

| Time delay of residual switch | TS1 | 20 ms |

| Time delay of mechanical switch | TS2 | 2 ms |

© 2017 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Nguyen, V.-V.; Son, H.-I.; Nguyen, T.-T.; Kim, H.-M.; Kim, C.-K. A Novel Topology of Hybrid HVDC Circuit Breaker for VSC-HVDC Application. Energies 2017, 10, 1675. https://doi.org/10.3390/en10101675

Nguyen V-V, Son H-I, Nguyen T-T, Kim H-M, Kim C-K. A Novel Topology of Hybrid HVDC Circuit Breaker for VSC-HVDC Application. Energies. 2017; 10(10):1675. https://doi.org/10.3390/en10101675

Chicago/Turabian StyleNguyen, Van-Vinh, Ho-Ik Son, Thai-Thanh Nguyen, Hak-Man Kim, and Chan-Ki Kim. 2017. "A Novel Topology of Hybrid HVDC Circuit Breaker for VSC-HVDC Application" Energies 10, no. 10: 1675. https://doi.org/10.3390/en10101675