Characterization of the Diamond Wire Sawing Process for Monocrystalline Silicon by Raman Spectroscopy and SIREX Polarimetry

Abstract

:1. Introduction

2. Materials and Methods

2.1. Sample Description

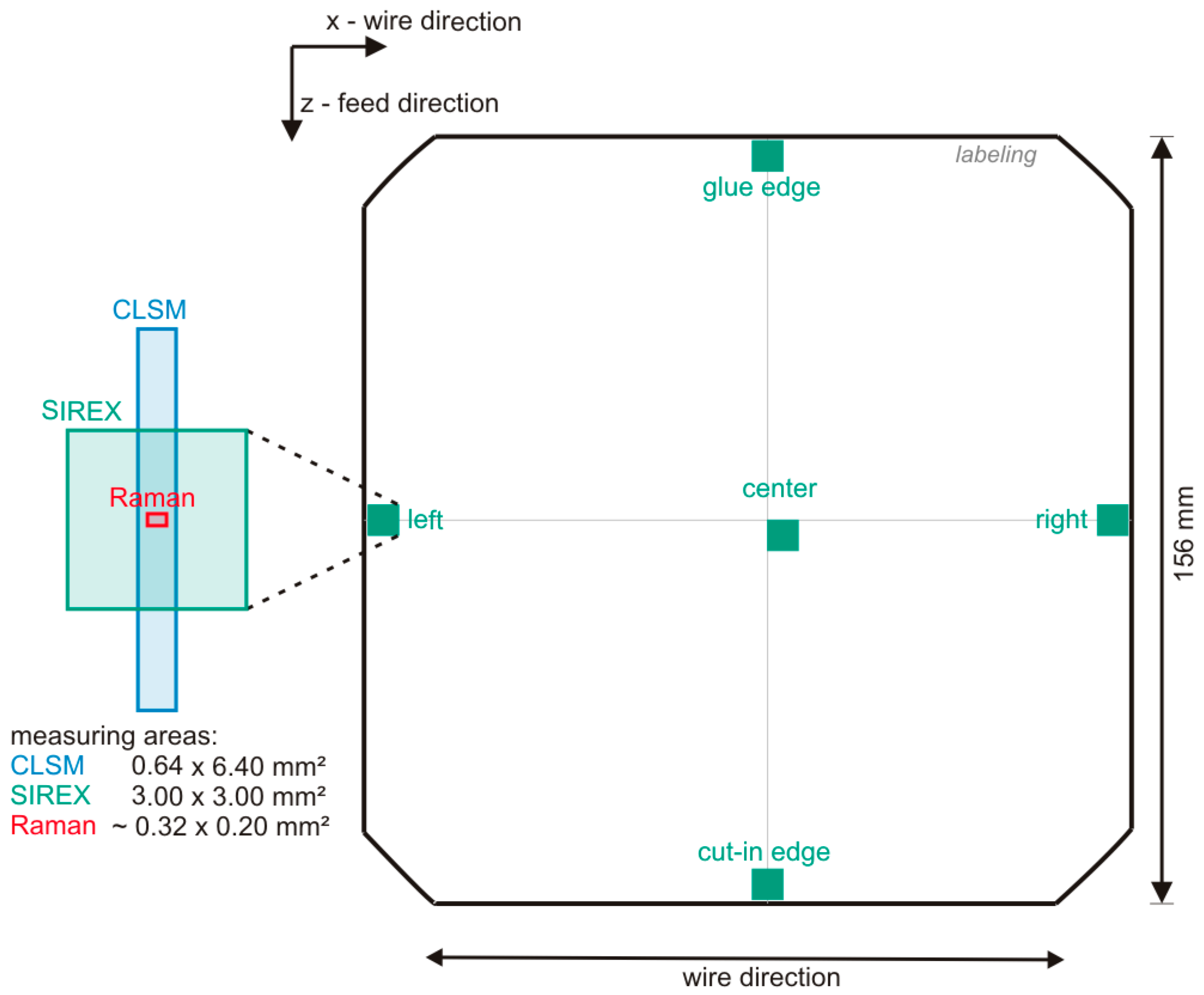

2.2. Measurement Procedure

2.2.1. Raman Spectroscopy

2.2.2. SIREX Polarimetry

2.2.3. Confocal Laser Scanning Microscopy

3. Experimental Results and Discussion

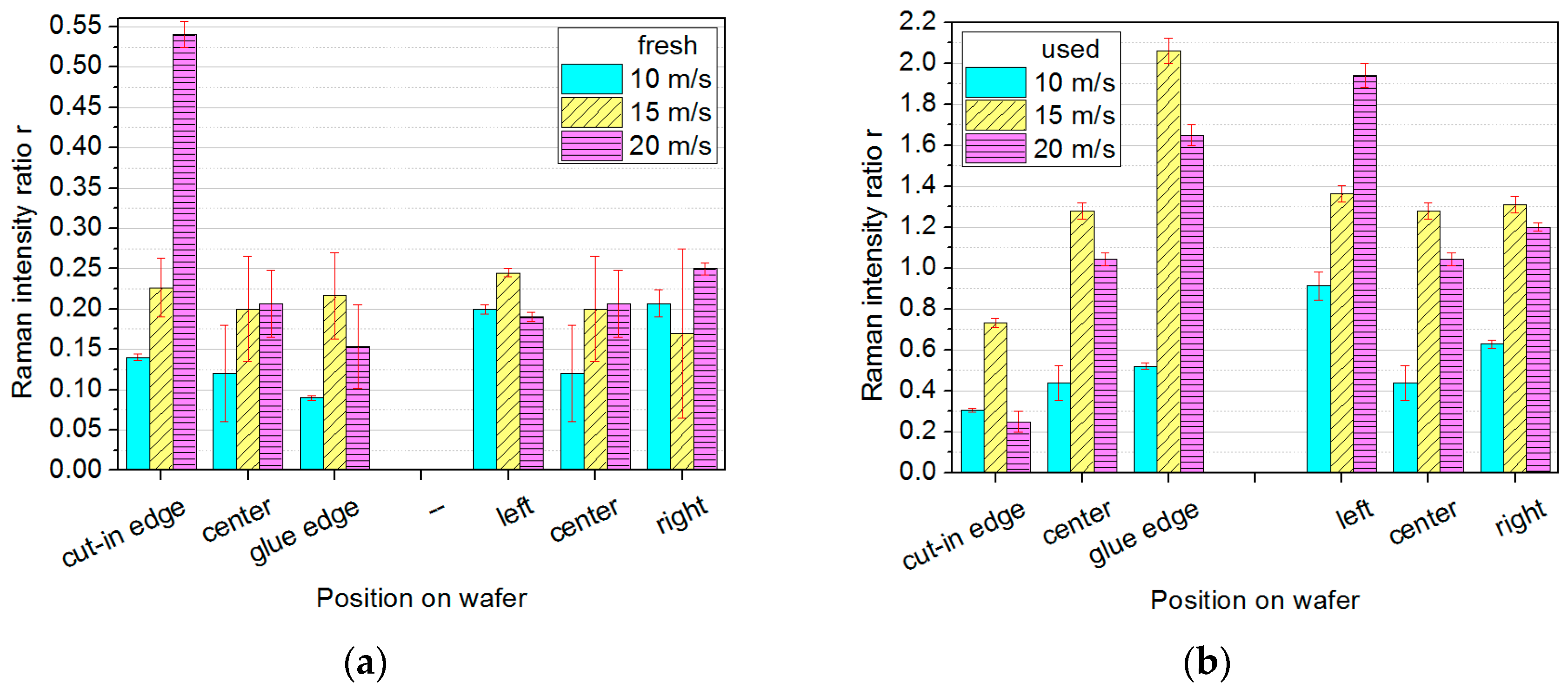

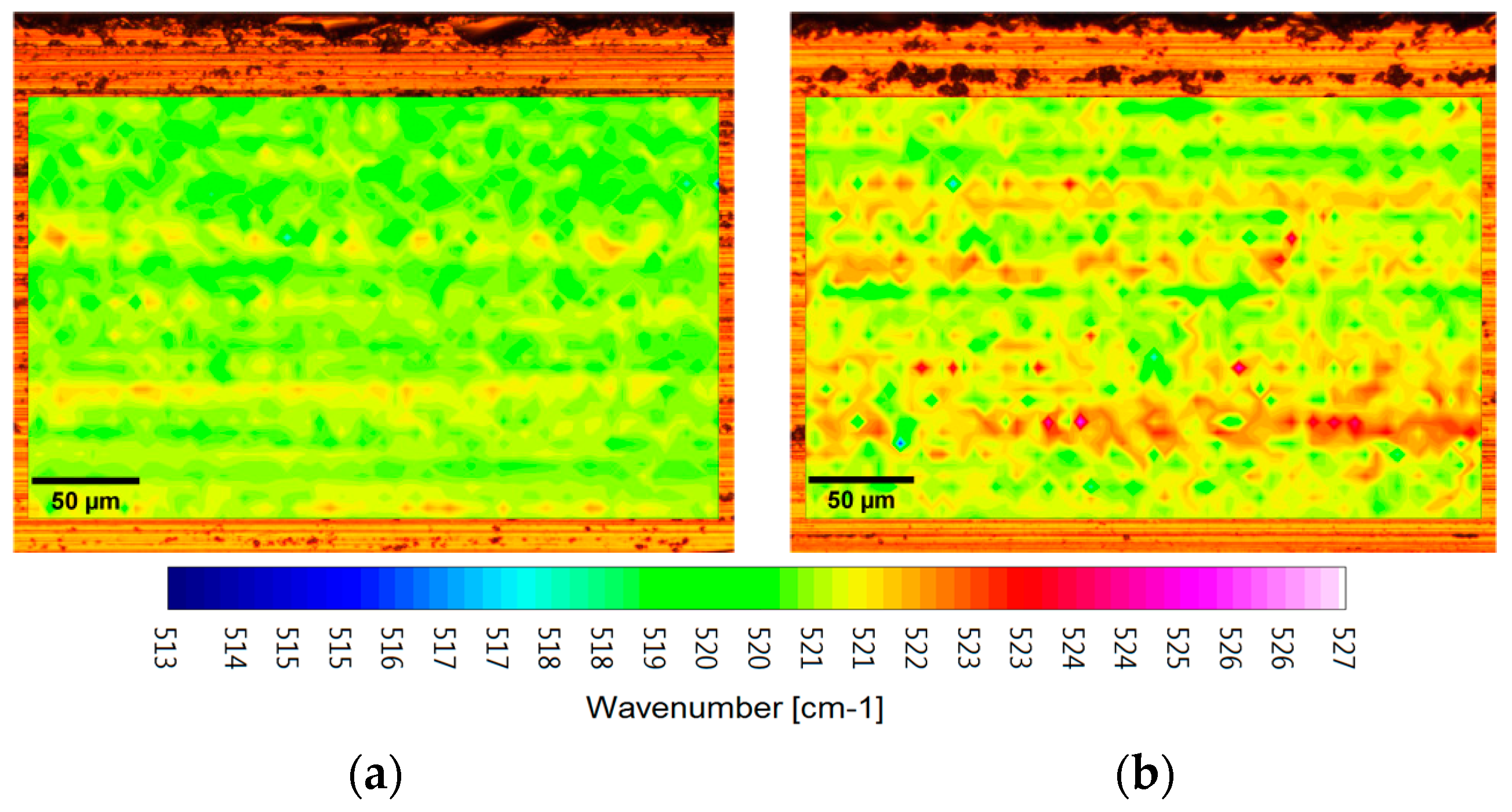

3.1. Investigation of Surface Amorphization and Material Stresses with Raman

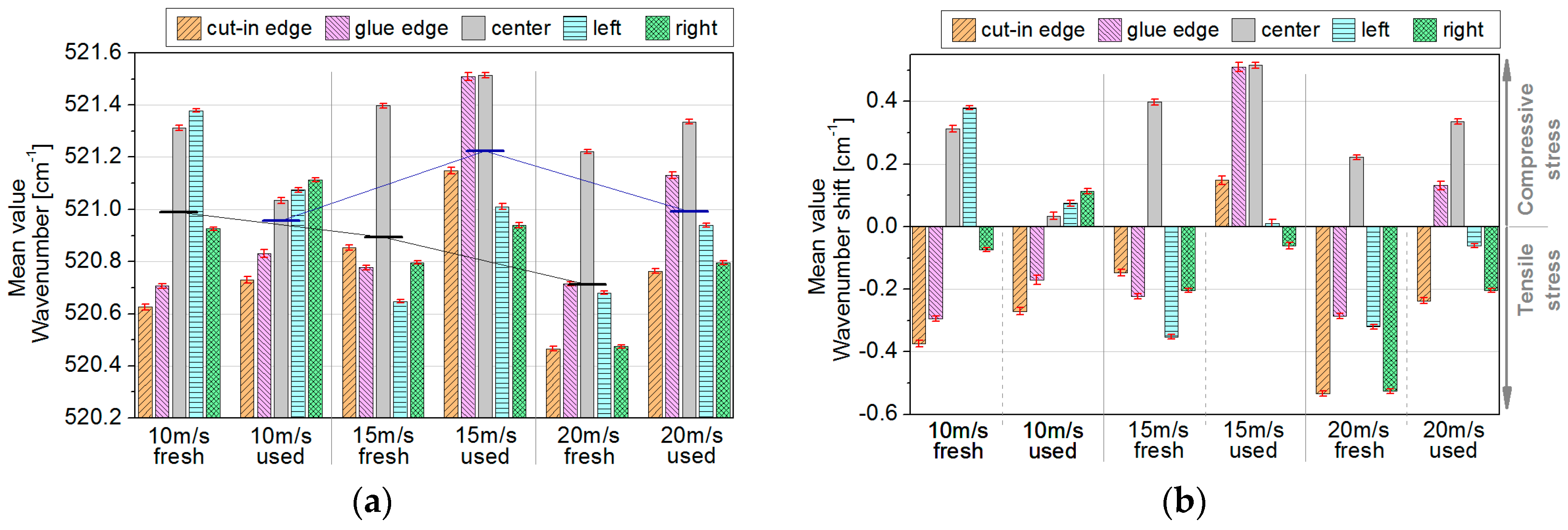

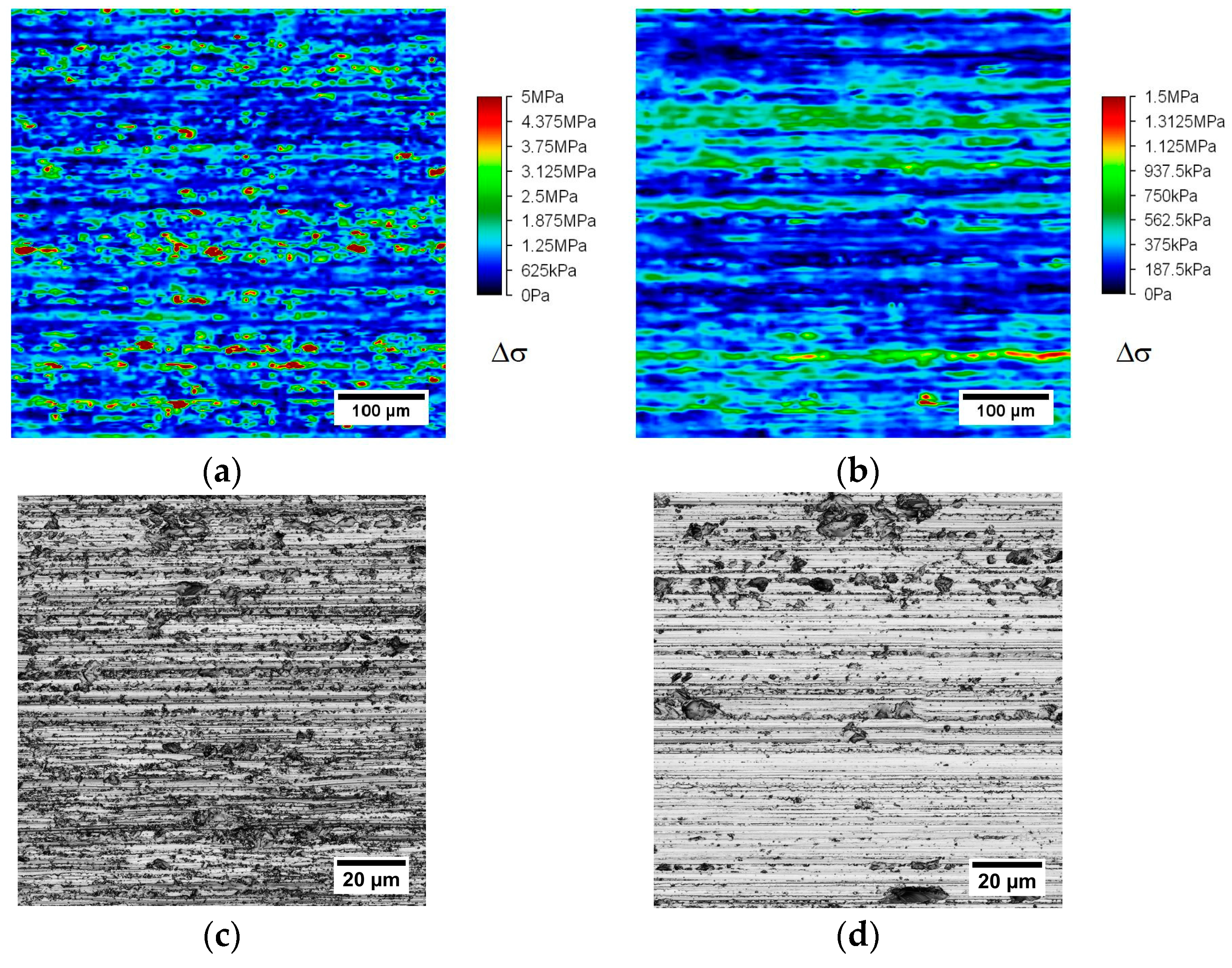

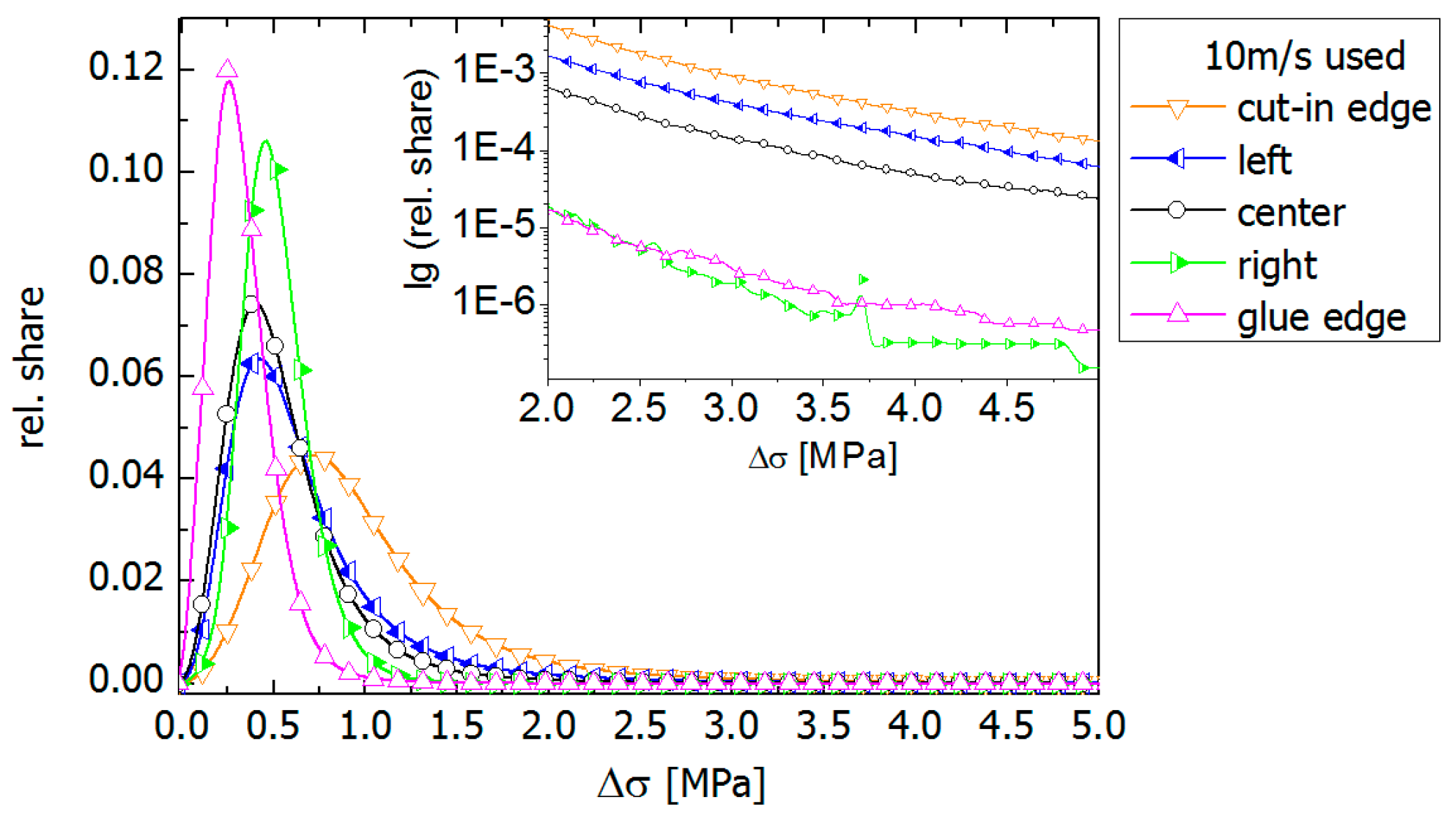

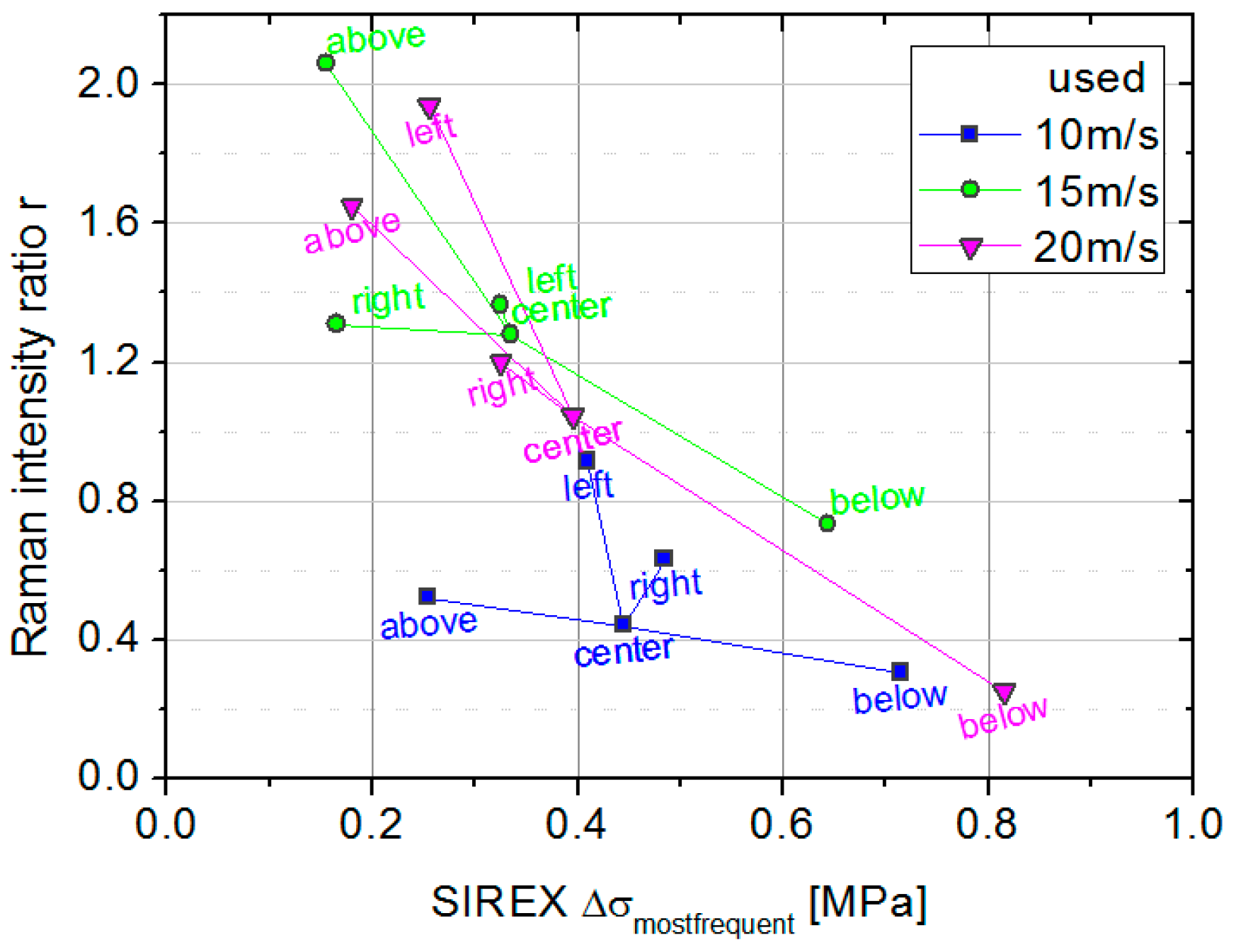

3.2. Characterization of Sub-Surface Stresses with SIREX

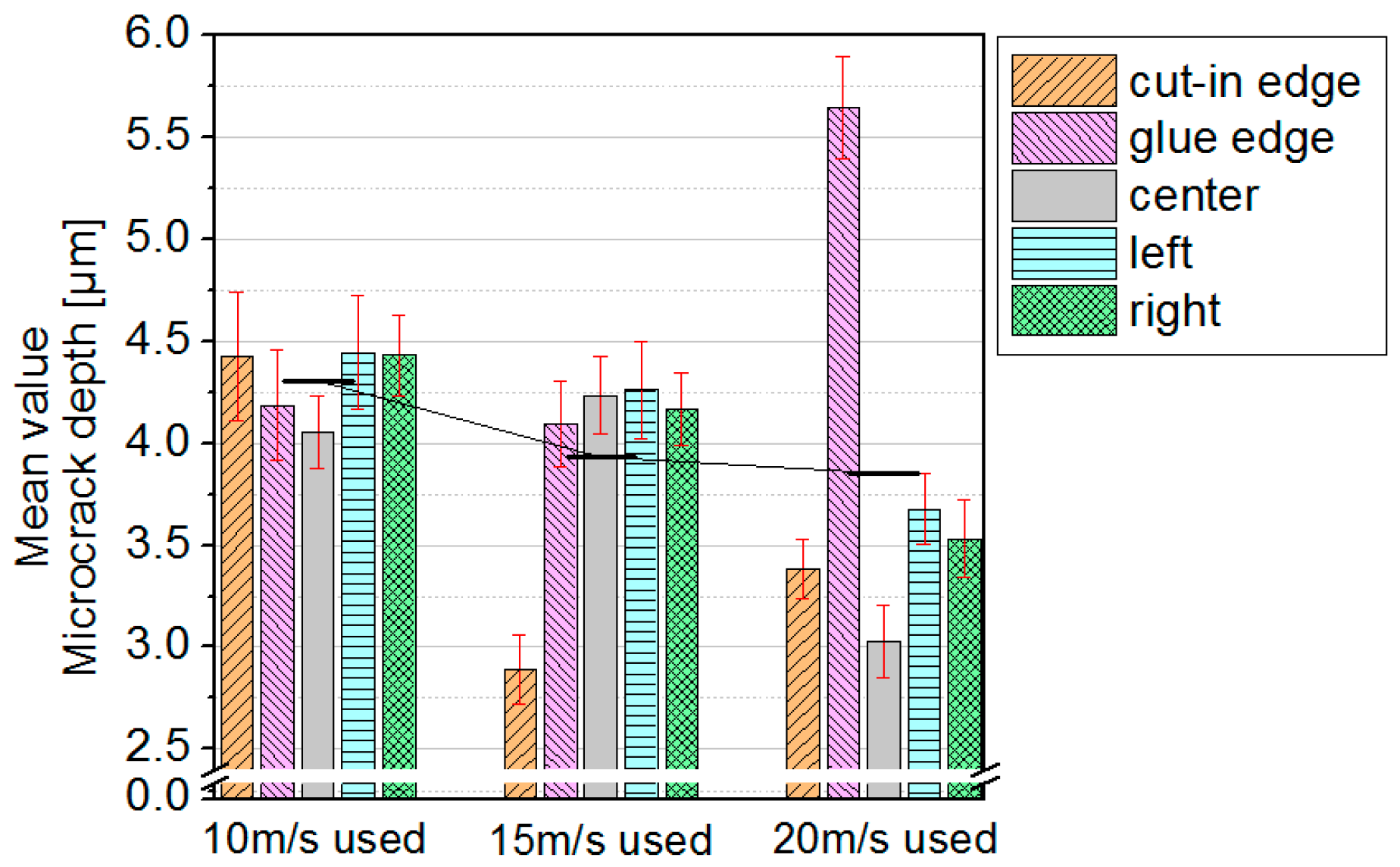

3.3. Determination of Microcrack Depths

4. Summary and Conclusions

- A lower Raman intensity ratio r (a-Si/c-Si ratio) correlates with a more homogeneous stress distribution.

- -

- A lower amount of a-Si phase occurs at the cut-in side of the wafer from the used wire side.

- -

- Lower a-Si is present at the wafer center from the used wire side compared to the left and right wafer edges.

- -

- Lower amorphization occurs on wafers from the fresh wire side.

- -

- Lower a-Si occurs on the wafer surface due to sawing with a lower wire velocity.

- Lower ∆σ peak maxima correspond to a higher amorphization of the silicon surface.

- -

- Lower ∆σ values occur at the gluing edge side of the wafer compared to the cut-in side.

- -

- Lower stress values occur on wafers cut by used wires.

- -

- The stress difference tends to be lower when sawing with a higher wire velocity.

- A lower microcrack depth shows a tendency toward higher stress.

- -

- Lower crack depth with higher crack number and higher stress occurs at the wafer cut-in side.

- -

- Lower damage by microcracks arises from sawing with a higher wire velocity.

- (1)

- Sawing with fresh diamond wire induces lower depth damage with shallower cracks. Reducing the crack length increases the fracture strength. Additionally, the fraction of the amorphous silicon on the wafer surface is smaller compared to sawing with diamond wire with worn particles. However, the maximal measured stress difference is higher on the fresh wire wafer side.

- (2)

- Sawing with higher wire velocity (reduction of the forces in the sawing direction under a constant feed rate) results in a lower crack depth. However, the local amorphization of the silicon surface is increased.

Acknowledgments

Author Contributions

Conflicts of Interest

References

- Würzner, S.; Buchwald, R.; Möller, H.J. Surface damage and mechanical strength of silicon wafers. Phys. Stat. Sol. C 2015, 12, 1119–1122. [Google Scholar] [CrossRef]

- Würzner, S.; Buchwald, R.; Retsch, S.; Möller, H.J. Investigation of the development of the microcrack structure in scratch tests with single diamond particles on monocrystalline silicon wafers. In Proceedings of the 29th European Photovoltaic Solar Energy Conference and Exhibition (EU PVSEC 2014), Amsterdam, The Netherlands, 22–26 September 2014; pp. 742–746. [Google Scholar]

- Möller, H.J.; Würzner, S.; Buchwald, R.; Herms, M.; Wagner, M. Comparative investigations of the surface damage of monocrystalline silicon wafers by Scanning Infrared Reflection Examination and Raman spectroscopy. Solid. State Phenom. 2016, 242, 466–471. [Google Scholar] [CrossRef]

- Geiler, H.D.; Karge, H.; Wagner, M.; Eichler, S.; Jurisch, M.; Kretzer, U.; Scheffer-Czygan, M. Photoelastic characterization of residual stress in GaAs-wafers. Mater. Sci. Semicond. Process. 2006, 9, 345–350. [Google Scholar] [CrossRef]

- Wolf, I.D. Micro-Raman spectroscopy to study local mechanical stress in silicon integrated circuits. Semicond. Sci. Technol. 1996, 11, 139–154. [Google Scholar] [CrossRef]

- Becker, M.; Scheel, H.; Christiansen, S.; Strunk, H.P. Grain orientation, texture, and internal stress optically evaluated by micro-Raman spectroscopy. J. Appl. Phys. 2007, 101, 063531. [Google Scholar] [CrossRef]

- Gogotsi, Y.; Baek, C.; Kirscht, F. Raman microspectroscopy study of processing-induced phase transformations and residual stress in silicon. Semicond. Sci. Technol. 1999, 14, 936–944. [Google Scholar] [CrossRef]

- Yan, J.; Asami, T.; Kuriyagawa, T. Nondestructive measurement of machining-induced amorphous layers in single-crystal silicon by laser micro-Raman spectroscopy. Precis. Eng. 2008, 32, 186–195. [Google Scholar] [CrossRef]

- Würzner, S.; Falke, A.; Buchwald, R.; Möller, H.J. Determination of the impact of the wire velocity on the surface damage of diamond wire sawn silicon wafers. Energy Procedia 2015, 77, 881–890. [Google Scholar] [CrossRef]

- D’Aragona, F.S. Dislocation etch for (100) planes in silicon. J. Electrochem. Soc. 1972, 119, 948–951. [Google Scholar]

- Buchwald, R.; Würzner, S.; Fröhlich, K.; Winstanley, S.; Lehmann, T.; Sunder, K.; Möller, H.J. Analysis of the sub-surface damage of mc- and cz-si wafers sawn with diamond-plated wire. In Proceedings of the 28th European Photovoltaic Solar Energy Conference and Exhibition (EU PVSEC 2013), Paris, France, 30 September–4 October 2013; pp. 1502–1506. [Google Scholar]

- Behm, T.; Fütterer, W.; Funke, C.; Kaminski, S.; Möller, H.J.; Rietzschel, R.; Wagner, T. Challenges of the wire saw wafering process. Photovol. Int. 2011, 11, 36–47. [Google Scholar]

- Domnich, V.; Gogotsi, Y. Phase transformations in silicon under contact loading. Rev. Adv. Mater. Sci. 2002, 3, 1–36. [Google Scholar]

| Parameter Name | Parameter Value |

|---|---|

| Type of wire saw | Meyer Burger DS264 |

| Wire core diameter | 120 µm |

| Diamond size distribution | 8–16 µm |

| Linear diamond density | 330 diamonds per mm2 wire surface |

| Coolant medium | neutral water based coolant |

| Wire velocities | 10 m/s; 15 m/s; 20 m/s |

| Pilgrim length | 322 m forward/319 m backward |

| Wire tension | 28 N |

| Feed rate | 0.6 mm/min |

| Wire Velocity | Raman Intensity Ratio r for Wafers of the | |

|---|---|---|

| Fresh Wire Side | Used Wire Side | |

| 10 m/s | 0.16 (8 nm) | 0.58 (23 nm) |

| 15 m/s | 0.21 (10 nm) | 1.29 (38 nm) |

| 20 m/s | 0.25 (12 nm) | 1.13 (35 nm) |

© 2017 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Würzner, S.; Herms, M.; Kaden, T.; Möller, H.J.; Wagner, M. Characterization of the Diamond Wire Sawing Process for Monocrystalline Silicon by Raman Spectroscopy and SIREX Polarimetry. Energies 2017, 10, 414. https://doi.org/10.3390/en10040414

Würzner S, Herms M, Kaden T, Möller HJ, Wagner M. Characterization of the Diamond Wire Sawing Process for Monocrystalline Silicon by Raman Spectroscopy and SIREX Polarimetry. Energies. 2017; 10(4):414. https://doi.org/10.3390/en10040414

Chicago/Turabian StyleWürzner, Sindy, Martin Herms, Thomas Kaden, Hans Joachim Möller, and Matthias Wagner. 2017. "Characterization of the Diamond Wire Sawing Process for Monocrystalline Silicon by Raman Spectroscopy and SIREX Polarimetry" Energies 10, no. 4: 414. https://doi.org/10.3390/en10040414