Control Strategy of Single-Phase Three Level Neutral Point Clamped Cascaded Rectifier

Abstract

:1. Introduction

- To obtain sinusoidal grid current;

- To achieve unity power factor;

- To regulate and equalize voltages across the output terminals;

- To balance the dc-link capacitor voltages in each module.

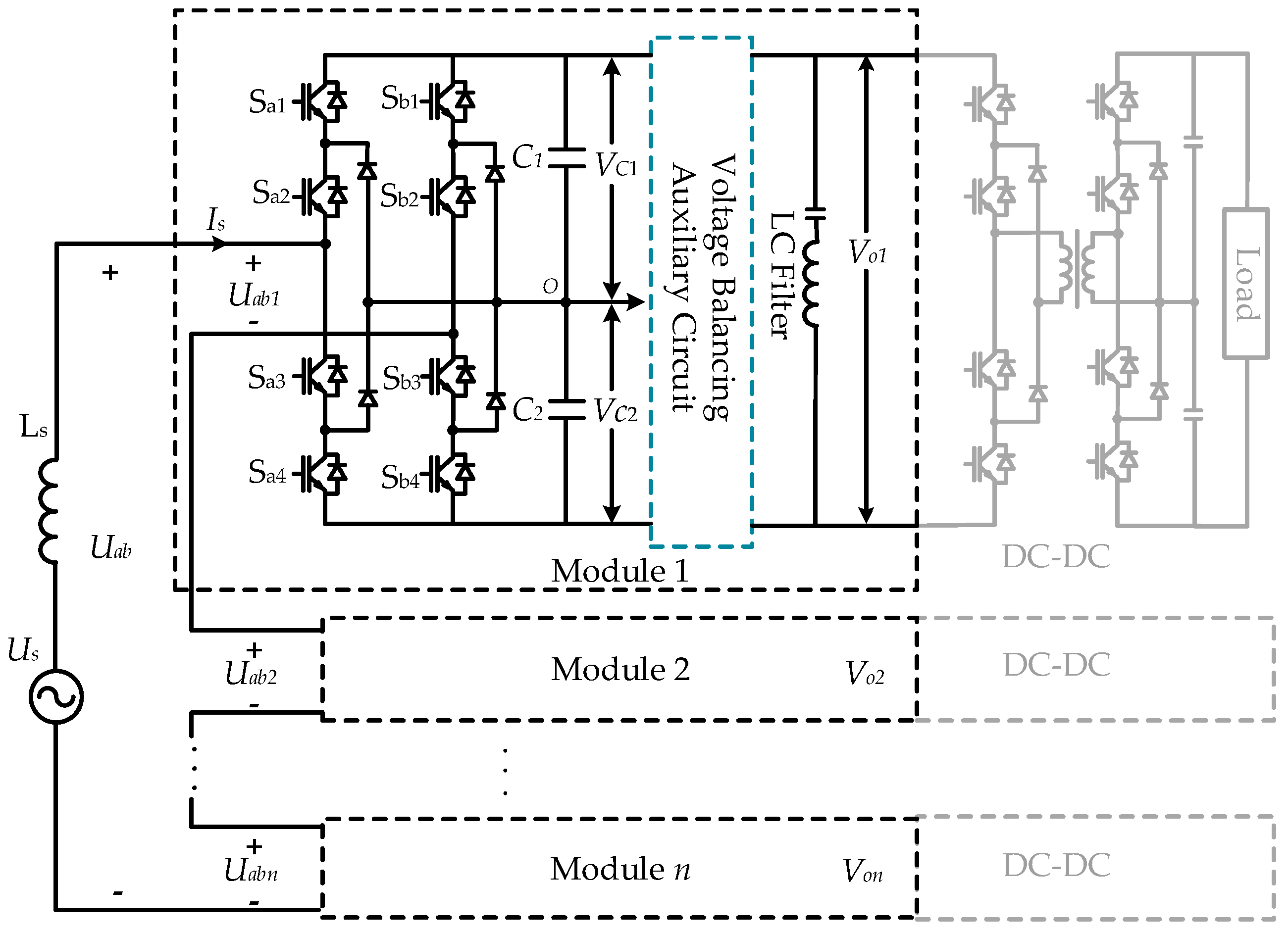

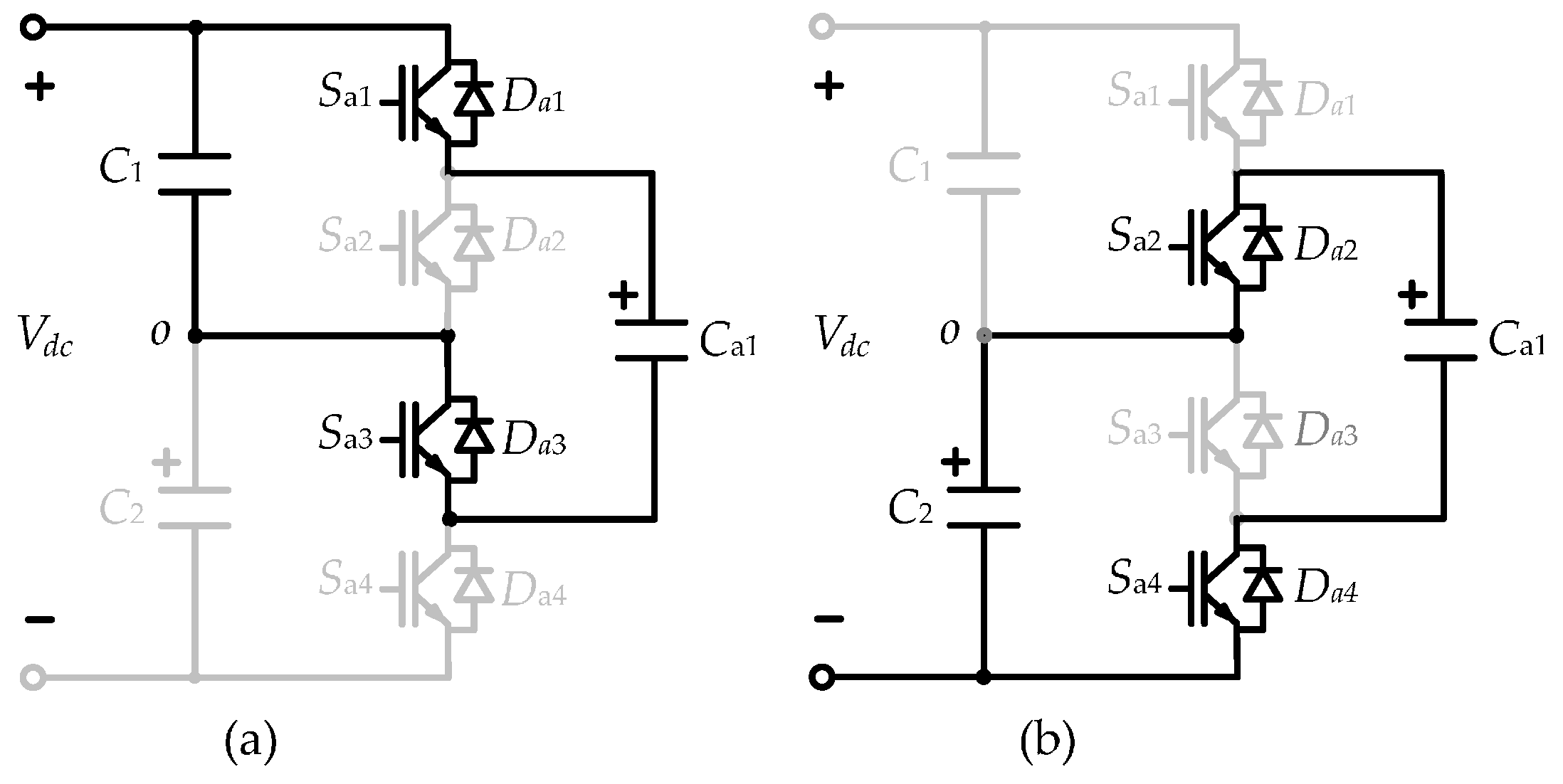

2. Topology

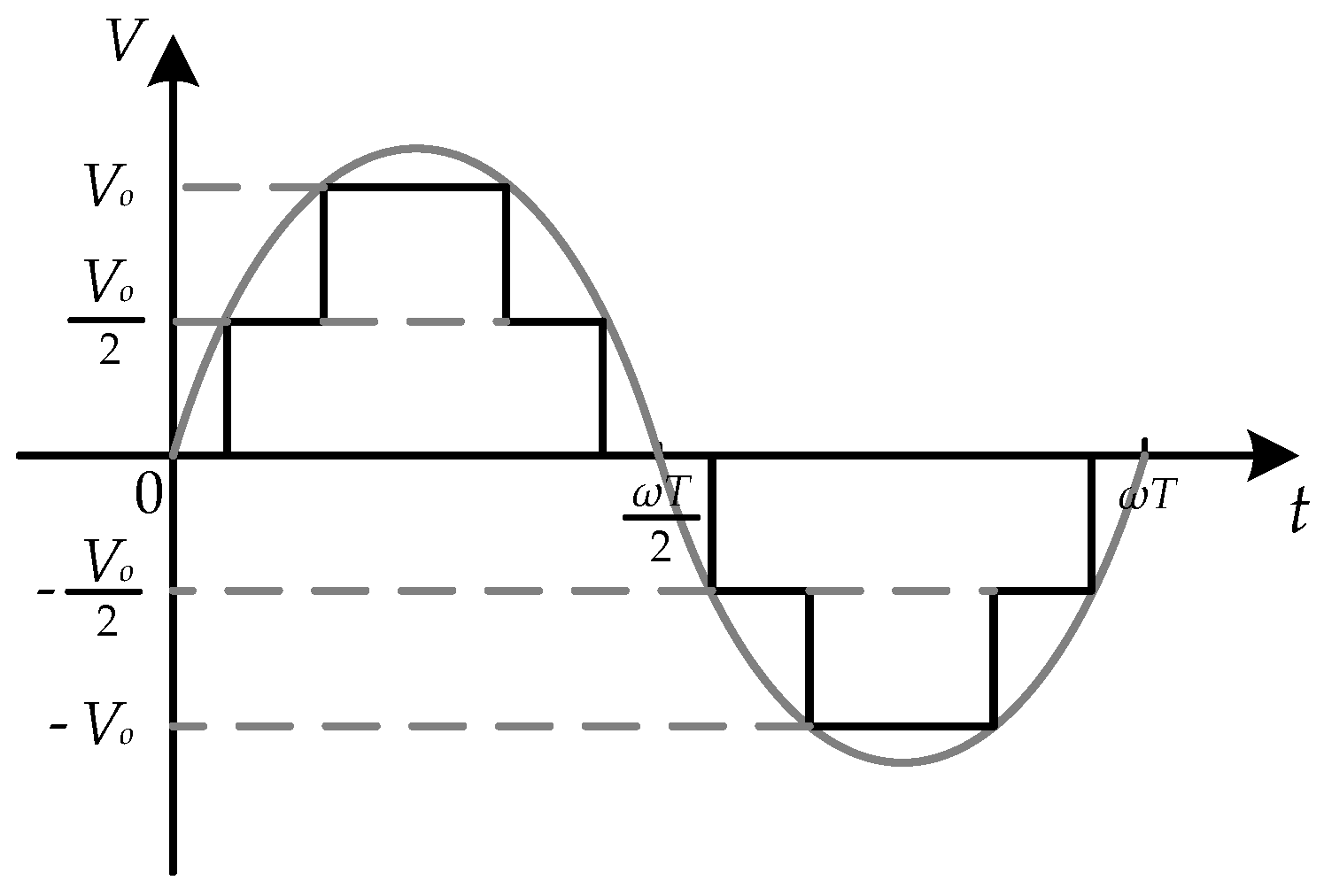

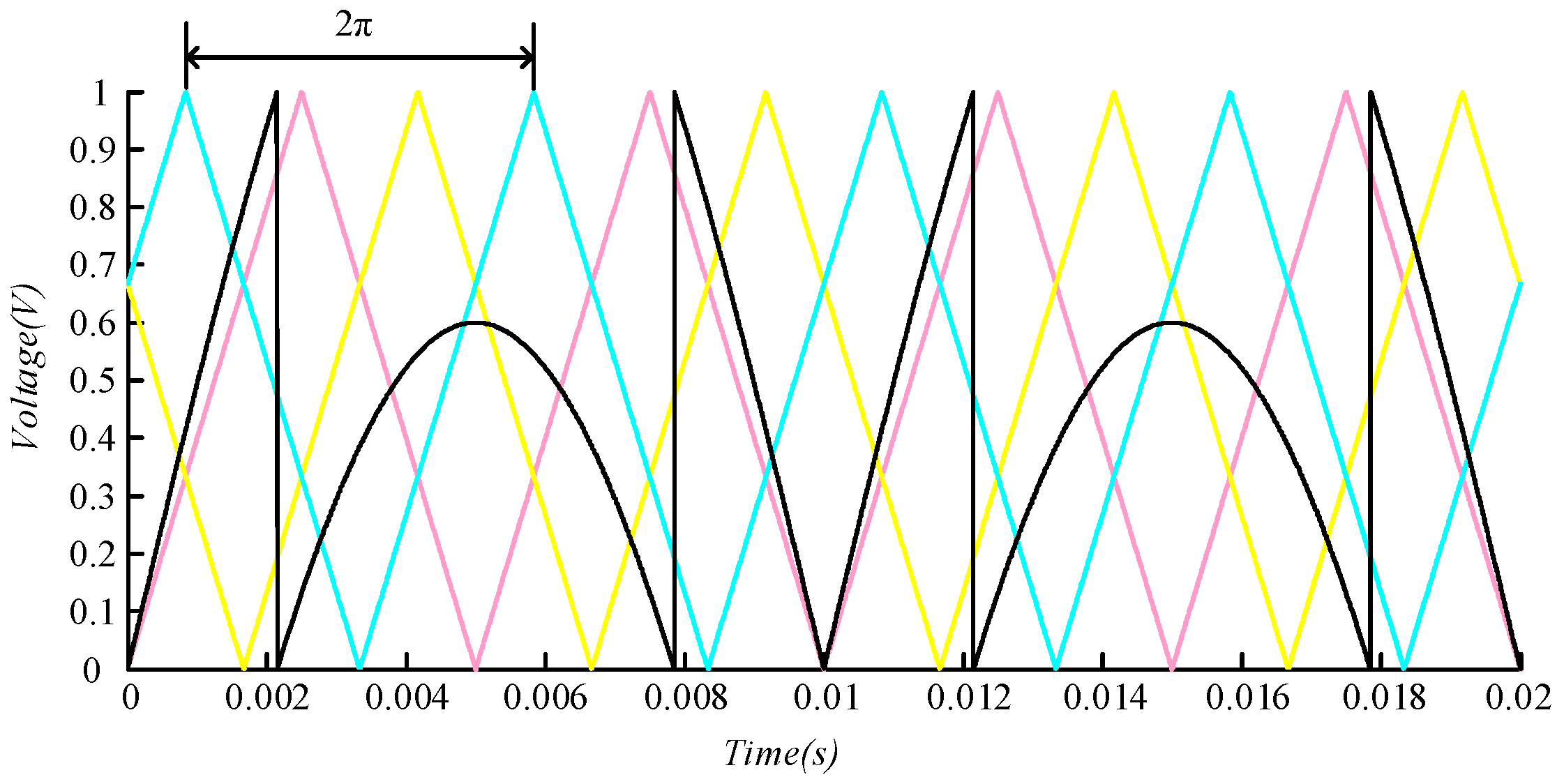

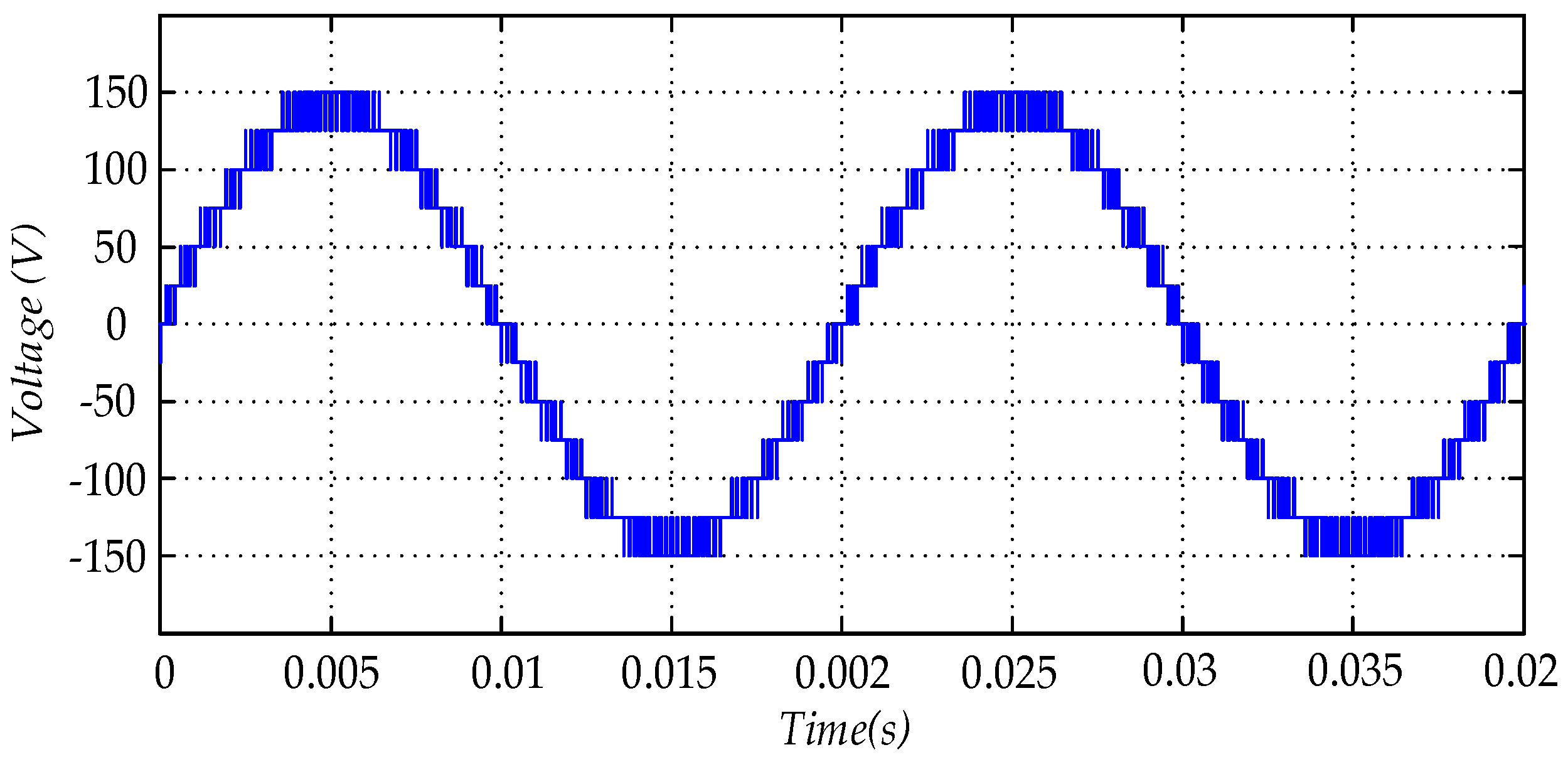

3. Modulation Scheme

- Sector 1: 0.5 < Vref ≤ 1;

- Sector 2: 0 < Vref ≤ 0.5;

- Sector 3: −0.5 ≤ Vref < 0;

- Sector 4: −1 < Vref ≤ −0.5.

4. Balancing Strategy

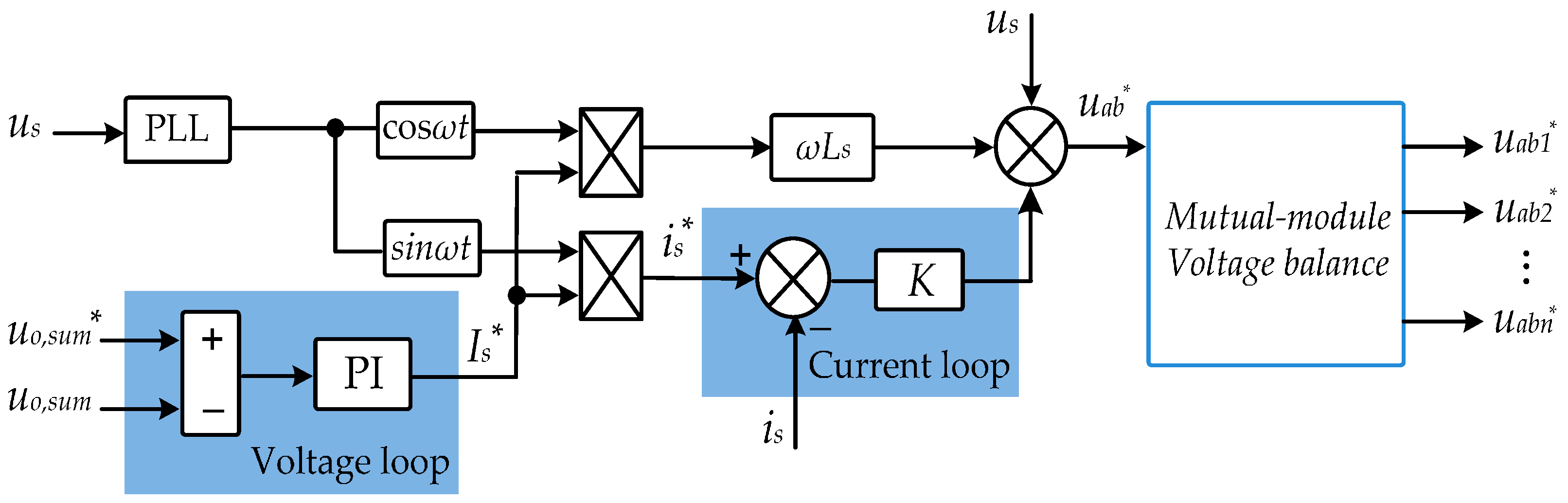

4.1. Overall Control

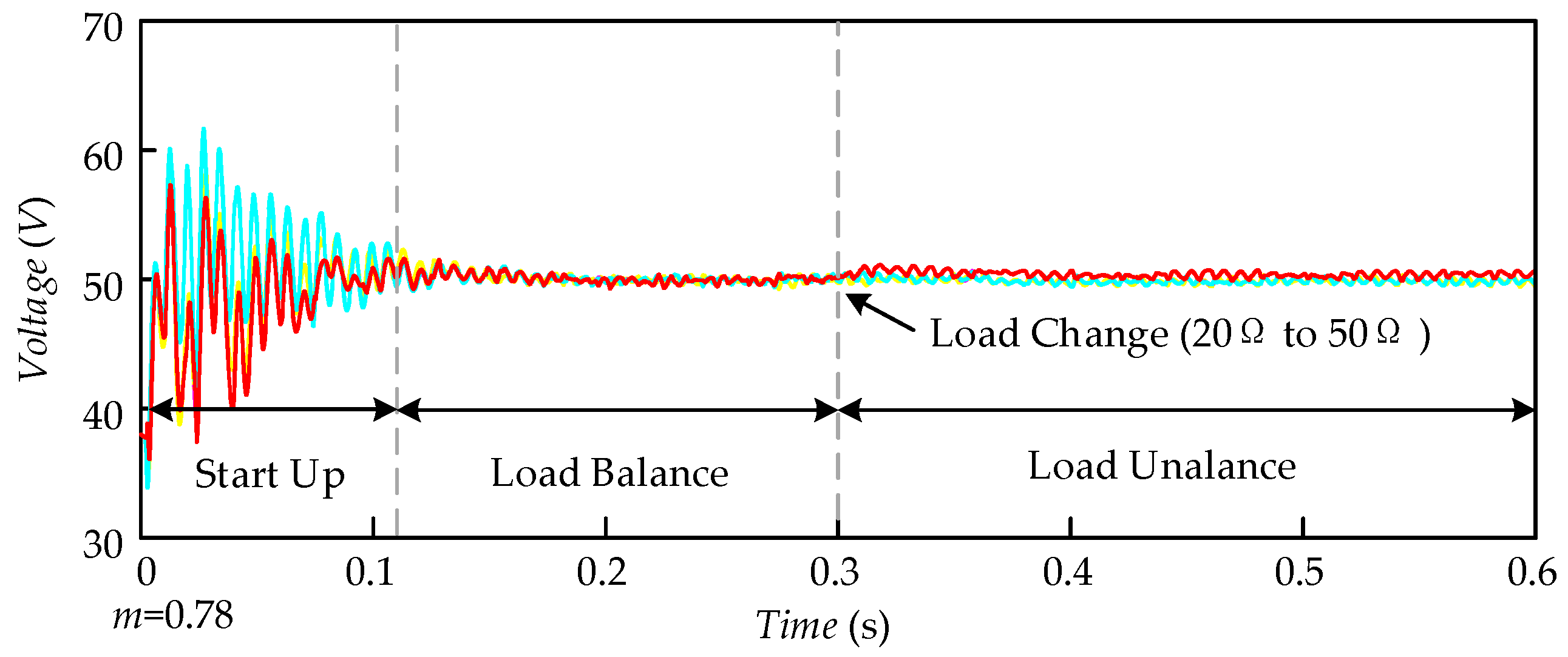

4.2. Mutual-Module Voltage Balancing Strategy

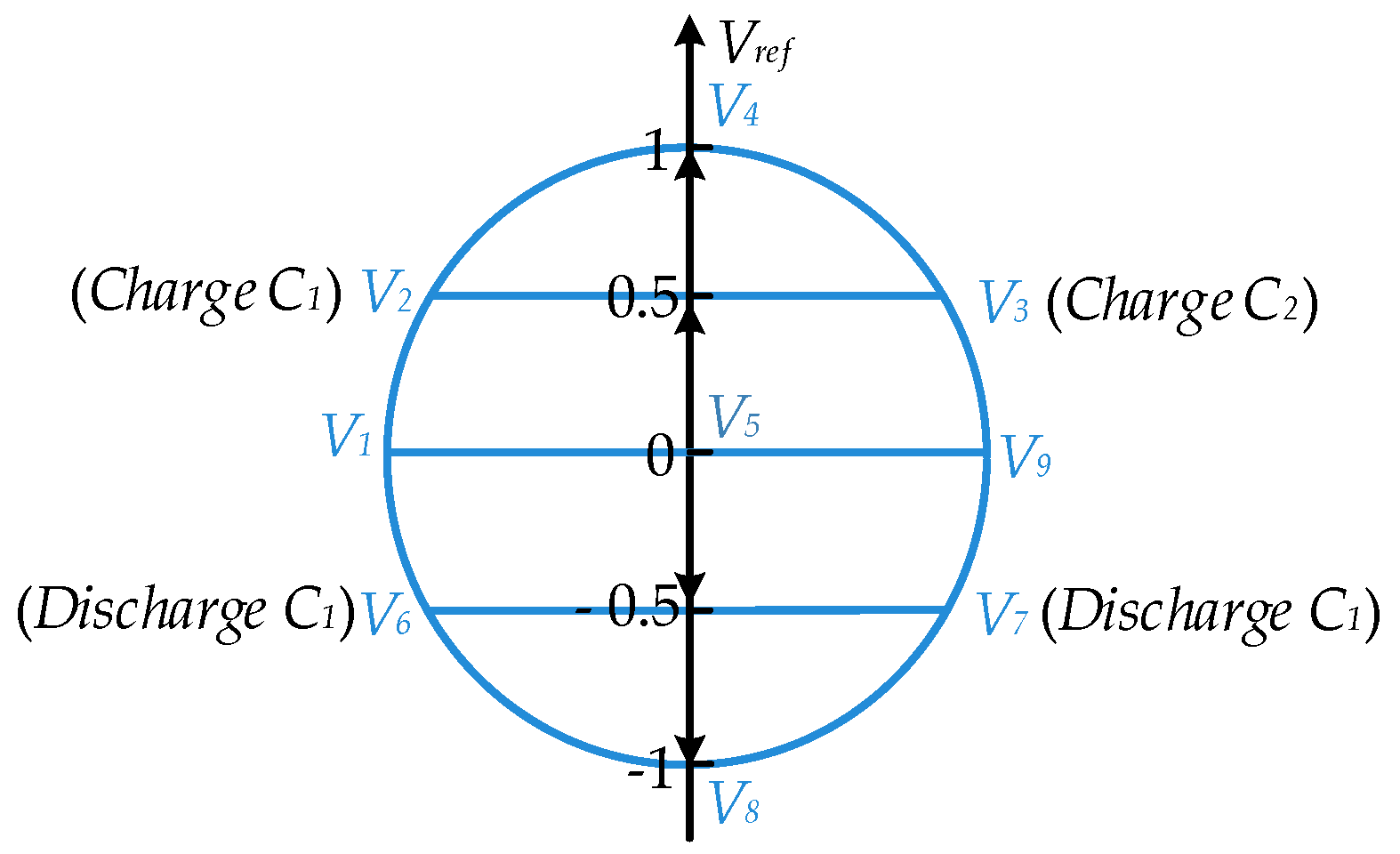

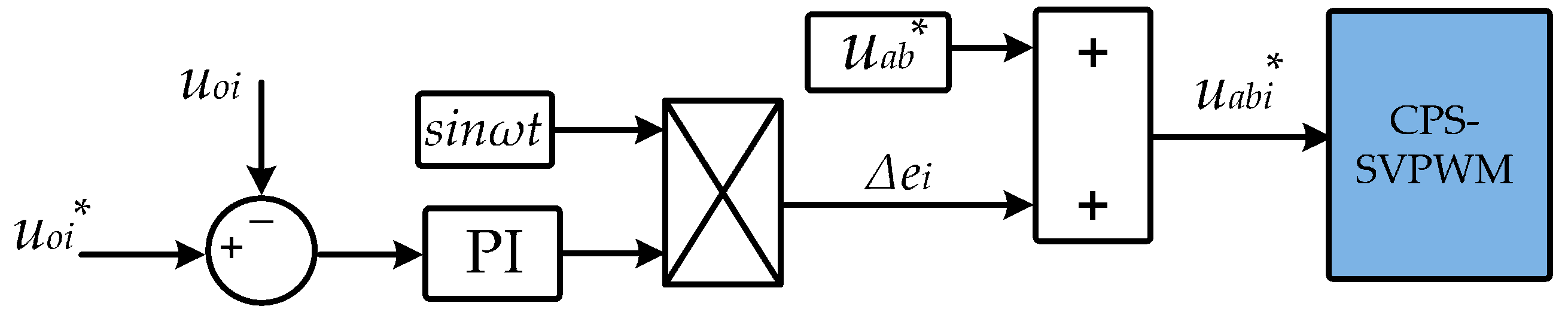

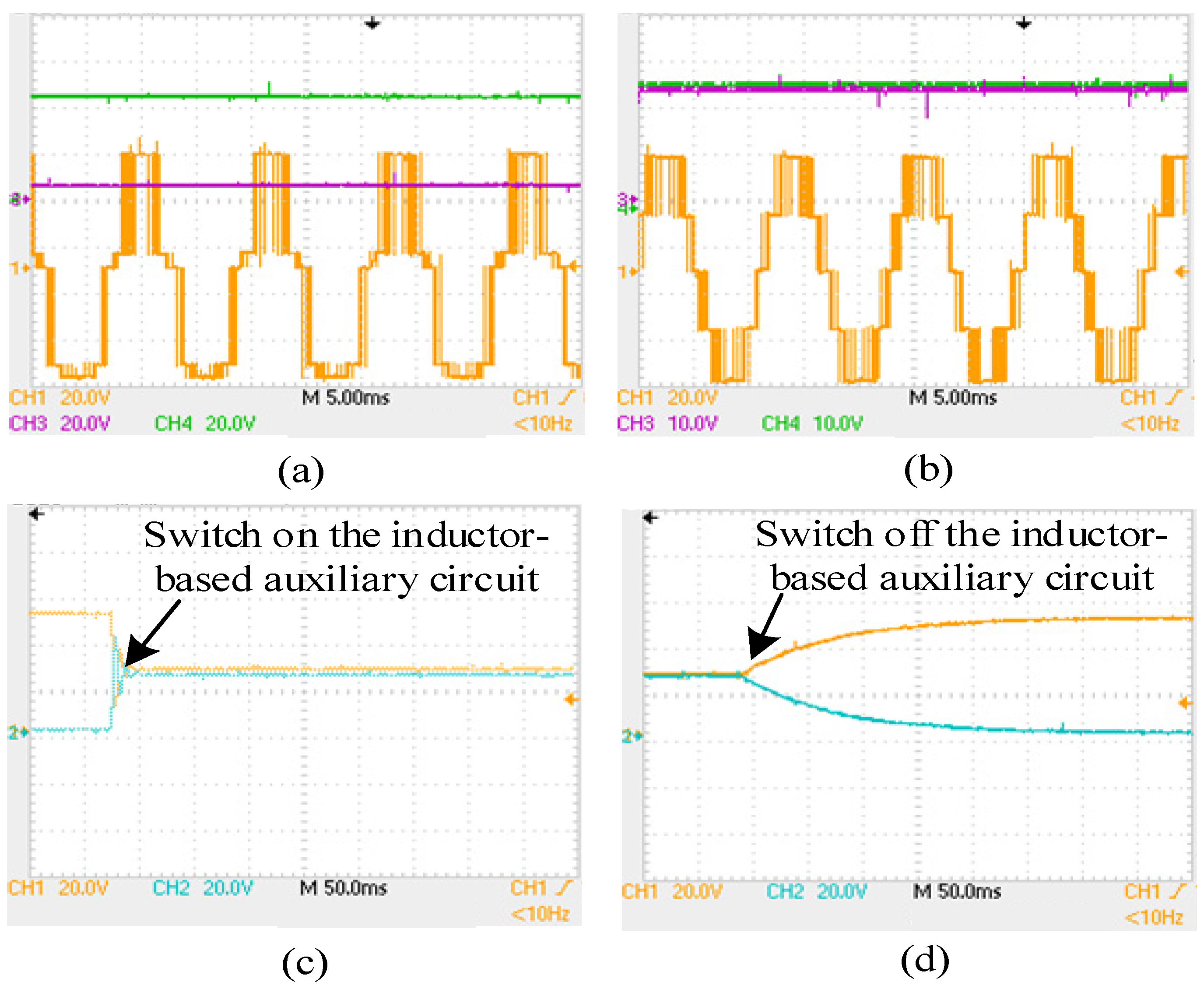

4.3. Internal-Module Voltage Balancing Strategy

- Determining the location of the reference signal;

- The calculation of on-times;

- Determination and selection of redundant vectors.

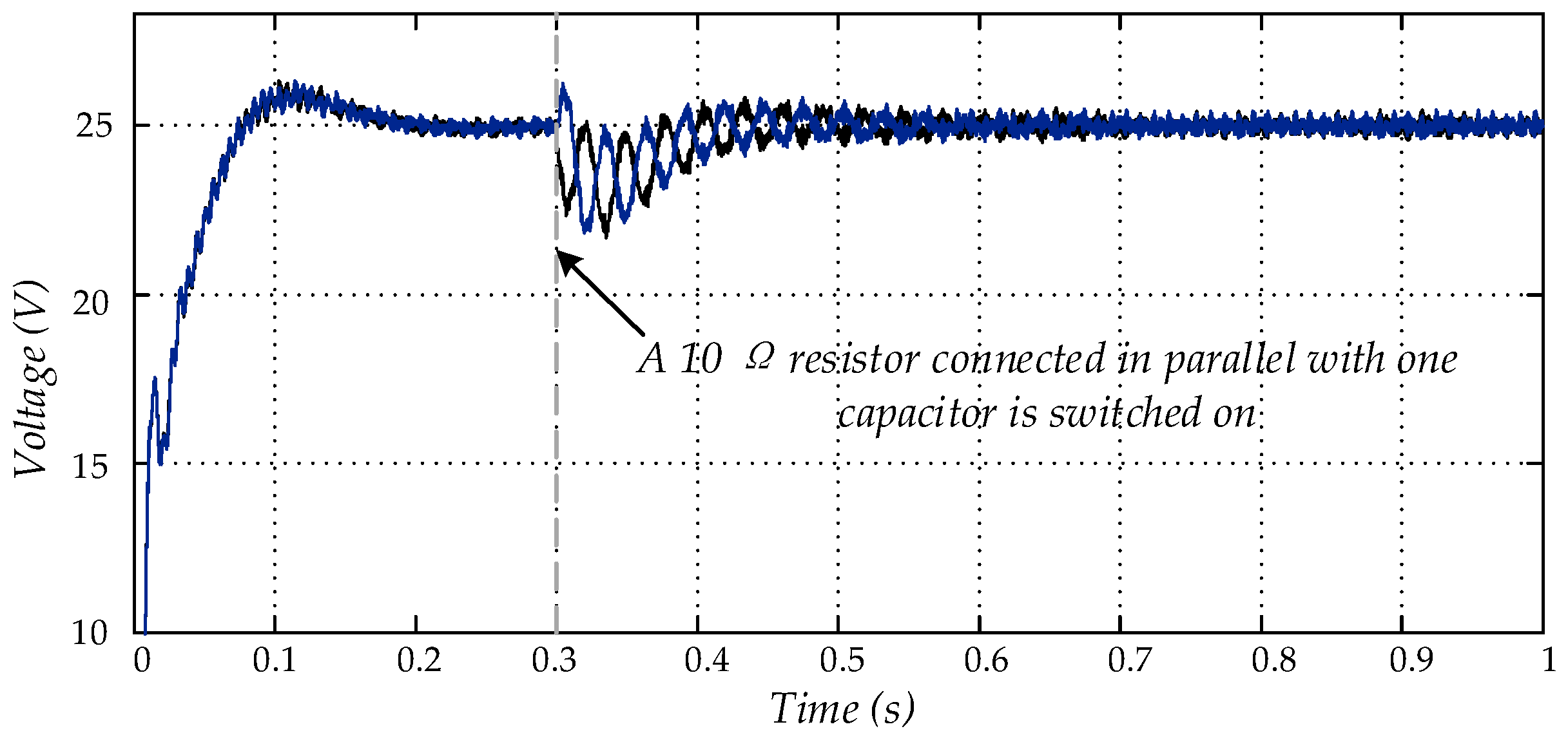

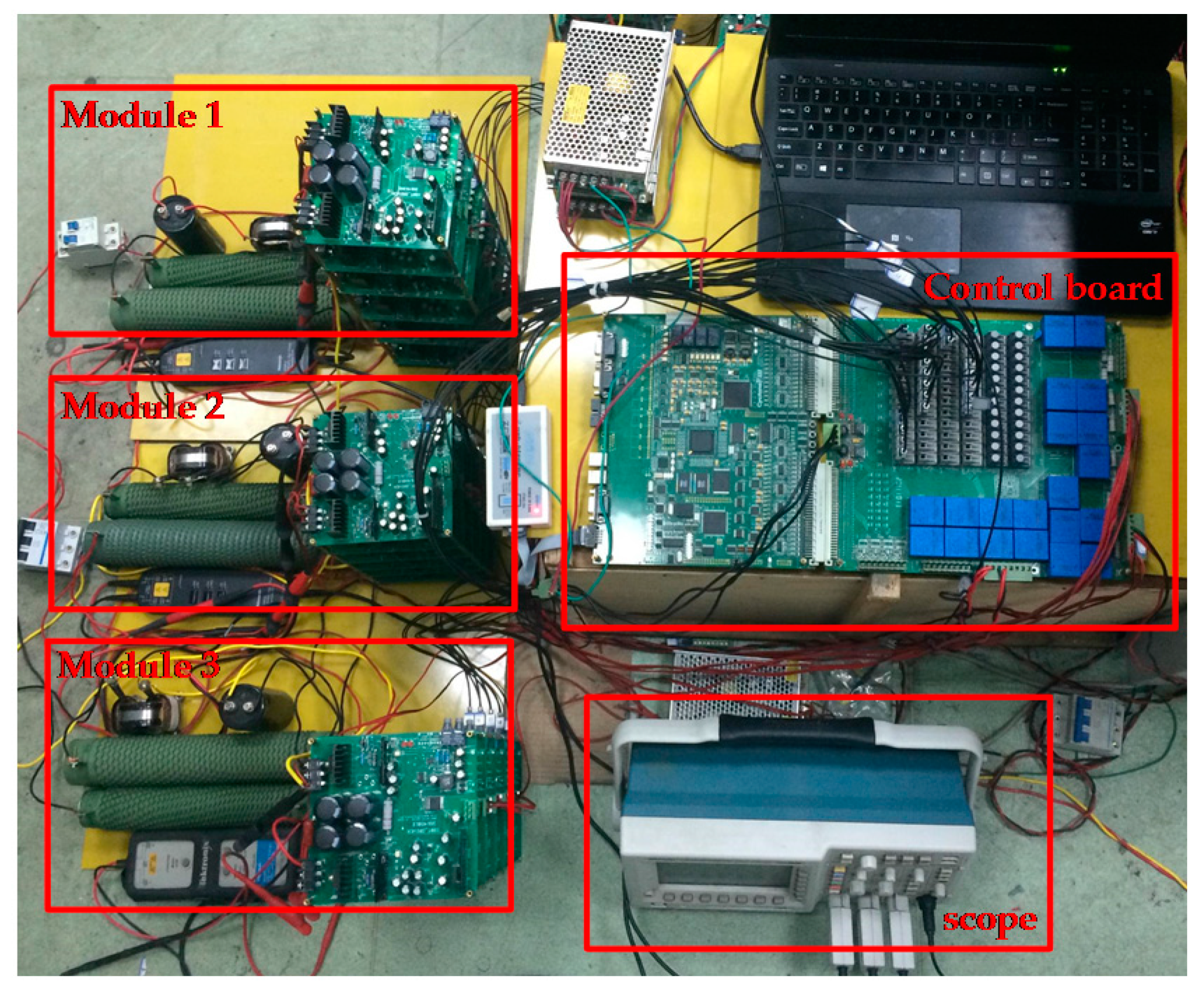

5. Simulation and Experiment

6. Conclusions

Acknowledgments

Author Contributions

Conflicts of Interest

References

- Kouro, S.; Malinowski, M.; Gopakumar, K.; Pou, J.; Franquelo, L.G.; Wu, B.; Rodriguez, J.; Perez, M.A.; Leon, J.I. Recent advances and industrial applications of multilevel converters. IEEE Trans. Ind. Electron. 2010, 57, 2553–2580. [Google Scholar] [CrossRef]

- Franquelo, L.G.; Leon, J.I.; Dominguez, E. Recent advances in high-power industrial applications. In Proceedings of the 2010 IEEE International Symposium on Industrial Electronics (ISIE), Bari, Italy, 4–7 July 2010; pp. 5–10. [Google Scholar]

- Vahedi, H.; Shojaei, A.A.; Chandra, A.; Al-Haddad, K. Five-level reduced-switch-count boost PFC rectifier with multicarrier PWM. IEEE Trans. Ind. Appl. 2016, 52, 4201–4207. [Google Scholar] [CrossRef]

- Vahedi, H.; Labbé, P.A.; Al-Haddad, K. Sensor-less five-level packed U-cell (PUC5) inverter operating in stand-alone and grid-connected modes. IEEE Trans. Ind. Inform. 2016, 12, 361–370. [Google Scholar] [CrossRef]

- Shu, Z.; Ding, N.; Chen, J.; Zhu, H.; He, X. Multilevel SVPWM with DC-link capacitor voltage balancing control for diode-clamped multilevel converter based STATCOM. IEEE Trans. Ind. Electron. 2013, 60, 1884–1896. [Google Scholar] [CrossRef]

- Villanueva, E.; Correa, P.; Rodriguez, J.; Pacas, M. Control of a single-phase cascaded H-bridge multilevel inverter for grid-connected photovoltaic systems. IEEE Trans. Ind. Electron. 2009, 56, 4399–4406. [Google Scholar] [CrossRef]

- Cecati, C.; Dell’Aquila, A.; Liserre, M.; Monopoli, V.G. Design of H-bridge multilevel active rectifier for traction systems. IEEE Trans. Ind. Appl. 2003, 39, 1541–1550. [Google Scholar] [CrossRef]

- Tao, X.; Li, Y.; Sun, M. A Pi-based control scheme for primary cascaded H-bridge rectifier in transformerless traction converters. In Proceedings of the International Conference on Electrical Machines and Systems, Incheon, Korea, 10–13 October 2010; pp. 824–828. [Google Scholar]

- Chuanhong, Z.; Dujic, D.; Mester, A.; Steinke, J.K.; Weiss, M.; Lewdeni-Schmid, S.; Chaudhuri, T.; Stefanutti, P. Power electronic traction transformer—Medium voltage prototype. IEEE Trans. Ind. Electron. 2014, 61, 3257–3268. [Google Scholar]

- Malinowski, M.; Gopakumar, K.; Rodriguez, J.; Perez, M.A. A survey on cascaded multilevel inverters. IEEE Trans. Ind. Electron. 2010, 57, 2197–2206. [Google Scholar] [CrossRef]

- Vahedi, H.; Al-Haddad, K. A novel multilevel multioutput bidirectional active buck PFC rectifier. IEEE Trans. Ind. Electron. 2016, 63, 5442–5450. [Google Scholar] [CrossRef]

- Sebaaly, F.; Vahedi, H.; Kanaan, H.Y.; Moubayed, N.; Al-Haddad, K. Design and implementation of space vector modulation-based sliding mode control for grid-connected 3L-NPC inverter. IEEE Trans. Ind. Electron. 2016, 63, 7854–7863. [Google Scholar] [CrossRef]

- Rodriguez, J.; Bernet, S.; Steimer, P.K.; Lizama, I.E. A survey on neutral-point-clamped inverters. IEEE Trans. Ind. Electron. 2010, 57, 2219–2230. [Google Scholar] [CrossRef]

- Marzoughi, A.; Imaneini, H. Optimal selective harmonic elimination for cascaded H-bridge-based multilevel rectifiers. IET Power Electron. 2014, 7, 350–356. [Google Scholar] [CrossRef]

- Dell’Aquila, A.; Liserre, M.; Monopoli, V.G.; Rotondo, P. Overview of PI-based solutions for the control of DC buses of a single-phase H-bridge multilevel active rectifier. IEEE Trans. Ind. Appl. 2008, 44, 857–866. [Google Scholar] [CrossRef]

- Shu, Z.; Kuang, Z.; Wang, S.; Peng, X.; He, X. Diode-clamped three-level multi-module cascaded converter based power electronic traction transformer. In Proceedings of the IEEE 2nd International Future Energy Electronics Conference (IFEEC), Taipei, Taiwan, 1–4 November 2015. [Google Scholar]

- Vahedi, H.; Labbe, P.A.; Al-Haddad, K. Balancing three-level neutral point clamped inverter DC bus using closed-loop space vector modulation: Real-time implementation and investigation. IET Power Electron. 2016, 9, 2076–2084. [Google Scholar] [CrossRef]

- Celanovic, N.; Boroyevich, D. A comprehensive study of neutral-point voltage balancing problem in three-level neutral-point-clamped voltage source PWM inverters. IEEE Trans. Power Electron. 2000, 15, 242–249. [Google Scholar] [CrossRef]

- Shu, Z.; He, X.; Wang, Z.; Qiu, D.; Jing, Y. Voltage balancing approaches for diode-clamped multilevel converters using auxiliary capacitor-based circuits. IEEE Trans. Power Electron. 2013, 28, 2111–2124. [Google Scholar] [CrossRef]

- Shu, Z.; Zhu, H.; He, X.; Ding, N.; Yang, Y. One-inductor-based auxiliary circuit for DC-link capacitor voltage equalisation of diode-clamped multilevel converter. IET Power Electron. 2013, 6, 1339–1349. [Google Scholar]

- Peng, X.; He, X.; Han, P.; Guo, A.; Shu, Z.; Gao, S. Smooth switching technique for voltage balance management based on three-level neutral point clamped cascaded rectifier. Energies 2016, 9, 803. [Google Scholar] [CrossRef]

- Moeini, A.; Iman-Eini, H.; Marzoughi, A. DC link voltage balancing approach for cascaded H-bridge active rectifier based on selective harmonic elimination-pulse width modulation. IET Power Electron. 2015, 8, 583–590. [Google Scholar] [CrossRef]

- Cecati, C.; Dell’Aquila, A.; Liserre, M.; Monopoli, V.G. A passivitybased multilevel active rectifier with adaptive compensation for traction applications. IEEE Trans. Ind. Appl. 2003, 39, 1404–1413. [Google Scholar] [CrossRef]

- Dell’Aquila, A.; Liserre, M.; Monopoli, V.G.; Rotondo, P. An energy-based control for an n-H-bridges multilevel active rectifier. IEEE Trans. Ind. Electron. 2005, 52, 670–678. [Google Scholar] [CrossRef]

- Zhao, T.; Wang, G.; Bhattacharya, S.; Huang, A.Q. Voltage and power balance control for a cascaded H-bridge converter-based solid-state transformer. IEEE Trans. Power Electron. 2013, 28, 1523–1532. [Google Scholar] [CrossRef]

| Vectors | Sa | Sb | uab | C1 | C2 | Categories |

|---|---|---|---|---|---|---|

| V1 | p | p | 0 | no effect | no effect | Z |

| V2 | p | o | VC1 | Charge | no effect | SP |

| V3 | o | n | VC2 | no effect | charge | SP |

| V4 | p | n | VC1 + VC2 | charge | charge | LP |

| V5 | o | o | 0 | no effect | no effect | Z |

| V6 | n | o | −VC2 | no effect | discharge | SN |

| V7 | o | p | −VC1 | discharge | no effect | SN |

| V8 | n | p | −VC1 − VC2 | discharge | discharge | LN |

| V9 | n | n | 0 | no effect | no effect | Z |

| VC1 > VC2, is > 0 | VC1 > VC2, is < 0 | VC1 < VC2, is < 0 | VC1 < VC2, is > 0 |

|---|---|---|---|

| SP = V3 | SP = V2 | SP = V3 | SP = V2 |

| SN = V7 | SN = V6 | SN = V7 | SN = V6 |

| Parameter Name | Parameter Value |

|---|---|

| Number of modules | 3 |

| Voltage source | 75 V/50 Hz |

| dc-link capacitor | 2200 µF |

| Inductance of auxiliary circuit | 1 mH |

| Inductance of LC filter | 1 mH |

| Capacitance of LC filter | 2200 µF |

| Switching frequency | 2 kHz |

© 2017 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

He, X.; Lin, X.; Peng, X.; Han, P.; Shu, Z.; Gao, S. Control Strategy of Single-Phase Three Level Neutral Point Clamped Cascaded Rectifier. Energies 2017, 10, 592. https://doi.org/10.3390/en10050592

He X, Lin X, Peng X, Han P, Shu Z, Gao S. Control Strategy of Single-Phase Three Level Neutral Point Clamped Cascaded Rectifier. Energies. 2017; 10(5):592. https://doi.org/10.3390/en10050592

Chicago/Turabian StyleHe, Xiaoqiong, Xiaolan Lin, Xu Peng, Pengcheng Han, Zeliang Shu, and Shibin Gao. 2017. "Control Strategy of Single-Phase Three Level Neutral Point Clamped Cascaded Rectifier" Energies 10, no. 5: 592. https://doi.org/10.3390/en10050592