# Article A SVPWM to Eliminate Common-Mode Voltage for Multilevel Inverters

## Xiongmin Tang<sup>1</sup>, Chengjing Lai<sup>1</sup>, Zheng Liu<sup>2</sup> and Miao Zhang<sup>1,\*</sup>

- <sup>1</sup> School of automation, Guangdong University of Technology, 510006 Guangzhou, China; tangxiongmin@126.com (X.T.); laichengjing@126.com (C.L.)

- <sup>2</sup> School of Electrical and Information Engineering, Changsha University of Science and Technology, 410004 Changsha, China; leo\_johncn@163.com

- \* Correspondence: bezhangm@gdut.edu.cn; Tel.: +86-020-3932-2552

Academic Editor: Gabriele Grandi Received: 5 April 2017; Accepted: 2 May 2017; Published: 18 May 2017

**Abstract:** This paper presents a new space vector pulse width modulation (SVPWM) to eliminate common-mode voltage (CMV) for multilevel inverters. The proposed SVPWM is performed in a new coordinate system, in which the converter voltage vectors have only integer entries and the absolute coordinate increment between adjacent vectors is equal to 1. The location of the reference vector, detection of the nearest three CMV vectors, and duty cycles of the nearest three CMV vectors are all obtained by simple calculations, no lookup table is needed and the SVPWM is computationally fast. Compared with earlier pulse width modulations (PWMs), the realization of the CMV vectors is very simple, and the CMV of multilevel inverters are limited to zero with any modulation index. Because the SVPWM is independent of the level number of the inverter, the proposed SVPWM is suitable for any level of inverter. This paper also thoroughly compares the proposed SVPWM with prior PWMs. Experimental results are also given in the paper.

Keywords: SVPWM; common-mode voltages; multilevel inverters

## 1. Introduction

Great progress has been made in the development of multilevel inverters in recent years [1–3]. It is well known that common-mode voltages (CMVs) are linked with excessive bearing currents, which may cause premature motor bearing failure. The causes of the bearing currents and their effect on the bearing currents have been well explained by References [4–6].

For decades, passive filters and active filters [7–9] have been proposed to reduce the impact of CMVs. However, these methods cause the volume and the control of the equipment to increase significantly. Therefore, in order to reduce the impact of CMV, it is necessary to adjust the control strategies.

For multilevel inverters, some vectors have redundant switching states, and these redundant switching states can be used to decrease or eliminate the CMV. Based on this idea, different modulation methods are proposed to reduce or eliminate the CMV.

Due to the simple principle and the low harmonic distortion characteristics of sinusoidal pulse width modulation (SPWM), SPWM is widely used in multilevel inverters. Hoverer, the amplitude and the rate of change of CMV remain large, especially with high modulation indexes. This has a great influence on motor-type load. To solve this problem, a carrier modulation pulse width modulation (PWM) for a 3-level neutral point clamped (NPC) inverter is presented in Reference [10]. Because the non-nearest vectors for two triangles were selected in the PWM, this causes the total harmonic distortion (THD) of the line-to-line voltage to be higher than the conventional method. Similar PWMs have been presented in References [11–14]. However, these PWMs are difficult to extend to higher

levels. The SVPWM proposed in Reference [15] can be easily extended to higher level inverters. However, the maximum change of CMV is still limited to 1/3 of DC bus voltages of power cells.

To eliminate the CMV of multilevel inverters, zero CMVs are selected to synthesize the reference vector in the PWMs. However, most of these PWMs [16–19] are limited to 3-level or 5-level inverters, and have many unresolved issues, such as the fast location of the reference vector, the simple realization of the vectors, etc.

To address the issue, a new SVPWM to eliminate CMV for an n-level inverter is proposed in this paper. The SVPWM is carried out in a new coordinate system named the  $\alpha'\beta'$  coordinate system. This new SVPWM has the following salient features:

- Location of the reference vector, detection of the nearest three CMV vectors, and duty cycles are all obtained by simple calculations. No lookup table is required, less memory is needed, and the SVPWM is computationally fast.

- (2) Compared with earlier PWMs, the realization of the CMV vectors is very simple.

- (3) CMVs of multilevel inverters are limited to zero with any modulation index.

- (4) The PWM is suitable for any level of inverter.

The rest of the paper is organized as follows: Section 2 presents principle of the SVPWM. Section 3 gives experimental results and comparative analysis with other PWMs. Section 4 gives our concluding remarks.

## 2. Principle of the SVPWM

## 2.1. $\alpha'\beta'$ Coordinate System

A  $\alpha'\beta'$  coordinate system is our developed coordinate system [20], and this coordinate system has been successfully applied in a capacitor voltage balancing control for diode-clamped multilevel inverters [21] and a zero-order voltage constraint for cascaded multilevel inverters [20]. In the  $\alpha'\beta'$ coordinate system, the multilevel inverter voltage vectors have only integer entries, and the absolute coordinate increment between adjacent vectors is equal to 1. The transformation matrix between the  $\alpha'\beta'$  coordinate system, the traditional  $\alpha\beta$  coordinate system, and the *abc* coordinate system are written as:

$$\begin{bmatrix} \alpha'\\ \beta' \end{bmatrix} = \begin{bmatrix} \frac{\sqrt{3}}{2} & \frac{\sqrt{2}}{2}\\ -\frac{\sqrt{3}}{2} & \frac{\sqrt{2}}{2} \end{bmatrix} \begin{bmatrix} \alpha\\ \beta \end{bmatrix} = \begin{bmatrix} 1 & 0 & -1\\ -1 & 1 & 0 \end{bmatrix} \begin{bmatrix} a\\ b\\ c \end{bmatrix} = \begin{bmatrix} a-c\\ -a+b \end{bmatrix}$$

(1)

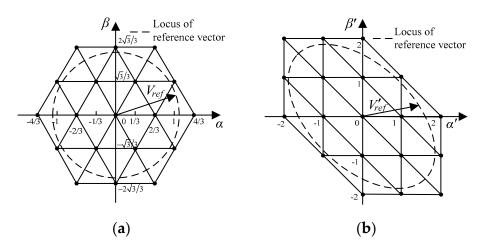

where, *a*, *b* and *c* are the normalized three phase voltages of multilevel inverters.  $[\alpha \beta]^T$  and  $[\alpha' \beta']^T$  are the coordinate values of  $[a b c]^T$  in the traditional  $\alpha\beta$  coordinate system and the  $\alpha'\beta'$  coordinate system, respectively. The projections of vectors for 3-level inverter in the  $\alpha\beta$  and  $\alpha'\beta'$  coordinate system are shown in Figure 1, where each vector is represented by one dot.  $V_{ref}$  and  $V'_{ref}$  are the reference vectors in the  $\alpha\beta$  and  $\alpha'\beta'$  coordinate systems, respectively.

**Figure 1.** Space vector diagram for a 3-level inverter, (**a**) in the traditional  $\alpha\beta$  coordinate system, and (**b**) in the  $\alpha'\beta'$  coordinate system.

## 2.2. Profile of Zero CMV

For convenience, the normalized CMV of multilevel inverters is define as:

$$N = a + b + c \tag{2}$$

With the definition, the Equation (1) can be rewritten as follows:

$$\begin{bmatrix} a \\ b \\ c \end{bmatrix} = \begin{bmatrix} 1 & 0 & -1 \\ -1 & 1 & 0 \\ 1 & 1 & 0 \end{bmatrix}^{-1} \begin{bmatrix} \alpha' \\ \beta' \\ N \end{bmatrix} = \frac{1}{3} \begin{bmatrix} \alpha' - \beta' + N \\ \alpha' + 2\beta' + N \\ -2\alpha' - \beta' + N \end{bmatrix}$$

(3)

The normalized CMV can be eliminated by designing for N = 0, and the constraint is given by the following:

$$\beta' - \alpha' = -3a$$

$$2\beta' + \alpha' = 3b$$

$$\beta' + 2\alpha' = -3c$$

(4)

Since the three sub-equations in Equation (4) are linearly dependent, Equation (4) can be simplified as:

$$\begin{cases} \beta' - \alpha' = -3a\\ \beta' + 2\alpha' = -3c \end{cases}$$

(5)

As shown in Equation (5), the zero CMV of the multilevel inverter must be at the intersection of the two abovementioned equations.

For *n*-level multilevel inverters, the following additional constraints should be satisfied:

$$\begin{cases}

-n \le a \le n \\

-n \le b \le n \\

-n \le c \le n

\end{cases}$$

(6)

hence,

$$\begin{cases} |\alpha'| \le 2n \\ |\beta'| \le 2n \\ |\alpha' + \beta'| \le 2n \end{cases}$$

$$(7)$$

After some substations and manipulations, the boundary condition for zero CMV can be obtained as:

$$\begin{cases} -3n \le \beta' - \alpha' \le 3n \\ -3n \le 2\beta' + \alpha' \le 3n \\ -3n \le \beta' + 2\alpha' \le 3n \end{cases}$$

$$(8)$$

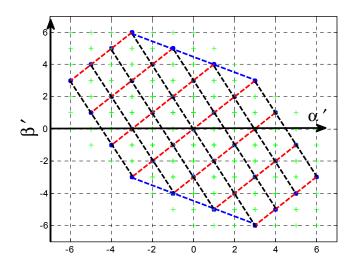

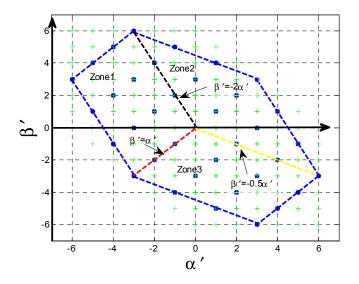

From Equations (5) and (8), the space vector diagram of zero CMV for 7-level multilevel inverters is plotted in Figure 2, where each star stands for a zero CMV vector.

Figure 2. Space vector diagram of a zero common-mode voltage (CMV) vectors for a 7-level multilevel inverter.

## 2.3. Detection of the Nearest Three CMV Vectors

As shown Figure 2, the space vector diagram composed of CMV vectors are very different from the classical space vector diagram. Hence, the location of the reference vector and the detection of the nearest three CMV vectors cannot be achieved with traditional reference vector location methods and classical vectors detection technologies [22]. In order to use the existing location methods and vectors detection technologies, the space vector diagram is divided into three zones, which are formed by the following three inequalities, respectively:

$$\begin{cases} \beta' > \alpha' \\ \beta' < -2\alpha' \end{cases}$$

(9)

$$\begin{cases} \beta' > -2\alpha' \\ \beta' > -0.5\alpha' \end{cases}$$

(10)

$$\begin{cases} \beta' < \alpha' \\ \beta' < -0.5\alpha' \end{cases}$$

(11)

The three zones in space vector diagram for a 7-level inverter are shown in Figure 3.

Based on the zone division in the space vector diagram, the location of the reference vector and the detection of the nearest three CMV vectors can be made with existing location methods and vectors detection technologies.

If the reference vector is in zone 1, the four adjacent vectors  $V_0-V_3$  around the reference vector can be calculated as:

$$\begin{cases}

V_{0} = [floor(\alpha'_{r})floor(\beta'_{r})] = [\alpha'_{0}\beta'_{0}] \\

V_{1} = [floor(\alpha'_{r}) + 2floor(\beta'_{r}) - 1] = [\alpha'_{0} + 2\beta'_{0} - 1] \\

V_{2} = [floor(\alpha'_{r}) + 1floor(\beta'_{r}) - 2] = [\alpha'_{0} + 1\beta'_{0} - 2] \\

V_{3} = [floor(\alpha'_{r}) + 1floor(\beta'_{r}) + 1] = [\alpha'_{0} + 1\beta'_{0} + 1]

\end{cases}$$

(12)

where  $\alpha'_r$  and  $\beta'_r$  are the normalized three phase voltages of the reference vector. The floor function rounds towards negative infinity.

Figure 3. Three zones in a space vector diagram for an 11-level inverter.

Because  $V_0$  and  $V_1$  are always two of the nearest three vectors, the third vector  $V_{sel}$  can be obtained by:

if

$$\beta'_r + 0.5 \cdot \alpha'_r \le 1.5(N_1 + N_2)$$

then  $V_{sel} = V_2$

else  $V_{sel} = V_3$  (13)

where  $N_1 = \text{ceil}((\beta'_r - \alpha'_r)/3)$ ,  $N_2 = \text{floor}((\beta'_r + 2\alpha'_r)/3)$ . The ceil function rounds towards positive infinity.

If the third vector was  $V_2$ , the duty cycles of the three vectors are calculated as:

$$\begin{cases} d_{V0} = (\alpha'_r - \beta'_r + 3N_1)/3\\ d_{V1} = (\alpha'_r + 2\beta'_r - 3N_2 - 3N_1)/3\\ d_{V2} = (1 - d_{V0} - d_{V1}) \end{cases}$$

(14)

And, if the third vector was  $V_3$ , the duty cycles of the three vectors are obtained from:

$$\begin{cases} d_{V0} = (2\alpha'_r + \beta'_r + 3N_2)/3\\ d_{V1} = (-\alpha'_r - 2\beta'_r + 3N_2 + 3N_1)/3\\ d_{V3} = (1 - d_{V0} - d_{V1}) \end{cases}$$

(15)

By following the above mentioned steps, the location of the reference vector and the detection of the nearest three CMV vectors in zone 2 and in zone 3 can be obtained easily.

After the CMV vector is selected, the realization of the CMV vectors is obtained from:

$$\begin{cases} a = (\alpha' + \beta')/3 \\ b = a + \beta' \\ c = a - \alpha' \end{cases}$$

(16)

Without complicated calculations, the realization of the CMV vectors is calculated.

Clearly, the location of the reference vector, detection of the nearest three CMV vectors, duty cycles, and realization of the CMV vectors are all obtained by simple calculations, and no lookup table is needed. Hence, the proposed SVPWM is computationally fast.

## 3. Experimental Results

## 3.1. Experimental Setup

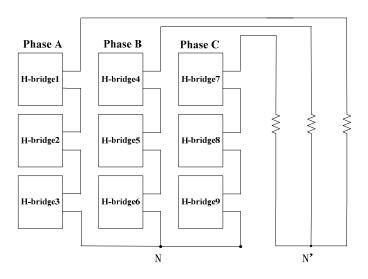

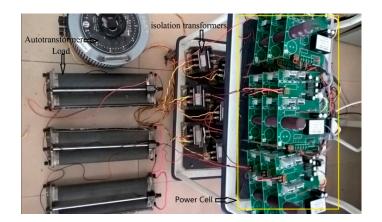

A 7-level cascaded multilevel inverter was built in the laboratory, as shown in Figure 4. Nine isolation DC powers for the 7-level inverter were formed by nine 200 W isolation transformers and diode rectifier bridges. The dc-bus voltage of power cells was selected to be 50 V. The model of switches in the inverter was IRFP460, and the driver circuits for the switches were a compound of a high-speed opt-coupler (model: 6N137) and IR2110. The 7-level inverter was controlled by a TMS320F28335 floating-point digital signal processor (DSP) from Texas Instruments. The experimental setup is shown in Figure 5.

Figure 4. 7-level cascaded multilevel inverter.

Figure 5. Experimental setup.

## 3.2. Experimental Results

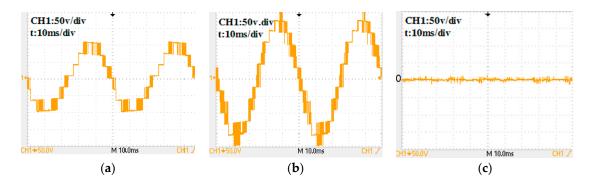

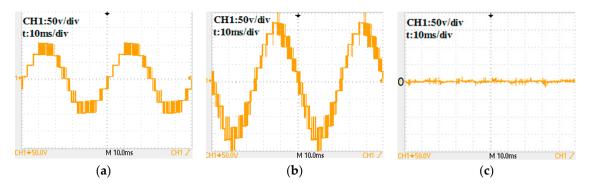

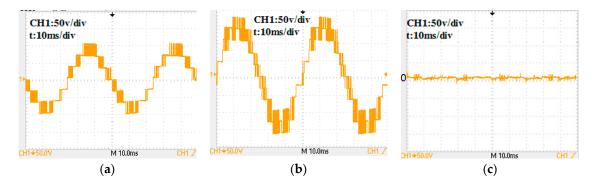

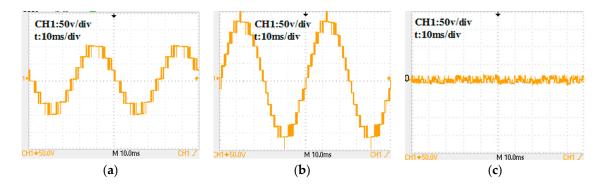

The waveforms, including phase voltage, line-to-line voltage and CMV, with different modulation indices are presented in Figures 6–8, respectively. In these figures, the fundamental frequency of the output voltage is 20 Hz, and there are 84 sampling points in a working period. The modulation index m is equal to 0.868, 0.797 and 0.707, respectively.

Figure 6. Experimental waves with m = 0.868: (a) phase voltage; (b) line-to-line voltage; (c) CMV.

Figure 7. Experimental waves with m = 0.791: (a) phase voltage; (b) line-to-line voltage; (c) CMV.

Figure 8. Experimental waves with m = 0.707: (a) phase voltage; (b) line-to-line voltage; (c) CMV.

As can be seen from the waveforms, the CMV of the cascaded multilevel inverter is kept at zero with any modulation index when the proposed SVPWM is adopted.

## 3.3. Comparison with Prior PWMs

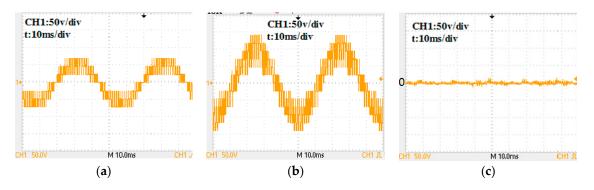

The waveforms of phase voltage, line-to-line voltage and CMV for a 7-level inverter by traditional CMV limiting SVPWM [15] and CMV eliminating PWM [20] are shown in Figures 9 and 10, respectively. In Figures 9 and 10, the fundamental frequency of the output voltage is 20 Hz, there are 84 sampling points in a working period, and the modulation index is 0.868.

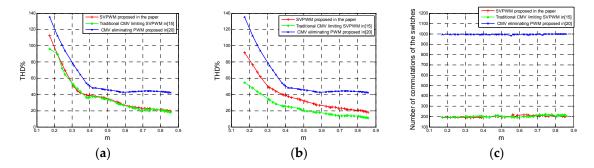

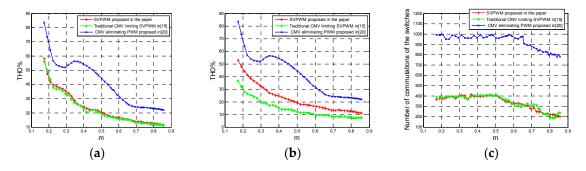

The THD of phase voltage, line-to-line voltage and the number of commutations of the switches for a 7-level multilevel and an 11-level multilevel with different modulation indexes for the three PWMs are shown in Figures 11 and 12, respectively.

**Figure 9.** Experimental waves by traditional CMV-limiting SVPWM proposed in Reference [15] for a 7-level inverter: (**a**) phase voltage; (**b**) line-to-line voltage; (**c**) CMV.

**Figure 10.** Experimental waves by a CMV-eliminating PWM proposed in Reference [20] for a 7-level inverter: (**a**) phase voltage; (**b**) line-to-line voltage; (**c**) CMV.

**Figure 11.** Comparison of the three PWMs in a 7-level inverter with different modulation indices: (a) THD of phase voltage; (b) THD of line-to-line voltage; (c) the number of commutations of switches.

**Figure 12.** Comparison of the three PWMs mentioned above in an 11-level inverter with different modulation indices: (**a**) THD of phase voltage; (**b**) THD of line-to-line voltage; (**c**) the number of commutations of switches.

As shown in Figures 9 and 10, while the CMV of multilevel inverters can be limited to 1/3 of the dc-bus voltage of power cells by traditional CMV-limiting SVPWM, the CMV of multilevel inverters can be eliminated by the proposed SVPWM.

It is shown in Figures 11 and 12 that the THD of the phase voltage by the SVPWM proposed in this paper is almost exactly the same as the THD of the phase voltage by the traditional CMV-limiting SVPWM, and similar findings have been obtained for the number of commutations of the switches by the two SVPWMs as well. This is because the reference vector is synthesized with the three nearest vectors in both of these SVPWMs.

However, the THD of line-to-line voltage by the proposed SVPWM is higher than that by the traditional CMV-limiting SVPWM. This is because the distance between the selected vectors in the proposed SVPWM is longer than that in the traditional SVPWM. Because the distances between the three selected vectors decrease with the increasing of the number of level, the difference of the THD of line-to-line voltage becomes smaller.

Although the CMV can be eliminated by the CMV-eliminating PWM proposed in Reference [20], the PWM is still a carrier modulation. This makes the THD of phase voltage, the THD of line-to-line voltage and the number of commutations of the switches higher than those achieved by the proposed SVPWM.

## 4. Conclusions

A new SVPWM to eliminate common-mode voltages for multilevel inverters is proposed in this paper. The proposed SVPWM is performed in the  $\alpha'\beta'$  coordinate system. Based on the constraints of zero CMVs in the  $\alpha'\beta'$  coordinate system, the nearest three vectors are selected and their duty cycles are calculated by simple calculations. Experimental results for a 7-level inverter verified the proposed SVPWM. The proposed SVPWM scheme has the following significant advantages compared with prior SVPWM schemes:

- (1) Switching states and duty cycles are all obtained by simple calculations, and the SVPWM is computationally fast.

- (2) Compared to earlier PWMs, the realization of the CMV vectors is very simple.

- (3) CMVs of multilevel inverters are limited to zero, and the SVPWM works well with any modulation index.

- (4) The proposed SVPWM is suitable for any level inverter. A more detailed comparison between the proposed SVPWM and prior PWMs is given. The advantages of this SVPWM make it a preferred SVPWM for the elimination of the common-mode voltages of multilevel inverters.

Acknowledgments: This work was supported by Guangdong Provincial Science and Technology Project under grant number 2015B020238013, and Guangdong Provincial Natural Science Foundation Project under grant number 2015A030313487.

**Author Contributions:** Xiongmin Tang wrote the paper and performed the experimental work; Chengjing Lai contributed to the writing and arranging of the analytical data; Zheng Liu contributed to perform the simulation work. Miao Zhang contributed to providing reagents/materials/analysis tools and supervised the paper.

Conflicts of Interest: The authors declare no conflict of interest.

## References

- 1. Rodriguez, J.; Lai, J.S.; Peng, F.Z. Multilevel inverters: A survey of topologies, controls, and applications. *IEEE Trans. Ind. Electron.* **2002**, *49*, 724–738.

- Cai, X.J.; Wu, Z.X.; Wang, S.X. Phase-Shifted Carrier Pulse Width Modulation Based on Particle Swarm Optimization for Cascaded H-bridge Multilevel Inverters with Unequal DC Voltages. *Energies* 2015, *8*, 9670–9687.

- 3. Ravikant, P.; Tripathi, R.N.; Hanamoto, T. Comprehensive analysis of LCL filter interfaced cascaded h-bridge multilevel inverter-based DSTATCOM. *Energies* **2017**, *10*, 346.

- 4. Binojkumar, A.C.; Narayanan, G. A variable switching frequency PWM technique for induction motor drive to spread acoustic noise spectrum with reduced current ripple. *IEEE Trans. Ind. Appl.* **2016**, *52*, 3927–3938.

- 5. Busse, D.; Erdman, J.; Kerkman, R.J.; Schlegel, D.; Skibinski, G. Bearing currents and their relationship to PWM drivers. *IEEE Trans. Power Electron.* **1997**, *33*, 577–585.

- 6. Zhang, Y.C.; Gao, J.H.; Qu, C.Q. Relationship between two direct power control methods for PWM rectifiers under unbalanced network. *IEEE Trans. Power Electron.* **2017**, *32*, 4084–4094.

- Chen, X.; Xu, D.; Liu, F.; Zhang, J. A novel inverter-output passive filter for reducing both differential-and common-mode dv/dt at the motor terminal in PWM drivers systems. *IEEE Trans. Ind. Electron.* 2007, 54, 419–426.

- 8. Swamy, M.M.; Yamada, K.; Kume, T. Common mode current attenuation techniques for use with PWM drives. *IEEE Trans. Power. Electron.* **2001**, *16*, 248–255.

- 9. Akagi, H.; Doumoto, T. An approach to eliminate high-frequency shaft voltage and ground leakage current from an inverter-driven motor. *IEEE Trans. Ind. Appl.* **2004**, *40*, 1162–1169.

- 10. Kim, H.J.; Lee, H.D.; Sul, S.K. A new PWM strategy for common-mode voltage reduction in neutral-point-clamped inverter-fed ac motor drivers. *IEEE Trans. Ind. Appl.* **2001**, *37*, 1840–1845.

- 11. Zhang, H.; Jouance, A.V.; Dai, S.; Wallce, A.K.; Wang, F. Multi-level inverter modulation schemes to eliminate common-mode voltage. *IEEE Trans. Ind. Appl.* **2000**, *36*, 1645–1653.

- 12. Wu, X.; Tan, G.J.; Ye, Z.B.; Li, Y.; Xu, S.Z. Optimized common-mode voltage reduction PWM for three-phase voltage-source inverters. *IEEE Trans. Power Electron.* **2016**, *31*, 2959–2969.

- Basu, K.; Umarikar, A.C.U.; Mohapatra, K.K.; Mohan, N. High-frequency transformer-link three-level inverter drive with common-mode voltage elimination. In Proceedings of the IEEE Power Electronics Specialists Conference, Rhodes, Greece, 15–19 June 2008; pp. 4413–4418.

- Chiasson, J.N.; Ozpineci, B.; Tolbert, L.M. A five-level three-phase hybrid cascade multilevel inverter using a single-dc source for a PM synchronous motor drive. In Proceedings of the APEC 2007-Twenty Second Annual IEEE Applied Power Electronics Conference, Anaheim, CA, USA, 25 February–1 March 2007; pp. 1504–1507.

- 15. Gupta, A.K.; Khambadkone, A.M. A space vector modulation scheme to reduce common-mode voltage for cascaded multilevel inverters. *IEEE Trans. Power. Electron.* **2007**, 22.

- Mehrasa, M.; Pouresmaeil, E.; Zabihi, S.; Caballero, J.C.T.; Catalão, J.P.S. A Novel Modulation Function-Based Control of Modular Multilevel Converters for High Voltage Direct Current Transmission Systems. *Energies* 2016, 9, 867.

- 17. Moranchel, M.; Huerta, F.; Sanz, I.; Bueno, E.; Rodríguez, F.J. A Comparison of Modulation Techniques for Modular Multilevel Converters. *Energies* **2016**, *9*, 1091.

- Bang, N.L.H.; Nho, N.V.; Tam, N.K.T.; Dung, N.M. A phase shift PWM technique for common-mode voltage reduction in five level H-bridge cascaded inverter. In Proceedings of the 2014 International Conference and Utility Exhibition on Green Energy for Sustainable Development (ICUE), Pattaya, Thailand, 19–21 March 2014; pp. 1–7.

- 19. Rodriguez, J.; Pontt, J.; Correa, P.; Cortes, P.; Silva, C. A new modulation method to reduces common-mode voltages in multilevel inverters. *IEEE Trans. Ind. Electron.* **2004**, *51*, 834–839.

- 20. Wang, C.; Zhang, Y.; Tang, X.M.; Cheng, S.Z. Rapid and generalised space vector modulation algorithm for cascaded multilevel converter based on zero-order voltage constraint. *IET Power Electron.* **2016**, *9*, 989–996.

- Shu, Z.L.; Ding, N.; Chen, J.; Zhu, H.F.; He, X.Q. Multilevel SVPWM With DC-Link capacitor voltage balancing control for diode-clamped multilevel converter based STATCOM. *IEEE Trans. Ind. Electron.* 2013, 60, 1884–1896.

- 22. Celanovic, N.; Boroyevich, D. A fast space-vector modulation algorithm for multilevel three-phase converters. *IEEE Trans. Ind. Appl.* **2001**, *37*, 637–641.

© 2017 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).