A Switching Frequency Optimized Space Vector Pulse Width Modulation (SVPWM) Scheme for Cascaded Multilevel Inverters

Abstract

:1. Introduction

- (1)

- Locate the reference voltage vector and select three nearest space vectors.

- (2)

- Calculate the duty cycles for the three space vectors.

- (3)

- Generate the switching sequences with specific constraint.

2. Basic Switching Modes and Switching Paths

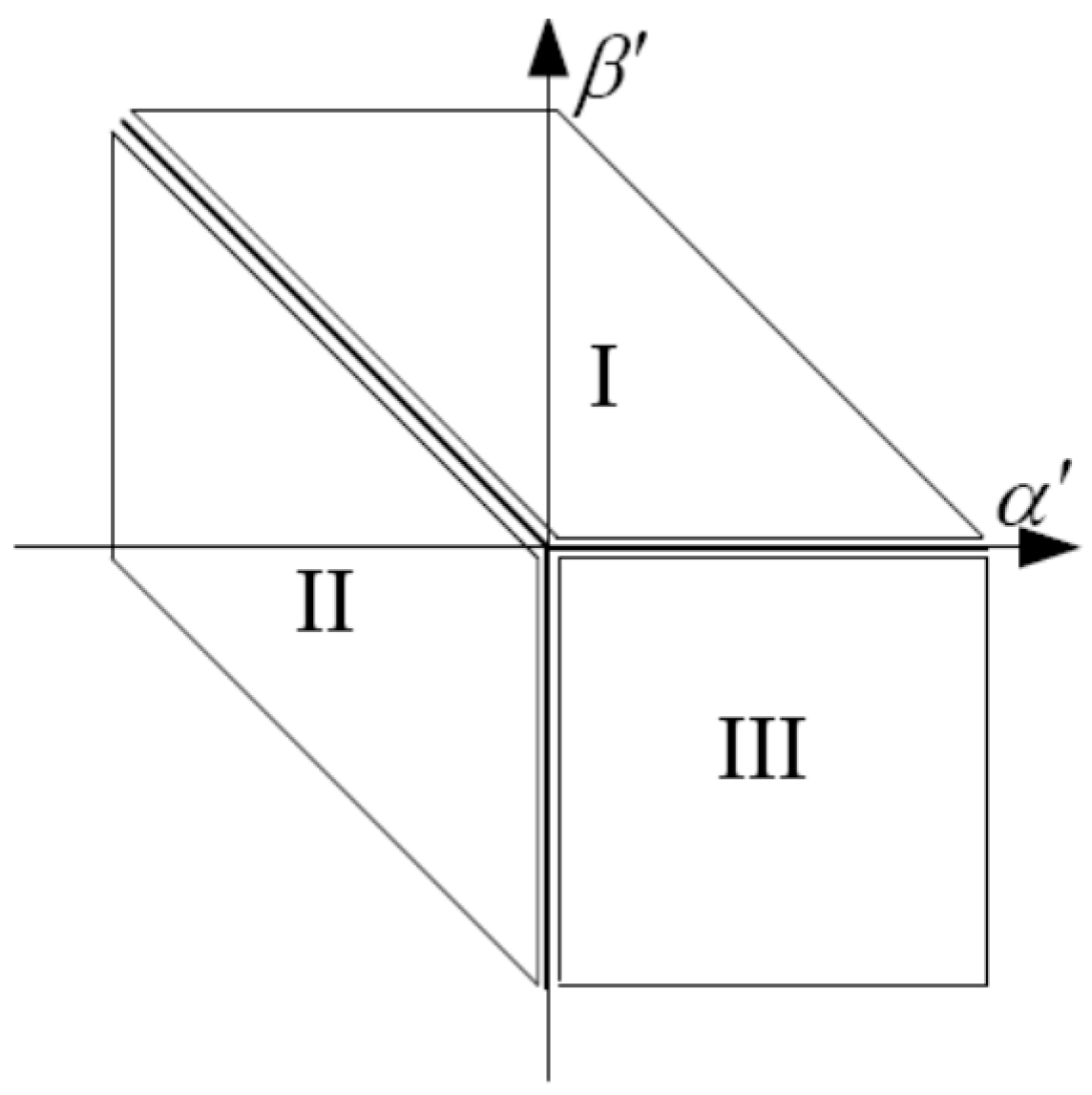

2.1. α′β′ Coordinate System

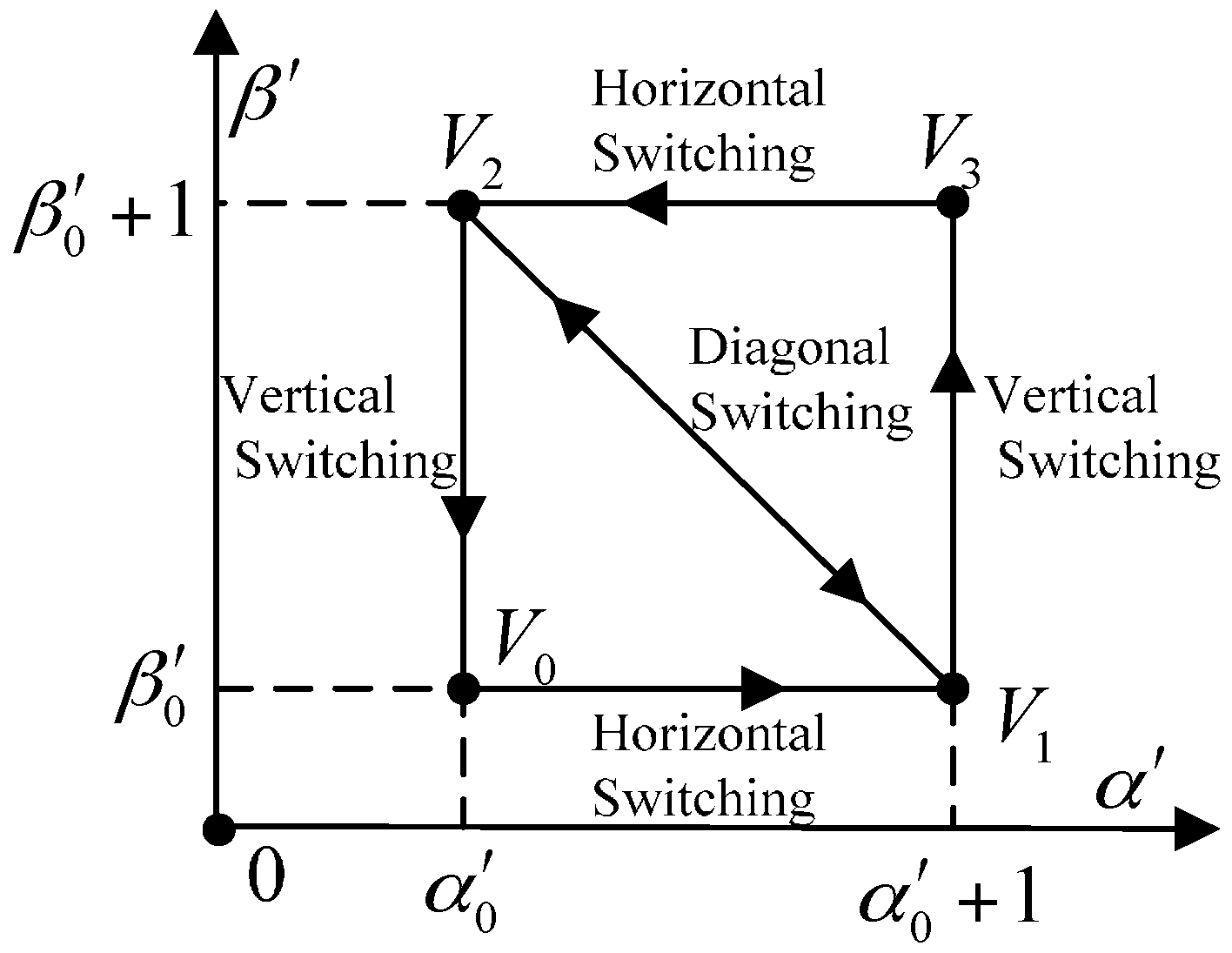

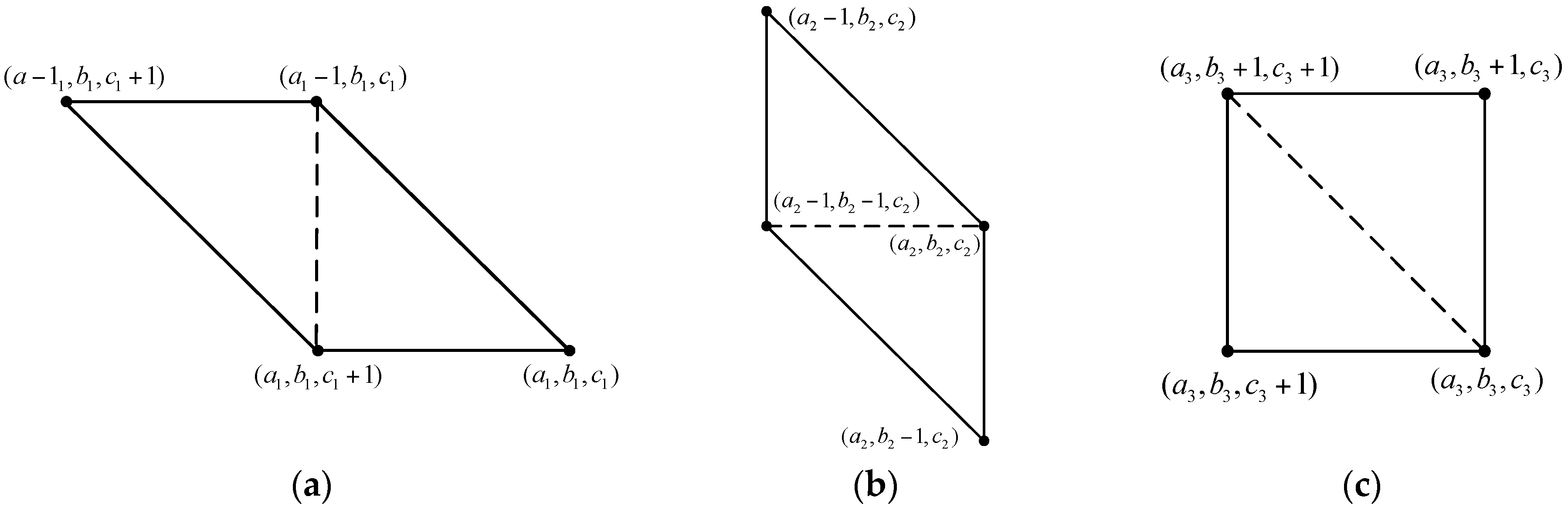

2.2. Three Basic Switching Modes

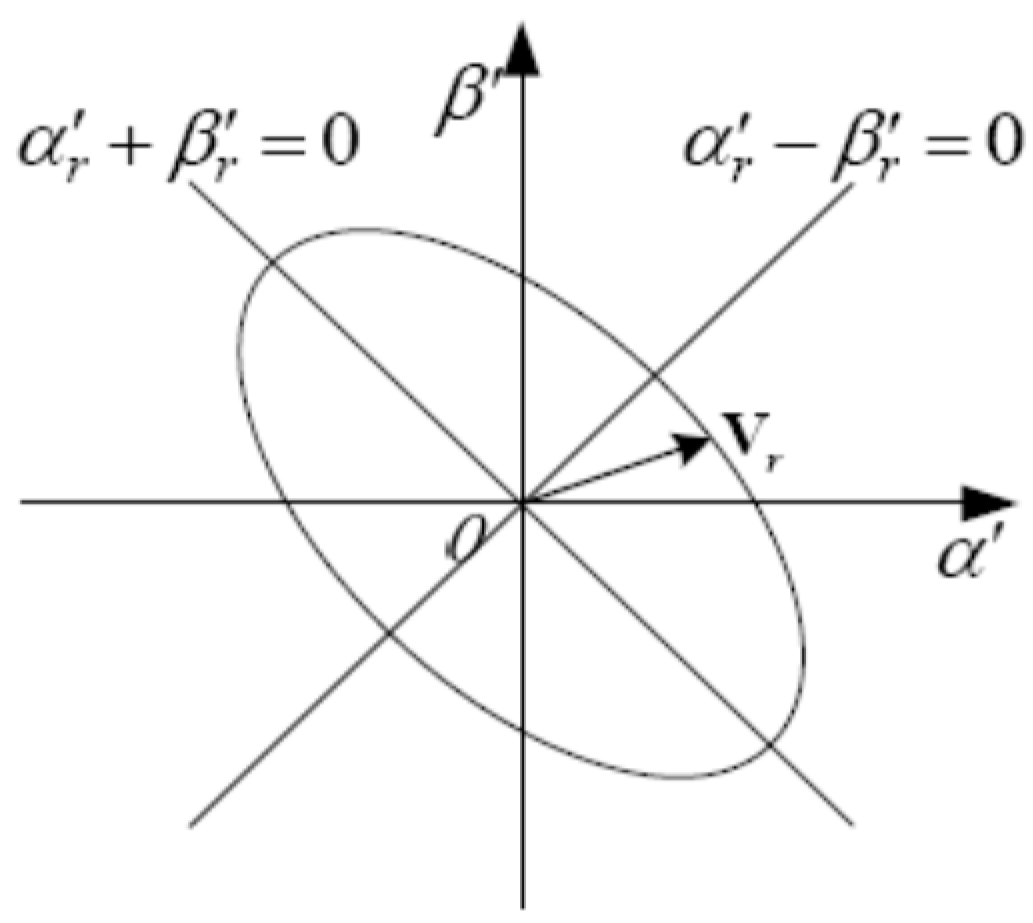

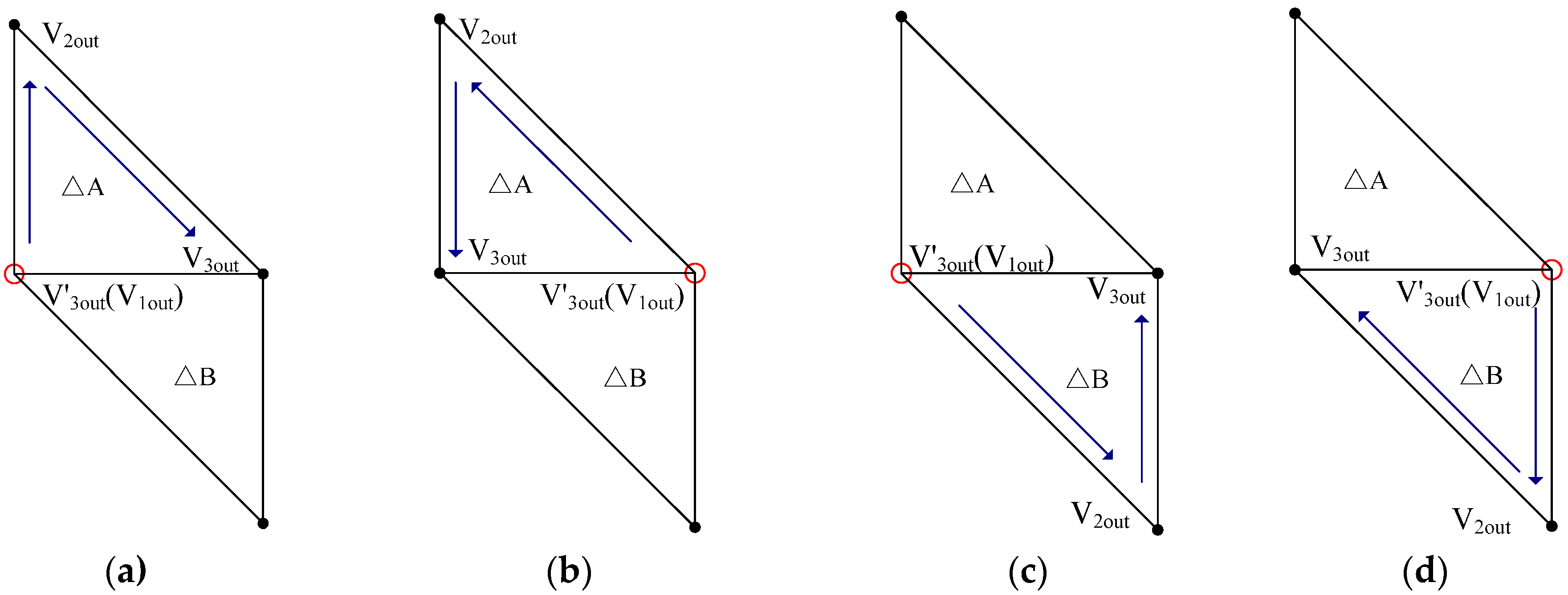

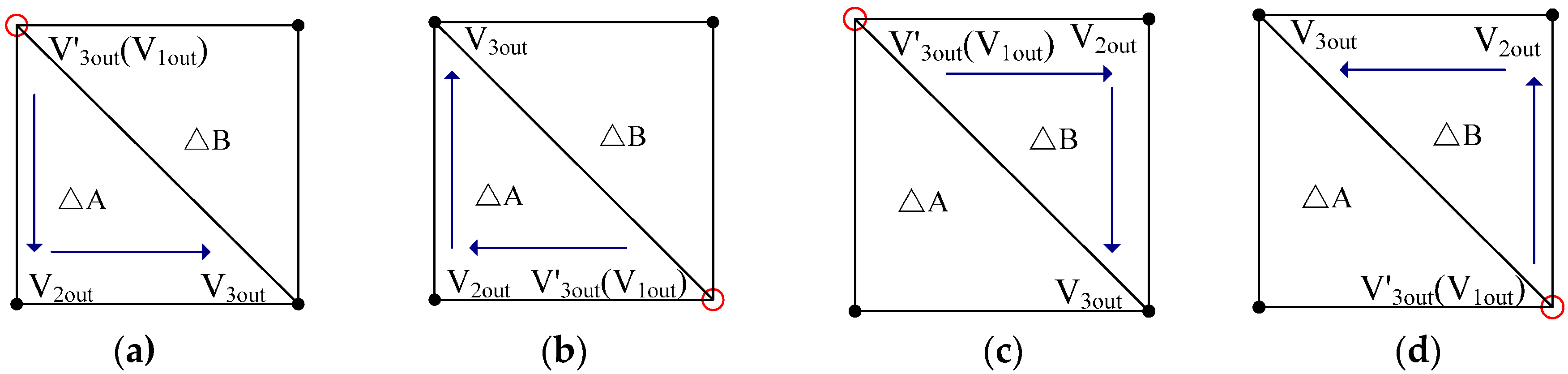

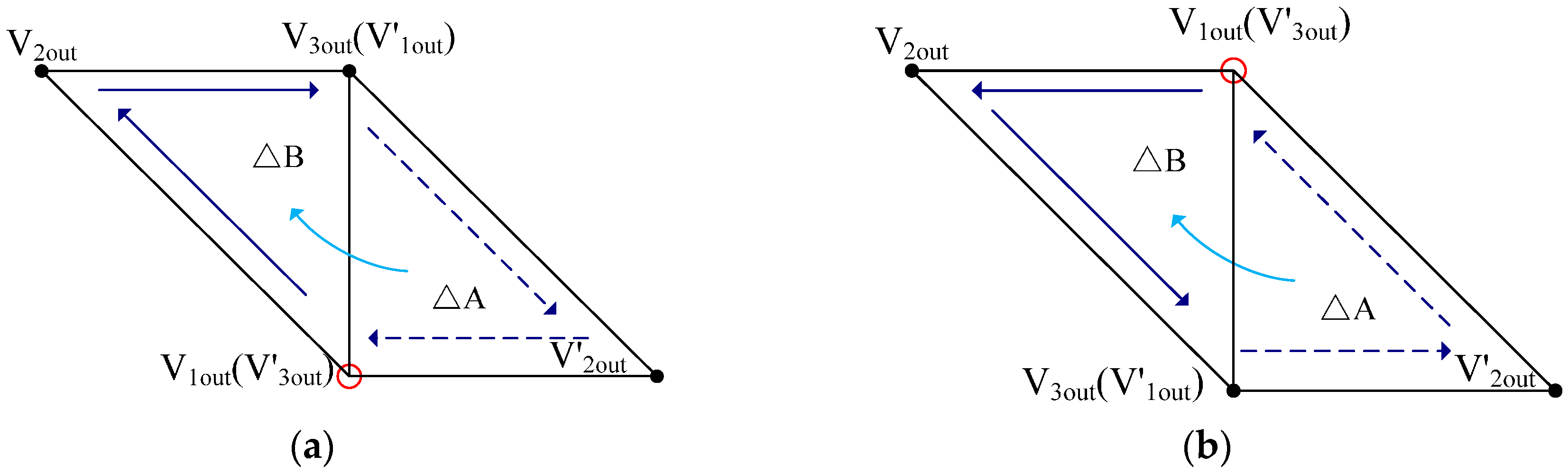

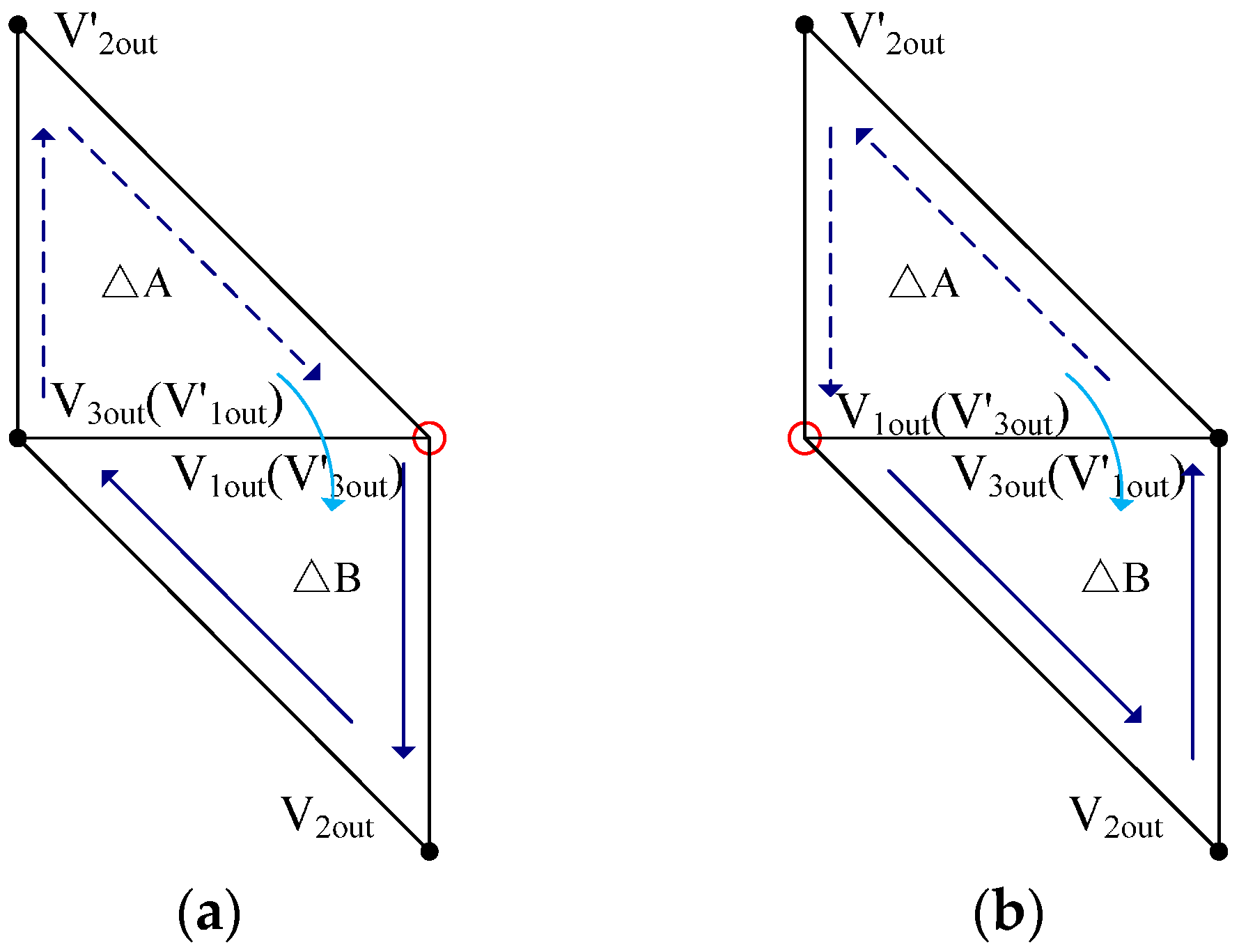

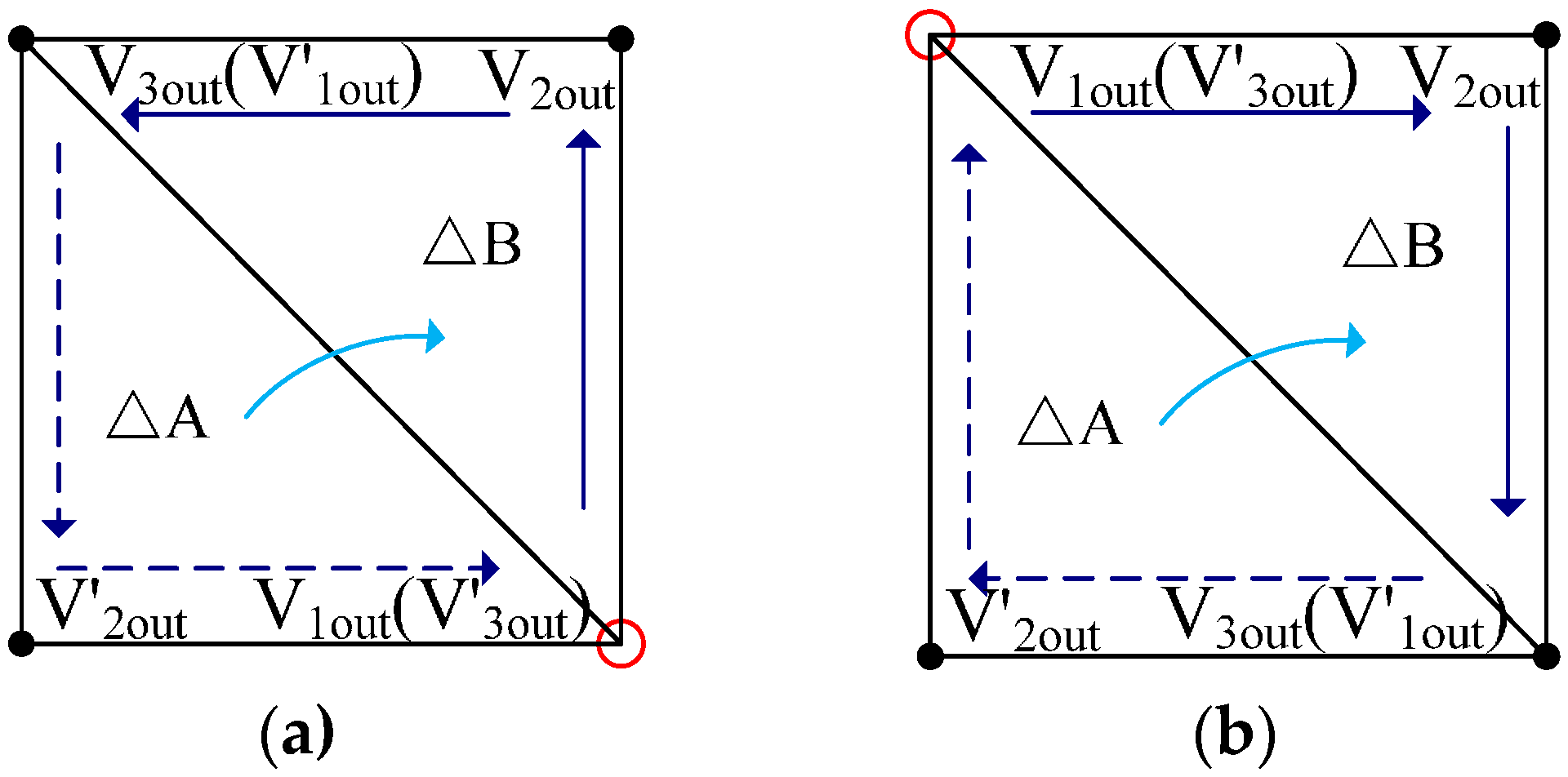

2.3. Characteristics of Switching Paths

3. The Proposed SVPWM Scheme

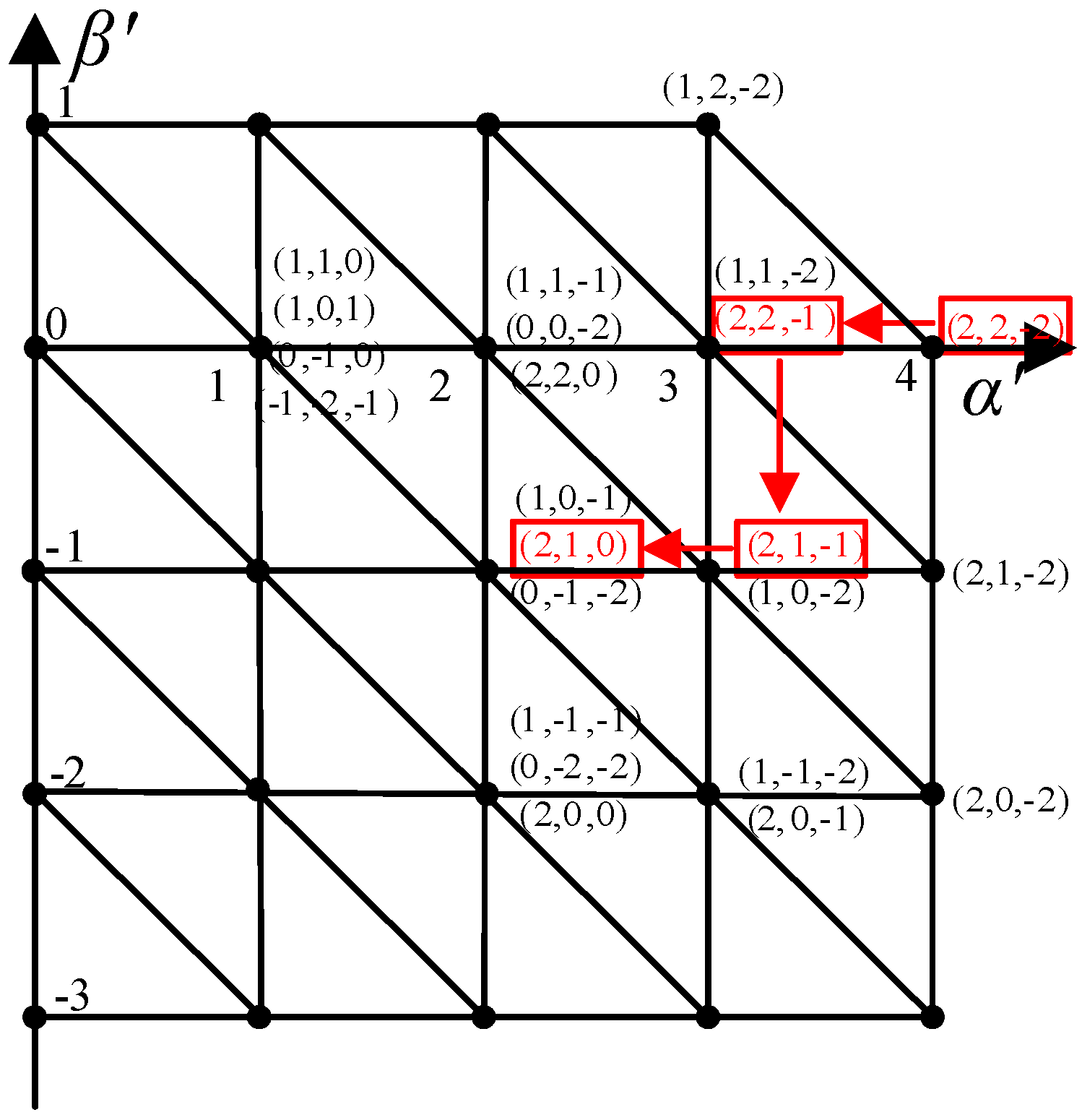

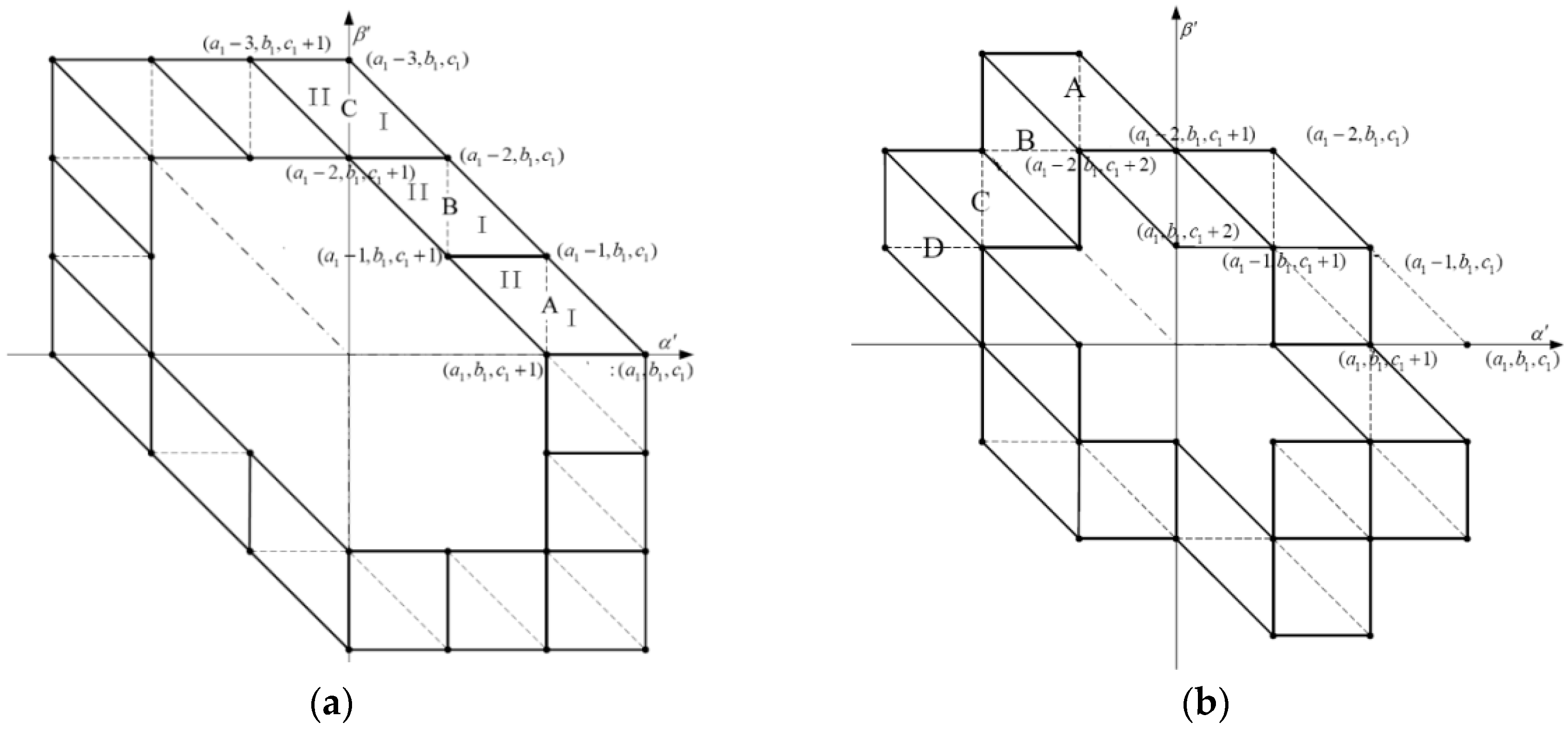

3.1. Trajectory and Traversing Graphs of Reference Voltage Vector

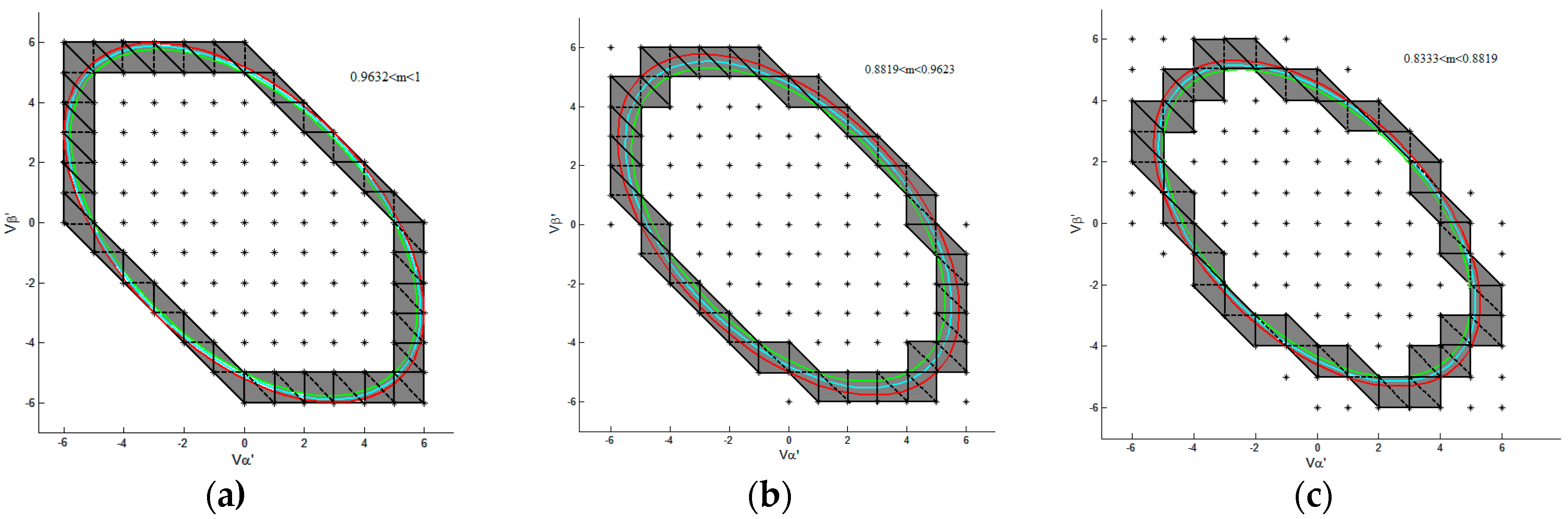

3.2. Switching Path Planning

3.2.1. Switching Paths in a Triangle

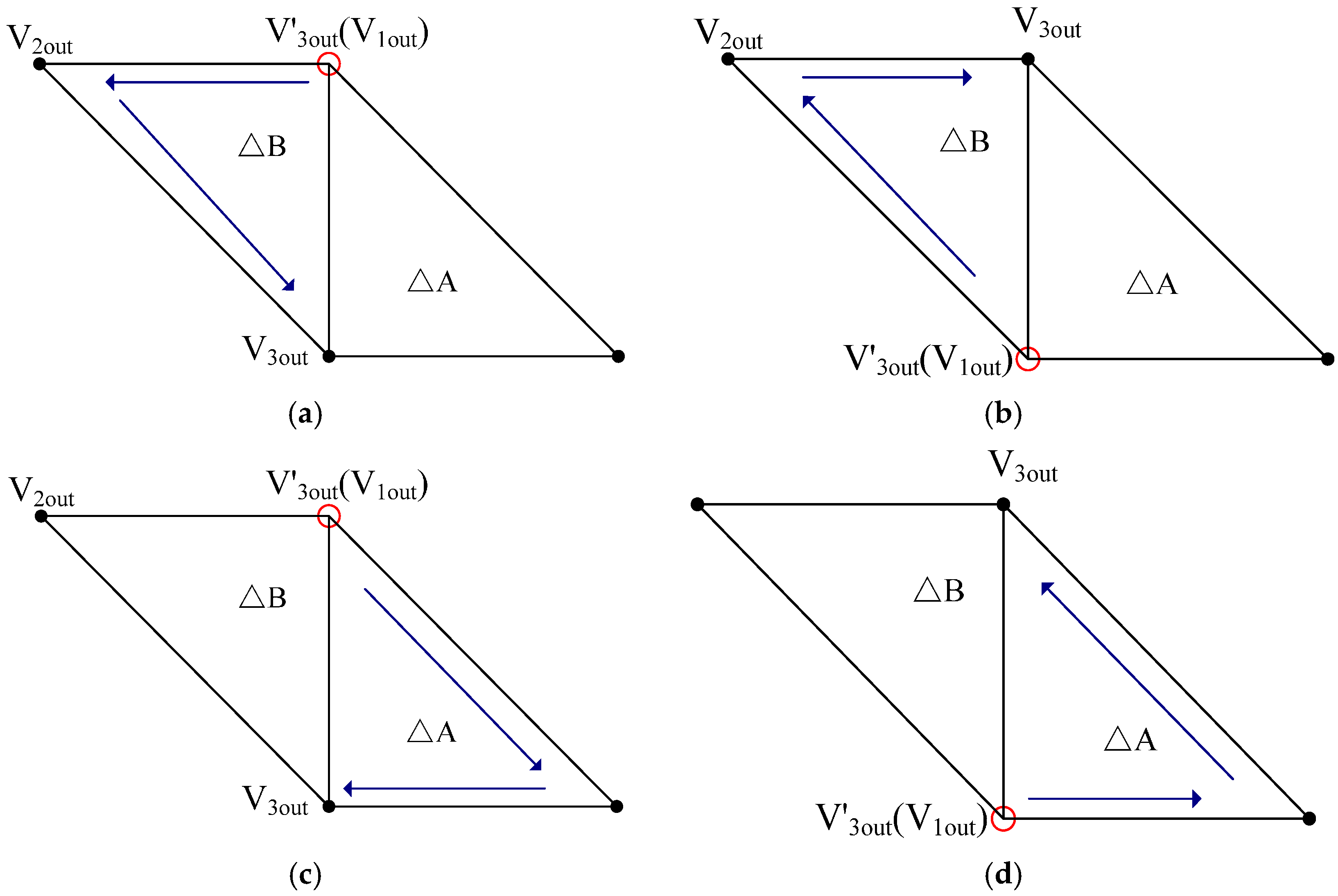

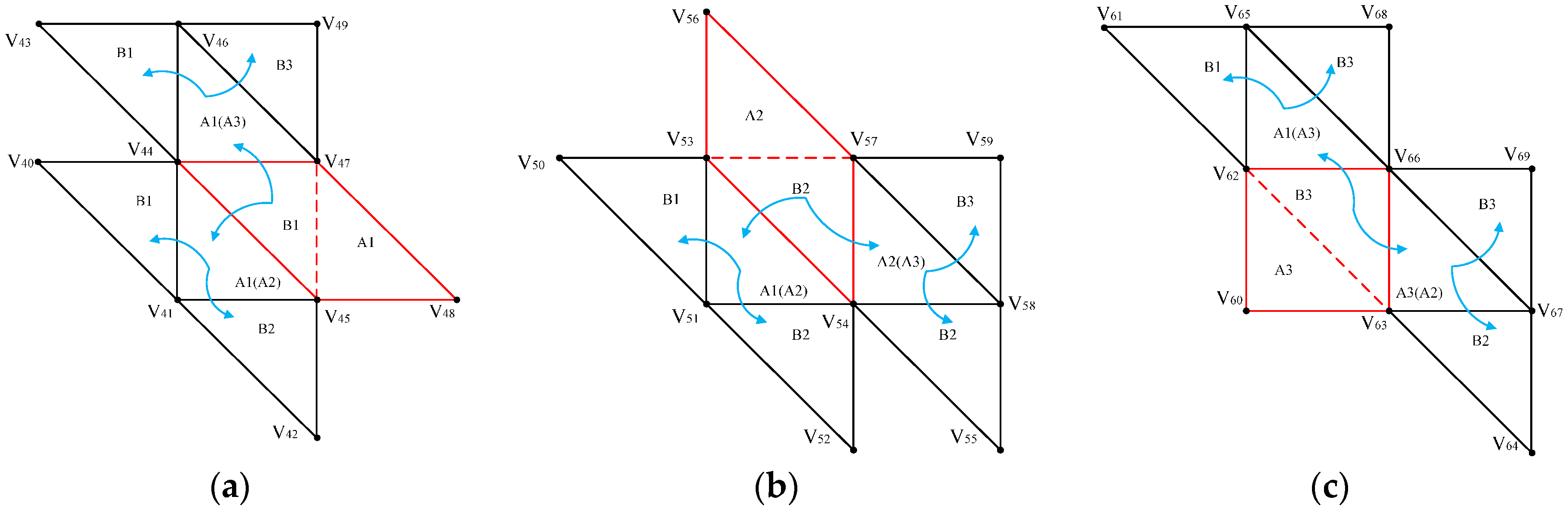

3.2.2. Switching Paths not In a Triangle but in a Quadrilateral

3.2.3. Switching Paths between Quadrilaterals

3.3. Realization of Vectors

3.3.1. Realization of the First Vector

3.3.2. Realization of Other Vectors

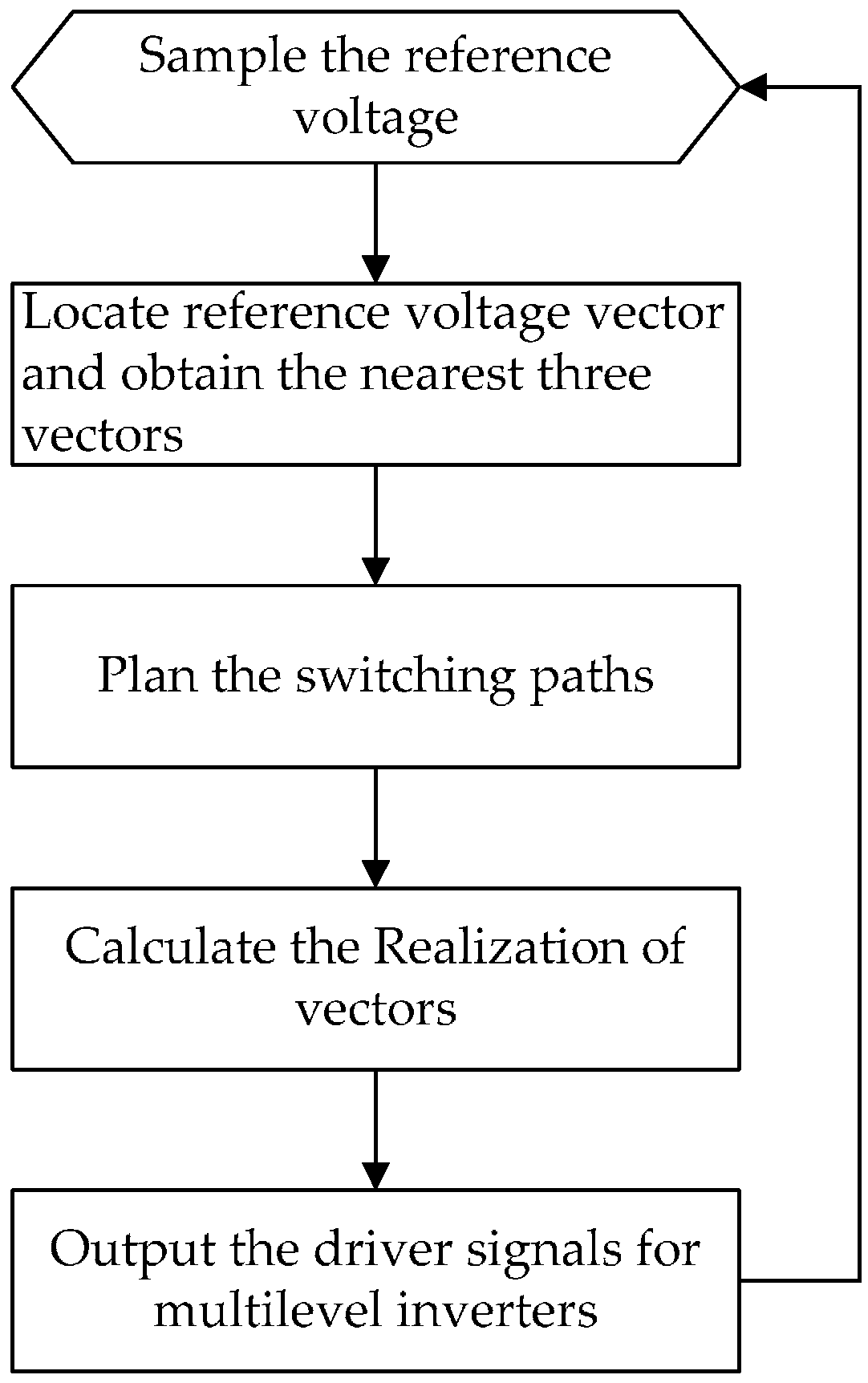

3.4. Flowchart of the Implementation of the SVPWM Scheme

4. Experimental Results

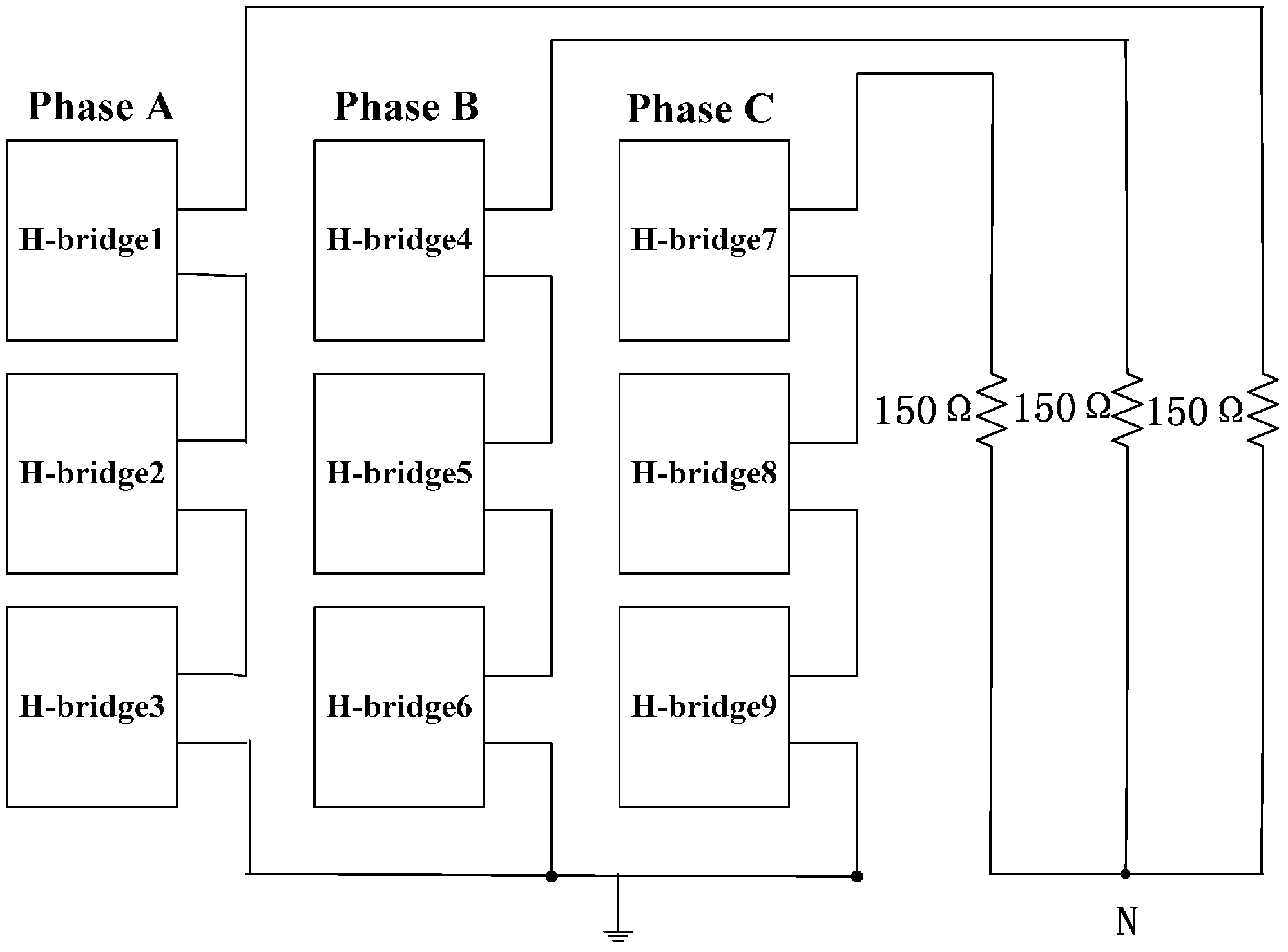

4.1. Experimental Setup

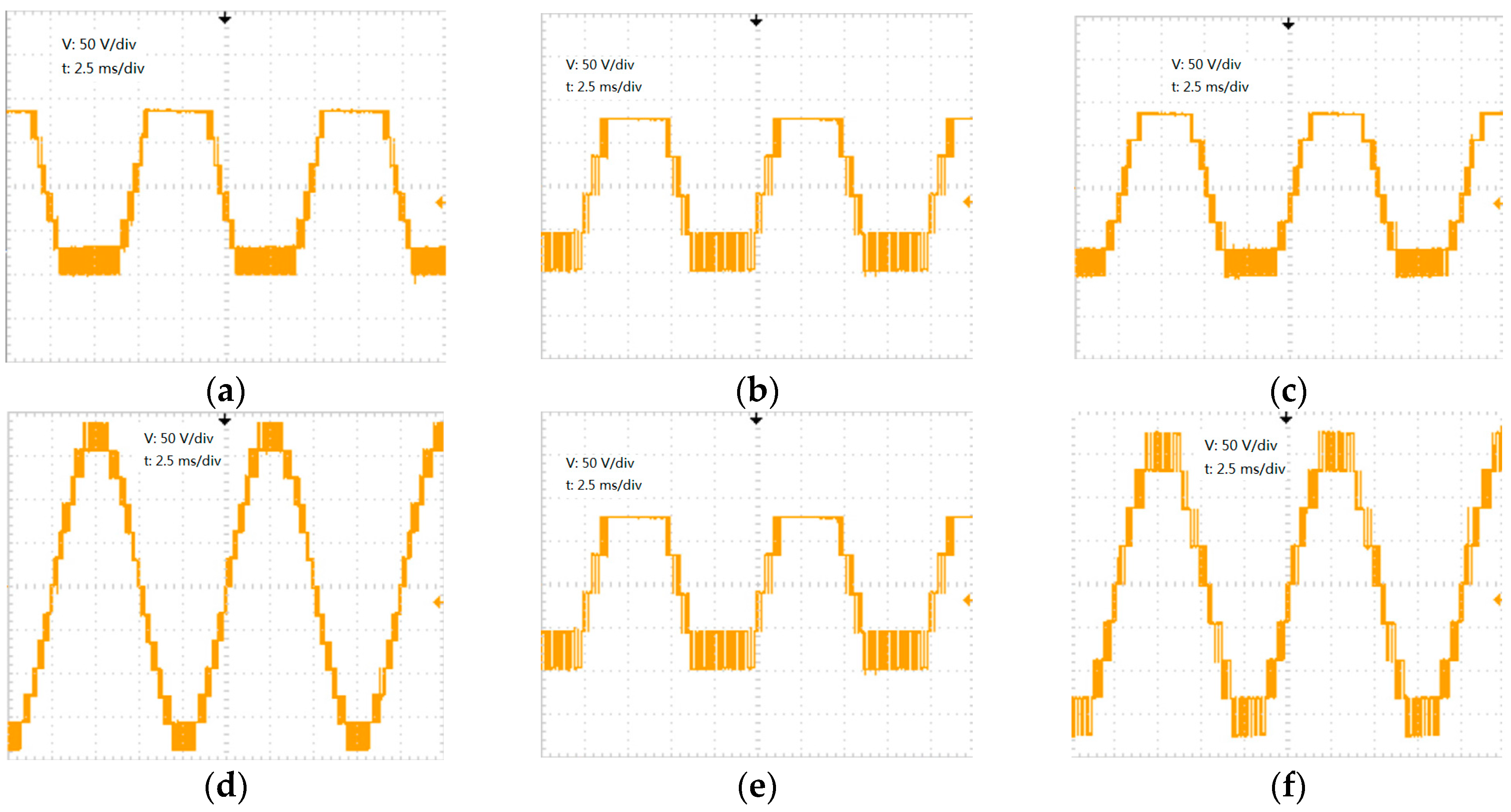

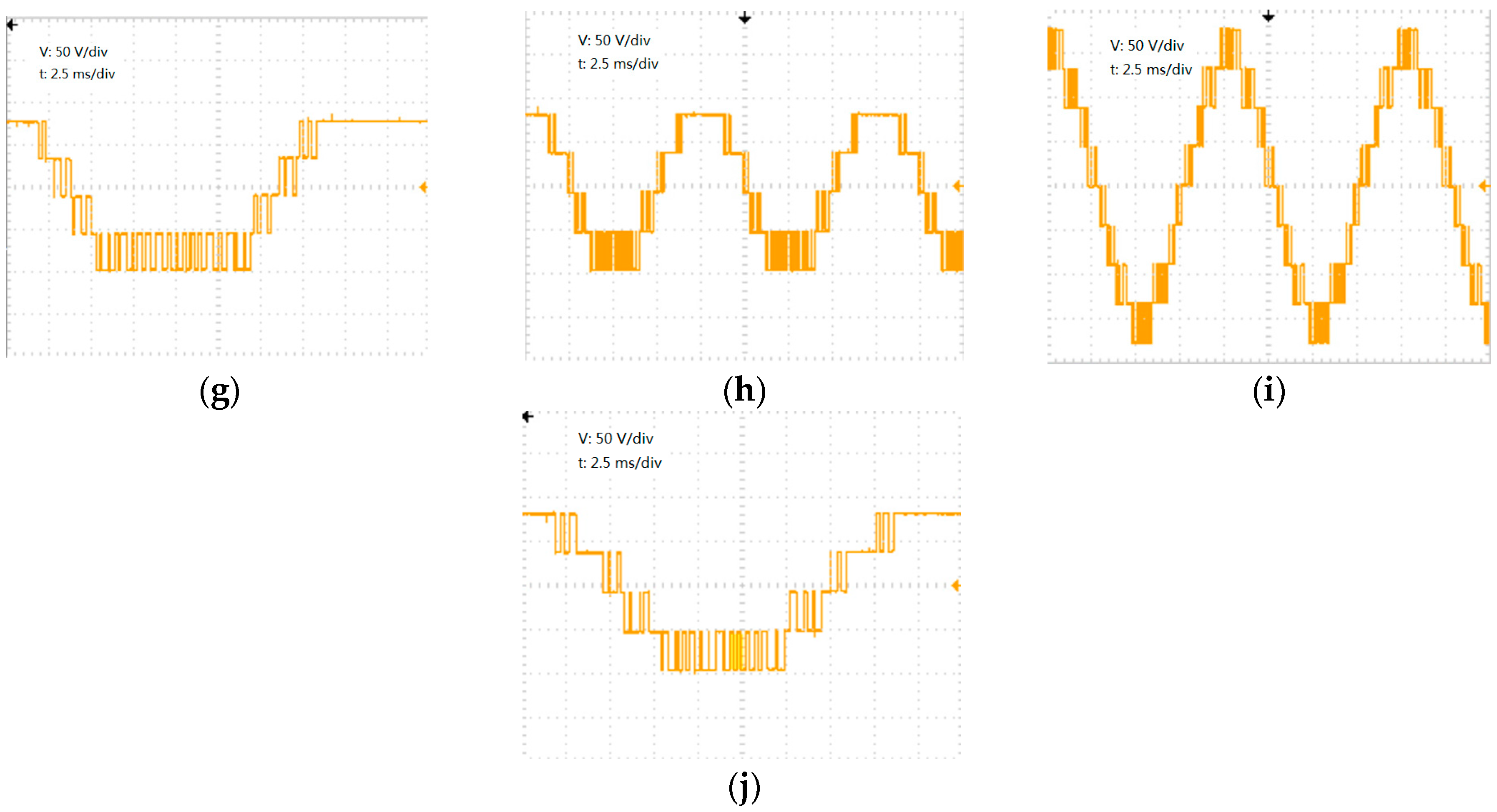

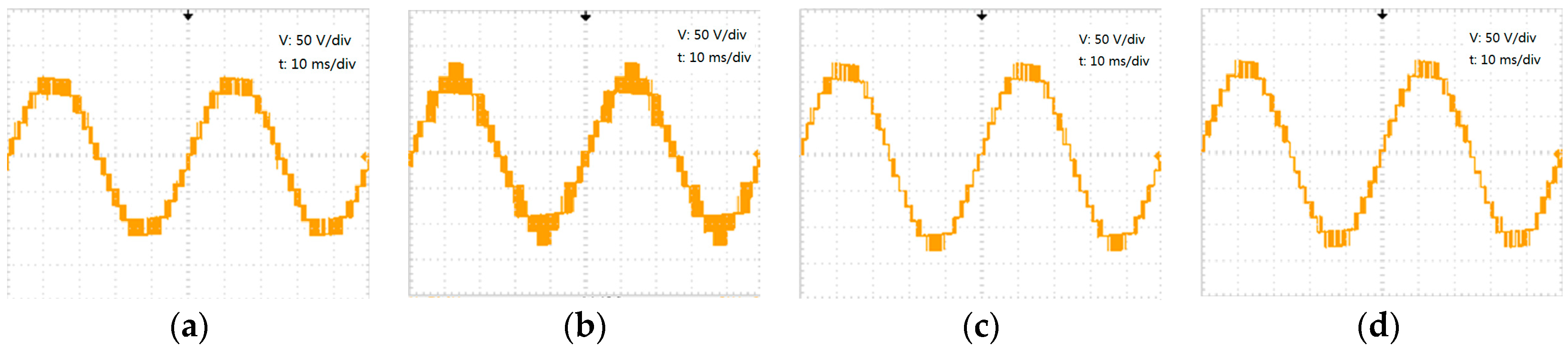

4.2. Experimental Results

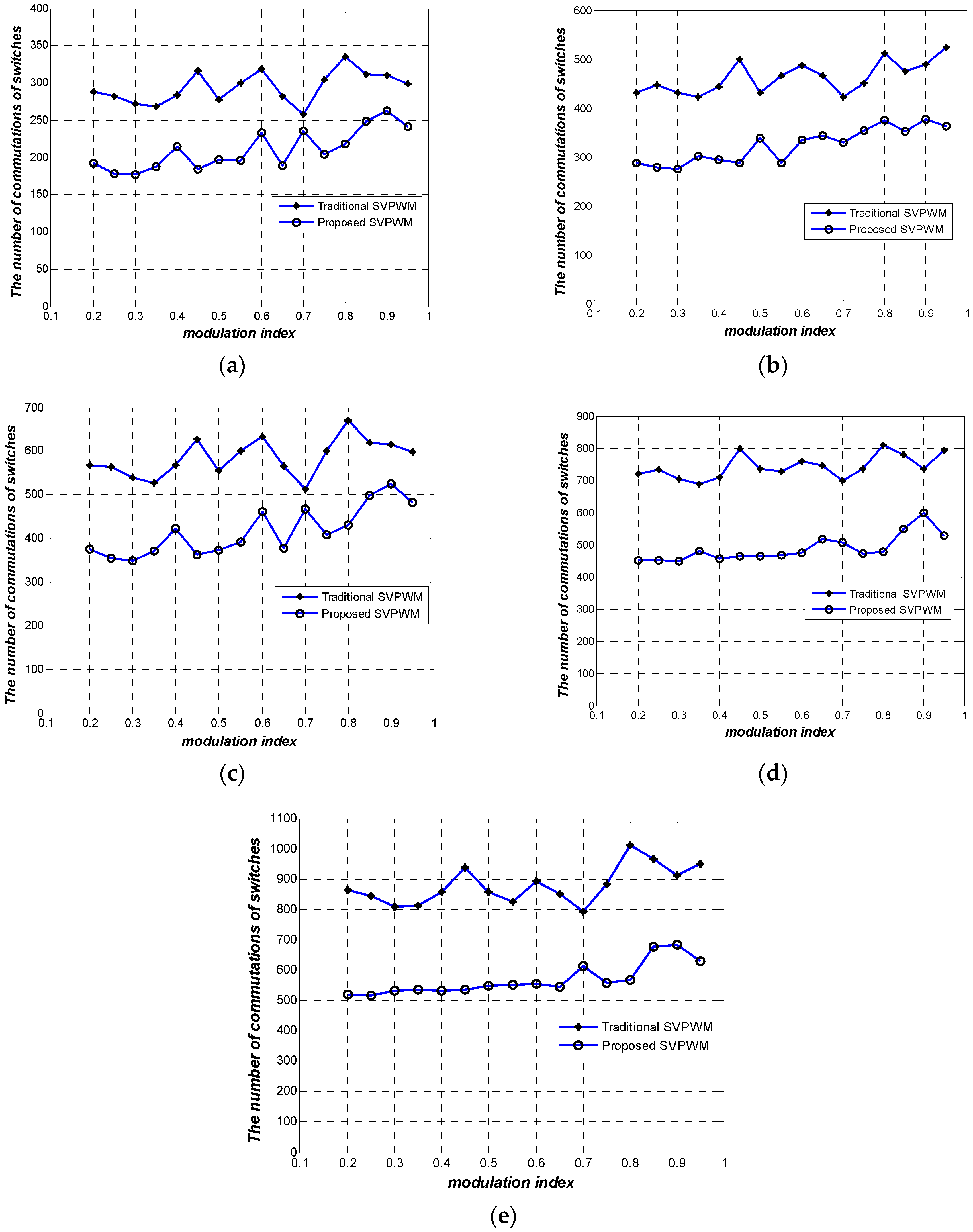

4.3. Compared with Other PWM Schemes

5. Conclusions

Acknowledgments

Author Contributions

Conflicts of Interest

References

- Rodriguez, J.; Lai, J.S.; Peng, F.Z. Multilevel inverters: A survey of topologies, controls, and applications. IEEE Trans. Ind. Electron. 2002, 49, 724–738. [Google Scholar] [CrossRef]

- Cai, X.J.; Wu, Z.X.; Wang, S.X. Phase-Shifted Carrier Pulse Width Modulation Based on Particle Swarm Optimization for Cascaded H-bridge Multilevel Inverters with Unequal DC Voltages. Energies 2015, 8, 9670–9687. [Google Scholar] [CrossRef]

- Patil, U.V.; Suryawanshi, H.M.; Renge, M.M. Closed-loop hybrid direct torque control for medium voltage induction motor drive for performance improvement. IET Power Electron. 2014, 7, 31–40. [Google Scholar] [CrossRef]

- Stefan, P.E.; Marco, S.; Nils, S.; Sedigheh, R.; Hanno, S.; Rik, W.D.D. Comparison of the modular multilevel DC Converter and the dual-active bridge converter for power conversion in HVDC and MVDC grids. IEEE Trans. Power Electron. 2015, 30, 124–137. [Google Scholar] [CrossRef]

- Ravikant, P.; Tripathi, R.N.; Hanamoto, T. Comprehensive analysis of LCL filter interfaced cascaded h-bridge multilevel inverter-based DSTATCOM. Energies 2017, 10, 346. [Google Scholar] [CrossRef]

- Zhu, H.F.; Shu, Z.L.; Qin, B.; Gao, S.B. Five-level diode-clamped active power filter using voltage space vector-based indirect current and predictive harmonic control. IET Power Electron. 2014, 7, 713–723. [Google Scholar] [CrossRef]

- Parastar, A.; Kuan, Y.C.; Seok, J.K. Multilevel modular dc/dc power converter for high-voltage dc-connected offshore wind energy applications. IEEE Trans. Ind. Electron. 2015, 62, 2879–2890. [Google Scholar] [CrossRef]

- Essakiappan, S.; Krishnamoorthy, H.S.; Enjeti, P.; Balog, R.S.; Ahmed, S. Multilevel medium-frequency link inverter for utility scale photovoltaic integration. IEEE Trans. Power Electron. 2015, 30, 3674–3684. [Google Scholar] [CrossRef]

- Sadigh, A.K.; Dargahi, V.; CorzineK, A. Analytical determination of conduction and switching power losses in flying-capacitor-based active neutral-point-clamped multilevel converter. IEEE Trans. Power Electron. 2016, 31, 5473–5494. [Google Scholar] [CrossRef]

- Wang, H.; Zhang, D.L.; Wang, Y.; Wu, B.; Athab, H.S. Power and voltage balance control of a novel three-phase solid-state transformer using multilevel cascaded h-bridge inverters for microgrid applications. IEEE Trans. Power Electron. 2016, 31, 3289–3301. [Google Scholar] [CrossRef]

- Mehrasa, M.; Pouresmaeil, E.; Zabihi, S.; Caballero, J.C.T.; Catalão, J.P.S. A novel modulation function-based control of modular multilevel converters for high voltage direct current transmission systems. Energies 2016, 9, 867. [Google Scholar] [CrossRef]

- Li, X.; Akin, S.D.B.; Rajashekara, K. A new active fault-tolerant SVPWM strategy for single-phase faults in three-phase multilevel converters. IEEE Trans. Ind. Electron. 2015, 62, 3955–3965. [Google Scholar] [CrossRef]

- Jana, K.C.; Biswas, S.K. Generalised switching scheme for a space vector pulse-width modulation-based N-level inverter with reduced switching frequency and harmonics. IET Power Electron. 2015, 8, 2377–2385. [Google Scholar] [CrossRef]

- Moranchel, M.; Huerta, F.; Sanz, I.; Bueno, E.; Rodríguez, F.J. A Comparison of modulation techniques for modular multilevel converters. Energies 2016, 9, 1091. [Google Scholar] [CrossRef]

- Dekka, A.; Wu, B.; Zargari, N.R.; Fuentes, R.L. A space-vector PWM-based voltage-balancing approach with reduced current sensors for modular multilevel converter. IEEE Trans. Ind. Electron. 2016, 63, 2734–2745. [Google Scholar] [CrossRef]

- Lopez, O.; Alvarez, J.; Malvar, J.; Yepes, A.G.; Vidal, A.; Baneira, F.; Estevez, D.P.; Freijedo, F. Space vector PWM with common-mode voltage elimination for multiphase drives. IEEE Trans. Power Electron. 2016, 31, 8151–8161. [Google Scholar] [CrossRef]

- Liu, Z.; Wang, Y.; Tan, G.J.; Li, H.; Zhang, Y.F. A novel SVPWM algorithm for five-level active neutral-point-clamped converter. IEEE Trans. Power Electron. 2016, 31, 3859–3866. [Google Scholar] [CrossRef]

- Rodríguez, J.; Morán, L.; Pontt, J.; Correa, P.; Silva, C. A high-performance vector control of an 11-level Inverter. IEEE Trans. Ind. Electron. 2003, 50, 80–85. [Google Scholar] [CrossRef]

- Celanovic, N.; Boroyevich, D. A fast space vector modulation algorithm for multilevel three phase converters. IEEE Trans. Ind. Appl. 2001, 37, 637–641. [Google Scholar] [CrossRef]

- Carnielutti, F.; Pinheiro, H. Hybrid modulation strategy for asymmetrical cascaded multilevel converters under normal and fault conditions. IEEE Trans. Ind. Electron. 2016, 63, 92–101. [Google Scholar] [CrossRef]

- Carnielutti, F.; Rech, C.; Pinheiro, H. Space vector modulation for cascaded asymmetrical multilevel converters under fault conditions. IEEE Trans. Ind. Appl. 2015, 51, 344–352. [Google Scholar] [CrossRef]

- Sozer, Y.; Torrey, D.A.; Saha, A.; Nguyen, H.; Hawes, N. Fast minimum loss space vector pulse-width modulation algorithm for multilevel inverters. IET Power Electron. 2014, 7, 1590–1602. [Google Scholar] [CrossRef]

- Deng, Y.; Teo, K.H.; Duan, C.; Habetler, T.G.; Harley, R.G. A fast and generalized space vector modulation scheme for multilevel inverters. IEEE Trans. Power Electron. 2014, 29, 5204–5217. [Google Scholar] [CrossRef]

- Wang, C.; Zhang, Y.; Tang, X.M.; Cheng, S.Z. Rapid and generalised space vector modulation algorithm for cascaded multilevel converter based on zero-order voltage constraint. IET Power Electron. 2016, 9, 989–996. [Google Scholar] [CrossRef]

- Yao, W.; Hu, H.; Lu, Z. Comparisons of space-vector modulation and carrier-based modulation of multilevel inverter. IEEE Trans. Power Electron. 2008, 23, 45–51. [Google Scholar] [CrossRef]

- Lim, Y.C.; Wi, S.O.; Kim, J.N.; Jung, Y.G. A pseudorandom carrier modulation scheme. IEEE Trans. Power Electron. 2010, 25, 797–805. [Google Scholar] [CrossRef]

- Boonmee, C.; Wajanatepin, N. Comparison of using carrier-based pulse width modulation techniques for cascaded h-bridge inverters application in the PV energy systems. In Proceedings of the International Electrical Engineering Congress, Chonburi, Thailand, 19–21 March 2014; pp. 1–4. [Google Scholar] [CrossRef]

| Switching Mode | ∆a | ∆b | ∆c | ∆α′ | ∆β′ |

|---|---|---|---|---|---|

| diagonal | ±1 | 0 | 0 | ±1 | ∓1 |

| vertical | 0 | ±1 | 0 | 0 | |

| horizontal | 0 | 0 | ±1 | ∓1 | 0 |

| Adjacent Quadrilateral | Starting Vector | Switching Path | Note |

|---|---|---|---|

| the first kind of quadrilateral | V47 | V47→V44→V47→V46 | B1 into A1(A3) |

| V45 | V45→V44→V47→V46 | B1 into A1(A3) | |

| the first kind of quadrilateral | V47 | V47→V44→V45→V41 | B1 into A1(A2) |

| V45 | V45→V41→V45→V44 | B1 into A1(A2) | |

| the second kind of quadrilateral | V47 | V47→V44→V45→V44→V41 | B1 into A1(A2) |

| V45 | V45→V44→V41 | B1 into A1(A2) | |

| the third kind of quadrilateral | V47 | V47→V44→V46 | B1 into A1(A3) |

| V45 | V45→V44→V47→V44→V46 | B1 into A1(A3) |

| Adjacent Quadrilateral | Starting Vector | Switching Path | Note |

|---|---|---|---|

| the first kind of quadrilateral | V57 | V57→V54→V53→V54→V52 | B2 into A1(A2) |

| V53 | V53→V54→V51 | B2 into A1(A3) | |

| the second kind of quadrilateral | V57 | V57→V54→V53→V51 | B2 into A1(A2) |

| V53 | V53→V54→V53→V54 | B2 into A1(A2) | |

| the second kind of quadrilateral | V57 | V57→V54→V57→V58 | B2 into A2(A3) |

| V53 | V53→V54→V57→V58 | B2 into A2(A3) | |

| the third kind of quadrilateral | V57 | V57→V54→V58 | B2 into A1(A3) |

| V53 | V53→V54→V57→V54→V58 | B2 into A1(A3) |

| Adjacent Quadrilateral | Starting Vector | Switching Path | Note |

|---|---|---|---|

| the first kind of quadrilateral | V62 | V62→V66→V65 | B3 into A1(A3) |

| V63 | V63→V66→V62→V66→V65 | B3 into A1(A3) | |

| the second kind of quadrilateral | V62 | V62→V66→V63→V66→V67 | B3 into A3(A2) |

| V63 | V63→V66→V67 | B3 into A3(A2) | |

| the third kind of quadrilateral | V62 | V62→V66→V63→V67 | B3 into A3(A2) |

| V63 | V63→V66→V63→V67 | B3 into A3(A2) | |

| the third kind of quadrilateral | V62 | V62→V66→V62→V65 | B3 into A1(A3) |

| V63 | V63→V66→V62→V65 | B3 into A1(A3) |

| Number of Sampling Points in One Period | Maximum Number from Theoretical Calculation (Times) | Experimental Results (Times) |

|---|---|---|

| 42 | 108 | 103 |

| 63 | 150 | 149 |

| 84 | 192 | 190 |

© 2017 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Tang, X.; Zhang, J.; Liu, Z.; Zhang, M. A Switching Frequency Optimized Space Vector Pulse Width Modulation (SVPWM) Scheme for Cascaded Multilevel Inverters. Energies 2017, 10, 725. https://doi.org/10.3390/en10050725

Tang X, Zhang J, Liu Z, Zhang M. A Switching Frequency Optimized Space Vector Pulse Width Modulation (SVPWM) Scheme for Cascaded Multilevel Inverters. Energies. 2017; 10(5):725. https://doi.org/10.3390/en10050725

Chicago/Turabian StyleTang, Xiongmin, Junhui Zhang, Zheng Liu, and Miao Zhang. 2017. "A Switching Frequency Optimized Space Vector Pulse Width Modulation (SVPWM) Scheme for Cascaded Multilevel Inverters" Energies 10, no. 5: 725. https://doi.org/10.3390/en10050725