Line-to-Line Fault Analysis and Location in a VSC-Based Low-Voltage DC Distribution Network

Abstract

:1. Introduction

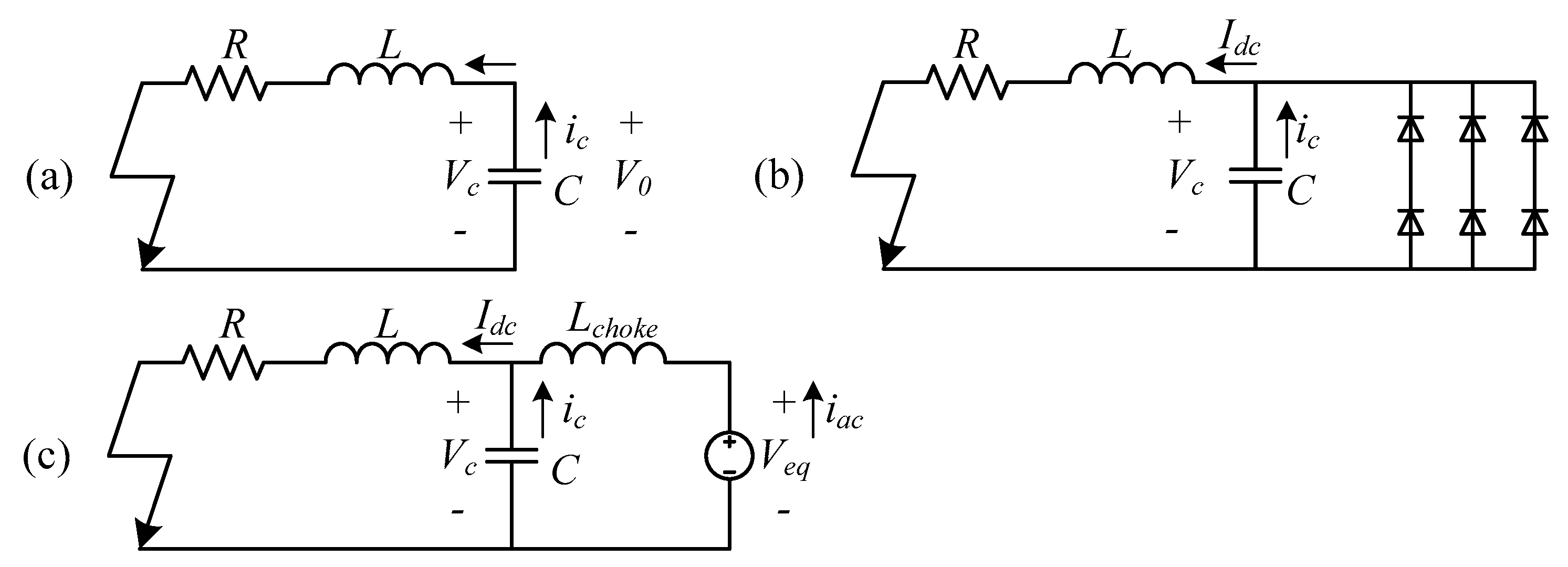

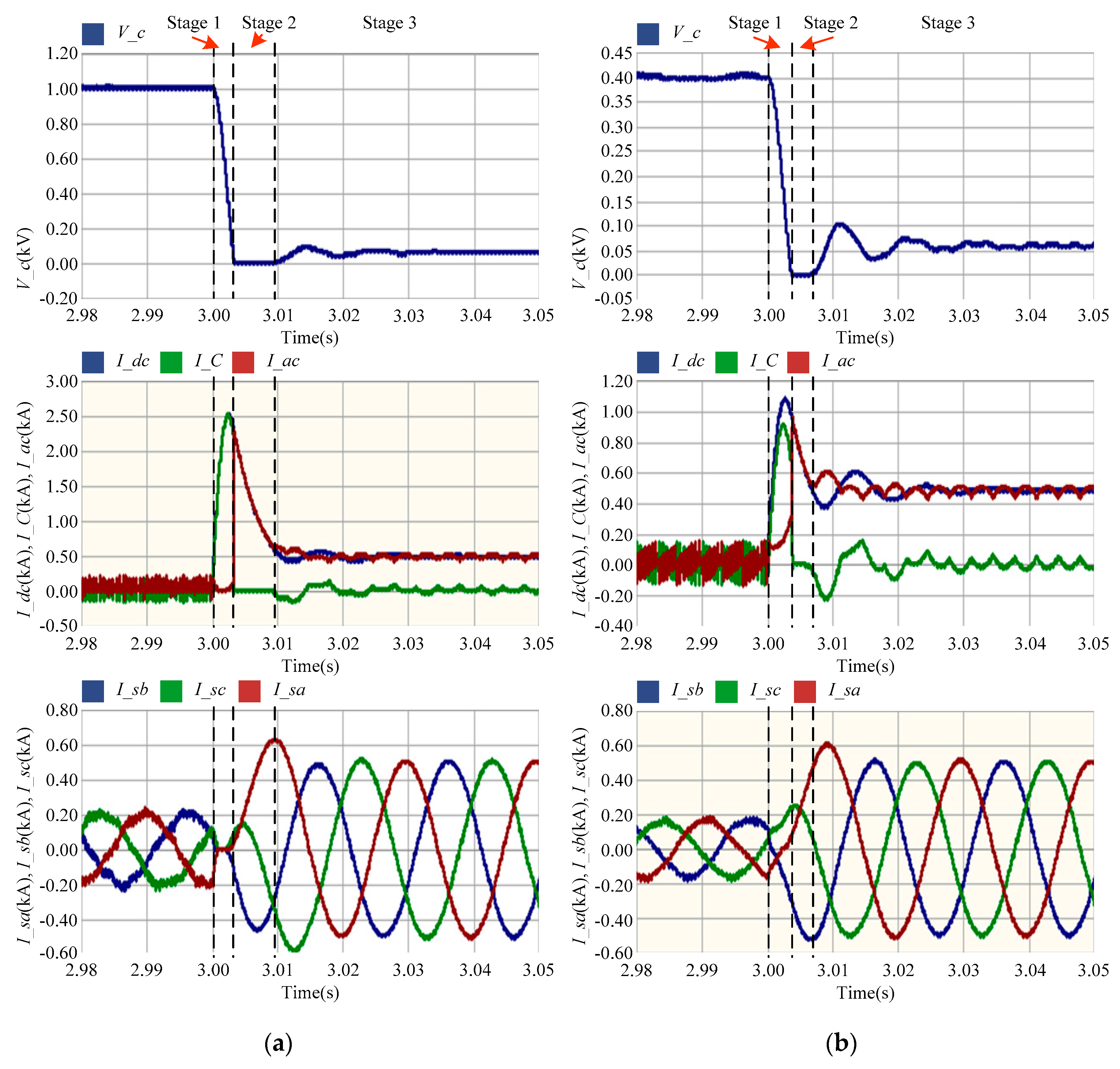

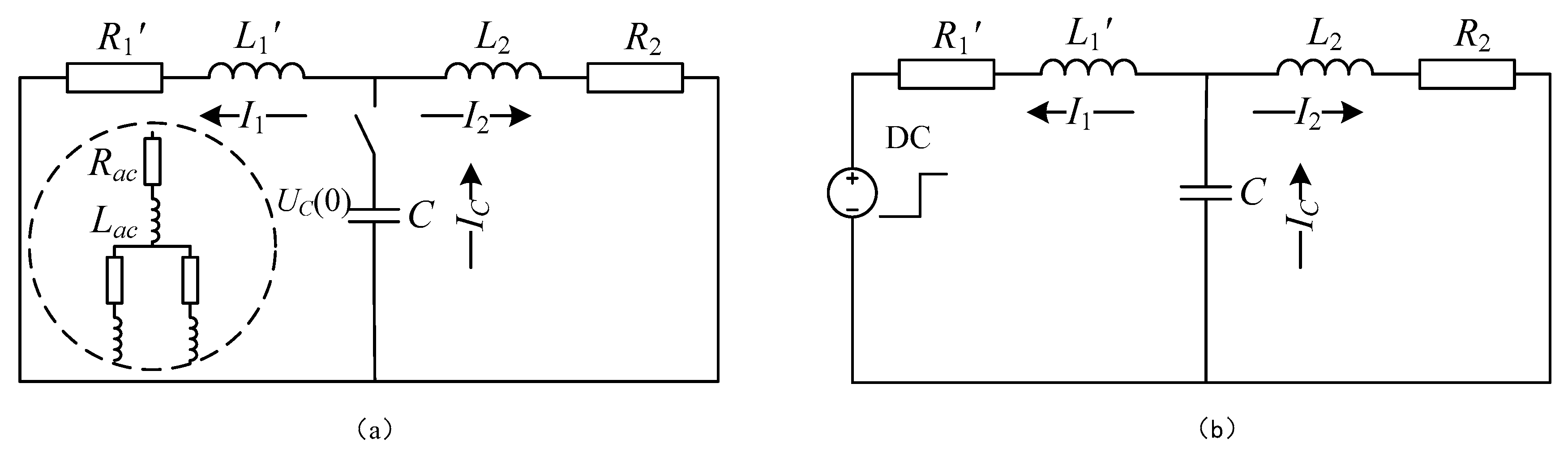

2. LVDC Cable Short-Circuit Fault Analysis

2.1. Fault Stages Comparison

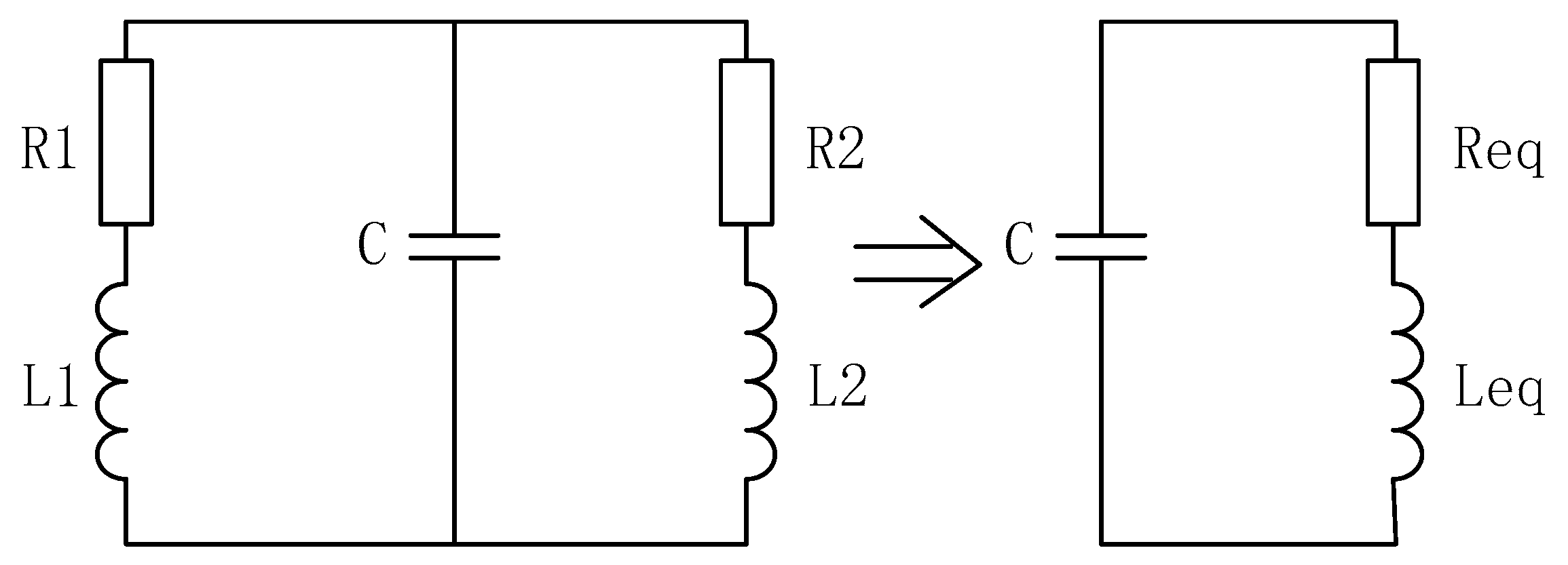

2.2. Fault Stages Comparison

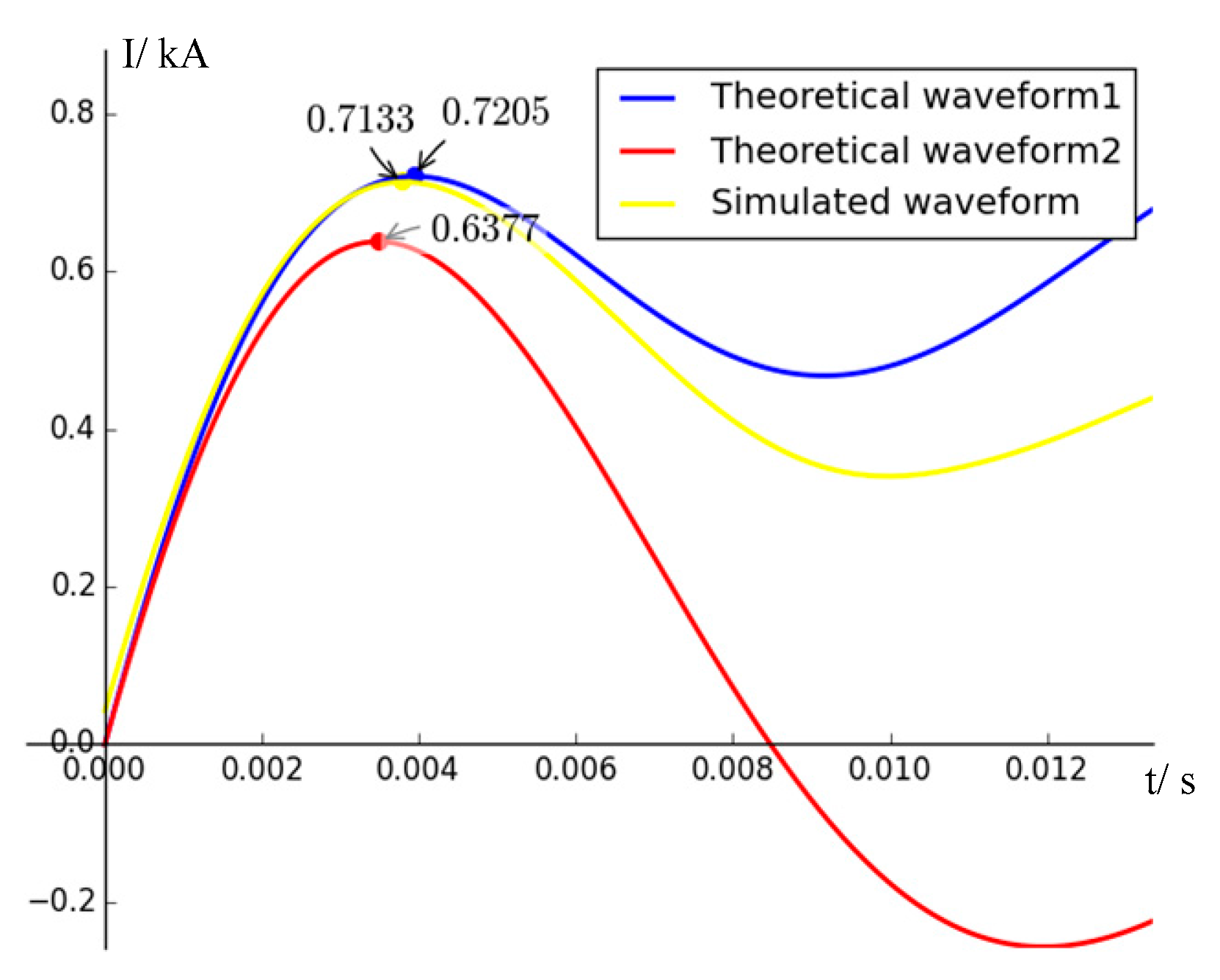

2.3. Transient-State Fault

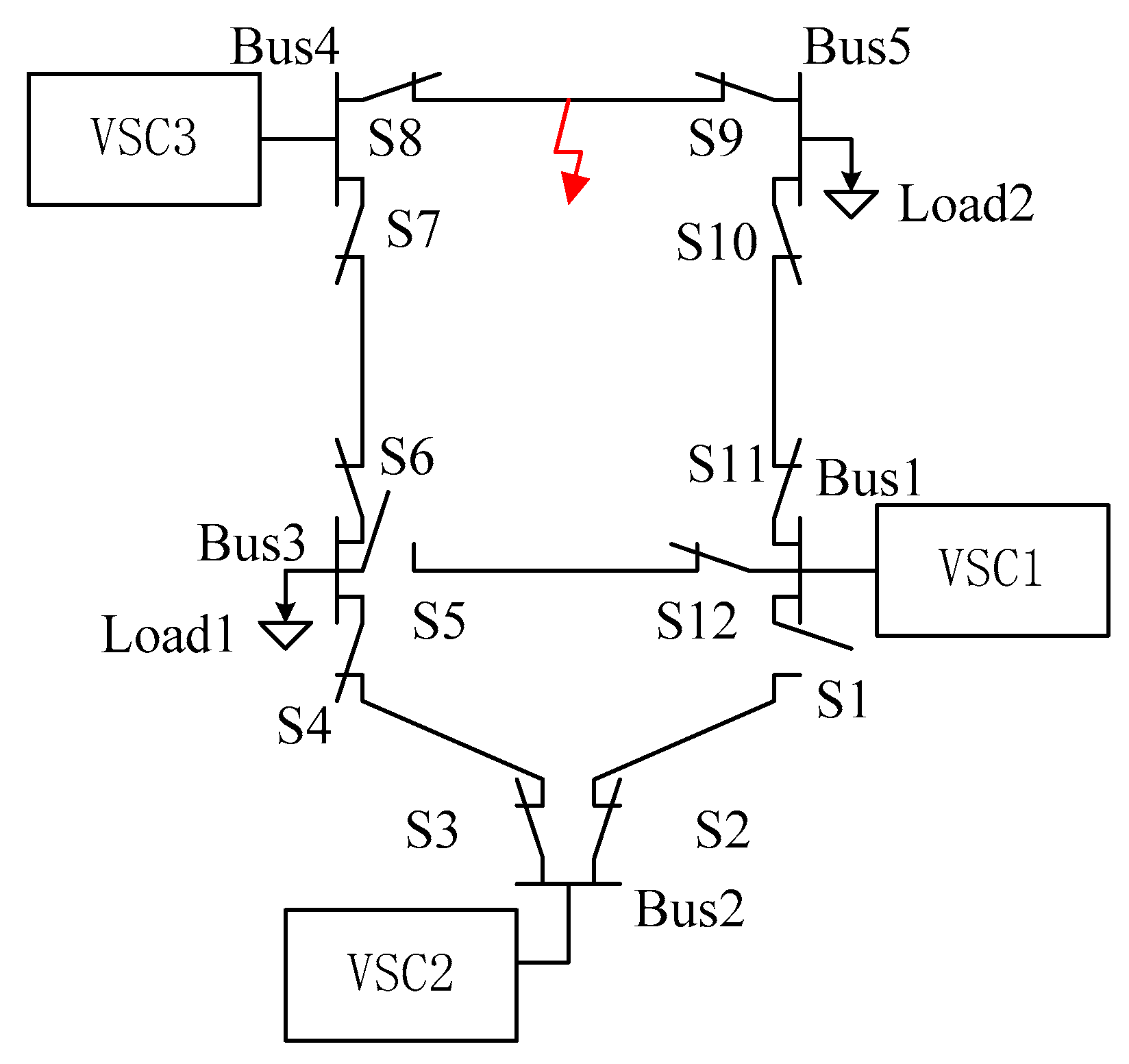

3. Case Studies

4. Fault Location and Protection Coordination

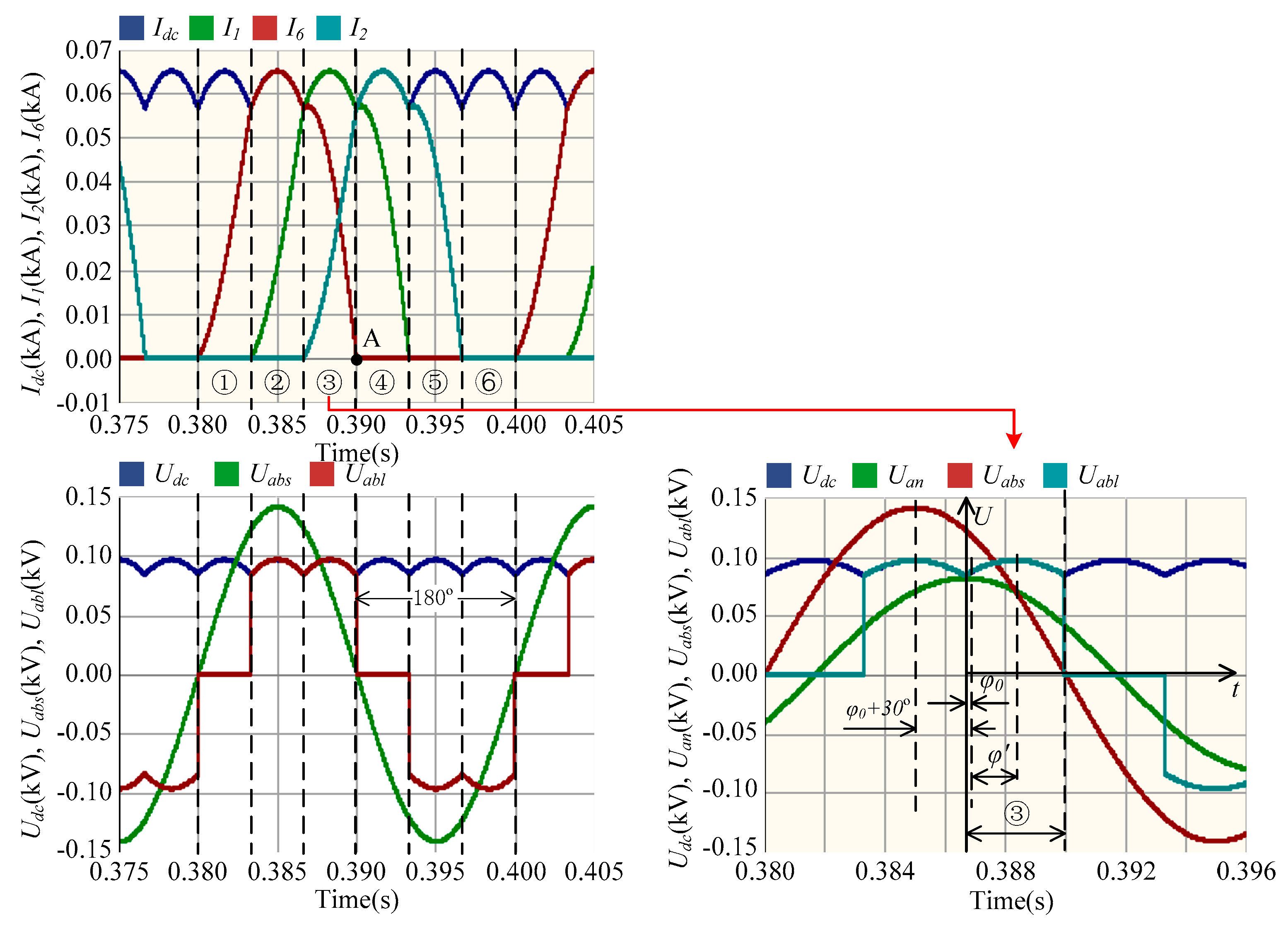

4.1. Short-Circuit Fault Location and Analysis

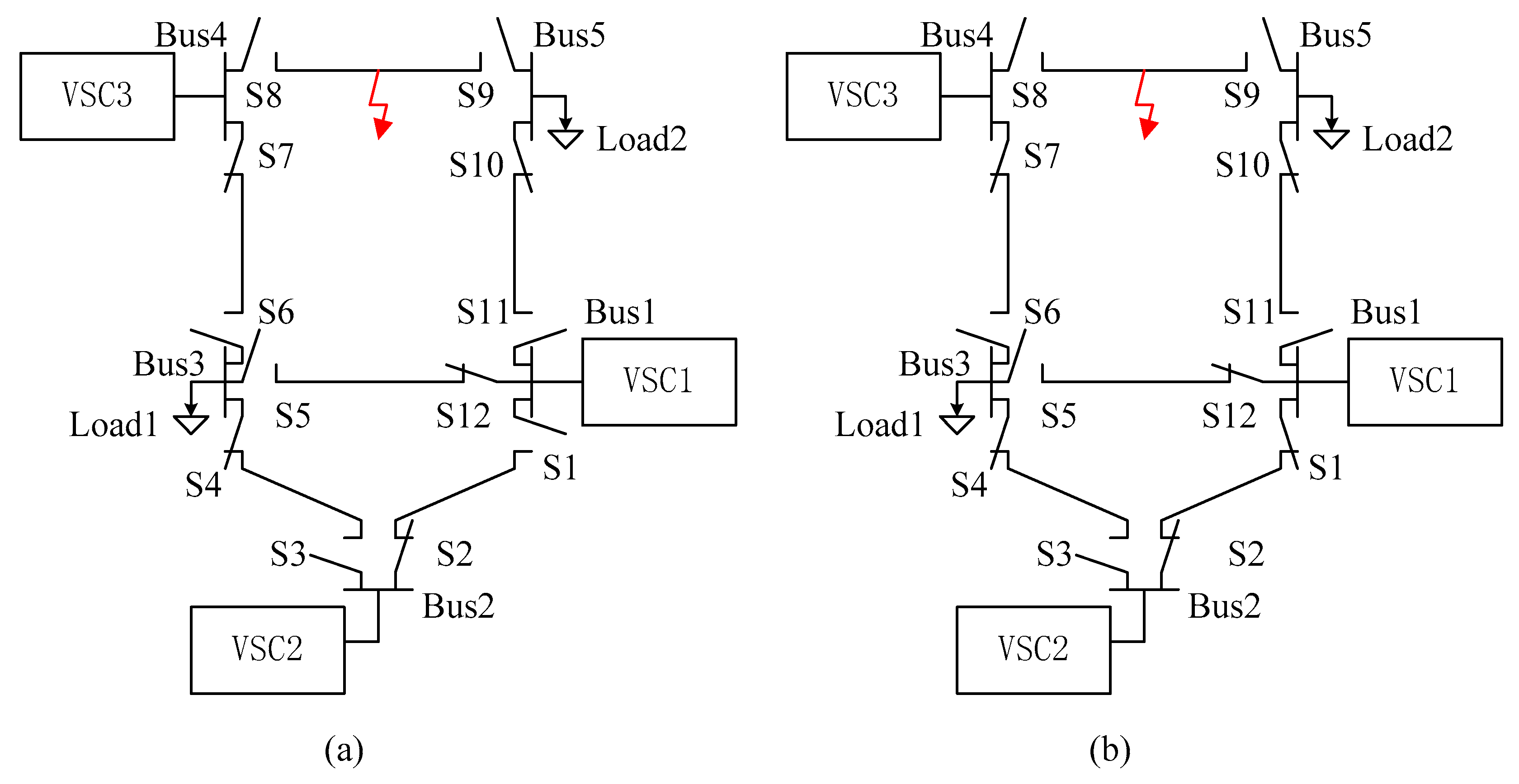

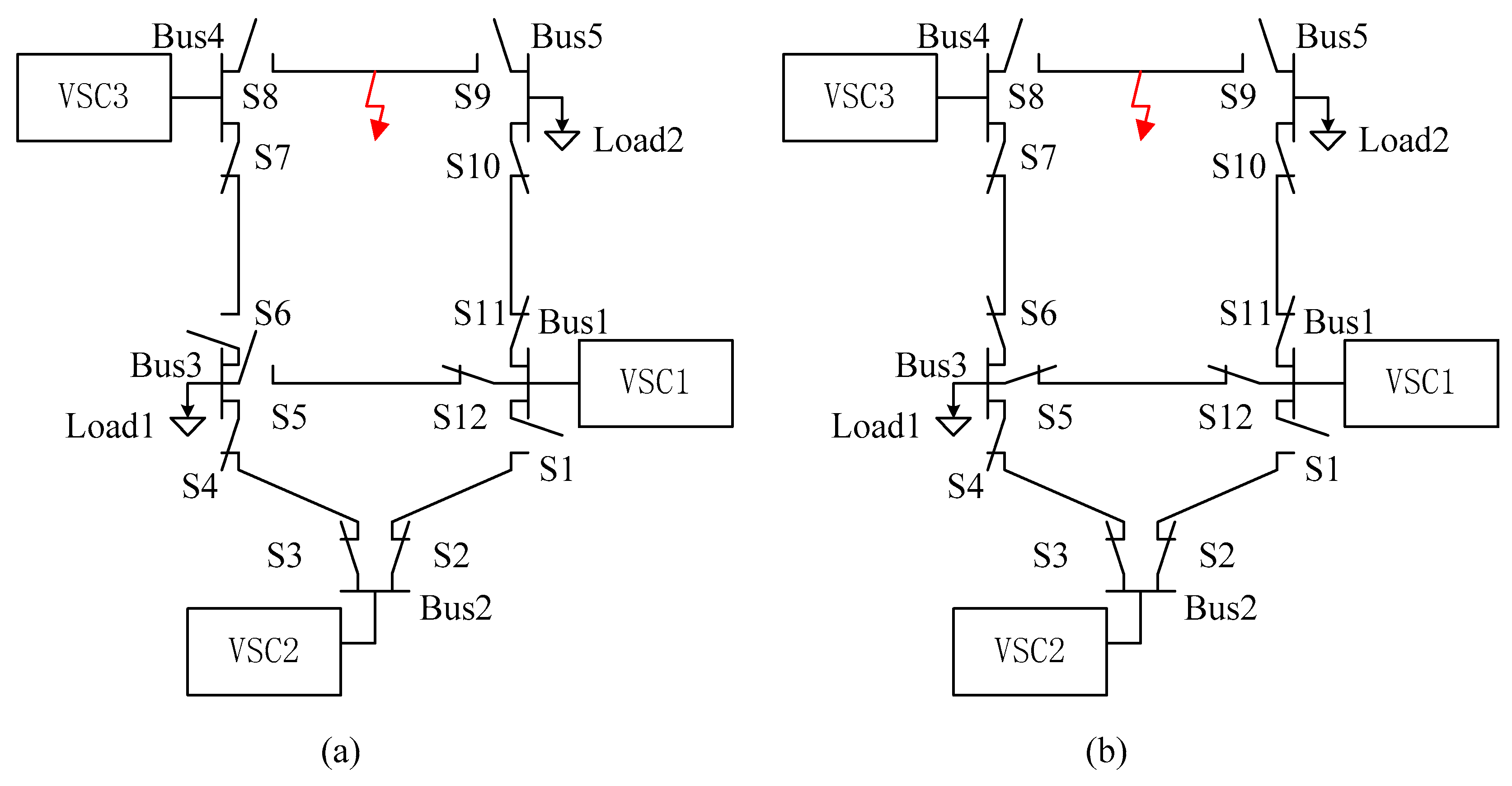

4.2. Coordination with the Handshaking Method

- Disconnect all the sources;

- Open the switches that carry the fault current from the bus to the line;

- Reconnect all the sources; and

- Re-close the switches with both of their poles connected to an energized bus.

5. Conclusions

Acknowledgments

Author Contributions

Conflicts of Interest

References

- Jackson, J.J.; Mwasilu, F.; Lee, J.; Jung, J.W. AC-microgrids versus DC-microgrids with distributed energy resources: A review. Renew. Sustain. Energy Rev. 2013, 24, 387–405. [Google Scholar]

- Dragicevic, T.; Lu, X.N.; Vasquez, J.C.; Guerrero, J.M. DC microgrids-Part II: A review of power architectures, applications, and standardization issues. IEEE Trans. Power Electron. 2016, 31, 3528–3549. [Google Scholar] [CrossRef]

- Baran, M.E.; Mahajan, N.R. Overcurrent protection on voltage-source-converter-based multiterminal DC distribution systems. IEEE Trans. Power Deliv. 2007, 22, 406–412. [Google Scholar] [CrossRef]

- Yang, J.; Fletcher, J.E.; O’Reilly, J. Short-circuit and ground fault analyses and location in VSC-based DC network cables. IEEE Trans. Ind. Electron. 2012, 59, 3827–3837. [Google Scholar] [CrossRef]

- Deng, F.J.; Chen, Z. Design of protective inductors for HVDC transmission line within DC grid offshore wind farms. IEEE Trans. Power Deliv. 2013, 28, 75–83. [Google Scholar] [CrossRef]

- Deng, C. Study of a modified flux-coupling-type superconducting fault current limiter for mitigating the effect of DC short circuit in a VSC HVDC system. Supercond. Novel Magn. 2015, 28, 1525–1534. [Google Scholar] [CrossRef]

- Wang, C.Q.; Li, B.; He, J.W.; Xin, Y. Design and Application of the SFCL in the Modular Multilevel Converter Based DC System. IEEE Trans. Appl. Supercond. 2017, 27, 3800504. [Google Scholar] [CrossRef]

- Lee, J.G.; Khan, U.A.; Lee, H.Y.; Lee, B.W. Impact of SFCL on the four types of HVDC circuit breakers by simulation. IEEE Trans. Appl. Supercond. 2016, 26, 5602606. [Google Scholar] [CrossRef]

- Li, B.T.; Jia, J.F.; Li, B.; Zhang, Y.K. Fault Analysis of VSC-HVDC System with Saturated Iron-Core Superconductive Fault Current Limiter. In Proceedings of the 2015 IEEE International Conference on Applied Superconductivity and Electromagnetic Devices (ASEMD), Shanghai, China, 20–23 November 2015. [Google Scholar]

- Mesas, J.J.; Monjo, L.; Sainz, L.; Pedra, J. Cable Fault Characterization in VSC DC Systems. In Proceedings of the 2016 International Symposium on Fundamentals of Electrical Engineering (ISFEE), Bucharest, Romania, 30 June–2 July 2016. [Google Scholar]

- Niaki, S.H.A.; Karegar, H.K.; Monfared, M.G. A novel fault detection method for VSC-HVDC transmission system of offshore wind farm. Electr. Power Energy Syst. 2015, 73, 475–483. [Google Scholar] [CrossRef]

- Sun, X.Y.; Gao, X.; Ji, X.J.; Song, Y. Analysis of fault characteristics of converter in VSC-HVDC. In Proceedings of the 2016 IEEE International Power Modulator and High Voltage Conference (IPMHVC), San Francisco, CA, USA, 6–9 July 2016. [Google Scholar]

- Ma, Y.Y.; Zou, G.B.; Gao, Z.J.; Sun, C.J. Analytic approximation of fault current contributed by DC capacitors in VSC-HVDC pole-to-pole fault. In Proceedings of the 2017 IEEE Electrical Power and Energy Conference (EPEC), Saskatoon, SK, Canada, 22–25 October 2017. [Google Scholar]

- Wang, Y.; Zhang, J.G.; Fu, Y.; Hei, Y.; Zhang, X.Y. Pole-to-ground fault analysis in transmission line of DC grids based on VSC. In Proceedings of the 2016 IEEE 8th International Power Electronics and Motion Control Conference (IPEMC-ECCE Asia), Hefei, China, 22–26 May 2016. [Google Scholar]

- Liu, D.H.; Wei, T.Z.; Huo, Q.H.; Wu, L.X. DC side line-to-line fault analysis of VSC-HVDC and DC-fault-clearing methods. In Proceedings of the 2015 5th International Conference on Electric Utility Deregulation and Restructuring and Power Technologies (DRPT), Changsha, China, 26–29 November 2015. [Google Scholar]

- Alwash, M.; Sweet, M.; Narayanan, E.M.S. Analysis of Voltage Source Converters Under DC Line-to-Line Short-Circuit Fault Conditions. In Proceedings of the 2017 IEEE International Electric Machines and Drives Conference (IEMDC), Edinburgh, UK, 19–21 June 2017. [Google Scholar]

- Park, J.-D.; Candelaria, J.; Ma, L. DC Ring-Bus Microgrid Fault Protection and Identification of Fault Location. IEEE Trans. Power Deliv. 2013, 28, 2574–2584. [Google Scholar] [CrossRef]

- Mohanty, R.; Balaji, U.S.M.; Pradhan, A.K. An Accurate Noniterative Fault-Location Technique for Low-Voltage DC Microgrid. IEEE Trans. Power Deliv. 2016, 31, 475–481. [Google Scholar] [CrossRef]

- Monadi, M.; Koch-Ciobotaru, C.; Luna, A.; Candela, J.I. A protection strategy for fault detection and location for multi-terminal MVDC distribution systems with renewable energy systems. In Proceedings of the 2014 International Conference on Renewable Energy Research and Application (ICRERA), Milwaukee, WI, USA, 19–22 October 2014. [Google Scholar]

- Yang, J.; Fletcher, J.E.; O’Reilly, J. Multiterminal dc wind farm collection grid internal fault analysis and protection scheme design. IEEE Trans. Power Deliv. 2010, 25, 2308–2318. [Google Scholar] [CrossRef]

- Tang, L.; Ooi, B.T. Locating and isolating DC faults in multiterminal DC systems. IEEE Trans. Power Deliv. 2007, 22, 1877–1884. [Google Scholar] [CrossRef]

- Bascom, E.C. Computerized underground cable fault location expertise. In Proceedings of the 1994 IEEE Power Engineering Society Transmission and Distribution Conference, Chicago, IL, USA, 10–15 April 1994. [Google Scholar]

- Liu, X.; Osman, A.H.; Malik, O.P. Hybrid travelling wave/boundary protection for monopolar HVDC line. IEEE Trans. Power Deliv. 2009, 24, 569–578. [Google Scholar] [CrossRef]

- Kwon, Y.J.; Kang, S.H.; Lee, D.G.; Kim, H.K. Fault location algorithm based on cross correlation method for HVDC cable lines. In Proceedings of the IET 9th International Conference on Developments in Power System Protection, Glasgow, UK, 17–20 March 2008. [Google Scholar]

- Yang, X.; Choi, M.S.; Lee, S.J.; Ten, C.W.; Lim, S.I. Fault location for underground power cable using distributed parameter approach. IEEE Trans. Power Syst. 2008, 23, 1809–1816. [Google Scholar] [CrossRef]

- Dhar, S.; Dash, P.K. Differential current-based fault protection with adaptive threshold for multiple PV-based DC microgrid. IET Renew. Power Gener. 2017, 11, 778–790. [Google Scholar] [CrossRef]

| System Components | Value | System Voltage | Value |

|---|---|---|---|

| AC-side Inductance Lac | 1.5 mH | Phase Voltage Up_p | 220 V |

| AC-side Resistance Rac | 0.3 Ω | Line Voltage Ul_l | 380 V |

| DC-linked Capacitance C | 6 mF | Equivalent DC Source Udc | 513 V |

| DC-side Inductance Ldc | 0.56 mH/km | Initial DC voltage V0 | 400 V |

| DC-side Resistance Rdc | 0.12 Ω/km |

| Fault Distance (km) | 1 | 2 | 3 | 4 | 5 |

|---|---|---|---|---|---|

| Simulation steady-state current (kA) | 0.480 | 0.445 | 0.411 | 0.380 | 0.351 |

| Theoretical steady-state current (kA) | 0.513 | 0.471 | 0.433 | 0.398 | 0.368 |

| Error (%) | 6.78 | 5.88 | 5.33 | 4.85 | 4.75 |

| Simulation transient-state peak current (kA) | 1.078 | 0.713 | 0.556 | 0.464 | 0.402 |

| Theoretical transient-state peak current1 (kA) | 1.087 | 0.721 | 0.564 | 0.475 | 0.416 |

| Error (%) | 0.91 | 1.06 | 1.51 | 2.32 | 3.52 |

| Theoretical transient-state peak current2 (kA) | 0.994 | 0.638 | 0.486 | 0.398 | 0.339 |

| Error (%) | 7.75 | 10.56 | 12.67 | 12.62 | 15.59 |

| Fault Distance/m | 500 | 1000 | 1500 | 2000 | 2500 | 3000 |

|---|---|---|---|---|---|---|

| d/m (Rf = 0) | 519 | 1015 | 1539 | 2054 | 2589 | 3130 |

| Error (%) | 0.63 | 0.50 | 1.30 | 1.80 | 2.97 | 4.33 |

| d/m (Rf = 0.5 Ω) | 579 | 1114 | 1653 | 2190 | 2769 | 3366 |

| Error (%) | 2.63 | 3.80 | 5.13 | 6.33 | 8.97 | 12.20 |

| Fault Distance/m | 500 | 1000 | 1500 | 2000 | 2500 | 3000 |

|---|---|---|---|---|---|---|

| d/m (Rf = 0) | 519 | 1012 | 1507 | 2016 | 2520 | 3032 |

| Error (%) | 0.63 | 0.40 | 0.23 | 0.53 | 0.67 | 1.07 |

| d/m (Rf = 0.5 Ω) | 536 | 1049 | 1564 | 2089 | 2620 | 3160 |

| Error (%) | 1.20 | 1.63 | 2.13 | 2.97 | 4.00 | 5.33 |

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Xue, S.-M.; Liu, C. Line-to-Line Fault Analysis and Location in a VSC-Based Low-Voltage DC Distribution Network. Energies 2018, 11, 536. https://doi.org/10.3390/en11030536

Xue S-M, Liu C. Line-to-Line Fault Analysis and Location in a VSC-Based Low-Voltage DC Distribution Network. Energies. 2018; 11(3):536. https://doi.org/10.3390/en11030536

Chicago/Turabian StyleXue, Shi-Min, and Chong Liu. 2018. "Line-to-Line Fault Analysis and Location in a VSC-Based Low-Voltage DC Distribution Network" Energies 11, no. 3: 536. https://doi.org/10.3390/en11030536