Single-Phase Shunt Active Power Filter Based on a 5-Level Converter Topology

Abstract

:1. Introduction

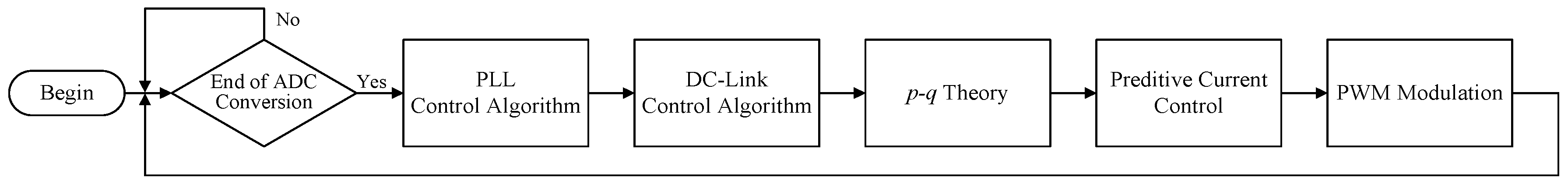

2. Proposed 5-Level Converter Topology

3. Control Algorithms

3.1. p-q Theory

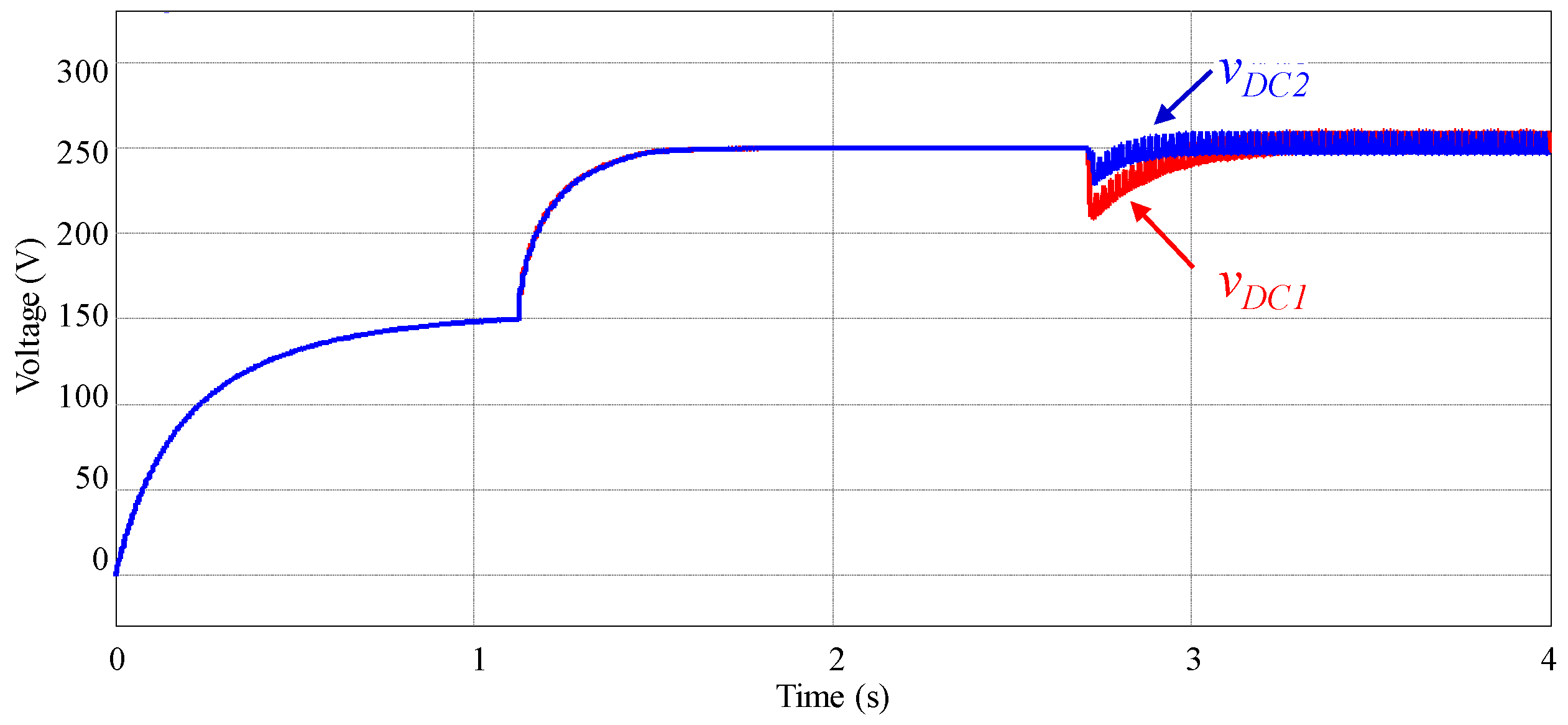

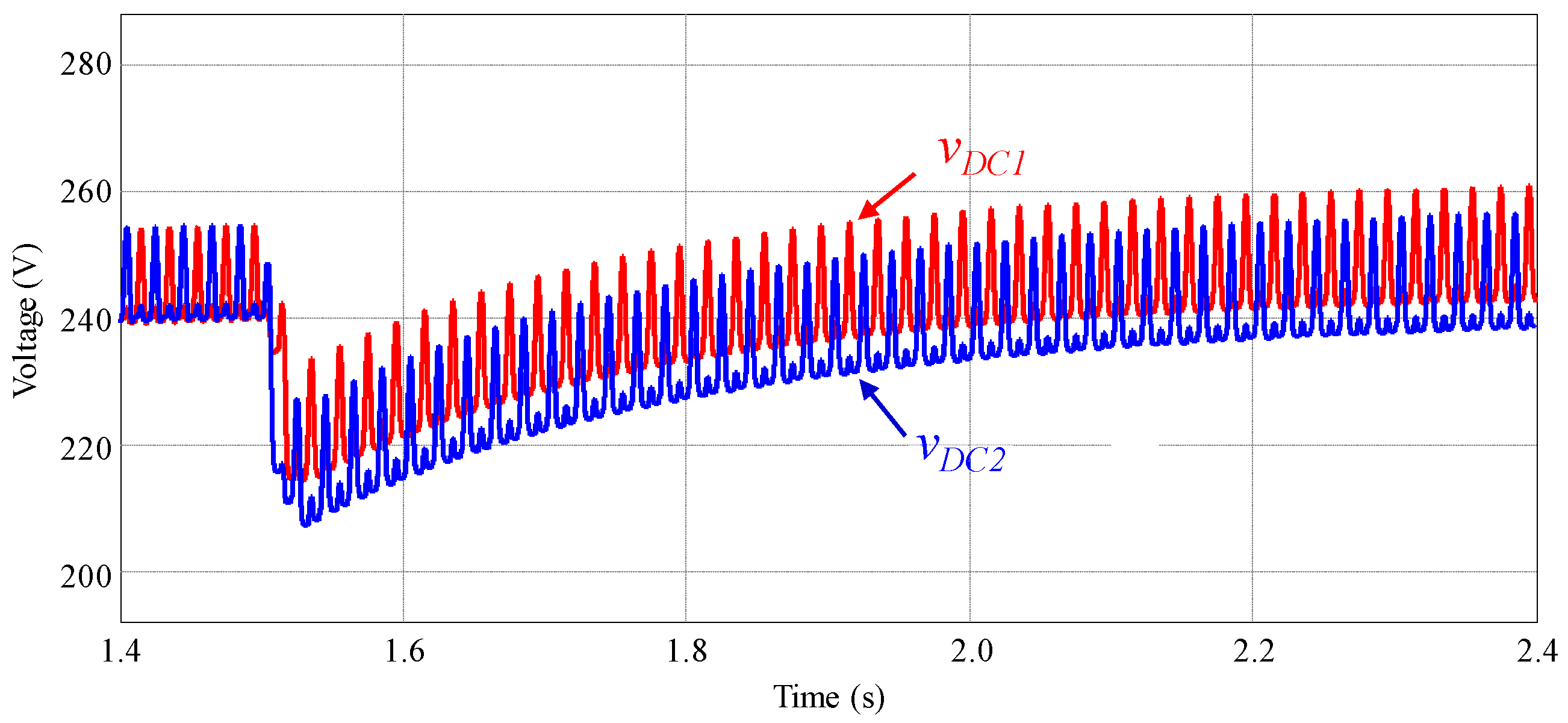

3.2. DC-Link Voltage Control

3.3. Predictive Current Control

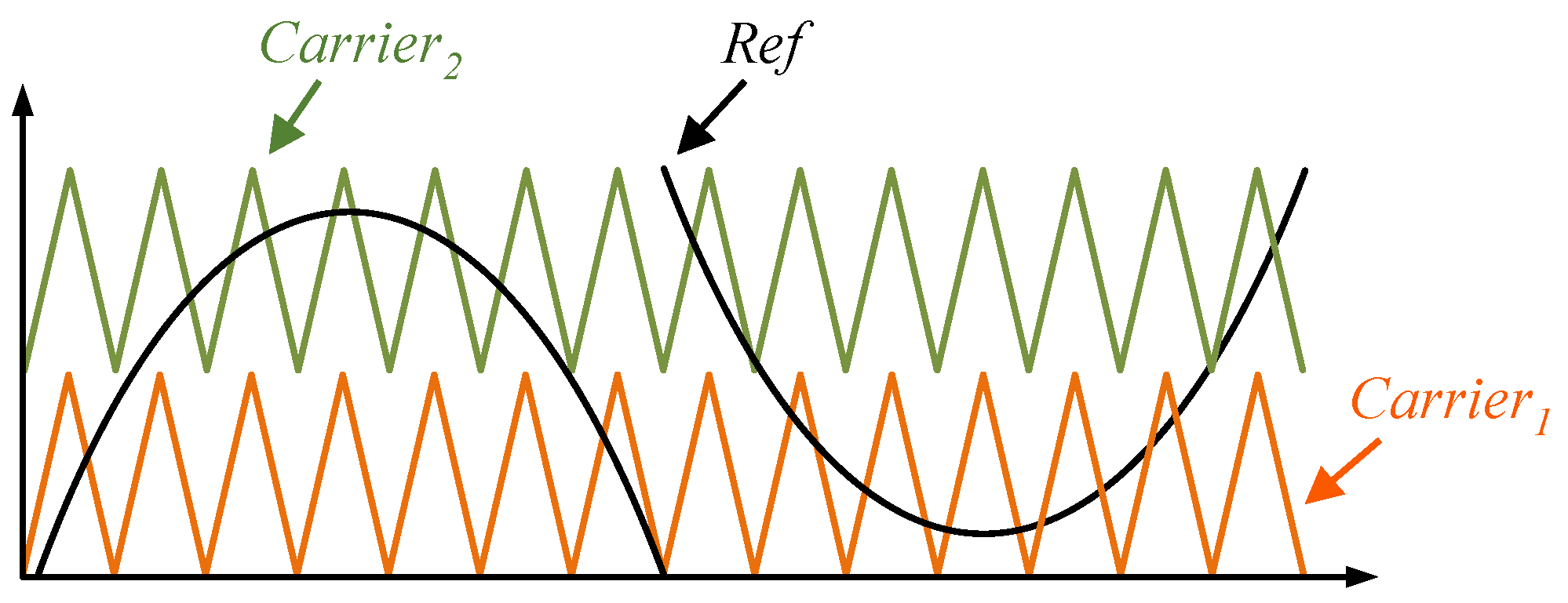

3.4. SPWM Strategy

4. Simulation Analysis

4.1. SPWM Strategy

4.2. DC-Link Voltage Control

4.3. SAPF Operation

4.3.1. SAPF Operating with Resistive-Inductive (RL) Load

4.3.2. SAPF Operating with Diode Rectifier with Resistive-Capacitive (RC) Load

4.3.3. SAPF Dynamic Response towards Load Changing

5. Implementation of a Laboratorial Prototype of the SAPF

5.1. Power Circuit Hardware

5.2. Control Circuit Hardware

6. Experimental Results

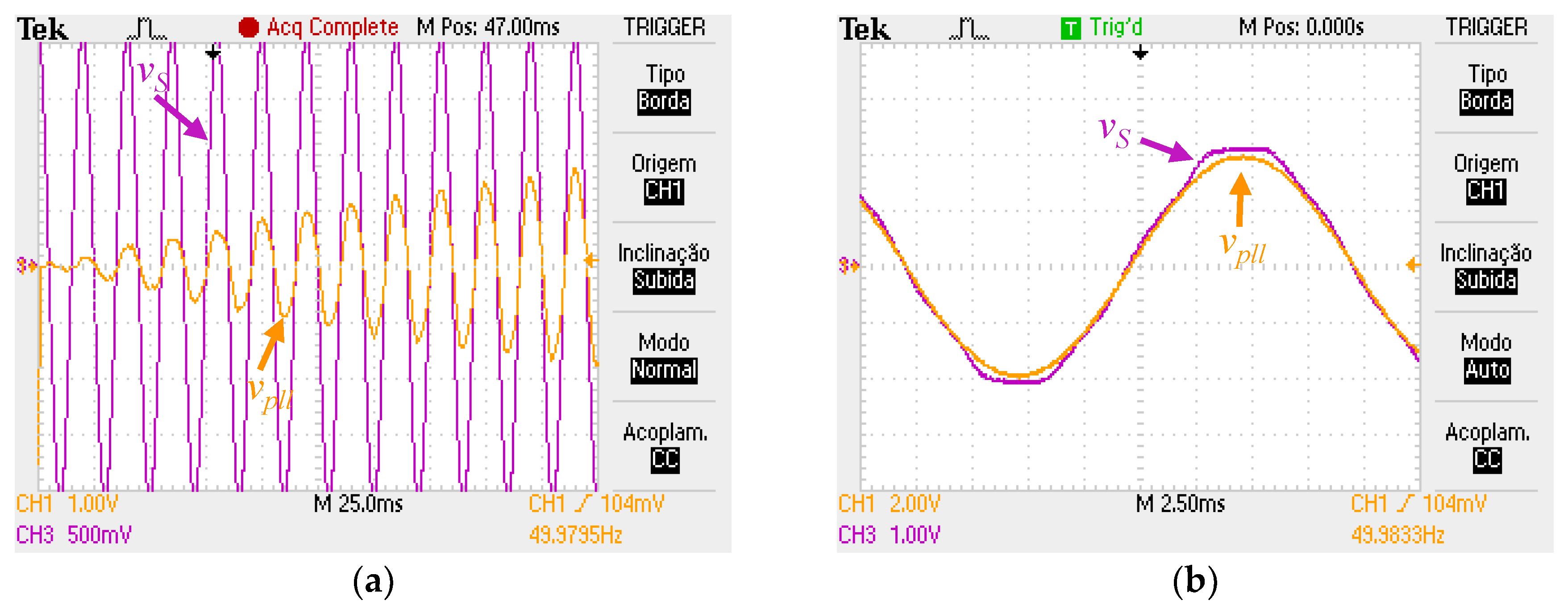

6.1. Experimental Validation of the PLL Algorithm

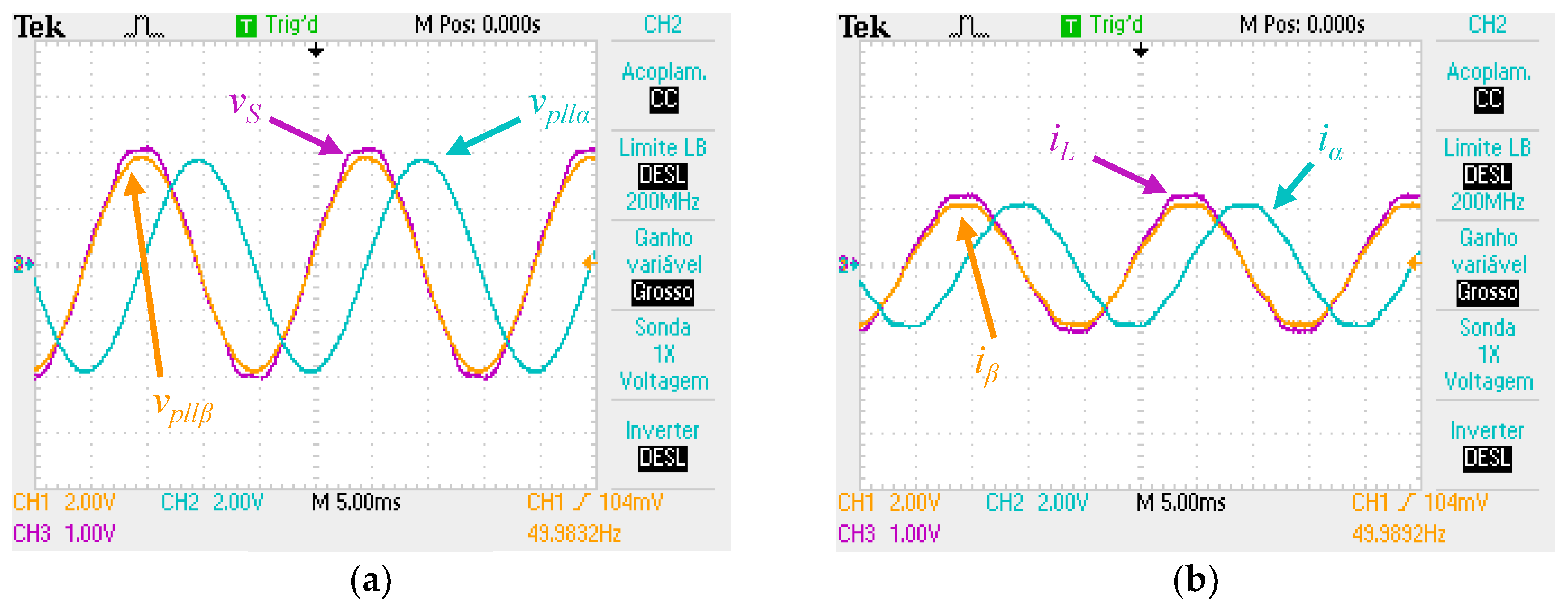

6.2. Experimental Validation of the p-q Theory

6.3. Experimental Validation of the Modulation Technique

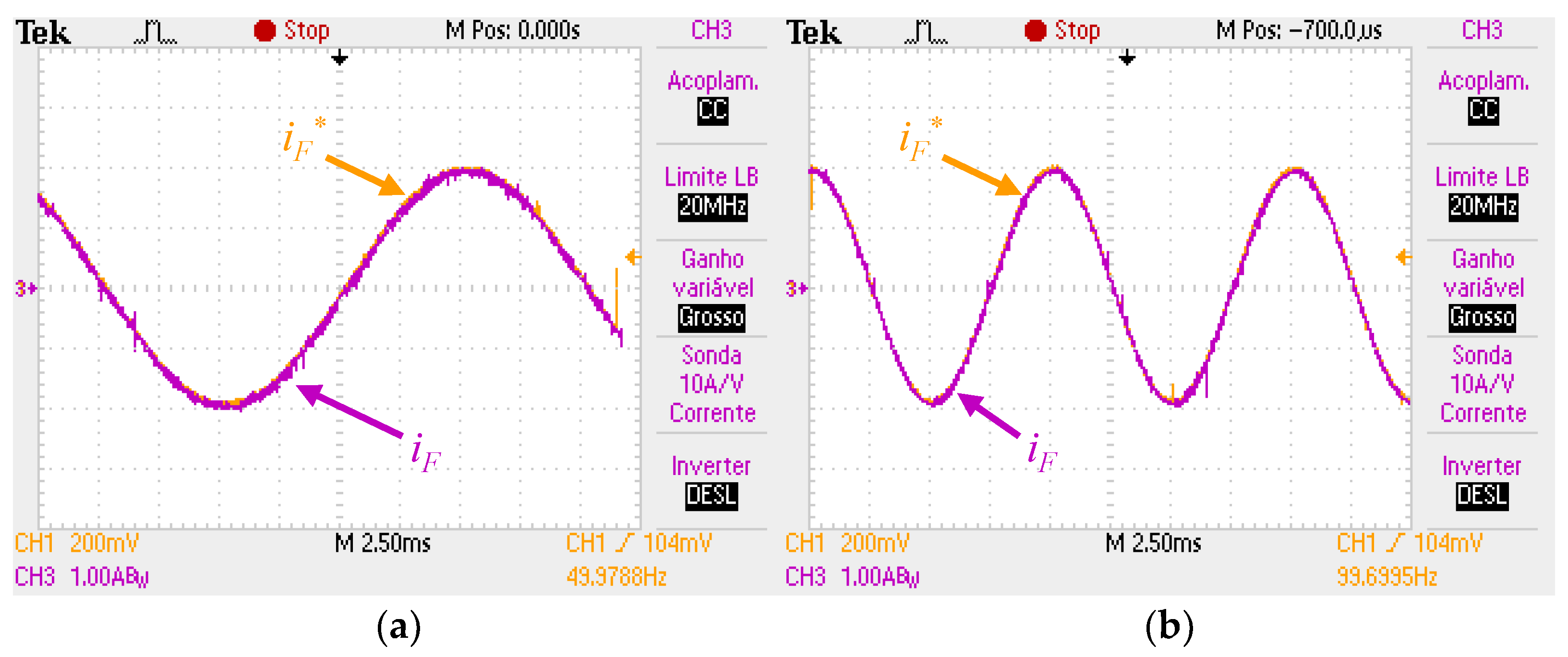

6.4. Experimental Validation of the Predictive Current Controller

6.5. Experimental Validation of the DC-Link Voltage Controller

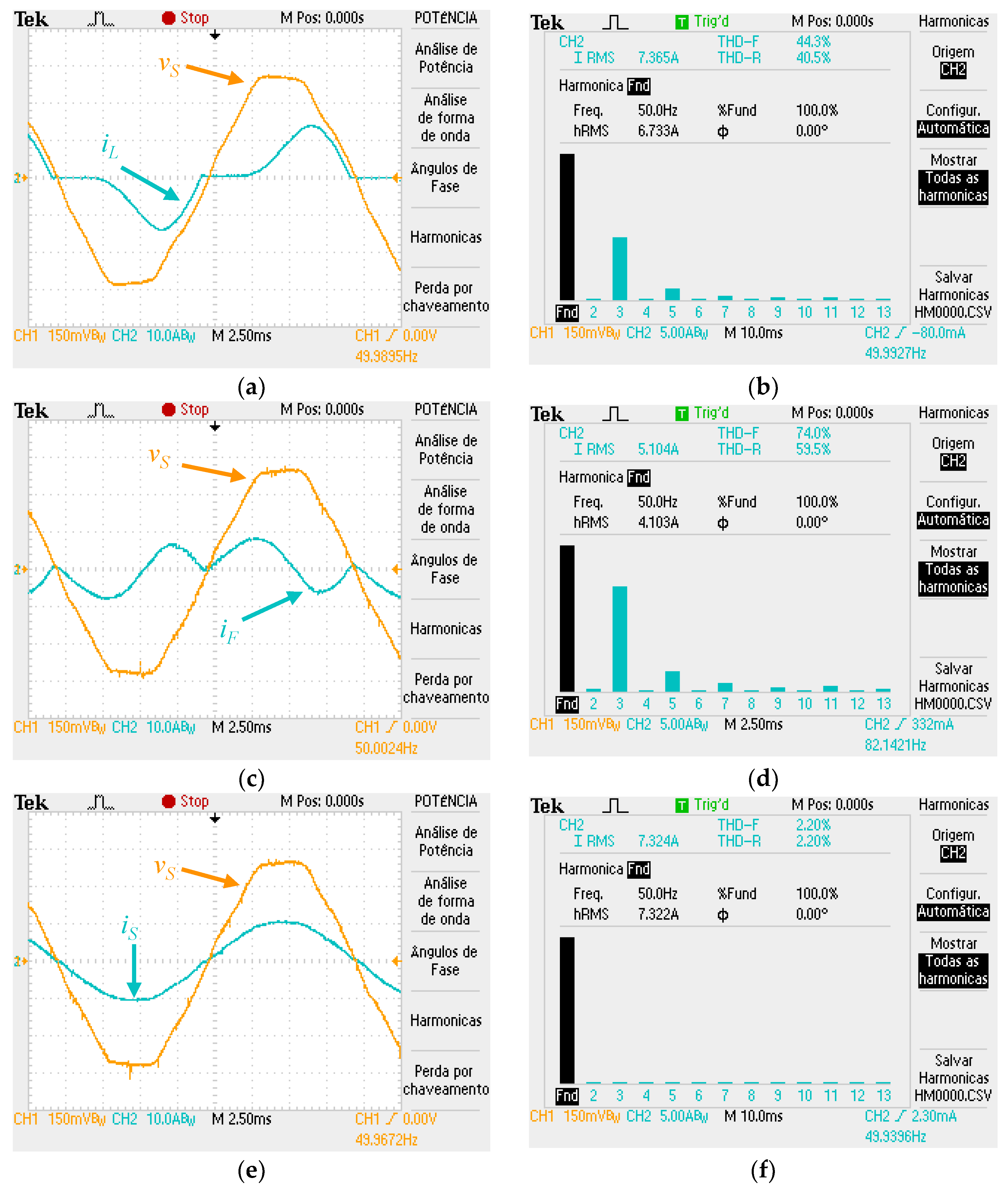

6.6. Experimental Results of the SAPF with RL Load

6.7. Experimental Results of the SAPF with a Diode Rectifier with Capacitive Filter

7. Conclusions

Acknowledgments

Author Contributions

Conflicts of Interest

References

- Dugan, R.C.; McGranaghan, M.F.; Santoso, S.; Beaty, H.W. Electrical Power Systems Quality, 3rd ed.; McGraw-Hill Education: New York, NY, USA, 2002. [Google Scholar]

- Balda, J.C.; Mantooth, A. Power-Semiconductor Devices and Components for New Power Converter Developments: A key enabler for ultrahigh efficiency power electronics. IEEE Power Electron. Mag. 2016, 3, 53–56. [Google Scholar] [CrossRef]

- Hoene, E.; Deboy, G.; Sullivan, C.R.; Hurley, G. Outlook on Developments in Power Devices and Integration: Recent Investigations and Future Requirements. IEEE Power Electron. Mag. 2018, 5, 28–36. [Google Scholar] [CrossRef]

- IEEE Recommended Practices and Requirements for Harmonic Control in Electrical Power Systems; 519-1992; IEEE: Piscataway, NJ, USA, 1993; pp. 1–112. [CrossRef]

- Palmer, J.A.; Degeneff, R.C.; McKernan, T.M.; Halleran, T.M. Pipe-type cable ampacities in the presence of harmonics. IEEE Trans. Power Deliv. 1993, 8, 1689–1695. [Google Scholar] [CrossRef]

- Faiz, J.; Ghazizadeh, M.; Oraee, H. Derating of transformers under non-linear load current and non-sinusoidal voltage—An overview. IET Electron. Power Appl. 2015, 9, 486–495. [Google Scholar] [CrossRef]

- Lee, K.; Carnovale, D.; Young, D.; Ouellette, D.; Zhou, J. System Harmonic Interaction Between DC and AC Adjustable Speed Drives and Cost Effective Mitigation. IEEE Trans. Ind. Appl. 2016, 52, 3939–3948. [Google Scholar] [CrossRef]

- Mendis, S.R.; Gonzalez, D.A. Harmonic and transient overvoltage analyses in arc furnace power systems. IEEE Trans. Ind. Appl. 1992, 28, 336–342. [Google Scholar] [CrossRef]

- Liu, Y.; Heydt, G.T.; Chu, R.F. The Power Quality Impact of Cycloconverter Control Strategies. IEEE Trans. Power Deliv. 2005, 20, 1711–1718. [Google Scholar] [CrossRef]

- Gomez, J.C.; Morcos, M.M. Impact of EV battery chargers on the power quality of distribution systems. IEEE Trans. Power Deliv. 2003, 18, 975–981. [Google Scholar] [CrossRef]

- Blanco, A.M.; Stiegler, R.; Meyer, J. Power Quality Disturbances Caused by Modern Lighting Equipment (CFL and LED). In Proceedings of the 2013 IEEE Grenoble Conference, Grenoble, France, 16–20 June 2013; pp. 1–6. [Google Scholar] [CrossRef]

- Peng, F.Z.; Akagi, H.; Nabae, A. A new approach to harmonic compensation in power systems-a combined system of shunt passive and series active filters. IEEE Trans. Ind. Appl. 1990, 26, 983–990. [Google Scholar] [CrossRef]

- Sasaki, H.; Machida, T. A New Method to Eliminate AC Harmonic Currents by Magnetic Flux Compensation-Considerations on Basic Design. IEEE Trans. Power Appar. Syst. 1971, PAS-90, 2009–2019. [Google Scholar] [CrossRef]

- Gyugyi, L.; Strycula, E.C. Active AC Power Filters. In Proceedings of the IEEE IAS Annual Meeting, Chicago, IL, USA, 11–14 October 1976; p. 529. [Google Scholar]

- Singh, B.; Al-Haddad, K.; Chandra, A. A review of active filters for power quality improvement. IEEE Trans. Ind. Electron. 1999, 46, 960–971. [Google Scholar] [CrossRef]

- Akagi, H.; Kanazawa, Y.; Nabae, A. Generalized Theory of the Instantaneous Reactive Power in Three-Phase Circuits. In Proceedings of the 1983 International Power Electronics Conference, Tokyo, Japan, 27–31 March 1983; pp. 1375–1386. [Google Scholar]

- Depenbrock, M. The FBD-method, a generally applicable tool for analyzing power relations. IEEE Trans. Power Syst. 1993, 8, 381–387. [Google Scholar] [CrossRef]

- Czarnecki, L.S. Orthogonal decomposition of the currents in a 3-phase nonlinear asymmetrical circuit with a nonsinusoidal voltage source. IEEE Trans. Instrum. Meas. 1988, 37, 30–34. [Google Scholar] [CrossRef]

- Bhattacharya, S.; Divan, D. Synchronous frame based controller implementation for a hybrid series active filter system. In Proceedings of the IAS ’95. Conference Record of the 1995 IEEE Industry Applications Conference Thirtieth IAS Annual Meeting, Orlando, FL, USA, 8–12 October 1995; pp. 2531–2540. [Google Scholar] [CrossRef]

- Hoon, Y.; Radzi, M.M.; Hassan, M.; Mailah, N. Control Algorithms of Shunt Active Power Filter for Harmonics Mitigation: A Review. Energies 2017, 10, 2038. [Google Scholar] [CrossRef]

- Pinto, J.G.; Exposto, B.; Monteiro, V.; Monteiro, L.F.C.; Couto, C.; Afonso, J.L. Comparison of current-source and voltage-source Shunt Active Power Filters for harmonic compensation and reactive power control. In Proceedings of the IECON 2012—38th Annual Conference on IEEE Industrial Electronics Society, Montreal, QC, Canada, 25–28 October 2012; pp. 5161–5166. [Google Scholar] [CrossRef]

- Lai, J.; Peng, F.Z. Multilevel converters-a new breed of power converters. In Proceedings of the 1995 Industry Applications Conference, Thirtieth IAS Annual Meeting, IAS ’95, Orlando, FL, USA, 8–12 October 1995; pp. 2348–2356. [Google Scholar] [CrossRef]

- Rodriguez, J.; Lai, J.; Peng, F.Z. Multilevel inverters: A survey of topologies, controls, and applications. IEEE Trans. Ind. Electron. 2002, 49, 724–738. [Google Scholar] [CrossRef]

- Nabae, A.; Takahashi, I.; Akagi, H. A New Neutral-Point-Clamped PWM Inverter. IEEE Trans. Ind. Appl. 1981, IA-17, 518–523. [Google Scholar] [CrossRef]

- Hochgraf, C.; Lasseter, R.; Divan, D.; Lipo, T.A. Comparison of multilevel inverters for static VAr compensation. In Proceedings of the 1994 IEEE Industry Applications Society Annual Meeting, Denver, CO, USA, 2–6 October 1994; pp. 921–928. [Google Scholar] [CrossRef]

- Teodorescu, R.; Blaabjerg, F.; Pedersen, J.K.; Cengelci, E.; Enjeti, P.N. Multilevel inverter by cascading industrial VSI. IEEE Trans. Ind. Electron. 2002, 49, 832–838. [Google Scholar] [CrossRef]

- Hasan, M.; Abu-Siada, A.; Islam, S.; Muyeen, S. A Novel Concept for Three-Phase Cascaded Multilevel Inverter Topologies. Energies 2018, 11, 268. [Google Scholar] [CrossRef]

- Reddy, K.B.M.; Pattnaik, S. Novel symmetric and asymmetric topology of multilevel inverter with reduced number of switches. In Proceedings of the 2017 IEEE International Conference on Industrial Technology (ICIT), Toronto, ON, Canada, 22–25 March 2017; pp. 165–170. [Google Scholar] [CrossRef]

- Elias, M.F.M.; Rahim, N.A.; Ping, H.W.; Uddin, M.N. Asymmetrical transistor-clamped H-bridge cascaded multilevel inverter. In Proceedings of the 2012 IEEE Industry Applications Society Annual Meeting, Las Vegas, NV, USA, 7–11 October 2012; pp. 1–8. [Google Scholar] [CrossRef]

- Dixon, J.; Moran, L. High-level multistep inverter optimization using a minimum number of power transistors. IEEE Trans. Power Electron. 2006, 21, 330–337. [Google Scholar] [CrossRef]

- Haddad, M.; Rahmani, S.; Hamadi, A.; Al-Haddad, K. New Single Phase Multilevel reduced count devices to Perform Active Power Filter. In Proceedings of the SoutheastCon 2015, Fort Lauderdale, FL, USA, 9–12 April 2015; pp. 1–6. [Google Scholar] [CrossRef]

- Martinez-Rodrigo, F.; Ramirez, D.; Rey-Boue, A.; de Pablo, S.; Lucas, L.H. Modular Multilevel Converters: Control and Applications. Energies 2017, 10, 1709. [Google Scholar] [CrossRef]

- Moranchel, M.; Huerta, F.; Sanz, I.; Bueno, E.; Rodríguez, F. A Comparison of Modulation Techniques for Modular Multilevel Converters. Energies 2016, 9, 1091. [Google Scholar] [CrossRef]

- Rolim, L.G.B.; da Costa, D.R.; Aredes, M. Analysis and Software Implementation of a Robust Synchronizing PLL Circuit Based on the pq Theory. IEEE Trans. Ind. Electron. 2006, 53, 1919–1926. [Google Scholar] [CrossRef]

- Karimi-Ghartemani, M. Linear and Pseudolinear Enhanced Phased-Locked Loop (EPLL) Structures. IEEE Trans. Ind. Electron. 2014, 61, 1464–1474. [Google Scholar] [CrossRef]

- Singh, B.N.; Khadkikar, V.; Chandra, A. Generalised single-phase p-q theory for active power filtering: Simulation and DSP-based experimental investigation. IET Power Electron. 2009, 2, 67–78. [Google Scholar] [CrossRef]

| Voltage Polarity | S1 | S1’ | S2 | S2’ | S3 | S3’ | vc |

|---|---|---|---|---|---|---|---|

| vC > 0 | OFF | ON | ON | OFF | ON | OFF | vDC |

| OFF | ON | OFF | ON | ON | OFF | vDC/2 | |

| OFF | ON | OFF | ON | OFF | ON | 0 | |

| vC < 0 | ON | OFF | ON | OFF | ON | OFF | 0 |

| ON | OFF | OFF | ON | ON | OFF | −vDC/2 | |

| ON | OFF | OFF | ON | OFF | ON | −vDC |

| Installation Parameter | Linear Load | Non-linear Load | ||

|---|---|---|---|---|

| Source | Load | Source | Load | |

| Current (RMS) | 10 A | 21 A | 15.8 A | 20.2 A |

| Current THD (%f) | 1.6% | 0.5% | 2.8% | 38% |

| PF | 0.99 | 0.47 | 0.99 | 0.78 |

| Installation Parameter | Linear Load | Non-linear Load | ||

|---|---|---|---|---|

| Source | Load | Source | Load | |

| Current (RMS) | 6.0 A | 6.4 A | 7.3 A | 7.4 A |

| Current THD (%f) | 2.6% | 2.5% | 2.2% | 44.3% |

| PF | 0.99 | 0.74 | 0.99 | 0.81 |

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Oliveira Pinto, J.G.; Macedo, R.; Monteiro, V.; Barros, L.; Sousa, T.; Afonso, J.L. Single-Phase Shunt Active Power Filter Based on a 5-Level Converter Topology. Energies 2018, 11, 1019. https://doi.org/10.3390/en11041019

Oliveira Pinto JG, Macedo R, Monteiro V, Barros L, Sousa T, Afonso JL. Single-Phase Shunt Active Power Filter Based on a 5-Level Converter Topology. Energies. 2018; 11(4):1019. https://doi.org/10.3390/en11041019

Chicago/Turabian StyleOliveira Pinto, José Gabriel, Rui Macedo, Vitor Monteiro, Luis Barros, Tiago Sousa, and João L. Afonso. 2018. "Single-Phase Shunt Active Power Filter Based on a 5-Level Converter Topology" Energies 11, no. 4: 1019. https://doi.org/10.3390/en11041019