New Switched-Dual-Source Multilevel Inverter for Symmetrical and Asymmetrical Operation

Abstract

:1. Introduction

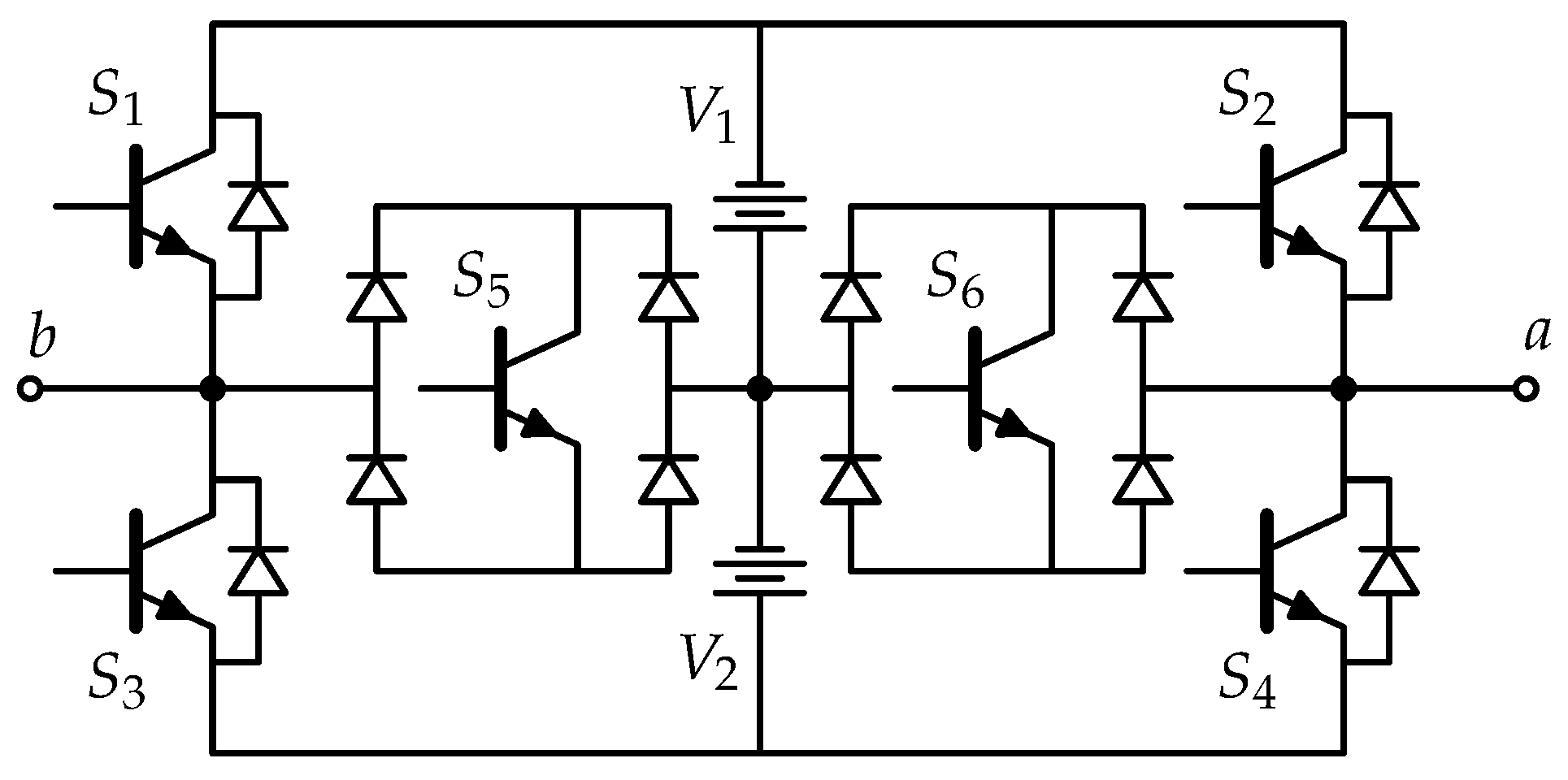

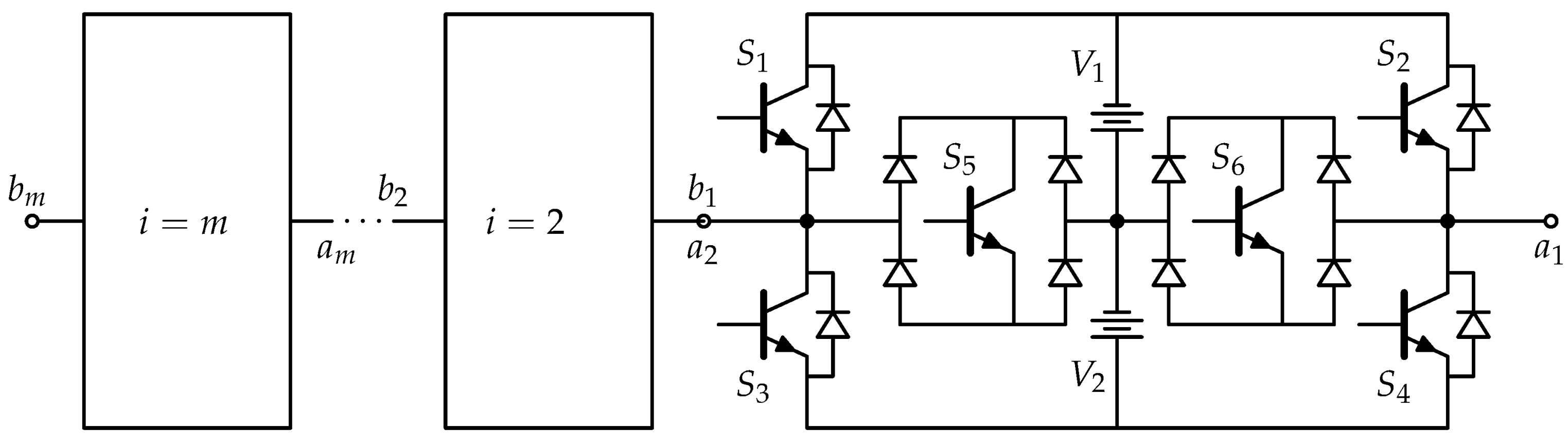

2. Architecture and Principle of Operation

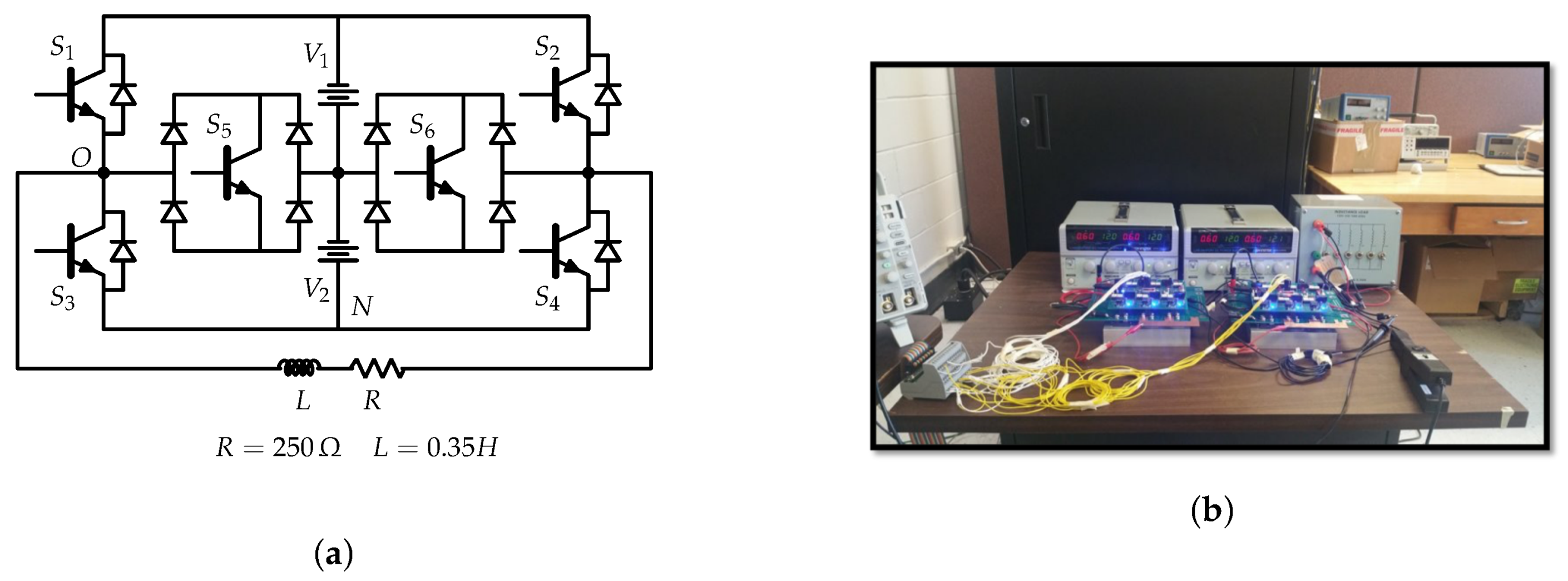

2.1. Architecture

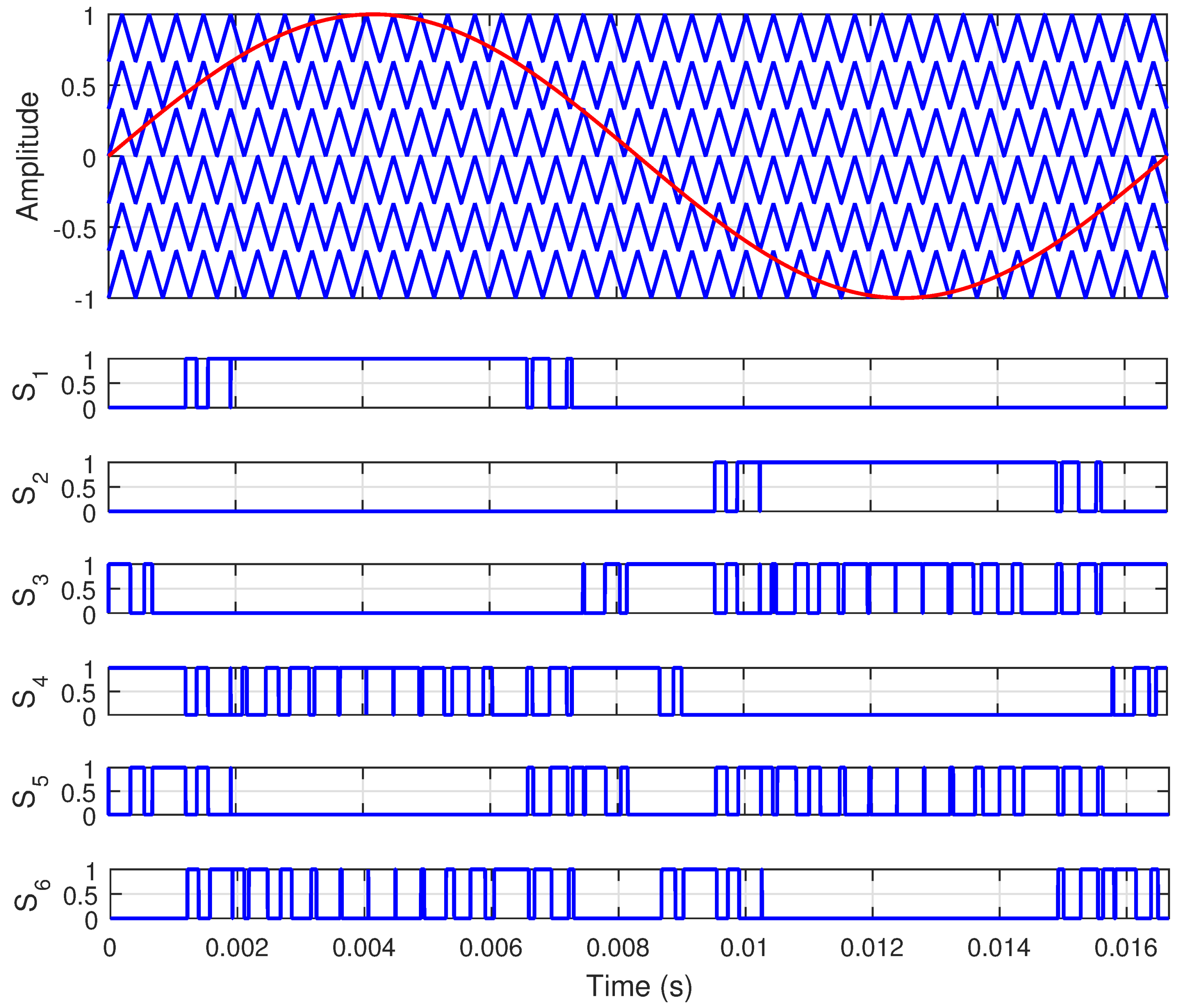

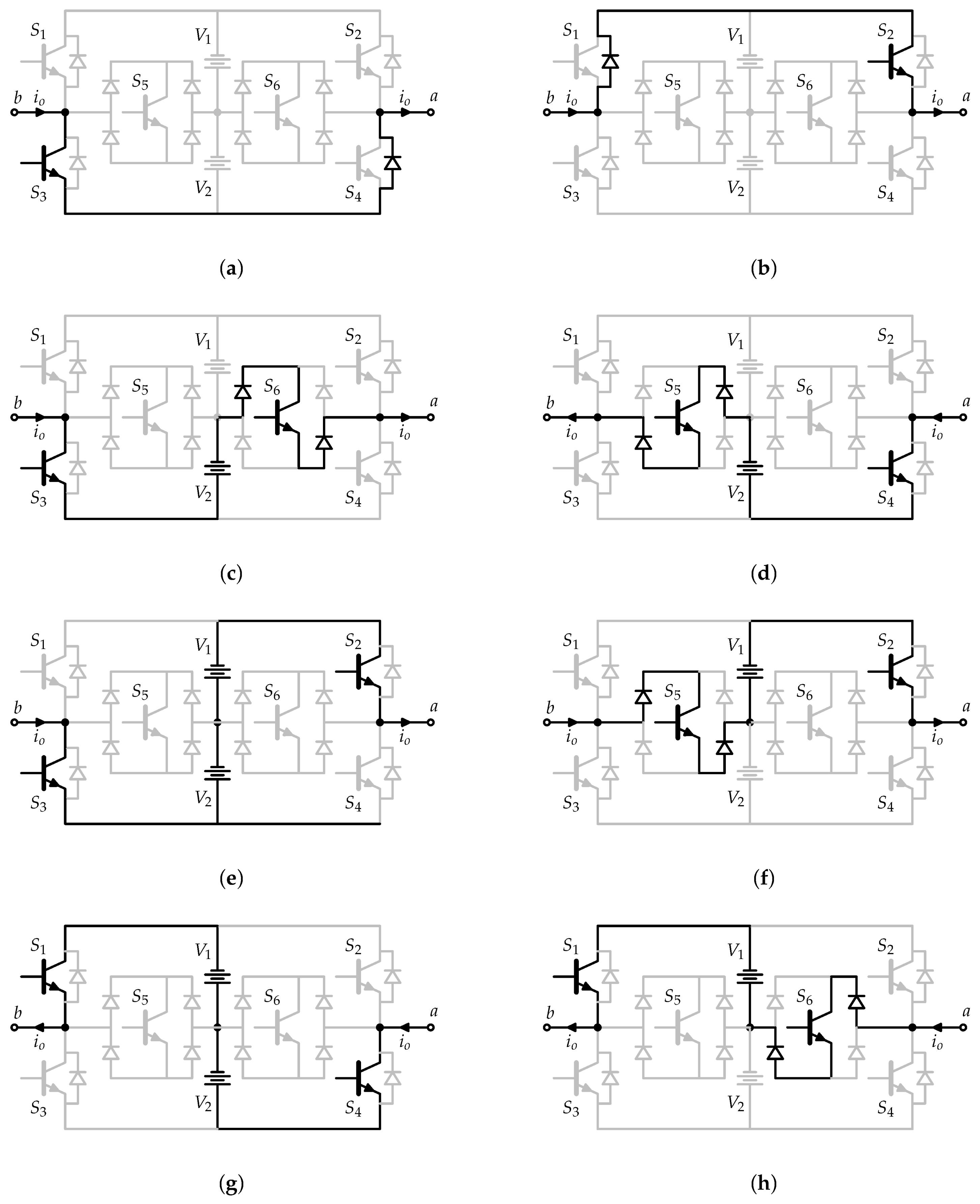

2.2. Operation Principle

3. Comparison with Similar Topologies

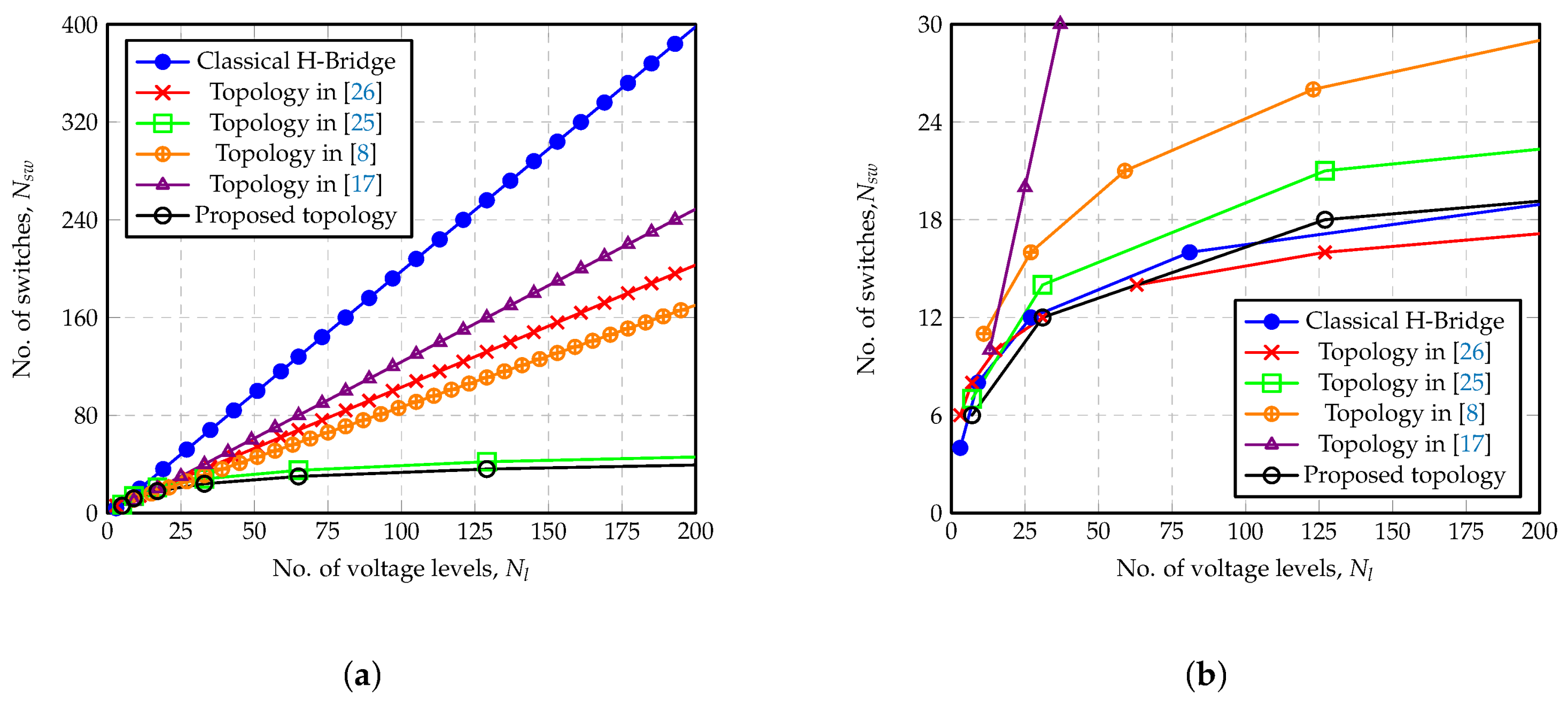

3.1. Number of Semiconductor Devices

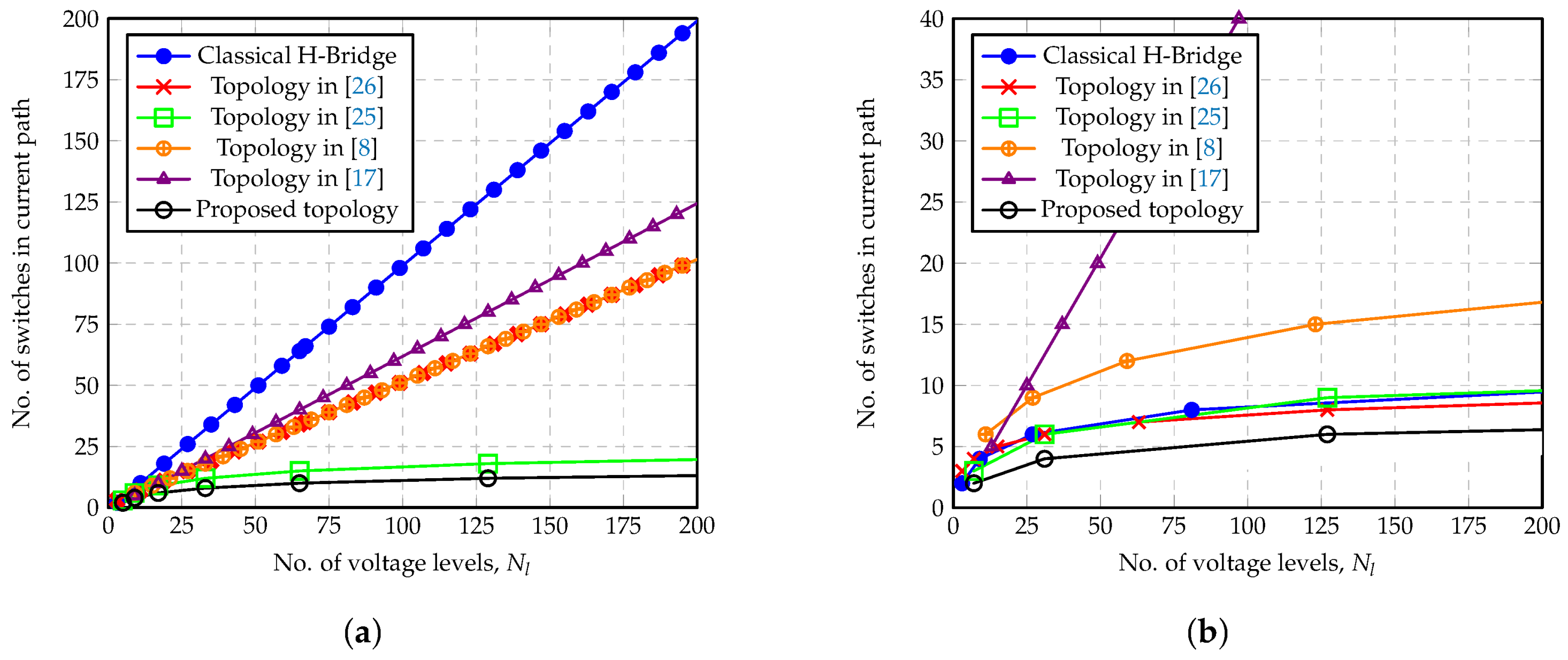

3.2. Number of Semiconductors in the Current Path

3.3. Total Standing Voltage

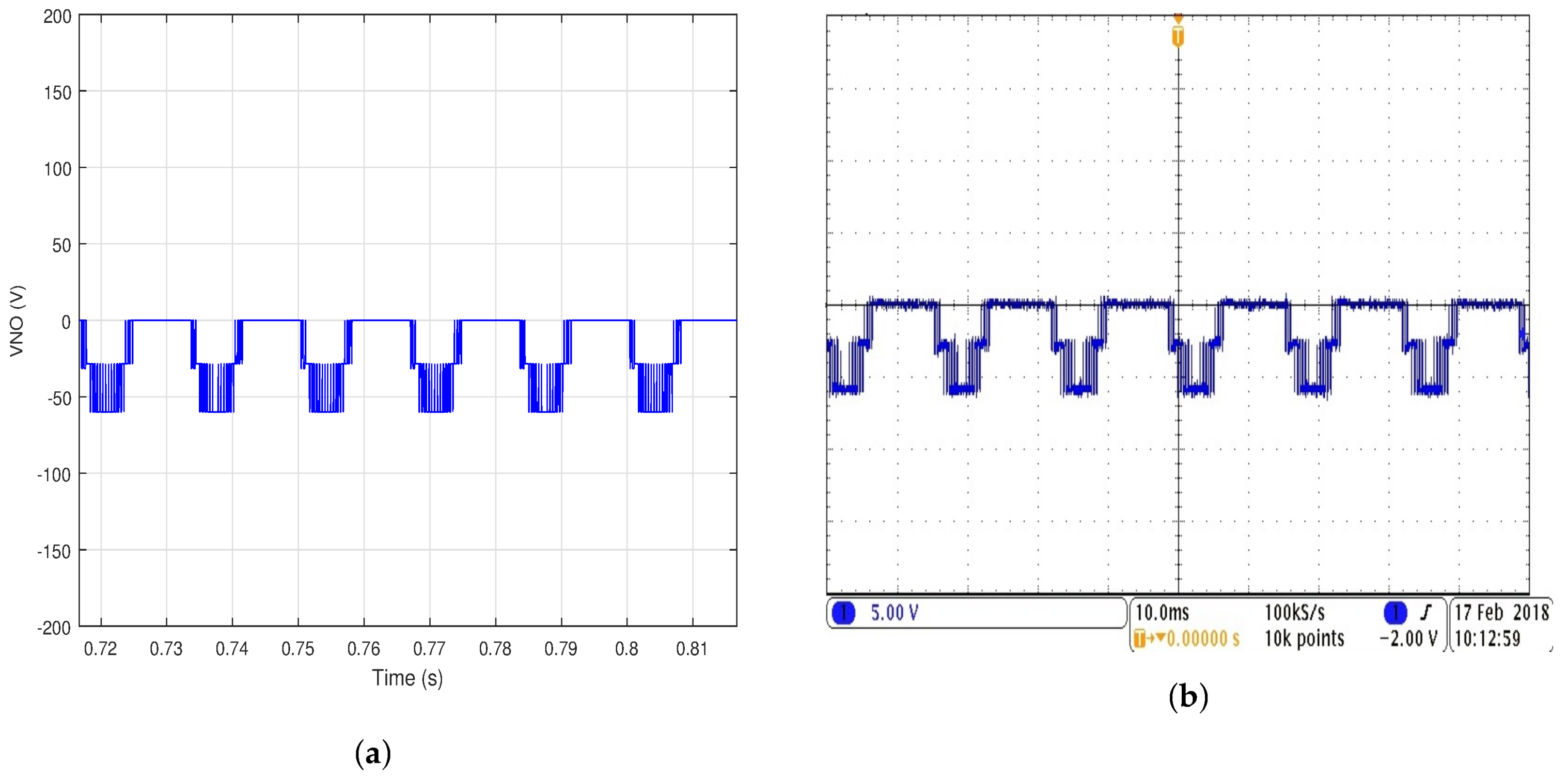

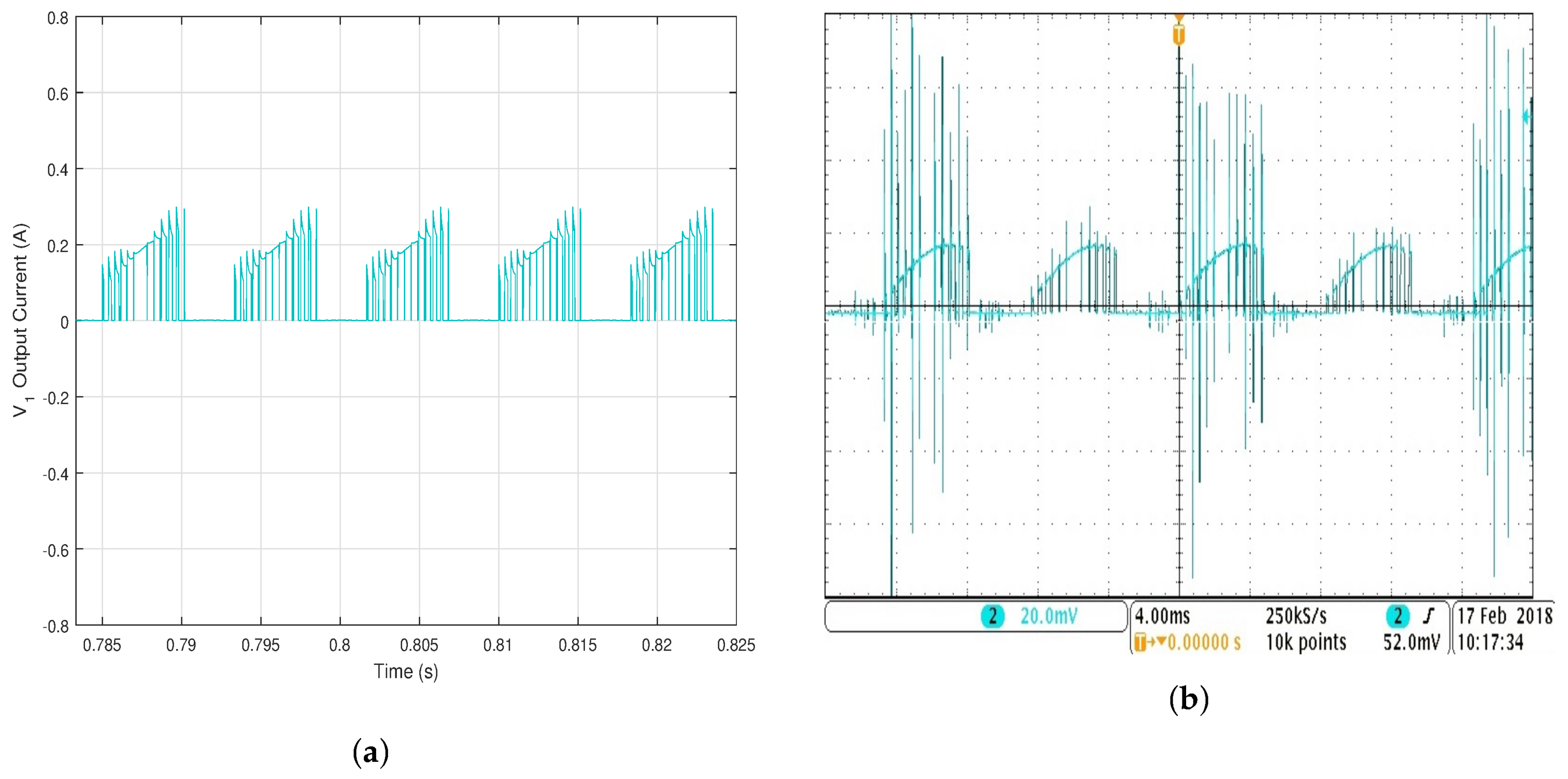

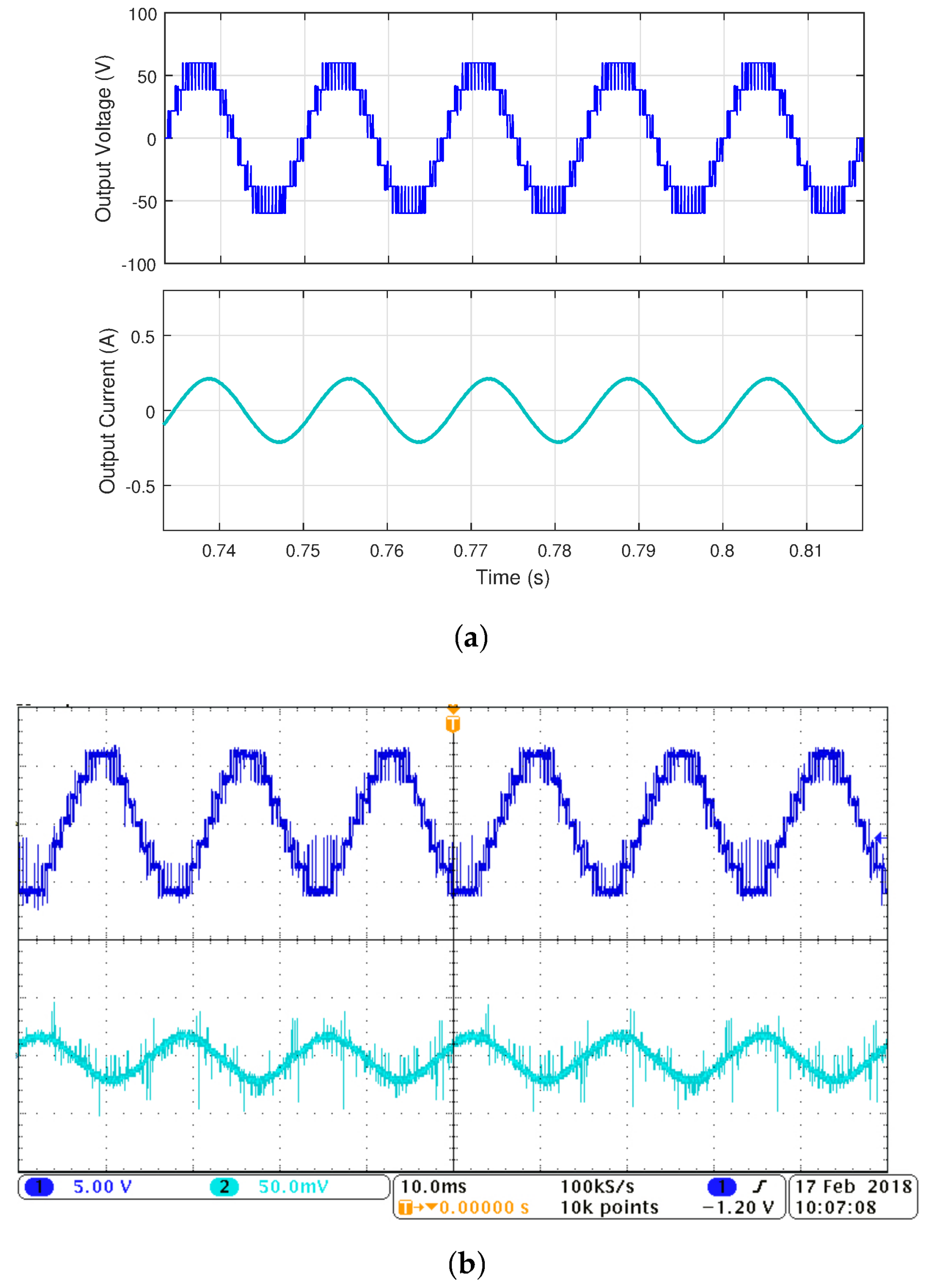

4. Simulation and Experimental Results

5. Conclusions

Acknowledgments

Author Contributions

Conflicts of Interest

References

- Krug, D.; Busse, S.; Beuermann, M. Complete performance test of MV drive with modular multilevel topology for high power oil & gas applications. In Proceedings of the Petroleum and Chemical Industry Technical Conference (PCIC), Philadelphia, PA, USA, 19–22 September 2016; pp. 1–6. [Google Scholar]

- Ma, K.; Blaabjerg, F. Modulation methods for neutral-point-clamped wind power converter achieving loss and thermal redistribution under low-voltage ride-through. IEEE Trans. Ind. Electron. 2014, 61, 835–845. [Google Scholar] [CrossRef]

- Wang, J.; Gao, Y.; Weidong, J. A Carrier-Based Implementation of Virtual Space Vector Modulation for Neutral Point Clamped Three-Level Inverter. IEEE Trans. Ind. Electron. 2017, 64, 9580–9586. [Google Scholar] [CrossRef]

- Shimmyo, S.; Mochikawa, H.; Morishima, Y. Development of high power density converter using flying capacitor multilevel circuits for PV systems. In Proceedings of the 2016 19th IEEE International Conference on Electrical Machines and Systems (ICEMS), Chiba, Japan, 13–16 November 2016; pp. 1–6. [Google Scholar]

- Lei, Y.; Barth, C.; Qin, S.; Liu, W.C.; Moon, I.; Stillwell, A.; Chou, D.; Foulkes, T.; Ye, Z.; Liao, Z.; et al. A 2 kW, Single-Phase, 7-Level Flying Capacitor Multilevel Inverter with an Active Energy Buffer. IEEE Trans. Power Electron. 2017, 32, 8570–8581. [Google Scholar] [CrossRef]

- Babaei, E.; Laali, S.; Alilu, S. Cascaded multilevel inverter with series connection of novel H-bridge basic units. IEEE Trans. Ind. Electron. 2014, 61, 6664–6671. [Google Scholar] [CrossRef]

- Babaei, E.; Laali, S.; Bayat, Z. A single-phase cascaded multilevel inverter based on a new basic unit with reduced number of power switches. IEEE Trans. Ind. Electron. 2015, 62, 922–929. [Google Scholar] [CrossRef]

- Babaei, E.; Alilu, S.; Laali, S. A New General Topology for Cascaded Multilevel Inverters With Reduced Number of Components Based on Developed H-Bridge. IEEE Trans. Ind. Electron. 2014, 61, 3932–3939. [Google Scholar] [CrossRef]

- Mesquita, S.; Antunes, F.; Daher, S. A new bidirectional hybrid multilevel inverter with 49-level output voltage using a single dc voltage source and reduced number of on components. Electr. Power Syst. Res. 2017, 143, 703–714. [Google Scholar] [CrossRef]

- Fazel, S.S.; Bernet, S.; Krug, D.; Jalili, K. Design and comparison of 4-kV neutral-point-clamped, flying-capacitor, and series-connected H-bridge multilevel converters. IEEE Trans. Ind. Appl. 2007, 43, 1032–1040. [Google Scholar] [CrossRef]

- Naderi, R.; Smedley, K. A new hybrid active neutral point clamped flying capacitor multilevel inverter. In Proceedings of the 2015 IEEE Applied Power Electronics Conference and Exposition (APEC), Charlotte, NC, USA, 15–19 March 2015; pp. 794–798. [Google Scholar]

- Naderi, R.; Rahmati, A. Phase-Shifted Carrier PWM Technique for General Cascaded Inverters. IEEE Trans. Power Electron. 2008, 23, 1257–1269. [Google Scholar] [CrossRef]

- Mohan, D.; Kurub, S.B. A comparative analysis of multi carrier SPWM control strategies using fifteen level cascaded H-bridge multilevel inverter. Int. J. Comput. Appl. 2012, 41, 7–11. [Google Scholar]

- Du Toit Mouton, H. Natural balancing of three-level neutral-point-clamped PWM inverters. IEEE Trans. Ind. Electron. 2002, 49, 1017–1025. [Google Scholar] [CrossRef]

- Choi, H.; Zhao, W.; Ciobotaru, M.; Agelidis, V.G. Large-scale PV system based on the multiphase isolated dc/dc converter. In Proceedings of the 2012 3rd IEEE International Symposium on Power Electronics for Distributed Generation Systems (PEDG), Aalborg, Denmark, 25–28 June 2012; pp. 801–807. [Google Scholar]

- Villanueva, E.; Correa, P.; Rodríguez, J.; Pacas, M. Control of a single-phase cascaded H-bridge multilevel inverter for grid-connected photovoltaic systems. IEEE Trans. Ind. Electron. 2009, 56, 4399–4406. [Google Scholar] [CrossRef]

- Samadaei, E.; Gholamian, S.A.; Sheikholeslami, A.; Adabi, J. An envelope type (E-Type) module: asymmetric multilevel inverters with reduced components. IEEE Trans. Ind. Electron. 2016, 63, 7148–7156. [Google Scholar] [CrossRef]

- Taghvaie, A.; Adabi, J.; Rezanejad, M. A Self-balanced Step-up Multilevel Inverter based on Switched-Capacitor Structure. IEEE Trans. Power Electron. 2017, 33, 199–209. [Google Scholar] [CrossRef]

- Barzegarkhoo, R.; Kojabadi, H.M.; Zamiry, E.; Vosoughi, N.; Chang, L. Generalized structure for a single phase switched-capacitor multilevel inverter using a new multiple dc link producer with reduced number of switches. IEEE Trans. Power Electron. 2016, 31, 5604–5617. [Google Scholar] [CrossRef]

- Alishah, R.S.; Hosseini, S.H.; Babaei, E.; Sabahi, M. Optimal design of new cascaded switch-ladder multilevel inverter structure. IEEE Trans. Ind. Electron. 2017, 64, 2072–2080. [Google Scholar] [CrossRef]

- Prayag, A.; Bodkhe, S. Novel Basic Block of Multilevel Inverter Using Reduced Number of On-State Switches and Cascaded Circuit Topology. Adv. Electr. Eng. 2017, 2017, 1–16. [Google Scholar] [CrossRef]

- Chinnaiyan, V.K.; Shanmugam, P.K. A Multilevel Inverter topology using Single Source and Double Source Module with reduced Power Electronic Components. J. Eng. 2017, 2017, 139–148. [Google Scholar]

- Gupta, K.K.; Jain, S. A novel multilevel inverter based on switched DC sources. IEEE Trans. Ind. Electron. 2014, 61, 3269–3278. [Google Scholar] [CrossRef]

- Banaei, M.; Salary, E. Asymmetric Cascaded Multi-level Inverter: A Solution to Obtain High Number of Voltage Levels. J. Electr. Eng. Technol. 2013, 8, 316–325. [Google Scholar] [CrossRef]

- Ahmed, B.; Aganah, K.A.; Ndoye, M.; Arif, M.A.; Luciano, C.; Murphy, G.V. Single-phase cascaded multilevel inverter topology for distributed DC sources. In Proceedings of the 2017 IEEE 8th Annual Ubiquitous Computing, Electronics and Mobile Communication Conference (UEMCON), New York, NY, USA, 19–21 October 2017; pp. 514–519. [Google Scholar]

- Babaei, E.; Hosseini, S.H. New cascaded multilevel inverter topology with minimum number of switches. Energy Convers. Manag. 2009, 50, 2761–2767. [Google Scholar] [CrossRef]

- Xiao, M.; Xu, Q.; Ouyang, H. An Improved Modulation Strategy Combining Phase Shifted PWM and Phase Disposition PWM for Cascaded H-Bridge Inverters. Energies 2017, 10, 1327. [Google Scholar] [CrossRef]

- Lakkas, G. MOSFET power losses and how they affect power-supply efficiency. Analog Appl. 2016, 10, 22–26. [Google Scholar]

| States | |||||||

|---|---|---|---|---|---|---|---|

| 1 | 0 | 0 | 1 | 1 | 0 | 0 | 0 |

| 2 | 0 | 0 | 1 | 0 | 0 | 1 | |

| 3 | 0 | 0 | 0 | 1 | 1 | 0 | |

| 4 | 0 | 0 | 0 | 0 | 1 | 1 | 0 |

| 5 | 0 | 1 | 1 | 0 | 0 | 0 | |

| 6 | 0 | 1 | 0 | 0 | 1 | 0 | |

| 7 | 1 | 0 | 0 | 1 | 0 | 0 | |

| 8 | 1 | 0 | 0 | 0 | 0 | 1 | |

| 9 | 1 | 1 | 0 | 0 | 0 | 0 | 0 |

| Parameter | Value |

|---|---|

| Frequency f | 60 Hz |

| Switching frequency | 2340 Hz |

| Modulation index | |

| DC power sources (5-level) | V V |

| DC power sources (7-level) | V V |

| Load | mH |

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Aganah, K.A.; Luciano, C.; Ndoye, M.; Murphy, G. New Switched-Dual-Source Multilevel Inverter for Symmetrical and Asymmetrical Operation. Energies 2018, 11, 984. https://doi.org/10.3390/en11040984

Aganah KA, Luciano C, Ndoye M, Murphy G. New Switched-Dual-Source Multilevel Inverter for Symmetrical and Asymmetrical Operation. Energies. 2018; 11(4):984. https://doi.org/10.3390/en11040984

Chicago/Turabian StyleAganah, Kennedy Adinbo, Cristopher Luciano, Mandoye Ndoye, and Gregory Murphy. 2018. "New Switched-Dual-Source Multilevel Inverter for Symmetrical and Asymmetrical Operation" Energies 11, no. 4: 984. https://doi.org/10.3390/en11040984