# Article Photometric and Colorimetric Assessment of LED Chip Scale Packages by Using a Step-Stress Accelerated Degradation Test (SSADT) Method

Cheng Qian <sup>1,3</sup> <sup>(D)</sup>, Jiajie Fan <sup>2,3</sup> <sup>(D)</sup>, Jiayi Fang <sup>2,4</sup> <sup>(D)</sup>, Chaohua Yu <sup>2,3</sup>, Yi Ren <sup>1,\*</sup> <sup>(D)</sup>, Xuejun Fan <sup>5</sup> and Guoqi Zhang <sup>6</sup>

<sup>1</sup> School of Reliability and Systems Engineering, Beihang University, Beijing 100191, China; cqian@sklssl.org

<sup>2</sup> College of Mechanical and Electrical Engineering, Hohai University, Changzhou 213022, China; jay.fan@connect.polyu.hk (J.F.); yuchaohua123@hhu.edu.cn (C.Y.)

- <sup>3</sup> Changzhou Institute of Technology Research for Solid State Lighting, Changzhou 213161, China

- <sup>4</sup> College of Mathematics and Physics, Changzhou University, Changzhou 213164, China

- <sup>5</sup> Department of Mechanical Engineering, Lamar University, Beaumont, TX 77710, USA; xfan@lamar.edu

- <sup>6</sup> EEMCS Faculty, Delft University of Technology, Delft 2628, The Netherlands; g.q.zhang@tudelft.nl

- \* Correspondence: renyi@buaa.edu.cn

Received: 17 September 2017; Accepted: 10 October 2017; Published: 16 October 2017

Abstract: By solving the problem of very long test time on reliability qualification for Light-emitting Diode (LED) products, the accelerated degradation test with a thermal overstress at a proper range is regarded as a promising and effective approach. For a comprehensive survey of the application of step-stress accelerated degradation test (SSADT) in LEDs, the thermal, photometric, and colorimetric properties of two types of LED chip scale packages (CSPs), i.e., 4000 °K and 5000 °K samples each of which was driven by two different levels of currents (i.e., 120 mA and 350 mA, respectively), were investigated under an increasing temperature from 55 °C to 150 °C and a systemic study of driving current effect on the SSADT results were also reported in this paper. During SSADT, junction temperatures of the test samples have a positive relationship with their driving currents. However, the temperature-voltage curve, which represents the thermal resistance property of the test samples, does not show significant variance as long as the driving current is no more than the sample's rated current. But when the test sample is tested under an overdrive current, its temperature-voltage curve is observed as obviously shifted to the left when compared to that before SSADT. Similar overdrive current affected the degradation scenario is also found in the attenuation of Spectral Power Distributions (SPDs) of the test samples. As used in the reliability qualification, SSADT provides explicit scenes on color shift and correlated color temperature (CCT) depreciation of the test samples, but not on lumen maintenance depreciation. It is also proved that the varying rates of the color shift and CCT depreciation failures can be effectively accelerated with an increase of the driving current, for instance, from 120 mA to 350 mA. For these reasons, SSADT is considered as a suitable accelerated test method for qualifying these two failure modes of LED CSPs.

**Keywords:** light-emitting diode; chip scale package; accelerated aging; step stress test; reliability qualification

## 1. Introduction

With a wide range of applications of LED products in the lighting market, the reliability of the phosphor converted white LED (pc-white LED) has become a global spread hot research [1–3]. A white LED with high reliability is expected to have a lower luminous flux degradation and color shift under a long-term operation time. Although some fundamental and advanced algorithms were

developed to assist people to understand more about the essence of reliability of pc-white LEDs, unfortunately, the traditional reliability evaluation test methods still require a test time of at least 6000 h, which is definitely a too long time for LED manufacturers [4–13]. Therefore, fast and effective test methods are urgently needed with time and cost considerations [14,15].

In order to shorten the test duration, the constant stress accelerated degradation tests (CSADTs) under manifold uni/multi-environmental overstress conditions are developed for pc-white LEDs and the relevant products [2,16]. Through the deep investigation on the degradation characteristics of LEDs, the accelerated loadings could be anyone among high temperature [17], high moisture [18], and a hybrid combination of both [19–22]. However, the selection of practical accelerated loadings always meets a dilemma between accuracy and universality. Due to the diversity of the failures existing in LED products, a complex coupled stress might be a good accelerated test solution for some LED products but totally invalid for many others. Improvement of the universality is often achieved by reducing the complexity of the accelerated loadings. For a general application, C. Qian et al. developed a CSADT method to reduce the reliability test period from 6000 h to 2000 h for LED luminaires and lamps [17]. Via a boundary curve theory, they proved that the qualification results obtained from the 6000 h test data under 25 °C and 1500 h test data under 55 °C are comparable to each other for a majority of LED lighting products.

Step stress accelerated degradation test (SSADT) is another commonly utilized test plan for lifetime evaluation of high reliability products [23]. When combined with stochastic degradation models such as Gamma process and Wiener process, and statistical luminous flux distributions such as Gaussian distribution, Weibull distribution and Lognormal distribution, SSADT is capable to provide more efficient lifetime evaluation test plan with a smaller sample size and less test time for LED products, as compared to CSADT [24–26]. This makes the optimization of the SSADT test strategy become a very hot research topic. Han proposed three different kinds of design criteria (i.e., C/D/A-optimal design criteria) for optimizing the increment step and test duration of each stress level in the SSADT with a constraint limit on the test cost [25]. Among these three design plans, the C-optimal design was applied to minimize the lifetime model parameters, whereas A-optimal design was applied to minimize the stress level in the step stress loading scheme. Moreover, Hu et al. investigated the optimization plans for the step stress levels in SSADT with a Wiener degradation model, and argued that an optimal strategy for SSADT test can only be accomplished with no more than two step stress levels [26].

Recently, there has been a couple of cases of using SSADT to estimate the lifetimes of LED products. Huang et al. built up a SSADT model by using a stochastic Wiener process to analyze the luminous flux data of pc-white LEDs collected from a k-step stress accelerated degradation test [27]. With this model, a 2-step stress accelerated degradation test is proved to give similar lifetime estimation of the pc-white LEDs when compared to CSADT, but halve the sample size. Cai et al. developed a three-step stress accelerated test on the light source of a LED lamp. The test data were further used together with a fault tree and Monte Carlo algorithm to predict the degradation of luminous flux of the LED lamp [28].

Although the above-mentioned SSADT models gained a successful use in literatures, it is noted that all of them are empirical models whose parameters were obtained by the curve fitting from experimental results. The physical failure mechanisms that occurred during the whole process of SSADT are unfortunately not fully investigated except for a rough assumption of no additional failure modes. Under such circumstances, the development of an optimum step stress strategy is always cumbersome and time-consuming as a huge amounts of experimental works need to be done. To enhance our understanding the failures existing in the SSADT for CSP LEDs, a comprehensive study on the failure analysis during the ageing process of SSADT for CSP LEDs, one of the most promising white LED light sources with benefits of small size, high power, and high color quality, is carried on in this paper. The remainder of this paper is organized as follows: Section 2

introduces the test samples used in this study and some conducted experiments. Section 3 discusses the measurement results from experiments. Finally, the concluding remarks are presented in Section 4.

## 2. Test Samples and Experiments

# 2.1. Test Sample Preparation

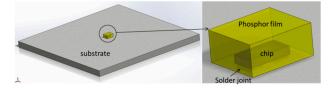

Nowadays, wafer level chip scale packaging (WLCSP) technology has attracted a lot of attention in manufacturing small-size, low assembly dependent, high color rendering, high thermal and electrical conductivities, and high reliable pc-white LEDs, which are called chip scale package LEDs (CSP LEDs) [29,30]. The CSP LEDs produced by the flip chip process were adopted in this study. As illustrated in Figure 1, this kind of LED has a simple structure that only consists of a phosphor layer, blue LED chip, and solders joints attached to substrate, resulting in relatively simple failure modes during the SSADT process as well.

Figure 1. The structure of white chip scale package LEDs (LED CSP).

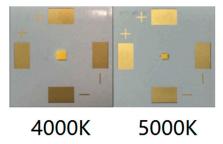

In this paper, two types of CSP LED samples with different powers were prepared in house with correlated color temperatures (CCTs) of 4000 °K and 5000 °K, respectively, as shown in Figure 2. Information of the prepared samples is given in Table 1, including the phosphor weight ratio, phosphor composition, and sample dimension. Among the phosphor compositions, YAG 04, GM537H, and RH650D are the commercial yellow, green, and red phosphors, respectively. The LED chips were bonded on an aluminum substrate using a eutectic bonding process with the SAC 305 solder paste. Depending on the applied LED chips, the rated currents of driving the CSP LED samples with CCTs of 4000 °K and 5000 °K are 350 mA and 120 mA, respectively. Then, the 4000 °K and 5000 °K samples were further mounted on an aluminum core board by customized aluminum clamps for SSADT, as shown in Figure 3, where the samples were tested under 120 mA during the SSADT process.

Figure 2. Illustration of the test samples.

| Table 1. | Information | of the C | SP LED | samples.   |

|----------|-------------|----------|--------|------------|

| Iuvic II | muormanon   | or the e |        | builtpico. |

| Target CCTs | Phosphor Weight | Phosphor Composition   | Sample Dimension                                                                    |

|-------------|-----------------|------------------------|-------------------------------------------------------------------------------------|

|             | Ratio %         | (YAG04:GM537H5:RH650D) | (L × W × H)                                                                         |

| 4000 °K     | 18.5            | 3.2:12.6:4.8           | 0.97 mm $\times$ 0.97 mm $\times$ 0.15 mm 0.78 mm $\times$ 0.38 mm $\times$ 0.14 mm |

| 5000 °K     | 18.5            | 0:3.38:1               |                                                                                     |

**Figure 3.** The CSP LED samples under 120 mA during the step-stress accelerated degradation test (SSADT) process. (Top: 4000 °K samples; Bottom: 5000 °K samples).

### 2.2. Junction Temperature Measurements

The junction temperature of the LED CSP test sample was measured by a linear relationship between junction temperature and voltage in semiconductor packages [31]. The temperature-voltage curves of the test samples in this study were measured by a LEETs LEDT-300B test equipment where its main technical characteristics are listed in Table 2. The temperature-voltage coefficients, also called *K* factors, were then extracted from these temperature-voltage curves. Once the *K* coefficient is obtained, the junction temperature of a CSP LED sample can be calculated based on its driving voltage by Equation (1).

$$T_{j} = T_{a} + (V_{j} - V_{a})/K$$

(1)

where  $T_a$  is the environmental temperature and  $V_a$  is the voltage of the test sample under a very small driving current, such as 1 mA;  $T_i$  is the junction temperature, and  $V_a$  is the voltage of the test sample under the given driving current. The junction temperature can be further used to estimate the junction-to-air thermal resistance of the test sample by Equation (2).

$$R_{\rm th} = \frac{T_{\rm j} - T_{\rm p}}{P_{\rm th}} = \frac{T_{\rm j} - T_{\rm p}}{P_{\rm tot} - P_{\rm opt}}$$

(2)

where  $R_{\text{th}}$  is the junction-to-board thermal resistance,  $T_{\text{p}}$  is the board temperature,  $P_{\text{th}}$  is the sample's thermal power, calculated by subtracting the optical power from the total electrical power.

| Item                                     | Description                         |

|------------------------------------------|-------------------------------------|

| Manufacturer                             | LEETs Lighting Shanghai             |

| Rated voltage                            | 220 V 50/60 Hz                      |

| Operational current                      | <0.5 A                              |

| Junction temperature measurement current | $1\mathrm{mA}/5\mathrm{mA}\pm0.2\%$ |

| Temperature tolerance of K coefficient   | ±0.5 °C                             |

| Sampling pulse width                     | 5 ms                                |

| Junction temperature measurement error   | ±1 °C                               |

Table 2. Technical characteristics of the LEETS LEDT-300B test equipment.

#### 2.3. Step Stress Accelerated Degradation Test

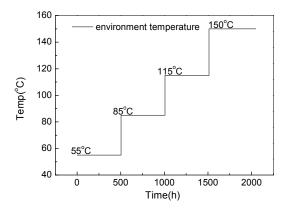

Determination of the stress levels during the SSADT process obeys the following principles. Firstly, no additional failure modes should be introduced during the whole test process. Secondly, the maximum environmental temperature should be high enough to reduce the test period. Thirdly, the testing time at each stress level should be long enough with a great exposure to the potential failure risk. When considering all of the above-mentioned issues, the environmental temperature was set from 55 °C to 150 °C, with an increment of 30 °C in every 504 h, as illustrated in Figure 4, in SSADT. During the test process, the LED CSP test samples were divided into two groups each of which contains 5 samples, under driving currents of 350 mA and 120 mA, respectively. Note that,

the 5000 °K sample under a driving current of 350 mA is in about three times overdrive since its rated current is only 120 mA. Once in a while, the test was paused to measure the photometric and chromatic properties, such as spectral power distributions (SPD), luminous flux, color coordinates, and CCT of the test samples using a 0.5 m integrating sphere at room temperature. In total, there are 10 times measurements, each of which the stoppage time is less than 8 h.

Figure 4. Illustration of the 4-step stress accelerated degradation test.

## 3. Results and Discussion

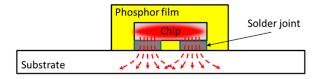

## 3.1. Thermal Analysis

As shown in Figure 5, most of the heat generated by the chip is dissipated through the LED body, the dissipation efficiency relies on thermal properties of all composing materials and interface along the heat transfer path. During the SSADT process, degradation of the thermal properties of the test sample usually appears concurrently with degradation of the photometric and chromatic properties of the CSP LED samples. Early tests on LEDs under 85 °C/85RH conditions showed that the LED junction temperature increases continuously along with the progress of the test due to a moisture induced delamination between the chip and lead frame [32]. A similar junction temperature rising phenomenon is also observed in our experiments.

Figure 5. Illustration of the heat transfer path in a CSP LED.

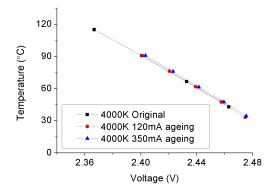

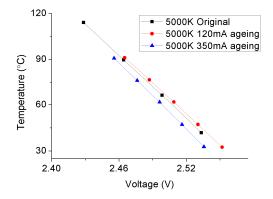

The temperature-voltage curves of typical 4000 °K and 5000 °K samples before and after SSADTs under 120 mA and 350 mA are plotted in Figures 6 and 7 for comparison. These curves show the linear relationships between the junction temperature and voltage driving under 1 mA of the test samples.

As shown in Figure 6, the temperature-voltage curves of the 4000 °K sample before and after SSADT remain the same under a driving current of 120 mA. Even driven by a current of 350 mA, the temperature-voltage curve only shifts slightly to the right when compared to that measured before SSADT. As a result, it can be argued that it will not introduce extra failures by elevating the driving current from 120 mA to 350 mA.

For the 5000 °K sample, a significant driving current effect is exhibited on the temperature-voltage curves, as shown in Figure 7. Similar to the 4000 °K sample, the temperature-voltage curve is slightly shifted to the right under its rated current which is 120 mA. However, by increasing the driving current to 350 mA, an apparently opposite shift is found in between the temperature-voltage curves before and

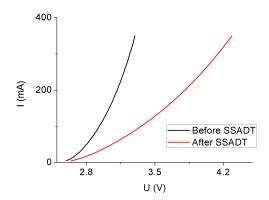

after SSADT. This might be because that, under a long-term over-driving condition, the active layer of the LED chip is partially damaged to reduce both the optical and heat output of the 5000 °K sample. Figure 8 plots the I-V curves of the 5000 °K sample under a driving current of 350 mA before and after SSADT. It can be seen that after SSADT, the 5000 °K sample exhibited a "flat" I-V curve which can be regarded by connecting a series resistance induced from the damage in the active layer [33].

Figure 6. Temperature-voltage curves of the 4000 °K samples before and after SSADTs with 2046 h.

Figure 7. Temperature-voltage curves of the 5000 °K samples before and after SSADT with 2046 h.

Figure 8. Current-voltage curves of the 5000 °K samples before and after SSADT.

Based on the temperature-voltage curves plotted in Figures 6 and 7, the junction temperatures of test samples before and after SSADT were calculated by Equation (1). The calculation process is divided into three steps: Firstly, a driving current (i.e., 350 mA for the 5000 °K samples and 120 mA for the 4000 °K samples) was applied on the test sample for 30 min that is long enough to reach a steady-state temperature distribution over that sample; then, the driving current was turned off, and immediately a 1 mA current was applied instead; lastly, the voltage of the sample was measured to

calculate the junction temperature by using Equation (1), in which the *K* coefficient was extracted from the plots shown in Figures 6 and 7. Subsequently, the junction-to-board thermal resistances were further calculated by Equation (2), and enumerated in Table 3 with the calculated junction temperatures and other parameters used in Equation (2). According to Table 3, the junction temperature of the 4000 °K sample continuously increases with the rise of the driving current. This implies that the driving current acts the same with the temperature stress on the degradation of the 4000 °K samples. However, as to the 5000 °K sample, its junction temperature increases under the driving current of 120 mA,

but drop obviously when the driving current is lifted up to 350 mA. Such a reduction is because of the additional failures on the 5000 °K sample that was caused by the over-driving current. In addition, a relatively higher increase rate on board temperatures of both 4000 °K and 5000 °K samples (except for those driven under 350 mA) was observed as compared to the junction temperatures. This makes the junction-to-board thermal resistances of these samples show a continuous decrease during SSADT. As to the 5000 °K samples after SSADT driven under 350 mA, the junction-to-board thermal resistances were dramatically reduced to about 1/3 of its original value, proving that the LED chip might be seriously damaged by the over-driving current.

| Driving Conditions      | 4000 °K Sample             |              |                  | 5000 °K Sample      |                            |              |                  |                     |

|-------------------------|----------------------------|--------------|------------------|---------------------|----------------------------|--------------|------------------|---------------------|

|                         | <i>Т</i> <sub>ј</sub> (°С) | $T_{p}$ (°C) | $P_{\rm th}$ (W) | $R_{\rm th}$ (°C/W) | <i>Т</i> <sub>ј</sub> (°С) | $T_{p}$ (°C) | $P_{\rm th}$ (W) | $R_{\rm th}$ (°C/W) |

| Original                | 75.52                      | 48.08        | 0.710            | 38.63               | 54.01                      | 34.37        | 0.219            | 89.84               |

| After test under 120 mA | 84.38                      | 58.59        | 0.744            | 34.65               | 59.78                      | 44.66        | 0.212            | 71.39               |

| After test under 350 mA | 89.41                      | 69.01        | 0.745            | 27.37               | 51.27                      | 41.99        | 0.297            | 31.24               |

Table 3. Thermal properties of test samples before and after SSADT.

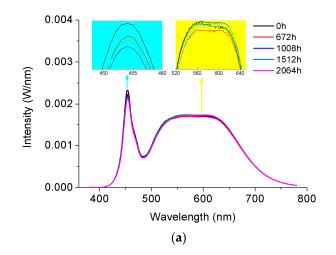

## 3.2. Spectral Power Distribution Attenuation

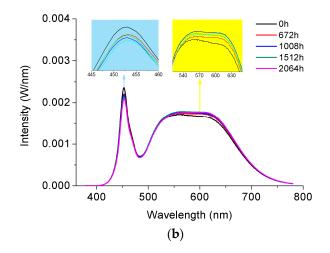

Figures 9 and 10 reveal the attenuation of SPDs of the test samples by plotting a number of SPDs of randomly selected 4000 °K and 5000 °K samples measured in about every 504 h of SSADT under the driving currents of 120 mA and 350 mA, respectively. As shown in Figure 9a, with the increase of the ageing time, the blue peak of the SPD is slightly weakened, whereas the phosphor converted peak shows a fluctuating downward trend. This implies that degradation of the LED chip and phosphor is evolved with different failure mechanisms. During SSADT, the LED chip is continuously degraded, corresponding to the rise of junction temperature, as shown in Table 3. However, the degradation of phosphor is not explicit due to the mutual synergistic effect of different thermal quenching failure mechanisms of its material constitutions [34].

Figure 9. Cont.

**Figure 9.** Attenuation of spectral power distributions of the 4000 °K samples during SSADT. (**a**) Driving by a 120 mA current; (**b**) Driving by a 350 mA current.

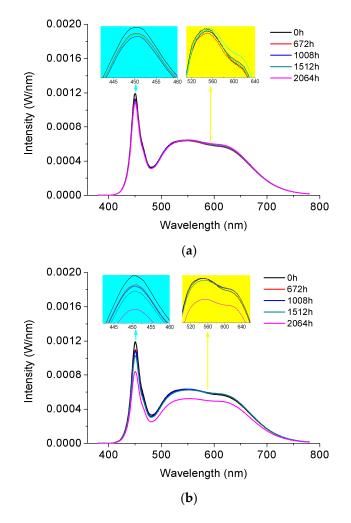

**Figure 10.** Attenuation of spectrum power distributions of the 5000 °K samples during SSADT. (a) Driving by a 120 mA current; (b) Driving by a 350 mA current.

The time-varying SPDs of the 4000 °K sample during SSADT under a driving current of 350 mA are plotted in Figure 9b. It can be seen that the SPDs shown in Figure 9b follow the same but more exaggerated attenuation trend as compared to those shown in Figure 9a. This agrees with

the observations from the temperature-voltage curves shown in Figure 6 that no additional failure is occurred by increasing the driving current from 120 mA to 350 mA.

The SPD attenuation is not altered for the 5000 °K sample under 120 mA during SSADT, as shown in Figure 10a, and under 350 mA during the first 1500 h of SSADT, as shown in Figure 10b. However, a dramatic fall is observed all over the SPD of the 5000 °K sample after 1500 h ageing under 350 mA. This supports the argument that the LED chip has been seriously damaged by such a high driving current after a long term of SSADT, as discussed in the aforementioned subsection.

### 3.3. Lumen Maintenance Depreciation

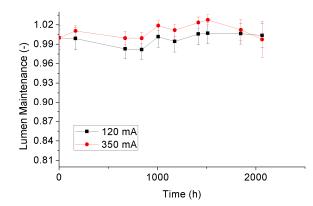

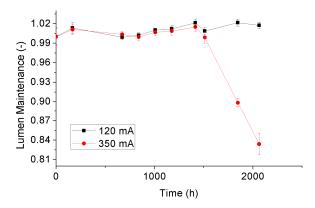

Luminous fluxes of the test samples at a certain ageing time can be calculated based on their SPDs at that time. Then, by normalizing these luminous fluxes with the average of the initial values at 0 h, the lumen maintenances can be further determined. Figures 11 and 12 display the variance trends of the averaged lumen maintenances with statistical error bars of the 4000 °K and 5000 °K samples, respectively. It can be seen that lumen maintenances of the 4000 °K and 5000 °K tests samples under a driving current of 120 mA are not presented downward trends during the whole SSADT process, indicating that they are still in a seasoning state. Driving by a current of 350 mA, the 4000 °K and 5000 °K tests samples show a same trend on lumen maintenances in the first 1500 h. After that, both test sample behave degradation under the dual effect of high temperature and high current. When compared to the 4000 °K samples, the 5000 °K samples, of which the rated current is far less than 350 mA, expressed a much rapid lumen maintenance depreciation that is caused by LED chip damage. This implies the application of a high driving current is helpful to accelerate the lumen maintenance depreciation of the test samples. However, an extreme over-drive current should be avoided since it increases the risk of chip damage to a great extent.

Figure 11. Lumen maintenance depreciation of the 4000 °K samples.

Figure 12. Lumen maintenance depreciation of the 5000 °K samples.

## 3.4. Color Shift

Color shift is a LED reliability characteristic related to the deviation of color coordinates from the initial values, and therefore can be calculated by Equation (3).

$$du'v' = \sqrt{\left(u' - u'_0\right)^2 + \left(v' - v'_0\right)^2}$$

(3)

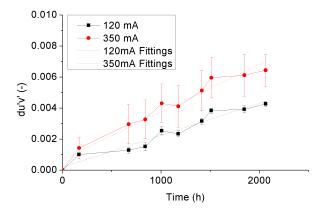

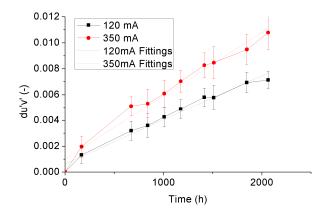

in which u' and v' are color coordinates in CIE 1976 color space, and  $u_0'$  and  $v_0'$  are the initial values of the color coordinates [35–39]. Figures 13 and 14 display the variance trends of the averaged du'v' with statistical error bars of the 4000 °K and 5000 °K samples, respectively. An overall view from these two figures is that the du'v' of both 4000 °K and 5000 °K samples show linear growing trends with the increase of ageing time, in which the growth rate is highly dependent on the driving current. Equation (4) is applied to describe the growing curve of du'v' of the test samples, and the corresponding fitting curves to the 4000 °K and 5000 °K samples are also plotted with the dotted lines in Figures 13 and 14, respectively.

$$du'v' = C_1 \times t + C_2 \tag{4}$$

in which  $C_1$  is the growth rate,  $C_2$  is the intercept, and *t* is the ageing time.

Figure 13. Color shift of the 4000 °K samples.

Figure 14. Color shift of the 5000 °K samples.

Table 4 enumerates the fitting coefficients in Equation (3) of the 4000  $^{\circ}$ K and 5000  $^{\circ}$ K samples under driving currents of 120 mA and 350 mA. It can be seen that the growth rates of the 4000  $^{\circ}$ K and 5000  $^{\circ}$ K samples aged under each own rated current are similar. The growth rate will move synchronously with the adjustment of the driving current. For quantitatively qualifying the current

effect on color shift of the test samples, the acceleration factors in between both samples were calculated based on the growth rates of them by Equation (5), and shown in Table 4 as well.

$$AF_{du'v'} = C_{1,350\text{mA}} / C_{1,120\text{mA}}$$

(5)

in which  $AF_{du'v'}$  is the acceleration factor of the growth rate of color shift,  $C_{1,350 \text{ mA}}$  and  $C_{1,120 \text{ mA}}$  are the growth rates of the test samples aged under currents of 350 mA and 120 mA, respectively.

| Driving Conditions  | Parameters                                     | 4000 °K Sample                               | 5000 °K Sample                                                            |

|---------------------|------------------------------------------------|----------------------------------------------|---------------------------------------------------------------------------|

| Driving by 120 mA   | C <sub>1,120 mA</sub><br>C <sub>2,120 mA</sub> | $2.05 	imes 10^{-6} \ 1.94 	imes 10^{-4}$    | $3.42 	imes 10^{-6} \ 6.28 	imes 10^{-4}$                                 |

| Driving by 350 mA   | C <sub>1,350 mA</sub><br>C <sub>2,350 mA</sub> | $3.06 	imes 10^{-6}$<br>$7.03 	imes 10^{-4}$ | $\begin{array}{c} 4.89 \times 10^{-6} \\ 1.02 \times 10^{-3} \end{array}$ |

| AF <sub>du'v'</sub> |                                                | 1.49                                         | 1.43                                                                      |

**Table 4.** Parameters of the linear color shift model.

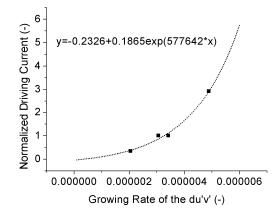

As seen in Figures 13 and 14 and Table 4, by increasing the driving current from 120 mA to 350 mA, the growth rates of du'v' of both 4000 °K and 5000 °K samples are increased with similar acceleration factors which are independent on the rated currents of the test samples. Therefore, it allows us to normalize the driving currents of both 4000 °K and 5000 °K samples by their rated currents to give an overall view of the driving current effect on du'v' of the test samples, as shown in Figure 15. This driving current effect is possible to be fitted by a three-parameter exponential curve in which the offset, pre-factor and power factor are -0.2326, 0.1865 and 577,642, respectively, as shown in Figure 15 as well.

**Figure 15.** Current effect on the growth rate of the du'v'.

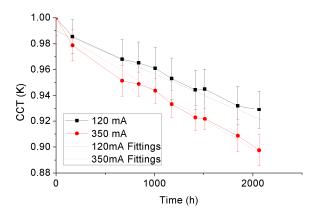

## 3.5. CCT Depreciation

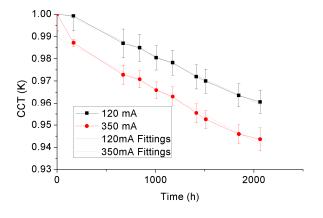

The correlated color temperature (CCT) represents the corresponding blackbody locus temperature of a pair of color coordinates along the iso-temperature line. Therefore, during SSADT, the CCT will show a time-varying variance along with the change of color coordinates. Figure 16 and display the CCTs of the 4000 °K and 5000 °K samples with statistical error bars during SSADT. For the purpose of comparison, CCTs of each of the test samples are normalized by its initial values. According to Figures 16 and 17, the CCTs of both 4000 °K and 5000 °K samples show linear degradation trends with the ageing time, opposite to the varying trends of du'v'. This linear degradation trend of CCTs was also found in other scenarios, for instance, from high power LED lamps under an 85 °C/85% relative humidity test [40]. To describe this linear degradation trend, Equation (6) is applied

in our study, and the acceleration factor of the degradation rates extracted from two different driving currents is calculated by Equation (7).

$$CCT = D_1 \times t + D_2 \tag{6}$$

$$AF_{CCT} = D_{1350mA} / D_{1120 mA} \tag{7}$$

in which  $D_{1350 \text{ mA}}$  is the degradation rate,  $D_{2120 \text{ mA}}$  is the intercept, *t* is the ageing time,  $AF_{CCT}$  is the acceleration factor,  $D_{1350 \text{ mA}}$ , and  $D_{1120 \text{ mA}}$  are the degradation rates of the test samples aged under currents of 350 mA and 120 mA, respectively.

**Figure 16.** CCT depreciation of the 4000 °K samples.

Figure 17. CCT depreciation of the 5000 °K samples.

Table 5 enumerates the fitting parameters in Equation (6) of the 4000 °K and 5000 °K samples under driving currents of 120 mA and 350 mA, and the resulting acceleration factors of the degradation rates. From Table 5, it can be seen that the driving current also plays an important role on the degradation of CCTs for both test samples. Such an effect is found relatively more significant on the 5000 °K samples.

| Driving Conditions | Parameters                                   | 4000 °K Sample                 | 5000 °K Sample                 |

|--------------------|----------------------------------------------|--------------------------------|--------------------------------|

| Driving by 120 mA  | D <sub>1120 mA</sub><br>D <sub>2120 mA</sub> | $-2.05 	imes 10^{-5}$<br>1.002 | $-3.05 	imes 10^{-5} \\ 0.990$ |

| Driving by 350 mA  | D <sub>1350 mA</sub><br>D <sub>2350 mA</sub> | $-2.35 	imes 10^{-5} \\ 0.990$ | $-4.14	imes 10^{-5}\ 0.983$    |

| AF <sub>CCT</sub>  |                                              | 1.15                           | 1.36                           |

Table 5. Parameters of the linear CCT model.

### 4. Conclusions

In this paper, the reliability issues, including thermal, photometric, and colorimetric properties, of LED chip scale packages during SSADT with driving currents of 120 mA and 350 mA were thoroughly investigated. The ageing process of SSADT is composed by four temperature stages from 55 °C to 150 °C, each step lasts 504 h. Two different types of LED chip scale packages were tested. The rate current is 350 mA for the 4000 °K samples, and 120 mA for the 5000 °K samples.

The thermal properties of the test samples were investigated via the comparison of junction temperatures and the temperature-voltage curves before and after SSADT. For a sample driving by a current below or equaling to the rated current, its junction temperature after SSADT was increased to a certain extent depending on the driving current. However, for the 5000 °K sample overdriven by a current of 350 mA, the junction temperature after SSADT was reduced, owing to a left shift of the temperature-voltage curve. This might be caused by partial damage in the active layer of the LED chip induced by a synergistic effect of the high temperature and overdrive current. The supporting evidence was obtained from two aspects: firstly, an obvious series resistance existed in the I-V curve of the 5000 °K sample after SSADT; secondly, a dramatic SPD attenuation of the 5000 °K sample was observed in the end of SSADT.

Finally, the time-dependent variances of lumen maintenance, color shift, and CCT of the test samples during SSADT, and the driving current effect on these results were studied in detail. The results suggest that failures, such as color shift and CCT depreciation of the LED chip scale packages, can be effectively aroused by SSADT. The varying rates of these two failures are further proved to have a positive relationship with the driving current.

At last, it is worth mentioning that similar time-varying trends of the photometric and colorimetric parameters observed in this study would be likely to occur in all types of phosphor converted LEDs, since the failure mechanisms among them are not significantly different. More case studies on other type of phosphor converted LEDs will be investigated in future studies to explore the applicability and usability of SSADT in fast evaluation of the reliability of LEDs.

Acknowledgments: The work described in the paper was partially supported by the Natural Science Foundation of Jiangsu Province (No. BK20150249), the National High-Tech Research and Development Program of China (863 Program) (No. 2015AA033301), the National Natural Science Foundation of China (61673037), and the Postgraduate Research & Practice Innovation Program of Jiangsu Province.

**Author Contributions:** Cheng Qian and Jiajie Fan conceived and designed the experiments; Jiayi Fang and Chaohua Yu performed the experiments; Cheng Qian and Jiajie Fan analyzed the data; Cheng Qian wrote the paper; Yi Ren, Xuejun Fan, and Guoqi Zhang contributed reagents/materials/analysis tools.

**Conflicts of Interest:** The authors declare no conflicts of interest. The founding sponsors had no role in the design of the study; in the collection, analyses, or interpretation of data; in the writing of the manuscript, and in the decision to publish the results.

### Abbreviations

- CCT Correlated Color Temperature

- CSP Chip Scale Package

- CSADT Constant-Stress Accelerated Degradation Test

- LED Light-emitting Diode

- SPD Spectral Power Distribution

- SSADT Step-Stress Accelerated Degradation Test

- WLCSP Wafer Level Chip Scale Packaging

## References

- Wang, F.K.; Lu, Y.C. Useful lifetime analysis for high-power white LEDs. *Microelectron. Reliab.* 2014, 54, 1307–1315. [CrossRef]

- 2. Sun, B.; Jiang, X.; Yung, K.-C.; Fan, J.; Pecht, M. A review of prognostics techniques for high-power white LEDs. *IEEE Trans. Power Electron.* **2017**, *32*, 6338–6362. [CrossRef]

- 3. Van Driel, W.D.; Fan, X.J. Solid State Lighting Reliability: Components to Systems; Springer: New York, NY, USA, 2012.

- 4. IES-LM-80-08. *Approved Method for Lumen Maintenance Testing of LED Light Source;* Illuminating Engineering Society: New York, NY, USA, 2008.

- 5. IES-TM-21-11. *Projecting Long Term Lumen Maintenance of LED Light Sources;* Illuminating Engineering Society: New York, NY, USA, 2011.

- 6. ENERGY STAR®Program Requirements for Solid State Lighting Luminaires Eligibility Criteria—Version 1.2. Available online: https://www.energystar.gov/ia/partners/product\_specs/program\_reqs/SSL\_prog\_req. pdf?d519-671a (accessed on 12 October 2017).

- ENERGY STAR®Program Requirements for Lamps (Light Bulbs) Eligibility Criteria—Version 1.1. Available online: https://www.energystar.gov/sites/default/files/ENERGY%20STAR%20Lamps%20V1% 201\_Specification.pdf (accessed on 12 October 2017).

- 8. IEC/PAS 62612. Self-Ballasted LED-Lamps for General Lighting Services—Performance Requirements; International Electrotechnical Commission: Geneva, Switzerland, 2009.

- 9. IES-TM-28-14. *Projecting Long-Term Luminous Flux Maintenance of LED Lamps and Luminaires;* Illuminating Engineering Society: New York, NY, USA, 2014.

- 10. Fan, J.J.; Yung, K.C.; Pecht, M. Lifetime estimation of high-power white LED using degradation-data-driven method. *IEEE Trans. Device Mater. Reliab.* **2012**, *12*, 470–477. [CrossRef]

- Huang, J.L.; Golubović, D.S.; Koh, S.; Yang, D.G.; Li, X.P.; Fan, X.J.; Zhang, G.Q. Degradation modeling of mid-power white-light LEDs by using Wiener process. *Opt. Express* 2015, 23, A966–A978. [CrossRef] [PubMed]

- 12. Tseng, S.T.; Peng, C.Y. Stochastic diffusion modeling of degradation data. J. Data Sci. 2007, 5, 315–333.

- Van Driel, W.D.; Schuld, M.; Jacobs, B.; Commissaris, F.; van der Eyden, J.; Hamon, B. Lumen maintenance predictions for LED packages using LM80 data. In Proceedings of the 2015 16th International Conference on Thermal, Mechanical and Multi-Physics Simulation and Experiments in Microelectronics and Microsystems (EuroSimE 2015), Budapest, Hungary, 19–22 April 2015.

- Tarashioon, S.; Baiano, A.; Van Zeijl, H.; Guo, C.; Koh, S.W.; Van Driel, W.D.; Zhang, G.Q. An approach to "Design for Reliability" in solid state lighting systems at high temperatures. *Microelectron. Reliab.* 2012, 52, 783–793. [CrossRef]

- 15. Hamon, B.; Driel, W.D.V. LED degradation: From component to system. *Microelectron. Reliab.* **2016**, *64*, 599–604. [CrossRef]

- 16. Escobar, L.A.; Meeker, W.Q. A review of accelerated test models. Stat. Sci. 2006, 21, 552–577. [CrossRef]

- 17. Qian, C.; Fane, X.J.; Fanb, J.J.; Yuan, C.A.; Zhang, G.Q. An accelerated test method of luminous flux depreciation for LED luminaires and lamps. *Reliab. Eng. Syst. Saf.* **2015**, *147*, 84–92. [CrossRef]

- 18. Luo, X.; Wu, B.; Liu, S. Effects of moist environments on LED module reliability. *IEEE Trans. Device Mater. Reliab.* **2010**, *10*, 182–186.

- 19. Chan, S.; Hong, W.; Kim, K.; Yoon, Y.; Han, J.; Jang, J.S. Accelerated life test of high power white light emitting diodes based on package failure mechanisms. *Microelectron. Reliab.* **2011**, *51*, 1806–1809. [CrossRef]

- Huang, J.L.; Golubović, D.S.; Koh, S.; Yang, D.G.; Li, X.P.; Fan, X.J.; Zhang, G.Q. Rapid degradation of mid-power white-light LEDs in saturated moisture conditions. *IEEE Trans. Device Mater. Reliab.* 2015, 15, 478–485. [CrossRef]

- 21. Meneghini, M.; Trevisanello, L.R.; Meneghesso, G.; Zanoni, E. A review on the reliability of GaN-based LEDs. *IEEE Trans. Device Mater. Reliab.* **2008**, *8*, 323–331. [CrossRef]

- Huang, J.L.; Golubović, D.S.; Koh, S.; Yang, D.G.; Li, X.P.; Fan, X.J.; Zhang, G.Q. Degradation mechanisms of mid-power white-light LEDs under high temperature-humidity conditions. *IEEE Trans. Device Mater. Reliab.* 2015, 15, 220–228. [CrossRef]

- 23. Tseng, S.T.; Wen, Z.C. Step-stress accelerated degradation analysis for highly reliable products. *J. Qual. Technol.* **2000**, *32*, 209–216.

- 24. Tseng, S.T.; Balakrishnan, N.; Tsai, C.C. Optimal step-stress accelerated degradation test plan for Gamma process. *IEEE Trans. Reliab.* **2009**, *58*, 611–618. [CrossRef]

- 25. Han, D. Time and cost constrained optimal designs of constant-stress and step-stress accelerated life tests. *Reliab. Eng. Syst. Saf.* **2015**, *140*, 1–14. [CrossRef]

- 26. Hu, C.H.; Lee, M.Y.; Tang, J. Optimum step-stress accelerated degradation test for Wiener degradation process under constraints. *Eur. J. Oper. Res.* 2015, 241, 412–421. [CrossRef]

- 27. Huang, J.; Golubovic, D.S.; Koh, S.; Yang, D.; Li, X.; Fan, X.; Zhang, G.Q. Lumen degradation modeling of white-light LEDs in step stress accelerated degradation test. *Reliab. Eng. Syst. Saf.* **2016**, *154*, 152–159. [CrossRef]

- 28. Cai, M.; Yang, D.; Tian, K.; Zhang, P.; Chen, X.; Liu, L.; Zhang, G. Step-stress accelerated testing of high-power LED lamps based on subsystem isolation method. *Microelectron. Reliab.* **2015**, *55*, 1784–1789. [CrossRef]

- Fan, J.; Yu, C.; Qian, C.; Fan, X.; Zhang, G. Thermal/luminescence characterization and degradation mechanism analysis on phosphor-converted white LED chip scale packages. *Microelectron. Reliab.* 2017, 74, 179–185. [CrossRef]

- 30. Huang, C.H.; Chen, K.J.; Tsai, M.T.; Shih, M.H.; Sun, C.W.; Lee, W.I.; Lin, C.C.; Kuo, H.C. High-efficiency and low assembly-dependent chip-scale package for white light-emitting diodes. *J. Photonics Energy* **2015**, *5*, 057606. [CrossRef]

- 31. Hopkins, T.; Cognetti, C.; Tiziani, R. Designing with thermal impedance. In Proceedings of the IEEE Semiconductor Thermal & Temperature Measurement Symposium, Reprint from "Semi-Thermal Proceedings", San Diego, CA, USA, 10–12 February 1988; pp. 55–61.

- 32. Hu, J.; Yang, L.; Shin, M.W. Mechanism and thermal effect of delamination in light-emitting diode packages. *Microelectron. J.* **2007**, *38*, 157–163. [CrossRef]

- 33. Sorokin, V.M.; Kudryk, Y.Y.; Shynkarenko, V.V.; Kudryk, R.Y.; Sai, P.O. Degradation processes in LED modules. *Semicond. Phys. Quantum Electron. Optoelectron.* **2016**, *19*, 248–254. [CrossRef]

- 34. Xie, R.J.; Li, Y.Q.; Hirosaki, N.; Yamamoto, H. *Nitride Phosphors and Solid-State Lighting*; CRC Press: Boca Raton, FL, USA, 2011.

- 35. CIE TN 001:2014. *Chromaticity Difference Specification for Light Source;* Central Bureau of the CIE: Vienna, Austria, 2014.

- 36. CIE 15:2004. Colorimetry, 3rd ed.; Central Bureau of the CIE: Vienna, Austria, 2004.

- 37. CIE 121:1996. *The Photometry and Goniophotometry of Luminaires;* Central Bureau of the CIE: Vienna, Austria, 1996.

- 38. CIE 127:2007. Measurements of LEDs, 2nd ed.; Central Bureau of the CIE: Vienna, Austria, 2007.

- 39. Fan, J.; Mohamed, M.G.; Qian, C.; Fan, X.; Zhang, G.; Pecht, M. Color shift failure prediction for phosphor-converted white LEDs by modeling features of spectral power distribution with a nonlinear filter approach. *Materials* **2017**, *10*, 819. [CrossRef] [PubMed]

- 40. Lall, P.; Sakalaukus, P.; Wei, J.; Davis, L. SSL and LED life prediction and assessment of CCT shift. In Proceedings of the 14th IEEE ITHERM Conference, Orlando, FL, USA, 27–30 May 2014; pp. 1179–1185.

© 2017 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).