Transparent Thin-Film Transistors Based on Sputtered Electric Double Layer

Abstract

:1. Introduction

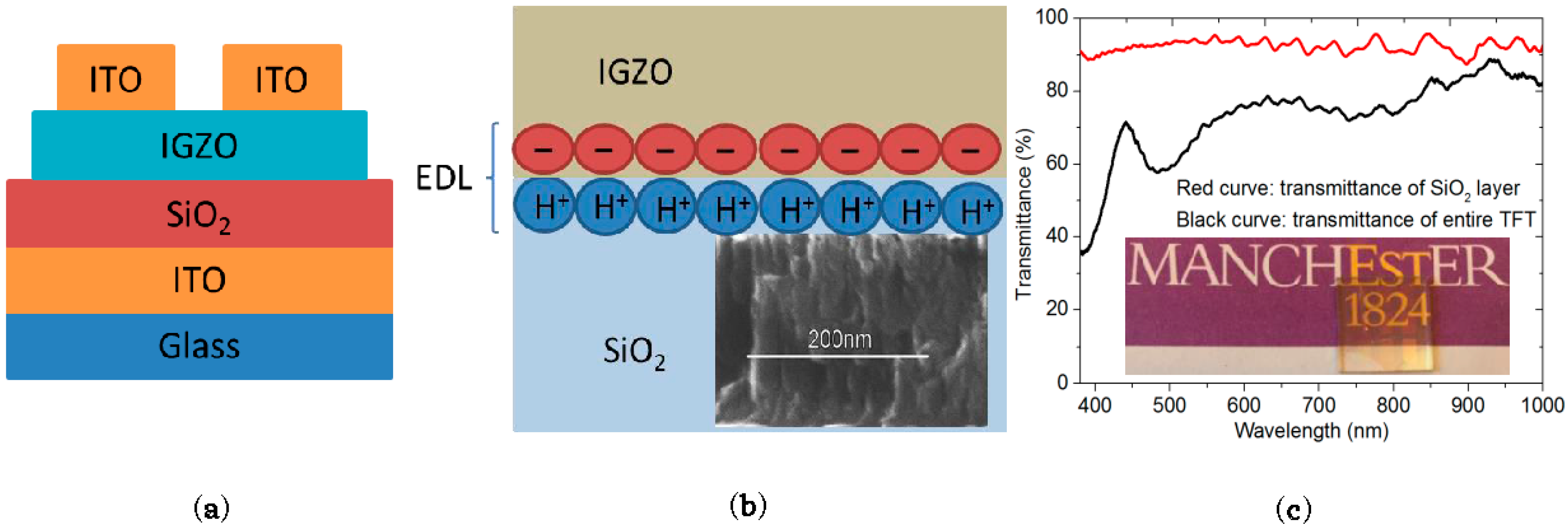

2. Materials and Methods

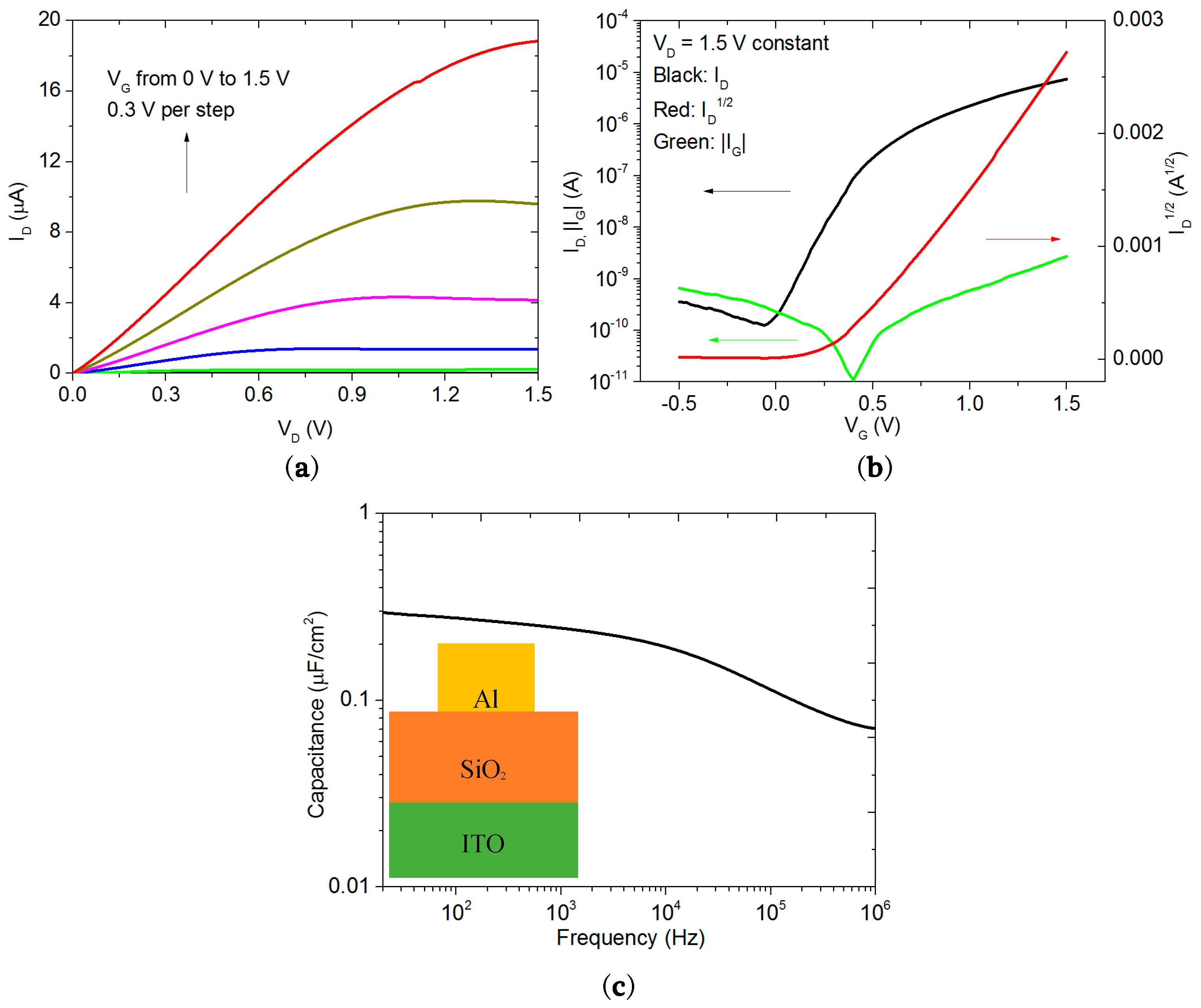

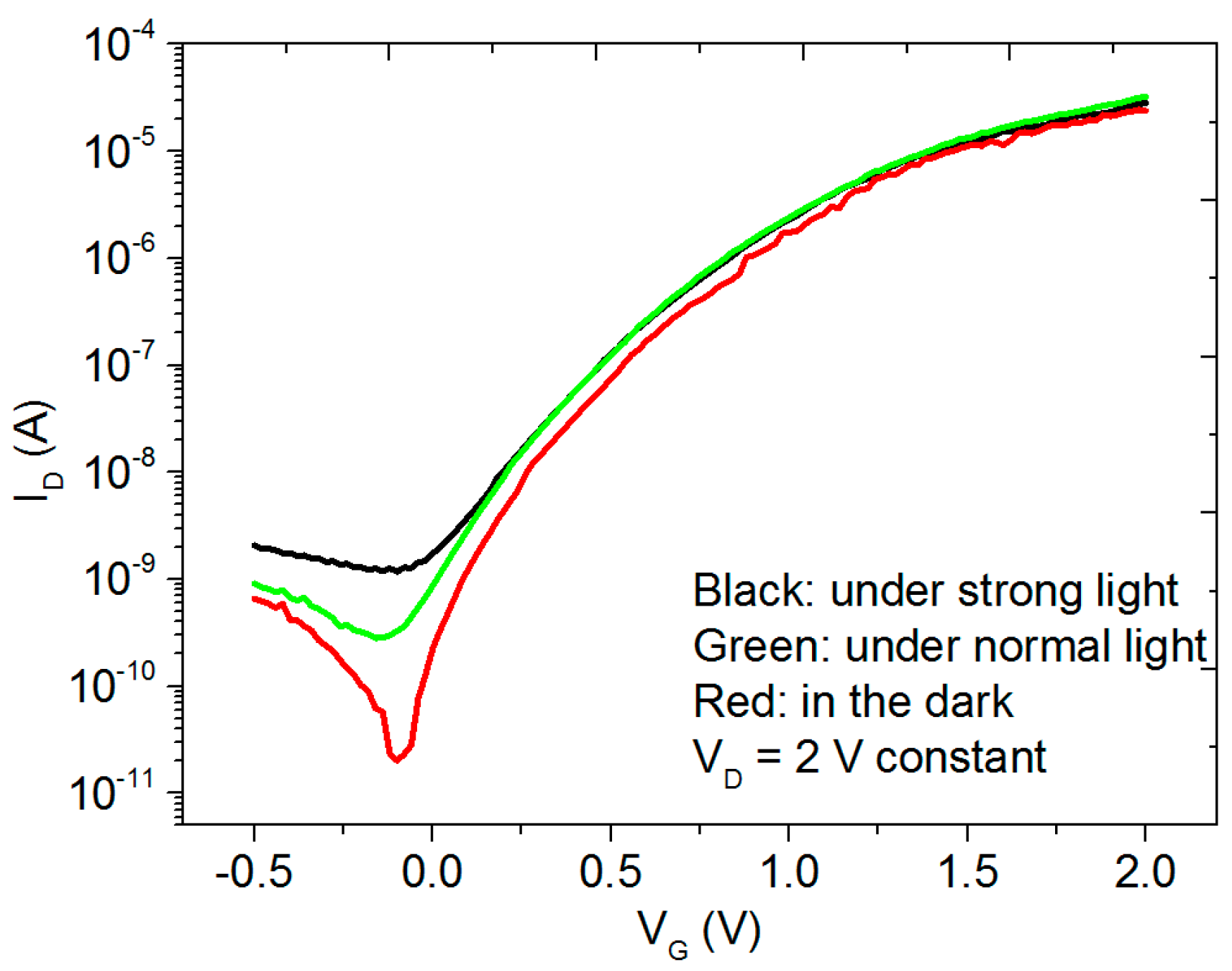

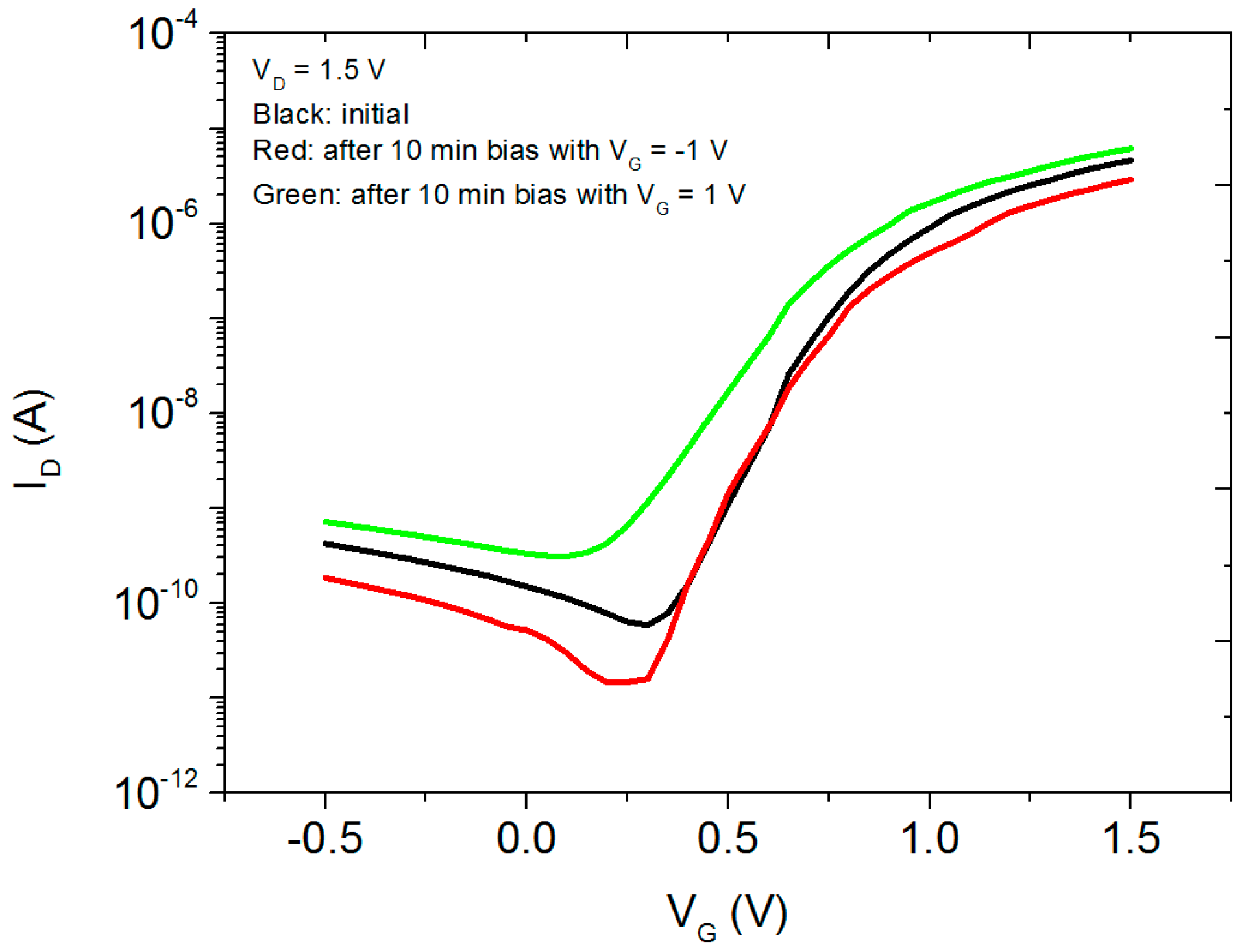

3. Results and Discussion

4. Conclusions

Supplementary Materials

Acknowledgments

Author Contributions

Conflicts of Interest

References

- Fortunato, E.; Correia, N.; Barquinha, P.; Pereira, L.; Gonçalves, G.; Martins, R. High-performance flexible hybrid field-effect transistors based on cellulose fiber paper. IEEE Electron Device Lett. 2008, 29, 988–990. [Google Scholar] [CrossRef]

- Nomura, K.; Ohta, H.; Takagi, A.; Kamiya, T.; Hirano, M.; Hosono, H. Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors. Nature 2004, 432, 488–492. [Google Scholar] [CrossRef] [PubMed]

- Yabuta, H.; Sano, M.; Abe, K.; Aiba, T.; Den, T.; Kumomi, H.; Nomura, K.; Kamiya, T.; Hosono, H. High-mobility thin-film transistor with amorphous InGaZnO4 channel fabricated by room temperature rf-magnetron sputtering. Appl. Phys. Lett. 2006, 89, 2123. [Google Scholar] [CrossRef]

- Hirao, T.; Furuta, M.; Hiramatsu, T.; Matsuda, T.; Li, C.; Furuta, H.; Hokari, H.; Yoshida, M.; Ishii, H.; Kakegawa, M. Bottom-gate Zinc oxide thin-film transistors (ZnO TFTs) for AM-LCDs. IEEE Trans. Electron Devices 2008, 55, 3136–3142. [Google Scholar] [CrossRef]

- Görrn, P.; Sander, M.; Meyer, J.; Kröger, M.; Becker, E.; Johannes, H.H.; Kowalsky, W.; Riedl, T. Towards see-through displays: Fully transparent thin-film transistors driving transparent organic light-emitting diodes. Adv. Mater. 2006, 18, 738–741. [Google Scholar] [CrossRef]

- Roberts, M.E.; Queraltó, N.; Mannsfeld, S.C.; Reinecke, B.N.; Knoll, W.; Bao, Z. Cross-linked polymer gate dielectric films for low-voltage organic transistors. Chem. Mater. 2009, 21, 2292–2299. [Google Scholar] [CrossRef]

- Yoon, M.-H.; Yan, H.; Facchetti, A.; Marks, T.J. Low-voltage organic field-effect transistors and inverters enabled by ultrathin cross-linked polymers as gate dielectrics. J. Am. Chem. Soc. 2005, 127, 10388–10395. [Google Scholar] [CrossRef] [PubMed]

- Collet, J.; Tharaud, O.; Chapoton, A.; Vuillaume, D. Low-voltage, 30 nm channel length, organic transistors with a self-assembled monolayer as gate insulating films. Appl. Phys. Lett. 2000, 76, 1941–1943. [Google Scholar] [CrossRef]

- Zhang, L.; Li, J.; Zhang, X.; Jiang, X.; Zhang, Z. High performance ZnO-thin-film transistor with Ta2O5 dielectrics fabricated at room temperature. Appl. Phys. Lett. 2009, 95, 2112. [Google Scholar] [CrossRef]

- Zhou, C.; Wang, X.; Raju, S.; Lin, Z.; Villaroman, D.; Huang, B.; Chan, H.L.-W.; Chan, M.; Chai, Y. Low voltage and high on/off ratio field-effect transistors based on CVD MoS2 and ultra high-k gate dielectric PZT. Nanoscale 2015, 7, 8695–8700. [Google Scholar] [CrossRef] [PubMed]

- Brox-Nilsen, C.; Jin, J.; Luo, Y.; Bao, P.; Song, A.M. Sputtered ZnO thin-film transistors with carrier mobility over 50 cm2/Vs. IEEE Trans. Electron Devices 2013, 60, 3424–3429. [Google Scholar] [CrossRef]

- Tan, S. Challenges and performance limitations of high-k and oxynitride gate dielectrics for 90/65 nm CMOS technology. Microelectron. J. 2007, 38, 783–786. [Google Scholar] [CrossRef]

- Yuan, H.; Shimotani, H.; Tsukazaki, A.; Ohtomo, A.; Kawasaki, M.; Iwasa, Y. High-density carrier accumulation in ZnO field-effect transistors gated by electric double layers of ionic liquids. Adv. Funct. Mater. 2009, 19, 1046–1053. [Google Scholar] [CrossRef]

- Cho, J.H.; Lee, J.; Xia, Y.; Kim, B.; He, Y.; Renn, M.J.; Lodge, T.P.; Frisbie, C.D. Printable ion-gel gate dielectrics for low-voltage polymer thin-film transistors on plastic. Nat. Mater. 2008, 7, 900–906. [Google Scholar] [CrossRef] [PubMed]

- Dhoot, A.S.; Yuen, J.D.; Heeney, M.; McCulloch, I.; Moses, D.; Heeger, A.J. Beyond the metal-insulator transition in polymer electrolyte gated polymer field-effect transistors. Proc. Natl. Acad. Sci. USA 2006, 103, 11834–11837. [Google Scholar] [CrossRef] [PubMed]

- Pu, J.; Yomogida, Y.; Liu, K.-K.; Li, L.-J.; Iwasa, Y.; Takenobu, T. Highly flexible MoS2 thin-film transistors with ion gel dielectrics. Nano Lett. 2012, 12, 4013–4017. [Google Scholar] [CrossRef] [PubMed]

- Sun, J.; Wan, Q.; Lu, A.; Jiang, J. Low-voltage electric-double-layer paper transistors gated by microporous SiO2 processed at room temperature. Appl. Phys. Lett. 2009, 95, 222108. [Google Scholar] [CrossRef]

- Lu, A.; Sun, J.; Jiang, J.; Wan, Q. Low-voltage transparent electric-double-layer ZnO-based thin-film transistors for portable transparent electronics. Appl. Phys. Lett. 2010, 96, 043114. [Google Scholar] [CrossRef]

- Jiang, J.; Sun, J.; Lu, A.; Wan, Q. Self-assembled ultralow-voltage flexible transparent thin-film transistors gated by-based solid electrolyte. IEEE Trans. Electron Devices 2011, 58, 547–552. [Google Scholar] [CrossRef]

- Zhou, J.; Liu, N.; Zhu, L.; Shi, Y.; Wan, Q. Energy-efficient artificial synapses based on flexible IGZO electric-double-layer transistors. IEEE Electron Device Lett. 2015, 36, 198–200. [Google Scholar] [CrossRef]

- Zhang, H.; Guo, L.; Wan, Q. Nanogranular Al2O3 proton conducting films for low-voltage oxide-based homojunction thin-film transistors. J. Mater. Chem. C 2013, 1, 2781–2786. [Google Scholar] [CrossRef]

- Jiang, J.; Wan, Q.; Sun, J.; Lu, A. Ultralow-voltage transparent electric-double-layer thin-film transistors processed at room-temperature. Appl. Phys. Lett. 2009, 95, 152114. [Google Scholar] [CrossRef]

- Ma, X.; Zhang, J.; Cai, W.; Wang, H.; Wilson, J.; Wang, Q.; Xin, Q.; Song, A. A sputtered silicon oxide electrolyte for high-performance thin-film transistors. Sci. Rep. 2017, 7, 809. [Google Scholar] [CrossRef] [PubMed]

- Chiu, C.; Yu, P.; Chang, C.; Yang, C.; Hsu, M.; Kuo, H.; Tsai, M. Oblique electron-beam evaporation of distinctive indium-tin-oxide nanorods for enhanced light extraction from InGaN/GaN light emitting diodes. Opt. Express 2009, 17, 21250–21256. [Google Scholar] [CrossRef] [PubMed]

- Caffrey, D.; Norton, E.; Coileáin, C.Ó.; Smith, C.M.; Bulfin, B.; Farrell, L.; Shvets, I.V.; Fleischer, K. Decoupling the refractive index from the electrical properties of transparent conducting oxides via periodic superlattices. Sci. Rep. 2016, 6. [Google Scholar] [CrossRef] [PubMed]

- Benzitouni, S.; Zaabat, M.; Khial, A.; Rechem, D.; Benaboud, A.; Bouras, D.; Mahdjoub, A.; Toubane, M.; Coste, R. High sensitivity of porous Cu-doped SnO2 thin films to methanol. Adv. Nanopart. 2016, 5, 140. [Google Scholar] [CrossRef]

- Inguva, S.; Vijayaraghavan, R.K.; McGlynn, E.; Mosnier, J.-P. Highly transparent and reproducible nanocrystalline ZnO and AZO thin films grown by room temperature pulsed-laser deposition on flexible Zeonor plastic substrates. Mater. Res. Express 2015, 2, 096401. [Google Scholar] [CrossRef]

- Zhang, B.; Li, H.; Zhang, X.; Luo, Y.; Wang, Q.; Song, A. Performance regeneration of InGaZnO transistors with ultra-thin channels. Appl. Phys. Lett. 2015, 106, 093506. [Google Scholar] [CrossRef]

- Guo, L.-Q.; Yang, Y.-Y.; Zhu, L.-Q.; Wu, G.-D.; Zhou, J.-M.; Zhang, H.-L. Effects of humidity on performance of electric-double-layer oxide-based thin-film transistors gated by nanogranular SiO2 solid electrolyte. AIP Adv. 2013, 3, 072110. [Google Scholar] [CrossRef]

- Liu, H.; Sun, J.; Tang, Q.; Wan, Q. Ultralow-voltage electric double-layer SnO2 nanowire transistors gated by microporous SiO2-based solid electrolyte. J. Phys. Chem. C 2010, 114, 12316–12319. [Google Scholar] [CrossRef]

- Godet, J.; Pasquarello, A. Proton diffusion mechanism in amorphous SiO2. Phys. Rev. Lett. 2006, 97, 155901. [Google Scholar] [CrossRef] [PubMed]

- Ono, S.; Seki, S.; Hirahara, R.; Tominari, Y.; Takeya, J. High-mobility, low-power, and fast-switching organic field-effect transistors with ionic liquids. Appl. Phys. Lett. 2008, 92, 103313. [Google Scholar] [CrossRef]

- Nomura, K.; Kamiya, T.; Hosono, H. Interface and bulk effects for bias—light-illumination instability in amorphous-In-Ga–Zn–O thin-film transistors. J. Soc. Inf. Disp. 2010, 18, 789–795. [Google Scholar] [CrossRef]

- Kikuchi, Y.; Nomura, K.; Yanagi, H.; Kamiya, T.; Hirano, M.; Hosono, H. Device characteristics improvement of a-In-Ga–Zn–O TFTs by low-temperature annealing. Thin Solid Films 2010, 518, 3017–3021. [Google Scholar] [CrossRef]

- Fuh, C.-S.; Sze, S.M.; Liu, P.-T.; Teng, L.-F.; Chou, Y.-T. Role of environmental and annealing conditions on the passivation-free In-Ga–Zn–O TFT. Thin Solid Films 2011, 520, 1489–1494. [Google Scholar] [CrossRef]

- Görrn, P.; Lehnhardt, M.; Riedl, T.; Kowalsky, W. The influence of visible light on transparent Zinc Tin Oxide thin film transistors. Appl. Phys. Lett. 2007, 91, 3504. [Google Scholar] [CrossRef]

- Kang, D.; Lim, H.; Kim, C.; Song, I.; Park, J.; Park, Y.; Chung, J. Amorphous Gallium Indium Zinc Oxide thin film transistors: Sensitive to oxygen molecules. Appl. Phys. Lett. 2007, 90, 192101. [Google Scholar] [CrossRef]

- Chen, T.-C.; Chang, T.-C.; Hsieh, T.-Y.; Tsai, C.-T.; Chen, S.-C.; Lin, C.-S.; Hung, M.-C.; Tu, C.-H.; Chang, J.-J.; Chen, P.-L. Light-induced instability of an InGaZnO thin film transistor with and without SiOx passivation layer formed by plasma-enhanced-chemical-vapor-deposition. Appl. Phys. Lett. 2010, 97, 192103. [Google Scholar] [CrossRef]

- Guo, L.; Huang, Y.; Shi, Y.; Cheng, G.; Ding, J. Indium-Zinc-Oxide electric-double-layer thin-film transistors gated by silane coupling agents 3-triethoxysilylpropylamine–graphene oxide solid electrolyte. J. Phys. D Appl. Phys. 2015, 48, 285103. [Google Scholar] [CrossRef]

- Jiang, J.; Wan, Q.; Zhang, Q. Transparent junctionless electric-double-layer transistors gated by a reinforced chitosan-based biopolymer electrolyte. IEEE Trans. Electron Devices 2013, 60, 1951–1957. [Google Scholar] [CrossRef]

- Huang, S.-Y.; Chang, T.-C.; Chen, M.-C.; Chen, S.-C.; Tsai, C.-T.; Hung, M.-C.; Tu, C.-H.; Chen, C.-H.; Chang, J.-J.; Liau, W.-L. Effects of ambient atmosphere on electrical characteristics of Al2O3 passivated InGaZnO thin film transistors during positive-bias-temperature-stress operation. Electrochem. Solid-State Lett. 2011, 14, H177–H179. [Google Scholar] [CrossRef]

© 2017 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Cai, W.; Ma, X.; Zhang, J.; Song, A. Transparent Thin-Film Transistors Based on Sputtered Electric Double Layer. Materials 2017, 10, 429. https://doi.org/10.3390/ma10040429

Cai W, Ma X, Zhang J, Song A. Transparent Thin-Film Transistors Based on Sputtered Electric Double Layer. Materials. 2017; 10(4):429. https://doi.org/10.3390/ma10040429

Chicago/Turabian StyleCai, Wensi, Xiaochen Ma, Jiawei Zhang, and Aimin Song. 2017. "Transparent Thin-Film Transistors Based on Sputtered Electric Double Layer" Materials 10, no. 4: 429. https://doi.org/10.3390/ma10040429