## SUPPORTING INFORMATION

2 **for**

## "Rapid Processing of Wafer-scale Anti-Reflecting 3D Hierarchical Structures on Silicon and its Templation"

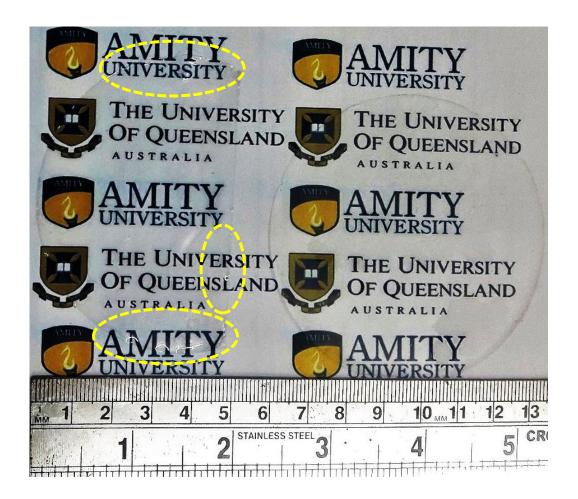

- Harsimran Singh Bindra <sup>1,†</sup>, Jaikrishna <sup>1,†</sup> Tushar Kumeria <sup>2,\*</sup> and Ranu Nayak <sup>1,\*</sup>

- <sup>1</sup> Amity Institute of Nanotechnology, Amity University Uttar Pradesh, Noida, UP, INDIA

- <sup>2</sup> School of Pharmacy, The University of Queensland, Queensland 4102, Australia

- † Authors have equal contribution

- \* Correspondence: rnayak@amity.edu; ranunayakbose@gmail.com

- \* Correspondence: t.kumeria@uq.edu.au

11 12

10

1

3

4

5

6

7

8 9

131415

**Figure S1:** The Digital image comparisition of the plain PDMS (left) and the partterned PDMS (right).

17 18

16

© 2016 by the authors; licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons by Attribution (CC-BY) license (http://creativecommons.org/licenses/by/4.0/).