Article

# 4H-SiC MOSFET Threshold Voltage Instability Evaluated via Pulsed High-Temperature Reverse Bias and Negative Gate Bias Stresses

Laura Anoldo <sup>1,\*</sup>, Edoardo Zanetti <sup>1</sup>, Walter Coco <sup>1</sup>, Alfio Russo <sup>1</sup>, Patrick Fiorenza <sup>2,\*</sup> and Fabrizio Roccaforte <sup>2</sup>

- <sup>1</sup> STMicroelectronics, Stradale Primosole, 50, 95125 Catania, Italy

- Consiglio Nazionale delle Ricerche-Istituto per la Microelettronica e Microsistemi (CNR-IMM), Strada VIII 5, 95121 Catania, Italy

- \* Correspondence: laura.anoldo@st.com (L.A.); patrick.fiorenza@cnr.it (P.F.)

Abstract: This paper presents a reliability study of a conventional 650 V SiC planar MOSFET subjected to pulsed HTRB (High-Temperature Reverse Bias) stress and negative HTGB (High-Temperature Gate Bias) stress defined by a TCAD static simulation showing the electric field distribution across the SiC/SiO<sub>2</sub> interface. The instability of several electrical parameters was monitored and their drift analyses were investigated. Moreover, the shift of the onset of the Fowler–Nordheim gate injection current under stress conditions provided a reliable method to quantify the trapped charge inside the gate oxide bulk, and it allowed us to determine the real stress conditions. Moreover, it has been demonstrated from the cross-correlation, the TCAD simulation, and the experimental  $\Delta V_{th}$  and  $\Delta V_{FN}$  variation in both  $\Delta V_{th}$  and  $\Delta V_{FN}$ , while HTRB showed only a 4% variation in both  $\Delta V_{th}$  and  $\Delta V_{FN}$ . The physical explanation was attributed to the accelerated degradation of the gate insulator in proximity to the source region under HTGB configuration.

Keywords: pMOSFET; 4H-SiC; HTGB; HTRB; pulsed stress; threshold voltage instability

Citation: Anoldo, L.; Zanetti, E.; Coco, W.; Russo, A.; Fiorenza, P.; Roccaforte, F. 4H-SiC MOSFET Threshold Voltage Instability Evaluated via Pulsed High-Temperature Reverse Bias and Negative Gate Bias Stresses. *Materials* 2024, 17, 1908. https://doi.org/10.3390/ma17081908

Academic Editor: Abderrahim Yassar

Received: 22 March 2024 Revised: 11 April 2024 Accepted: 17 April 2024 Published: 20 April 2024

Copyright: © 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

# 1. Introduction

Due to its superior physical properties compared to silicon (Si), such as a wide bandgap of about 3.2 eV, a critical electric field, and high thermal conductivity, Silicon carbide (4H-SiC), which is a wide-band gap (WBG) semiconductor material, is becoming the emerging candidate for automotive applications, making power transistors with a high power density module featuring high blocking voltage and ultra-low conduction resistance [1–5]. In this context, High-Temperature Reverse Bias (HTRB) and High-Temperature Gate Bias (HTGB) are routinely performed product qualification tests for PowerMOSFET manufacturing [6-14]. In particular, the HTGB test is designed to electrically stress the gate insulator by applying a DC bias voltage at a high temperature, detecting any drift in electrical parameters caused by a significant number of charge traps at and near the SiC/SiO<sub>2</sub> interface, and bulk oxide traps generated as the oxide has been deposed. The HTRB test aims to monitor the drain terminal leakage current of the devices under High-Temperature Reverse Bias conditions over a period of time. HTRB combines electrical and thermal stress; this test can be used to check junction integrity, crystal defects, and ionic-contamination level, which can reveal device weaknesses or degradation effects in the field depletion structures at device edge termination and in surface passivation. The aim of this work is to compare the effects of the, namely, similar—in terms of the electric field across the insulator layer—negative gate bias stress (HTGB) and drain bias stress (HTRB) on PowerMOSFET, respectively. In this context, TCAD simulations were used to select the experimental conditions to obtain a fair comparison of the two methods. In fact, a comparison of the results obtained on Power-MOSFET aging under both HTRB and HTGB, leading to a different drift or degradation

Materials **2024**, 17, 1908 2 of 12

of the threshold voltage ( $V_{th}$ ) and to the onset of the Fowler–Nordheim gate conduction ( $V_{FN}$ ), can be fundamental to refine the electrical characterization protocols for device manufacturers [15–21]. This comparison is of fundamental relevance for device manufacturing and to define the route to "zero-failure" of the field of device under its "mission-profile".

### 2. Materials and Methods

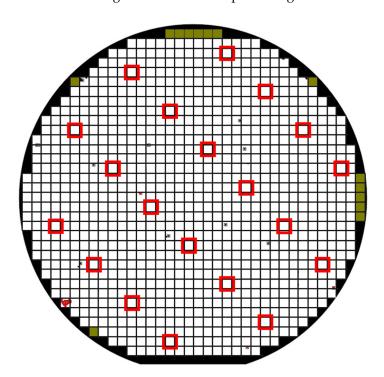

Several 4H-SiC wafers containing vertical PowerMOSFET transistors were investigated in this work. MOSFETs are fabricated on 150 mm wafers on an n-type (0001) 4H-SiC 180 µm thick substrate with a nitrogen-doping concentration of  $4-5 \times 10^{18}$  cm<sup>-3</sup> and resistivity of  $0.012-0.025 \Omega \cdot cm$ . The n-type drift epitaxial layer is 12 µm thick with a nitrogen-doping concentration of  $8 \times 10^{15}$  cm<sup>-3</sup> and is grown by chemical vapor deposition (CVD) in a warm wall multi-wafer reactor. The gate insulation layer is a 50 nm thick deposited oxide layer through a Low-Pressure Chemical Vapor Deposition (LPCVD) process followed by a state-of-the-art NO-based post-oxide deposition annealing [22]. The semiconductor materials were characterized at the beginning of the device fabrication process using microscopic techniques in order to select those devices without any visible epitaxial defect that may affect the device's reliability [12,23]. Firstly, the optical inspection at the surface of the epitaxial layer is carried out with Candela 8520 using a KLA-Tencor equipment scan which allows us to detect surface defects such as droplets, carrots, triangles, micro-pits, etc. Another optical inspection is performed, using a KLA Altair inspection microscope, after the first photo-lithography step, which defines the pitch of the device, that is, the width, distance, and PowerMOSFET edges. Then, an accurate selection of good devices normally intended for sale is carried out, superimposing defectivity maps, shown in Figure 1, and EWS (Electrical Wafer Sorting). In particular, the EWS is used to select devices distributed on the whole wafer surface, as schematically described in Figure 1 by red squares avoiding "dotted" devices spotted as defect-containing devices by optical inspection performed before and during device fabrication processing.

**Figure 1.** Defectivity maps at epitaxial inspection level. Red: The tested devices that are defect-free and good in the final test.

Materials **2024**, 17, 1908 3 of 12

## 3. Device and Stress Procedure Description

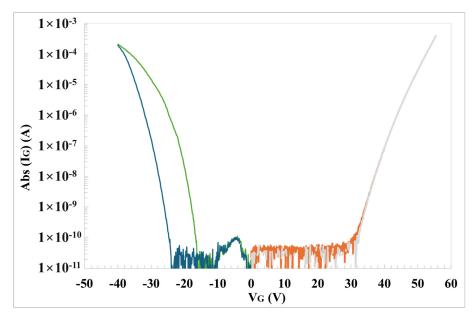

A preliminary electrical characterization of the gate oxide and the channel leakage current under reverse gate bias was performed, and it aimed to obtain the onset of the Fowler-Nordheim (FN) tunneling conduction and to define input elements for the TCAD numerical simulation. This iteration is used to define the stress conditions to keep the "real oxide electric field" and the insulator similar, as much as possible, in both HTGB and HTRB conditions. In fact, FN tunneling current it is used to univocally estimate the oxide electric field, the effective thickness and the active semiconductor doping concentration [24–26]. Furthermore, both HTGB and HTRB conditions induce different electric field distributions across the MOSFET structure and they can be complementary used to understand which are the more robust and weak components of the elementary cell. In fact, as has been demonstrated previously by Fiorenza et al. [27], Fowler-Nordheim gate conduction can be used as reliable feedback on the control of the oxide electric field. In particular, Figure 2 shows the gate current characteristics (I<sub>G</sub>-V<sub>G</sub>) repeated several times, both on the positive and negative polarization region, and used to define the steady onset of the Fowler-Nordheim (FN) injection current and to determine gate current onset and effective oxide thickness [19,25,28]. Figure 2 shows the I<sub>G</sub>-V<sub>G</sub> sweeps collected twice consecutively, both on positive and negative polarizations. It can be noticed that in the negative branch of the  $I_G$ - $V_G$  (Figure 2), the two consecutive curves do not overlap after repeated negative bias sweeps. This has been demonstrated previously [24] as a manifestation of transient trapping phenomena occurring at the SiO<sub>2</sub>/4H-SiC gate system, resulting in an uncontrolled transient oxide field variation. These measurements are fundamental for giving feedback to the TCAD simulation to set the stress conditions in a well-known oxide field regime.

**Figure 2.**  $I_G$ - $V_G$  characteristics of a 500 Å gate oxide on 650 V SiC PowerMOSFET under two consecutive positive (orange and grey) and negative (green and blue) bias sweeps at 200 °C.

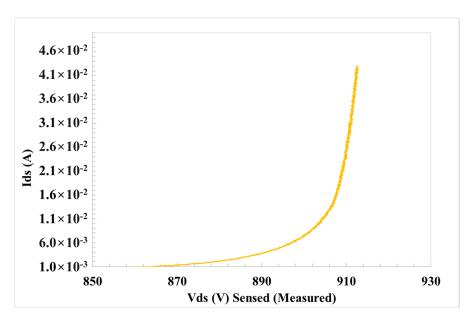

On the other hand, Figure 3 shows the  $I_{DS}$ - $V_{DS}$  characteristics used to determine the operation avalanche breakdown voltage (BV $_{DSs}$ ) of the device, the semiconductor parameters and to tune the HTRB stress conditions. The occurrence of the avalanche breakdown at a given BV $_{DSs}$  value is fundamental in order to give feedback to the TCAD simulation to set the stress conditions in a well-known semiconductor field regime.

Materials **2024**, 17, 1908 4 of 12

**Figure 3.** I<sub>D</sub>-V<sub>D</sub> characteristics under off conditions on a 650 V SiC PowerMOSFET at 200 °C.

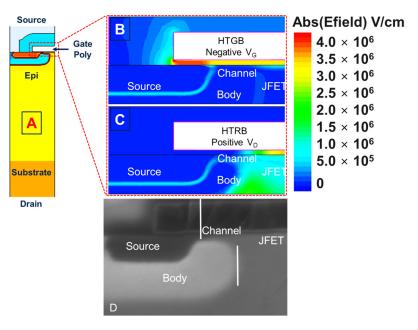

As mentioned in the introduction, the electrical characterization, provided in Figures 2 and 3, was used to understand the experimental conditions in the negative polarization of the gate, such as negative gate bias stress (HTGB) and drain bias stress (HTRB), respectively. TCAD simulations were used to fine-tune the values of  $V_G$  and  $V_{DS}$  in order to obtain similar electric fields in the gate oxide (Figure 4). The schematic of the half-cell structure of SiC Planar MOSFET used in the numerical simulation is presented in Figure 4A. In particular, the static 2D TCAD physical simulations of the gate oxide electric field (E) distribution near the SiC-SiO2 interface, under negative HTGB and HTRB conditions, of the 4H-SiC power MOSFET are also shown in Figures 4B and 4C, respectively. Finally, Figure 4D shows the scanning electron microscopy (SEM) performed on the MOSFET elementary cell structure. As can be seen, all the device components (source, body, JFET, etc.) are clearly distinguishable.

**Figure 4.** The half-cell structure of PowerMOSFET (**A**). Simulation of the gate oxide field under negative HTGB (**B**) and under HTRB (**C**) conditions. Scanning electron microscopy cross-section image of the MOSFET cell (**D**).

Materials **2024**, 17, 1908 5 of 12

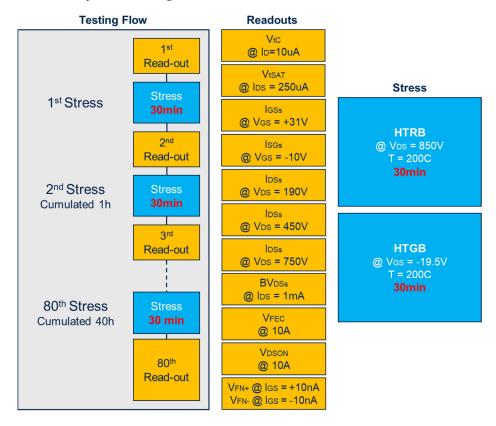

A simulation related to HTRB configuration, under the BV<sub>DSs</sub> condition and limited to  $I_{DSS} = 1$  mA, shows an oxide field maximum value in the JFET region (Figure 4C). On the other hand, the simulation under negative HTGB (Figure 4B), at an equivalent gate oxide field, shows a larger oxide field in the source region compared to the JFET. Hence, although the absolute value of the electric field induced on the gate oxide is the same, under negative HTGB, the field lines at the source/body interface are much higher than in the drift region due to the mismatch in the dielectric constant of the oxide and the semiconductor. Opposite behavior is seen in the case of the HTRB test, where the maximum electric field occurs in the drift region and is practically zero in the source/body region. In this context, it is mandatory to understand the device physics involved in both HTRB and HTGB configurations in order to clarify which particular phenomenon is involved in the different parts of the device degradation. In this scenario, it is fundamental to focus on the impact of these two different stress conditions (having a similar gate oxide field conditions), paying particular attention to the drift of key parameters, represented in Figure 5: the gate and drain terminals' leakage currents ( $I_{GSs}$  and  $I_{DSs}$ ); the gate oxide conduction ( $V_{FN+}$  and  $V_{FN-}$  namely the Fowler-Nordheim voltage onset by electrons and hole currents coming from the semiconductor); the drain-source breakdown voltage ( $BV_{DSs}$ ); the transistor threshold ( $V_{th}$ ); the threshold with source and drain grounded ( $V_{tSAT}$ ); threshold voltage at 10  $\mu$ A ( $V_{tC}$ ); the  $V_{DSs}$  voltage under conduction (ON-state) condition (V<sub>DSON</sub>); and the body-drain diode forward bias (V<sub>FEC</sub>). The testing protocol is performed using the Keysight Easy Expert platform, as schematically shown in Figure 5.

Figure 5. Stress cycling procedure.

The characterization flow—schematically depicted in Figure 5—consists of a sequence of stresses and read-outs, i.e., up to 40 h of cumulative stress which equates to 80 stress/read-outs. In each readout, the characteristic parameters of the MOSFET are measured; after the stresses sequence, either HTGB or HTRB are measured. Furthermore, the readout sequence is chosen from the mild perturbation to the more severe perturbation condition.

The investigation on the drift of the mentioned electrical parameters aims to understand which are the most sensitive parameters to drift under stress conditions. In order to

Materials **2024**, 17, 1908 6 of 12

induce significant drift in the selected parameters during stress, the measure/stress cycling routine allows us to control the Keysight B1505 device analyzer (Keysight, Santa Rosa, CA, USA) and the HV MPI-TS2000DP semiautomatic probe-station (MPI Corporation, Zhubei City, Taiwan) to perform wafer level measurements at a temperature of 200 °C. To take advantage of the simulation shown in Figure 4, and to accelerate device degradation, a higher  $V_{DSs}$  condition than  $BV_{DSs}$  (i.e.  $V_{DSs} = 890 \text{ V/I}_{DSs} \sim 2 \text{ mA}$ ) for HTRB stress has been chosen, beside an equivalent V<sub>GSs</sub> stress condition, in terms of a gate oxide field for negative HTBG at  $V_{GSs} = -19.5$  V. The purpose is to put the transistor under an avalanche condition in order to accelerate the stress effects within 40 h. This particular high-voltage/high-current stress-sensing configuration needed an unconventional experimental setup that is worth describing. The enhancement of the power capability until a voltage of ~960 V and leakage current of ~33 mA are reached under pulsed mode [29] is allowed by a Keysight N1266 HVSMU current expander, with interconnection of the so-called Keysight SMU as the MC (Medium Current) and MP (Medium Power) of the B1505. Moreover, in order to switch from a high-voltage to a high-current test, a N1258A Module selector is implemented, as shown in the complete schematic of the connections in Figure 6.

Figure 6. Test setup and system configuration schematic.

On the other hand, pulsed HTGB and HTRB stress occur close to the operative condition of the real application of the PowerMOSFET subjected to on/off hard switching. Hence, pulsed stress characterization was achieved by placing an oscilloscope with an

Materials **2024**, 17, 1908 7 of 12

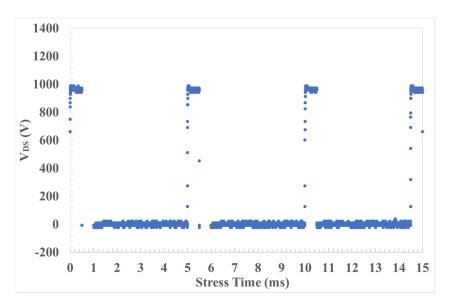

HV probe in series with the output of the resources. Although the N1266 module allows us to impose a maximum impulse of 1 ms, the resistance of the wiring system, and the consequent misalignment measured between forced voltage and applied voltage, led us to reduce the impulse to  $500~\mu s$ . Thus, each stress cycle consisted of 1000~pulses with a 5~ms period, repeated 360~times for a total stress time of 1800~s, as shown in Figure 7.

Figure 7. V<sub>D</sub> stress pulse characterization.

## 4. Data/Results and Discussion

To simplify the graphical representation of drifting parameters under HTRB and HTGB stress, a limited selection of devices under testing has been reported in the figures related to the test. The experimental results have been confirmed on samples collected on different wafers belonging to different production lots. Some representative devices are reported in the following tables labeled as the Dev number belonging to their wafer (Wf) number.

# 4.1. HTRB Test

A preliminary characterization of the devices was performed before the HTRB test by taking into account the different parameters, shown in Figure 5 in orange boxes. Table 1 shows only the parameters, which, after stress, exhibit the most significant drift. It has to be emphasized that  $V_{th}$  and  $V_{FN}$  (hole injections from p-body) are affected by the stress. The drift of the other electrical parameters is quite negligible.

**Table 1.** Channel- and gate oxide-related parameters before HTRB test and their corresponding drift (I(t)/I(0)) after 40 h of HTRB stress.

|           | $V_{th}$ (V)<br>@ $I_{DS} = 5 \mu A$<br>$V_{DS} = 0.1 V$ | $V_{FN+}$ (V)<br>@ $I_{GS} = +10$<br>nA | $V_{FN}$ (V) @ $I_{GS} = -10$ nA | $BV_{DSS} (V)$ @ $I_{DS} = 1 \text{ mA}$ G & S Grounded |                                             |

|-----------|----------------------------------------------------------|-----------------------------------------|----------------------------------|---------------------------------------------------------|---------------------------------------------|

| DEV33-WF1 | 0.523                                                    | 33.42                                   | -17.30                           | 879.11                                                  | Parametric<br>data<br>Before<br>HTRB stress |

| DEV36-WF1 | 0.510                                                    | 33.58                                   | -17.78                           | 881.43                                                  |                                             |

| DEV19-WF2 | 0.814                                                    | 36.00                                   | -18.59                           | 853.08                                                  |                                             |

| DEV20-WF2 | 0.842                                                    | 35.82                                   | -18.14                           | 853.34                                                  |                                             |

| DEV33-WF1 | 0.989                                                    | 1.01                                    | 1.07                             | 1.00                                                    | ———                                         |

| DEV36-WF1 | 0.950                                                    | 1.01                                    | 1.05                             | 1.00                                                    | Drift<br>analysis<br>After<br>TRB stress    |

| DEV19-WF2 | 1.014                                                    | 1.01                                    | 1.06                             | 1.00                                                    |                                             |

| DEV20-WF2 | 1.010                                                    | 1.01                                    | 1.07                             | 1.00                                                    |                                             |

Materials **2024**, 17, 1908 8 of 12

## 4.2. HTGB Test

The same preliminary characterization was performed in HTGB stress conditions and the most significant results are, respectively, shown in Table 2 for the first read-out and for drift analysis.

| Table 2. Channel- and gate oxide-related parameters before HTRB test and their corresponding drift |

|----------------------------------------------------------------------------------------------------|

| (I(t)/I(0)) after 40 h HTGB stress.                                                                |

|           | $V_{th}$ (V)<br>@ $I_{DS} = 5 \mu A$<br>$V_{DS} = 0.1 V$ | V <sub>FN+</sub> (V)<br>@ I <sub>GS</sub> = +10<br>nA | $V_{FN}$ (V) @ $I_{GS} = -10$ nA | $BV_{DSS} (V)$ @ $I_{DS} = 1 \text{ mA}$ G & S Grounded |                                             |

|-----------|----------------------------------------------------------|-------------------------------------------------------|----------------------------------|---------------------------------------------------------|---------------------------------------------|

| DEV34–WF1 | 0.45                                                     | 33.68                                                 | -17.59                           | 879.82                                                  | H P                                         |

| DEV37-WF1 | 0.51                                                     | 32.98                                                 | -17.38                           | 878.16                                                  | aran<br>da<br>Befo<br>IGB                   |

| DEV21-WF2 | 0.89                                                     | 36.21                                                 | -18.41                           | 840.66                                                  | Parametric<br>data<br>Before<br>ITGB stress |

| DEV22-WF2 | 0.82                                                     | 35.46                                                 | -18.55                           | 844.32                                                  |                                             |

| DEV34–WF1 | 0.96                                                     | 1.01                                                  | 1.16                             | 1.01                                                    | H                                           |

| DEV37-WF1 | 0.91                                                     | 1.01                                                  | 1.15                             | 1.01                                                    | Dr<br>anal<br>Af<br>IGB                     |

| DEV21-WF2 | 0.99                                                     | 1.01                                                  | 1.11                             | 1.01                                                    | Drift<br>analysis<br>After<br>IGB stress    |

| DEV22-WF2 | 1.00                                                     | 1.01                                                  | 1.10                             | 1.01                                                    |                                             |

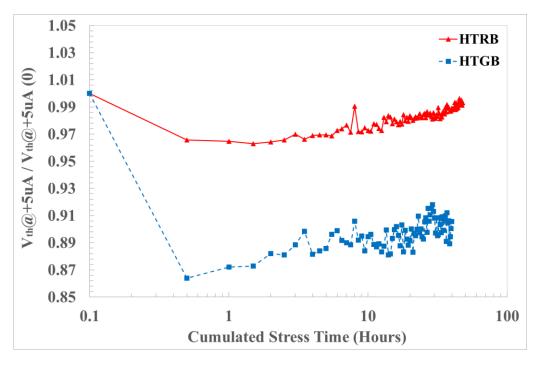

At the end of the characterization protocol, a data comparison of the drift analysis of HTRB-stressed devices and negative equivalent bias under HTGB stress was carried out on  $V_{th}$  (Figure 8). The decreasing  $V_{th}$  on the blue sample (stressed under HTGB conditions) is higher than that on the red ones (stressed under HTRB conditions). This is usually related to negative charge emission or hole trapping in the gate oxide. It can be noticed that the HTRB caused a variation in the threshold voltage of  $\Delta V_{th} < 4\%$  from the initial value. On the other hand, the HTGB caused a large variation (with respect of the HTRB) in the threshold voltage of  $\Delta V_{th} < 15\%$  from the initial value.

Figure 8. Threshold voltage drift under HTRB at 890 V (red) and HTGB at -19.5 V (blue) stress.

Materials **2024**, 17, 1908 9 of 12

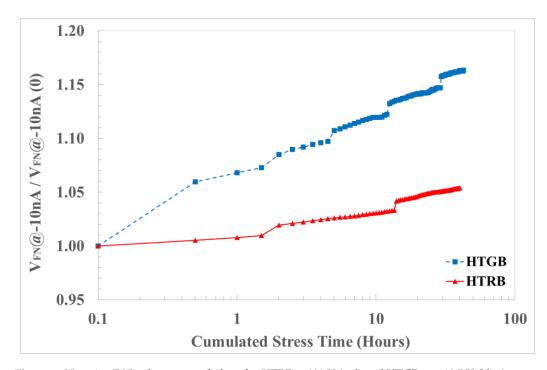

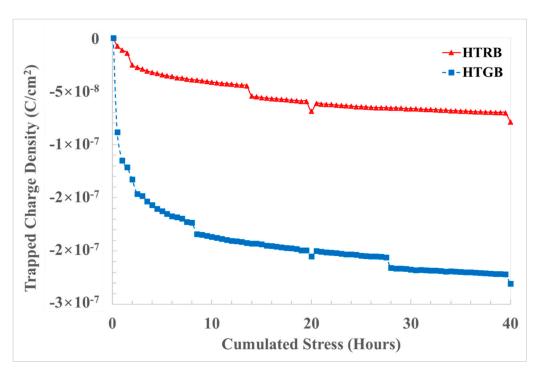

To confirm these results, and to emphasize the contribution of the charge trapped inside the gate oxide bulk, the  $V_{FN}$  drift under positive and negative bias has been put under analysis. The most significant drift, reported in Figure 9, is related to  $V_{FN}$ -, which is mainly affected by hole injection from the body and electrons from poly. Comparing the results with HTRB equivalent stress, the result is more evident than for  $V_{th}$  drift and the  $V_{FN}$ - shift is higher on the HTGB-stressed samples.

Figure 9. Negative F-N voltage onset drift under HTRB at 890 V (red) and HTGB at −19.5 V (blue) stress.

It can be noticed that the HTRB produced a variation in the onset voltage of the Fowler–Nordheim conduction of  $\Delta V_{FN}$  < 4% from the initial value. On the other hand, the HTGB produced a large variation (with respect of the HTRB) in the threshold voltage  $\Delta V_{FN}$  of < 15% from the initial value.

This experimental evidence can been understood by looking at the TCAD simulation in Figure 4B,C. In fact, in HTGB (Figure 4B) in the source region, the electric field is larger than that in the field in the JFET region; meanwhile, in HTRB (Figure 4C) in the source region, the electric field is a small fraction of that in the JFET region. Hence, different device degradation can be attributed to the different charge trapping occurring in the gate oxide in the proximity of the source region.

Finally, we calculated and quantified, by the charge-sensing method [30], the averaged trapped charge density inside the gate oxide. This confirmed the hypothesis of the worst-case effect on gate oxide degradation being that of negative bias gate stress as opposed to HTRB stress, even if the simulated gate field is the same (Figure 10). Negative bias stress causes a negative shift in  $V_{th}$ , which might be explained by the filling and emptying of near-interfacial oxide traps in the presence of a gate bias stress [31].

Materials **2024**, 17, 1908 10 of 12

Figure 10. Oxide trapped charge density under HTRB (red) and HTGB (blue) stress.

### 5. Conclusions

In the field of device reliability, it is fundamental to evaluate which is the experimental procedure that represents the best trade-off between real-world application conditions and an accelerated characterization test to qualify material processing for device fabrication. Therefore, in this paper, a comparison of pulsed HTGB and HTRB stress has been carried out on defect-free 4H-SiC PowerMOSFETs at EWS in order to identify the most sensitive electrical test parameter under different stress conditions. From a wide number of analyzed electrical parameters,  $V_{th}$  and  $V_{FN-}$  showed higher instability and degradation compared to the others. Moreover, it has been demonstrated from the cross-correlation, the TCAD simulation and the experimental  $\Delta V_{th}$  and  $\Delta V_{FN-}$  variation that HTGB stress is more severe compared to HTRB stress. In fact, HTGB showed a 15% variation in both  $\Delta V_{th}$  and  $\Delta V_{FN-}$ ; meanwhile, HTRB showed only a 4% variation in both  $\Delta V_{th}$  and  $\Delta V_{FN-}$  after an accumulated stress of 40 h. The physical explanation was attributed to the accelerated degradation of the gate insulator in the proximity of the source region under HTGB configuration.

**Author Contributions:** Conceptualization, L.A.; Methodology, W.C. and P.F.; Software, E.Z.; Investigation, L.A., E.Z., W.C. and P.F.; Data curation, P.F.; Writing—original draft, L.A.; Writing—review & editing, P.F.; Visualization, F.R.; Supervision, A.R. and F.R.; Project administration, F.R.; Funding acquisition, A.R. and P.F. All authors have read and agreed to the published version of the manuscript.

**Funding:** The AdvanSiC project has received funding from the European Union's Horizon Europe programme under grant agreement no. 101075709.

Data Availability Statement: Data are contained within the article.

**Acknowledgments:** This paper has been partially supported by the Horizon EU Advances in Cost-Effective HV SiC Power Devices for Europe's Medium Voltage Grids (AdvanSiC). The views and opinions expressed are those of the author(s) only and do not necessarily reflect those of the European Union. Neither the European Union nor the granting authority can be held responsible for them.

**Conflicts of Interest:** Authors Laura Anoldo, Edoardo Zanetti, Walter Coco, Alfio Russo are employed by STMicroelectronics. The remaining authors declare that the research was conducted in the absence of any commercial or financial relationships that could be construed as a potential conflict of interest.

Materials **2024**, 17, 1908 11 of 12

### References

1. Kimoto, T.; Cooper, J.A. Fundamentals of Silicon Carbide Technology: Growth, Characterization, Devices and Applications; John Wiley Sons Singapore Pre. Ltd.: Singapore, 2014.

- 2. Gil, B.; Keshavarz, M.; Wales, D.; Darzi, A.; Yeatman, E. Orthogonal Surface-Enhanced RamanScattering/Field-Effect Transistor Detection of Breast and Colorectal Cancer-Derived Exosomesusing Graphene as a Tag-Free Diagnostic Template. *Adv. NanoBiomed Res.* 2023, *3*, 2300055. [CrossRef]

- 3. Kimoto, T. Material science and device physics in SiC technology for high-voltage power devices. *Jpn. J. Appl. Phys.* **2015**, *54*, 040103. [CrossRef]

- 4. Langpoklakpam, C.; Liu, A.-C.; Chu, K.-H.; Hsu, L.-H.; Lee, W.-C.; Chen, S.-C.; Sun, C.-W.; Shih, M.-H.; Lee, K.-Y.; Kuo, H.-C. Review of Silicon Carbide Processing for Power MOSFET. *Crystals* **2022**, *12*, 245. [CrossRef]

- 5. Guo, X.; Xun, Q.; Li, Z.; Du, S.J.M. Silicon Carbide Converters and MEMS Devices for High-temperature Power Electronics: A Critical Review. *Micromachines* **2019**, *10*, 406. [CrossRef] [PubMed]

- 6. Lichtenwalner, D.J.; Sabri, S.; van Brunt, E.; Hull, B.; Ryu, S.H.; Steinmann, P.; Romero, A.; Ganguly, S.; Gajewski, D.A.; Allen, S.; et al. Accelerated Testing of SiC Power Devices. In Proceedings of the 2020 IEEE International Integrated Reliability Workshop (IIRW), South Lake Tahoe, CA, USA, 9–14 October 2022.

- 7. Yang, L.; Castellazzi, A. High temperature gate-bias and reverse-bias tests on SiC MOSFETs. *Microelectron. Reliab.* **2013**, *53*, 1771–1773. [CrossRef]

- 8. Yano, H.; Kanafuji, N.; Osawa, A.; Hatayama, T.; Fuyuki, T. Threshold voltage instability in 4H-SiC MOSFETs with phosphorus-doped and nitrided gate oxides. *IEEE Trans. Electron. Dev.* **2015**, *62*, 324. [CrossRef]

- 9. Lelis, A.J.; Habersat, D.; Green, R.; Ogunniyi, A.; Gurfinkel, M.; Suehle, J.; Goldsman, N. Time dependence of bias-stress-induced SiC MOSFET threshold-voltage instability measurements. *IEEE Trans. Electron. Dev.* **2008**, *55*, 1835. [CrossRef]

- 10. Lelis, A.J.; Green, R.; Habersat, D.B.; El, M. Basic mechanisms of threshold-voltage instability and implications for reliability testing of SiC MOSFETs. *IEEE Trans. Electron. Dev.* **2015**, *62*, 316. [CrossRef]

- 11. Cabello, M.; Soler, V.; Rius, G.; Montserrat, J.; Rebollo, J.P. Godignon; Advanced processing for mobility improvement in 4H-SiC MOSFETs: A review. *Mater. Sci. Semicond. Process.* **2018**, *78*, 22–31. [CrossRef]

- 12. Singh, R. Reliability and performance limitations in SiC power devices. Microelectron. Reliab. 2006, 46, 713–730. [CrossRef]

- Van Brunt, E.; Lichtenwalner, D.J.; Park, J.H.; Ganguly, S.J.W. McPherson; Lifetime Modeling of the 4H-SiC MOS Interface in the HTRB Condition Under the Influence of Screw Dislocations. In Proceedings of the 2023 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 26–30 March 2023.

- 14. Ganguly, S.; Lichtenwalner, D.J.; Isaacson, C.; Gajewski, D.A.; Steinmann, P.; Foarde, R.; Hull, B.; Ryu, S.-H.; Allen, S.; Palmour, J.W. Negative Gate Bias TDDB evaluation of n-Channel SiC Vertical Power MOSFETs. In Proceedings of the 2022 IEEE International Reliability Physics Symposium (IRPS) 8B. 1-1-8B, Dallas, TX, USA, 27–31 March 2022; pp. 1–6.

- 15. Schroder, D.K. Semiconductor Material and Device Characterization, 3rd ed.; Wiley: Hoboken, NJ, USA, 2006.

- 16. Aichinger, T.; Rescher, G.; Pobegen, G. Threshold voltage peculiarities and bias temperature instabilities of SiC MOSFETs. *Microelectron. Reliab.* **2018**, *80*, 68–78. [CrossRef]

- 17. Moens, P.; Geenen, F.; De Schepper, L.; Cano, J.F.; Lettens, J.; Maslougkas, S.; Franchi, J.; Domeij, M. The Concept of Safe Operating Area for Gate Dielectrics: The SiC/SiO<sub>2</sub> Case Study. In *IEEE International Reliability Physics Symposium Proceedings*; IEEE: Piscataway, NJ, USA, 2023.

- 18. Masin, F.; De Santi, C.; Lettens, J.; Franchi, J.; Domeij, M.; Moens, P.; Zanoni, E. Non-monotonic threshold voltage variation in 4H-SiC MOSFET: Investigation and modeling. *JAP* **2021**, *130*, 7285. [CrossRef]

- 19. Zhu, S.; Liu, T.; White, M.H.; Agarwal, A.K.; Salemi, A.; Sheridan, D. Investigation of gate leakage current behavior for commercial 1.2 kV 4H-SiC power mosfets. In Proceedings of the IRPS 2021, Monterey, CA, USA, 21–25 March 2021; pp. 1–7.

- 20. Green, R.; Lelis, A.; Habersat, D. Threshold-voltage biastemperature instability in commercially-available SiC MOSFETs. *Jpn. J. Appl. Phys.* **2016**, *55*, 4. [CrossRef]

- 21. Rescher, G.; Pobegen, G.; Grasser, T. Threshold voltage instabilities of present SiC-power MOSFETs under positive bias temperature stress. *Mater. Sci. Forum.* **2016**, *858*, 481–484. [CrossRef]

- 22. Fiorenza, P.; Zignale, M.; Camalleri, M.; Scalia, L.; Zanetti, E.; Saggio, M.; Giannazzo, F.; Roccaforte, F. Impact of the NO annealing duration on the SiO2/4H–SiC interface properties in lateral MOSFETs: The energetic profile of the near-interface-oxide traps. *Mater. Sci. Semicond. Process.* **2024**, *169*, 107866. [CrossRef]

- 23. El Hageali, S.A.; Guthrey, H.; Johnston, S.; Soto, J.; Odekirk, B.; Gorman, B.P. Mowafak Al-Jassim; Nondestructive microstructural investigation of defects in 4H-SiC epilayers using a multiscale luminescence analysis approach. *J. Appl. Phys.* **2022**, *131*, 185705. [CrossRef]

- Fiorenza, P.; La Magna, A.; Vivona, M.; Roccaforte, F. Near interface traps in SiO<sub>2</sub>/4H-SiC metal-oxide-semiconductor field effect transistors monitored by temperature dependent gate current transient measurements. *Appl. Phys. Lett.* 2016, 109, 012102.

[CrossRef]

- 25. Fiorenza, P.; Vivona, M.; Iucolano, F.; Severino, A.; Lorenti, S.; Nicotra, G.; Bongiorno, C.; Giannazzo, F.; Roccaforte, F. Temperature-dependent Fowler-Nordheim electron barrier height in SiO<sub>2</sub>/4H-SiC MOS capacitors. *Mater. Sci. Semicond. Process.* **2018**, 78, 38–42. [CrossRef]

Materials **2024**, 17, 1908 12 of 12

26. Chanana, R.K.; McDonald, K.; Di Ventra, M.; Pantelides, S.T.; FeldmanG, L.C.; Chung, Y.; Tin, C.C.; Williams, J.R.; Weller, R.A. Fowler–Nordheim hole tunneling in p-SiC/SiO<sub>2</sub> structures. *Appl. Phys. Lett.* **2000**, 77, 2560–2562. [CrossRef]

- 27. Fiorenza, P.; Cordiano, F.; Alessandrino, S.M.; Russo, A.; Zanetti, E.; Saggio, M.; Bongiorno, C.; Giannazzo, F.; Roccaforte, F. Consideration on the extrapolation of the low insulator field TDDB in 4H-SiC power MOSFETs. In Proceedings of the 2023 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 26–30 March 2023; pp. 1–4. [CrossRef]

- 28. Liu, T.; Zhu, S.; Yu, S.; Xing, D.; Salemi, A.; Kang, M.; Booth, K.; White, M.H.; Agarwal, A.K. Gate oxide reliability studies of commercial 1.2 kV 4H-SiC power MOSFETs. In Proceedings of the IRPS 2020, Dallas, TX, USA, 28 April–30 May 2020; pp. 1–5.

- 29. Fayyaz, A.; Castellazzi, A. High temperature pulsed-gate robustness testing of SiC power MOSFETs. *Microelectron. Reliab.* **2015**, 55, 1724–1728. [CrossRef]

- 30. DiMaria, D.J.; Stasiak, J.W. Trap creation insilicon dioxide produced by hot electrons. J. Appl. Phys. 1989, 65, 2342. [CrossRef]

- 31. Fiorenza, P.; Bongiorno, C.; Giannazzo, F.; Alessandrino, M.S.; Messina, A.; Saggio, M.; Roccaforte, F. Interfacial electrical and chemical properties of deposited SiO<sub>2</sub> layers in lateral implanted 4H-SiC MOSFETs subjected to different nitridations. *Appl. Surf. Sci.* **2021**, 557, 149752. [CrossRef]

**Disclaimer/Publisher's Note:** The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content.