Surface Preparation and Deposited Gate Oxides for Gallium Nitride Based Metal Oxide Semiconductor Devices

Abstract

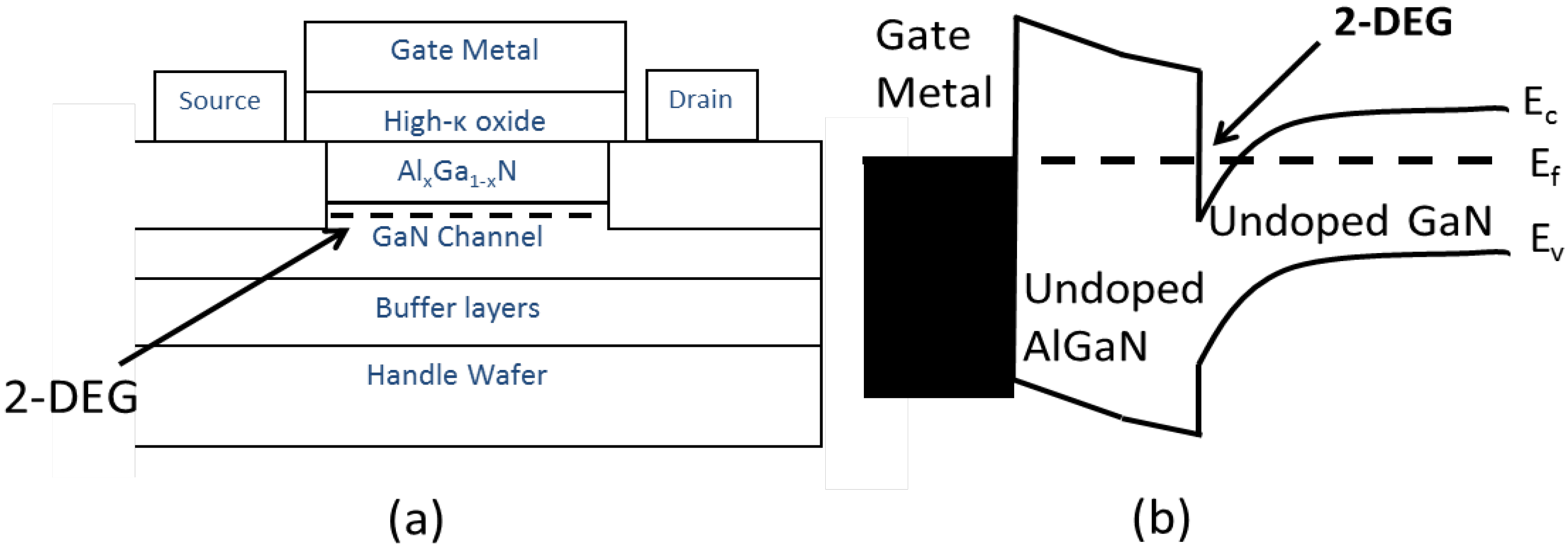

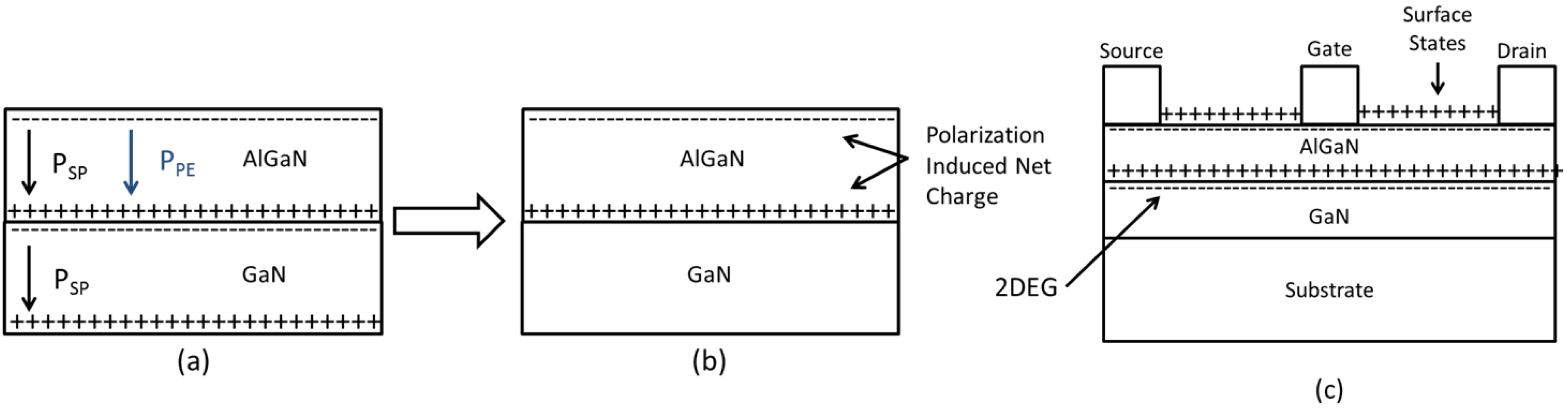

:1. Introduction

2. GaN Surfaces

2.1. Growth of GaN

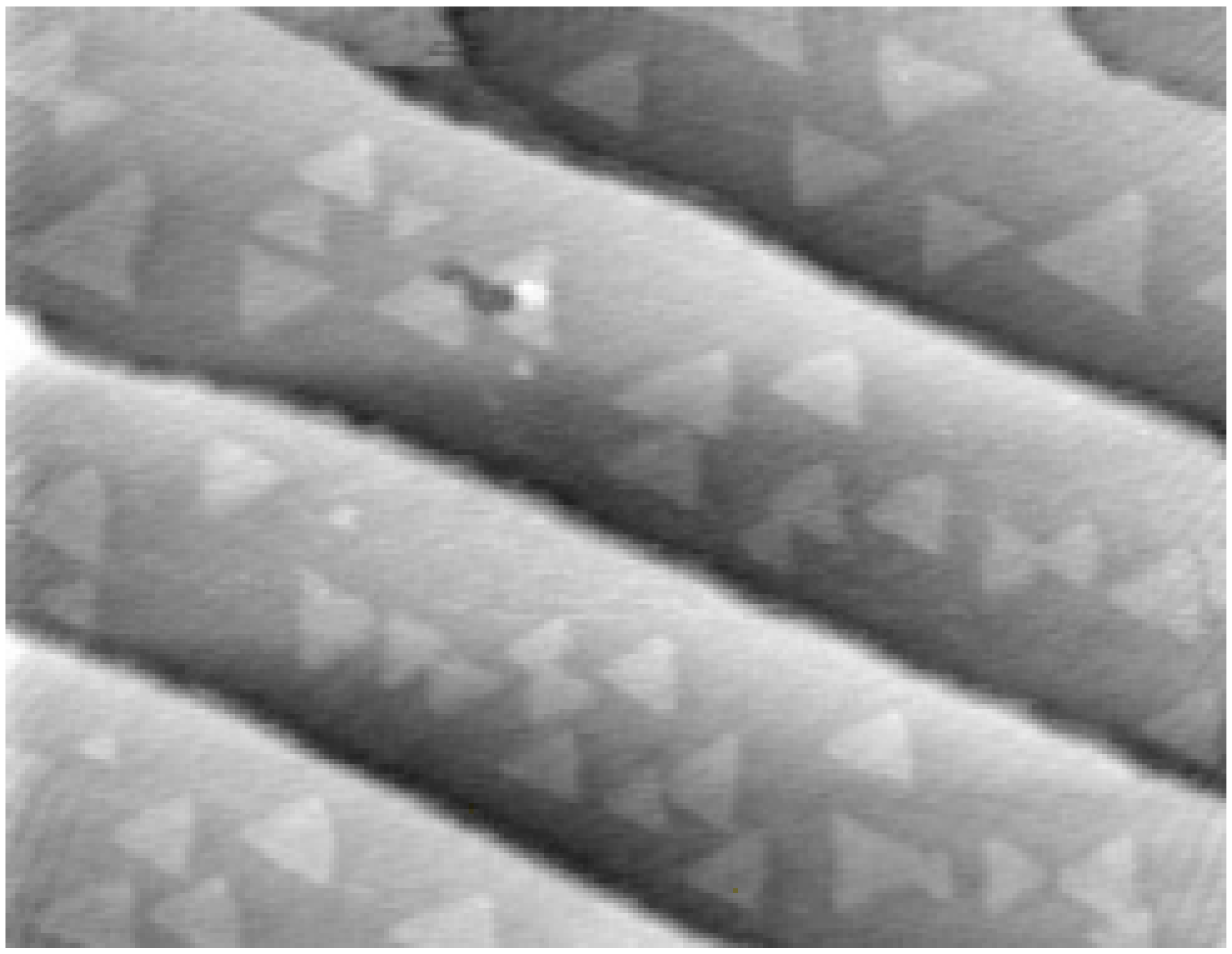

2.2. Surface Reconstruction

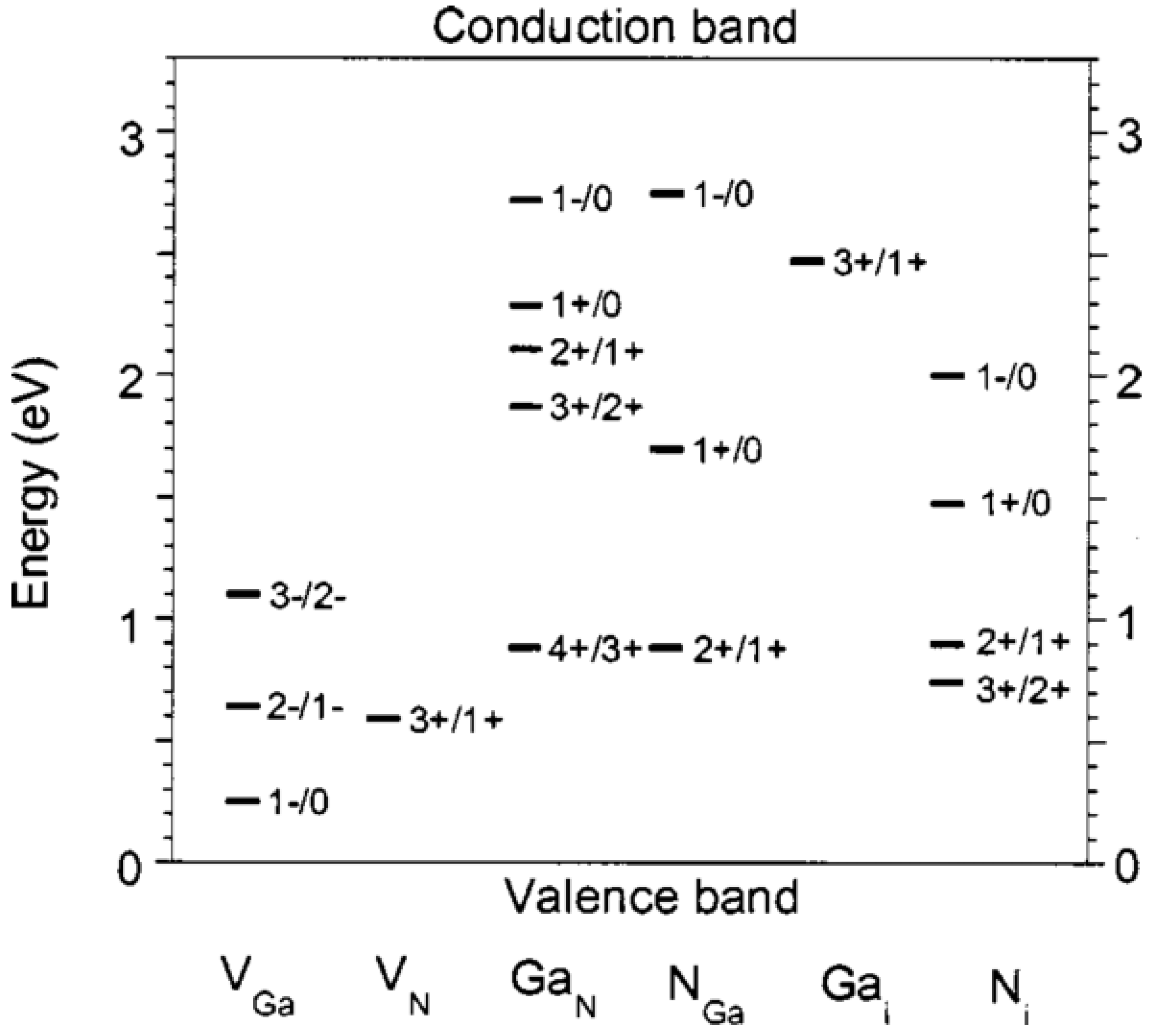

2.3. Bulk Defects

2.4. Surface Defects

| Reference | GaN Growth technique | Defect level | Defect type | Defect origin | Method of evaluation | Comment |

|---|---|---|---|---|---|---|

| [65] | Ammonia MBE n type GaN | Ec − 3.28 | Bulk | Carbon related acceptor impurity | DLTS/DLOS | Also observed for plasma assisted MBE and MOCVD GaN |

| Ec − 2.62 | Bulk | Gallium Vacancy | DLTS/DLOS | – | ||

| Ec − 1.28 | Bulk | Carbon related interstitial impurity | DLTS/DLOS | Also observed for plasma assisted MBE and MOCVD GaN | ||

| Ec−0.72 | Bulk | Unknown | DLTS | Observed in MBE & MOCVD GaN; low concentrations | ||

| Ec−0.62 | Bulk | Unknown | DLTS/DLOS | Seen in alternative growth methods; not carbon related | ||

| Ec − 0.4 | Bulk | Unknown | DLTS | Observed in MBE & MOCVD GaN; low concentrations | ||

| Ec − 0.25 | Bulk | Nitrogen vacancy related | DLTS/DLOS | Seen in alternative growth methods | ||

| [66] | MOCVD n type GaN | Ec−Et = 3.28 | Bulk | Carbon related acceptor impurity | DLTS/DLOS | – |

| Ec−3.22 | Bulk | Acceptor | DLTS/DLOS | Not seen in MBE grown GaN | ||

| Ec − Et = 1.35 | Bulk | Carbon related interstitial impurity | DLTS/DLOS | – | ||

| [64] | MOCVD p type GaN | – | Surface | Acceptor N Interstitials | NEXAFS | – |

| Pin Fermi Level close to CBM | Surface | Donor N vacancies | NEXAFS | – | ||

| [67] | N/A | Fermi level pinned 0.5–0.7 below CBM on polar Ga face | Surface | Ga dangling bonds | Modified DFT | N Type SubstrateModerate Ga/N ratios (close to 1) |

| Fermi level pinned 1.2 above VBM on polar N face | Surface | Ga dangling bonds | Modified DFT | P Type SubstrateModerate Ga/N ratios (close to 1) | ||

| Fermi level pinned 1.8 above VBM on polar Ga face | Surface | Ga-Ga bonds | Modified DFT | N Type SubstrateGa rich conditions | ||

| Fermi level pinned 1.6 above VBM on polar N face | Surface | Ga-Ga bonds | Modified DFT | P type SubstrateGa rich conditions | ||

| [27] | MBE n type GaN | Ef − EVBM = 2.89eV | Surface | – | XPS | Moderate Ga/N ratios (close to 1) |

| Ef − EVBM = 1.65eV | Surface | – | XPS | Ga rich conditions |

3. GaN Surface Treatment

| Reference | GaN | Clean | Comment |

|---|---|---|---|

| [69] | Plasma Assisted MBE GaN (0001) on Sapphire | 60 s in HCl (25 °C) and 30 s in buffered HF. The second cleaning process included a 20 min boil in (NH4)2S | boiling n- and p-GaN in (NH4)2S resulted in decreased barrier height |

| [74] | MOCVD GaN (0001) on Sapphire | (1) Degrease: Boil in trichloroethylene for 3 min; Boil in isopropanol for 3 min Three rinses in DI for 20 s each; Blow dry with N2; (2) Aqua regia (AR): Degrease; Boil in HCl:HNO3 = 3:1 for 8–10 min rinses in DI for 20 s each; Blow dry in N2; (3) HCl: Degrease; Aqua regia HCl:H2O = 1:1 dip for 60 s Two rinses in DI for 20 s each; Blow dry with N2; (4) KOH: Degrease; Aqua regia; 1 mol KOH boil for 3 min Three rinses in DI for 60 s each Blow dry with N2; (5) (NH4)2S: Degrease; Aqua regia; (NH4)2S for 1 min Three rinses in DI for 60 s each. Blow dry with N2 | AES has shown the contaminant as C and O and that using compounds with Cl and S, will leave Cl and S on the surface. Using (NH4)2S prevented re-oxidation of the surface, and further removes Cl from the surface of the GaN. KOH effectively removes the C on the surface. |

| [68] | Plasma Assisted MBE GaN (000). on sapphire | Samples were rinsed in a 1:10 solution of HCl, and then rinsed in DI water. Cleaned by repeated cycles of nitrogen ion sputtering and annealing to 850 °C. Sulfur was deposited from an UHV compatible electrochemical cell. | Exposure of the clean Ga adlayer (000) GaN surface to sulfur inhibits oxygen adsorption |

| [75] | HVPE GaN (0001) on Sapphire & MOCVD GaN(0001) on SiC | Strong acids, strong bases, strong oxidizers. After dipping in a given chemical, the sample is then rinsed in DI water and solvents and blown dry with N2. Sulfide solution consisting of 20%–50% (NH4)2S and 50%–80% H2O. | Various chemicals strongly affect the surface recombination velocity in GaN. Treatment with (NH4)2S or Na2S effectively reduces the SRV in GaN. A 1:1 (NH4)2Sand CH(OH)CH3 solution increases the PL intensity by a factor of four to six. The effect of the non-sulfide treatments on the SRV is important for GaN device processing. The HCl, BOE, and HF treatments produce the greatest improvements. |

| [76] | MOVPE GaN (0001) on Sapphire | (1) Chemical Etch only:Degreased in acetone, dipped in HF: DI H2O 1:10 for 1 min, rinse in DI; (2) In situ Annealing: Chemical Etch; Annealed at 600 °C for 10 min in UHV; (3) In Situ Ga Reflux: Chemical Etch: 2 cycles of Ga deposition, reduction and re-evaporation in UHV; 900 °C anneal | All treatments result in surfaces increasingly free of oxide contamination. HF etching and UHV annealing produce abrupt, well-defined interfaces. Conversely, GaN substrate cleaning in a Ga flux results in Au/GaN intermixing. |

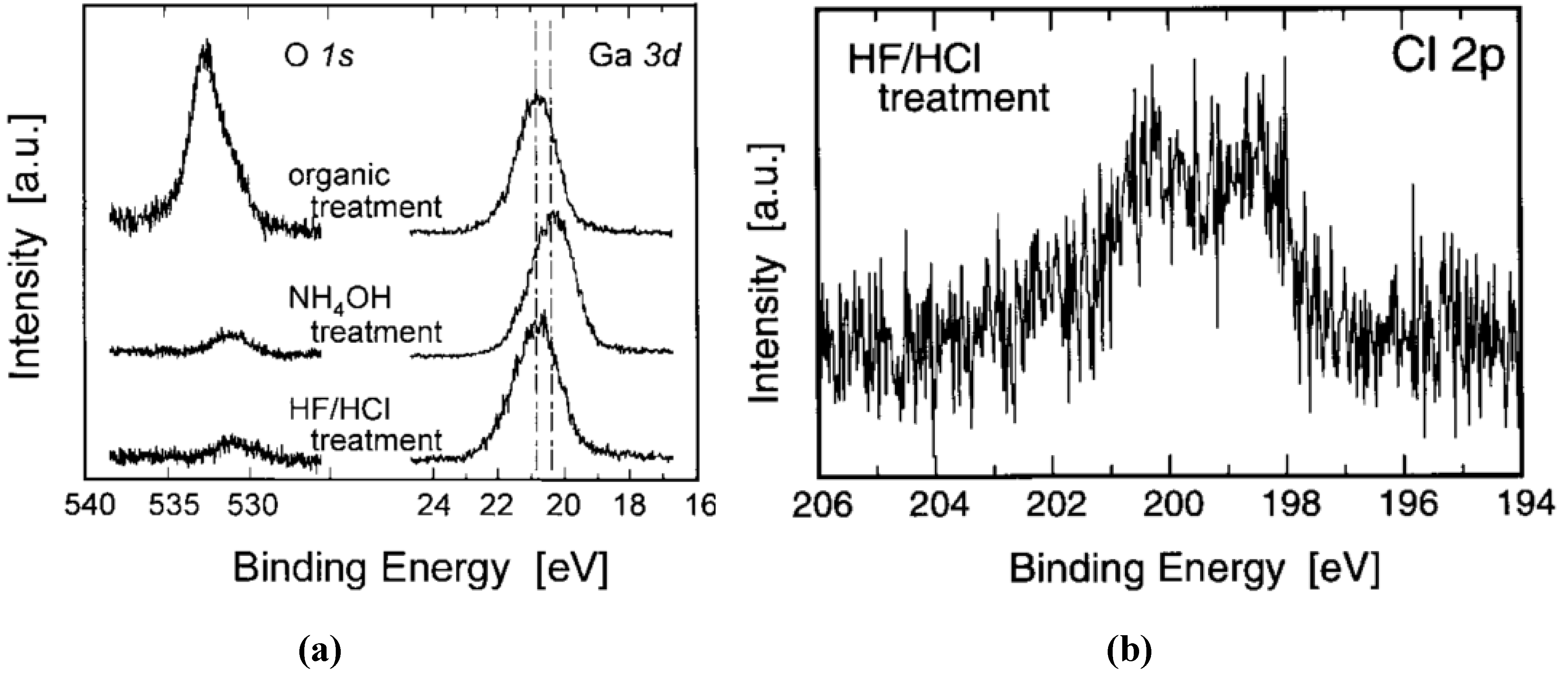

| [77] | MBE GaN (0001) on Sapphire | For ex situ cleaning, solvents (acetone and methanol), acids (HF and HCl), and UV/O3 treatments were used. The samples were rinsed in DI water and blown dry with N2. After all wet chemical treatments UV/O3 exposure was performed with N2 after all wet chemical treatments. N2 and N2/H2 plasma treatments were conducted in an ultrahigh vacuum (UHV) Metal Organic MBE | For ex situ cleaning methods, the lowest O levels on GaN surfaces were achieved after HF and HCl based acid treatments, while UV/O3 cleaning was very effective for removing carbon. Further removal of the O could be achieved after in situ thermal cleaning with H2/N2 plasma. |

| [78] | HVPE, LPE stand alone GaN (0001) | Rinsed in Ultrapure water for 5 min; dipped in etchant for 50–1000 s, rinsed in ultrapure water for 5 min, blown by dry N2, Four kinds of etchant were used: 0.5 wt.% HF (pH = 3.3 and ORP = 250mV), 0.7 wt.% HCl (2.1, 250 mV), 0.6 wt.% HNO3 (1.5, 240 mV), and 0.7 wt.% NaOH (12.0, −70 mV). All wet cleaning procedures were done under fluorescent light. Some samples were postannealed in UHV (base pressure: 1 × 10−8 Pa) by three-step annealing (200 °C for 12 h, 400 °C for 1 h, and 550 °C for 10min) | The HF-treated and postannealed commercial and original GaN (0001) could induce the similar quality to that of in situ MBE-grown GaN (0001) 2 × 2-N. In the case of performing wet etching on a GaN system, selecting an etchant solution with a certain pH and ORP and controlling etching time are important to obtain an oxide-free and balanced-stoichiometry surface. |

| [79] | MOCVD GaN (0001) on Sapphire | Boiling acetone followed by boiling isopropanol for 10 min each prior to HF (2:1 HF : distilled H2O), hot HCl (1:1 HCl: distilled H2O at 70 °C) or 2M NaOH. | Treatment in HF was the most effective method for removing surface O and minimizing additional deposition of C or other surface contaminants. HCl treatment was equally effective at oxygen removal, but C and Cl were also deposited during the cleaning procedure. The cleaning in 2M NaOH was more effective for removing surface C compared to HCl or HF; however residual Na remained on the surface and surface O was not removed. |

| [80] | MOVPE GaN (0001) on SiC | The samples were immersed in TCE, acetone, and methanol for 1 min in each solvent; in 37% HCl for 10 min and in de-ionized water for 10 s. In situ chemical vapor cleaning: Ammonia introduced into the chamber at a pressure of 1 × 10−4 Torr and the sample heated to 865 °C for 15 min. The sample was cooled to 500oC and then the ammonia was turned off. | A contamination layer of hydrocarbons and oxygen, the latter contained in a hydroxide, remained on the HCl treated surfaces. In contrast, the ammonia-based CVC produced surfaces that were free of these contaminants within the limits of XPS and UPS detection. |

| [81] | HVPE GaN (0001) on Sapphire | Degrease in an ultrasonic bath for 10 min each in TCE, acetone, methanol and DI water, then treated in concentrated HCl for 20 min, rinse in DI water, blow dry N2. NH3 introduced to the chamber at a pressure of 1 × 10−4 Torr. Sample was heated to 900oC for 20 minutes. Cooled and NH3 flow stopped when temperature reached 500oC | High temperature NH3 annealing treatment of the GaN (0001) surface can be used to clean the surface from carbon contaminants down to XPS detection limits, whereas a significant amount of residual oxygen species remains. |

| [82] | MBE GaN (0001) on Sapphire | (1) Cleaning in organic solvents; (2) Dip in HF:HCl:H2O = 1:5:5 solution for 1 min after organic solvents; (3) dip in NH4OH solution for 15 min at 50 °C | From the viewpoints of oxide removal and maintenance of stoichiometry, it is concluded that etching in NH4OH solution at 50 °C gives the best result. |

4. GaN MOS

4.1. Capacitance-Voltage Measurements

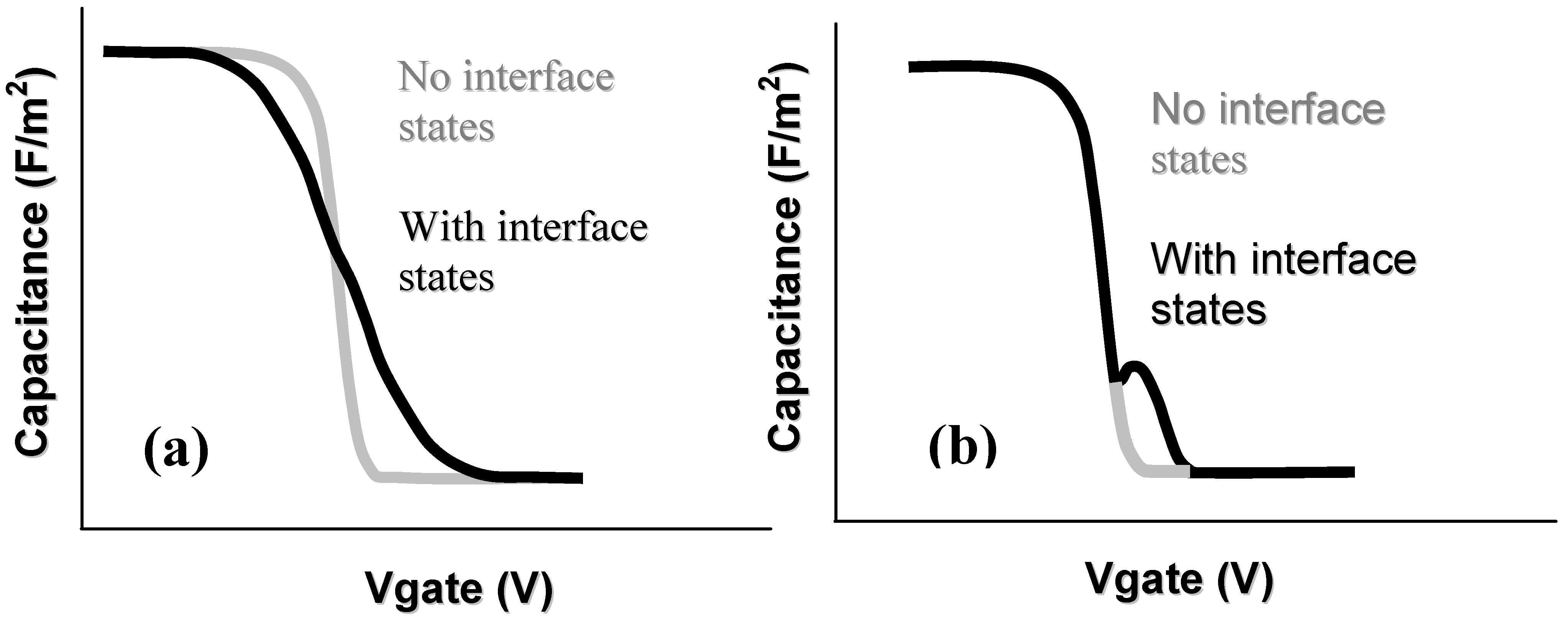

- Doping: In general for Si-SiO2 MOS capacitors, the doping concentration is modest, on the order of ~1016 cm−3. For GaN devices, there is significant variation in literature reports, with levels between ~1016 cm−3 and ~1018 cm−3 [85,86,87] This doping variation has a significant impact on the subsequent capacitance voltage profiles, with a more stretched-out profile observed in depletion going to deep depletion for a highly-doped channel layer. Qualitative analysis of such CV data might be misinterpreted as a high interface state density. An example of the effect of the GaN dopant concentration on measured capacitance voltage profiles is shown in [87].

- Oxide thickness: Metal-oxide-semiconductor structures for conventional CMOS digital applications require thin dielectrics. The push for < 1 nm equivalent oxide thicknesses (EOT - the thickness of SiO2 that would be required to achieve the same capacitance as the gate stack with adielectric other than SiO2) has been the focus of much investigation for highly-scaled MOS devices. However, for GaN based devices used in high power and high temperature applications, the oxide thicknesses employed have thus far been much thicker—up to 150 nm—compared to those investigated in CMOS logic [88]. Recent research has begun to focus on thinner oxides [89]. When working with thick oxides, the interpretation of the capacitance voltage profile can be complicated by the fact that the electric field in the GaN is reduced and, for the same interface state density, the modulation of the surface charge on the semiconductor—and thus the Fermi level movement—by the AC signal of the CV meter will be reduced. This leads to a more stretched out capacitance-voltage profile, which could be misinterpreted as a higher Dit.

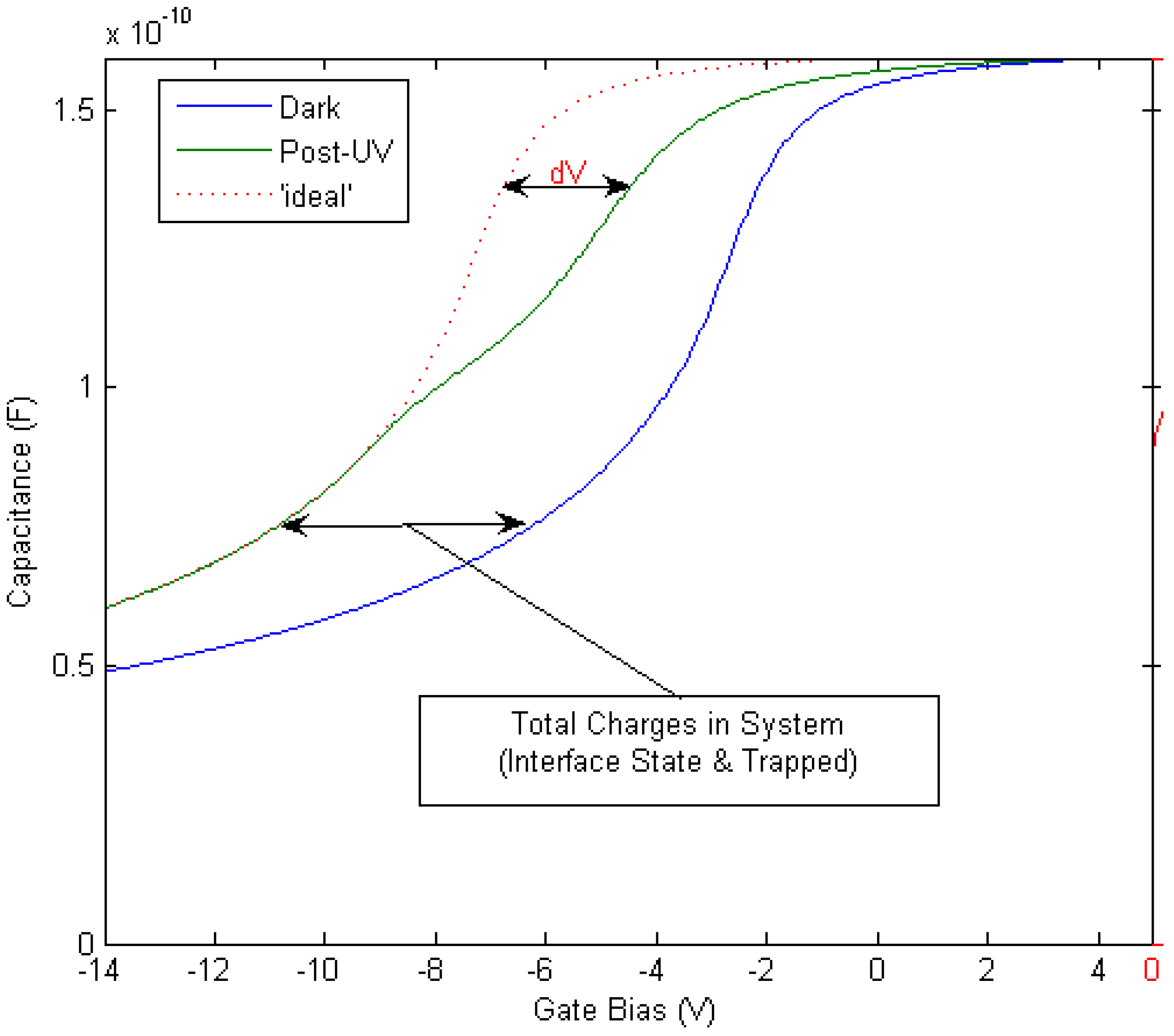

- Extraction of Dit: In materials with spontaneous polarization charges, such as the Group 3-nitrides, the Gray–Brown technique [90] is not useful because the effect of the interface traps on the flatband voltage shift as temperature is varied is confounded by the presence of pyroelectric polarization charges (the change in spontaneous charge density with temperature) [91]. There are two difficulties in applying the conventional Terman method [92] for Dit measurements of GaN-based MOS devices. Firstly, it fails to describe interface states with energies in portions of the band gap that are not close to the GaN conduction band edge due to the extremely low hole generation rate (as a result of the large band gap of GaN). Once an interface state captures an electron in this system, the lack of holes does not allow the electron to recombine [85]. The Terman method relies on the states to emit and/or capture carriers at high frequency while the DC bias is swept. If recombination can happen, the traps respond to the slowly varying DC gate voltage and cause the CV profile to “stretch out” along the gate voltage axis as interface trap occupancy changes with gate bias. Secondly, in the estimation of Dit using the conventional Terman method, doping concentration should be known exactly to compare the difference between the measured and calculated CV profiles. However, doping concentration for a calculated CV profile is selected until a close fit is obtained over the entire voltage range, because the CV characteristics of GaN MOS capacitors show deep depletion instead of inversion at practical measurement temperatures. Therefore, the “stretch-out” of the CV associated with uniformly distributed Dit can be misinterpreted as an increased doping concentration, leading to an underestimation of Dit [93]. The high-low frequency method or conductance method, which do not require a theoretical profile to compare with the measured profile, can be considered to reduce the uncertainty associated with doping concentration in CV characterizations of the GaN MOS system. However, due to high series resistance and system noise, very few quasi-static or low (below 100 Hz) frequency CV profiles have been reported to date [94] and the conductance method can only measure interface states with short emission times [85]. The method developed for SiC—a photo-assisted CV measurement—was used by Wu et al. on GaN [95] and measurements taken at varying temperatures were demonstrated in references [96] and [97]. However, photo-assisted high-frequency CV only yields the average interface state density as derived from the total number of interface states divided by the bandgap energy range. Swenson et al. [85] have modified the photo-assisted procedure to determine the interface state density variation across most of the GaN bandgap, by comparing an ‘ideal’ CV in the dark with a CV measured following UV illumination, see Figure 8. This procedure was optimized for the Si3N4/GaN system. More work is required in order to develop a method or a complimentary range of methods including deep level transient spectroscopy (DLTS), deep level optical spectroscopy (DLOS) as well as modified versions of current conventional CV/GV methods described herein for use on GaN-based MOS devices. In the summary of GaN MOS device performance presented in Table 3, the method used to extract the interface state density (if known) is stated and the limitations of the various methods should be borne in mind when interpreting the data.

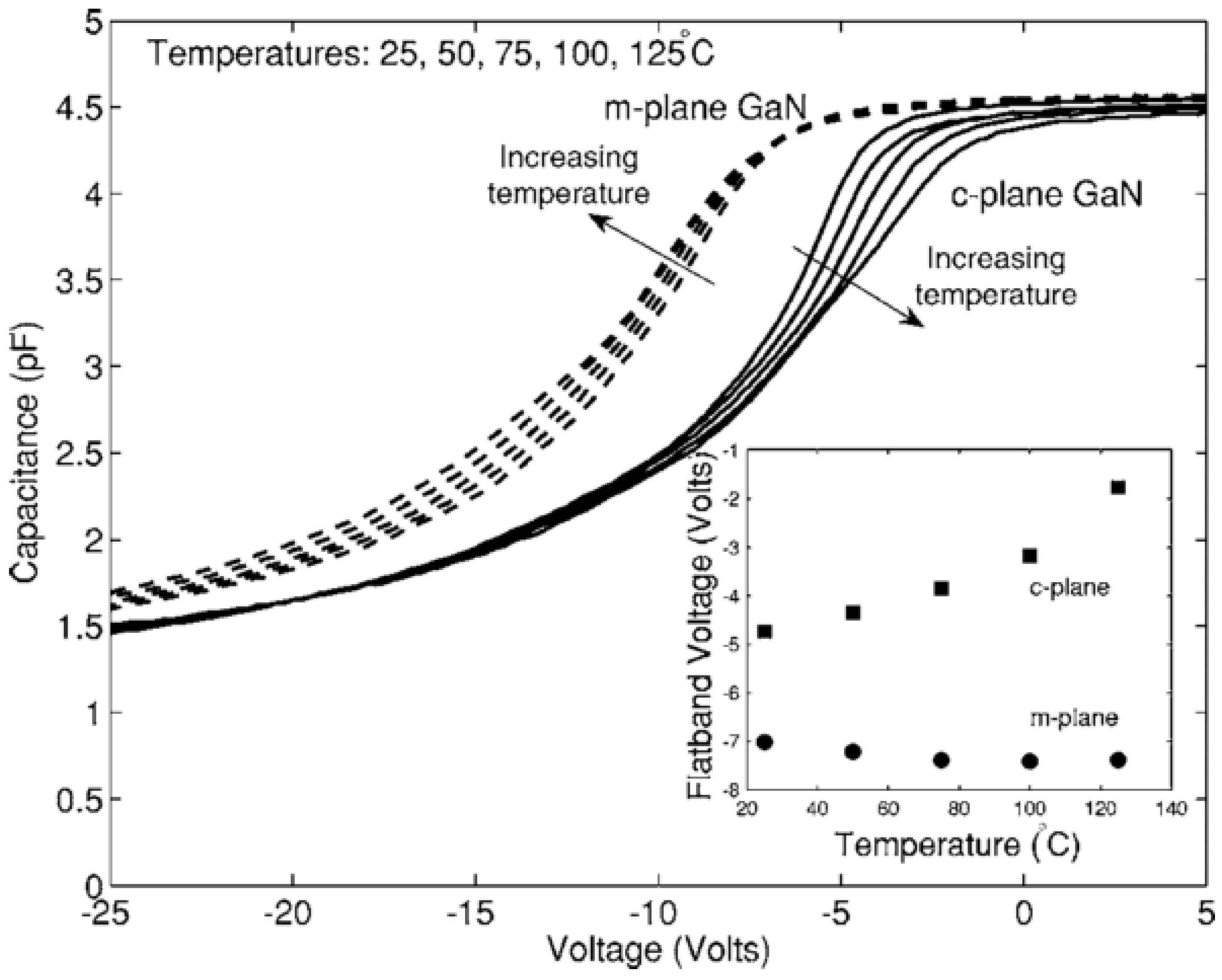

- Pyroelectric effect: The pyroelectric effect is the change in spontaneous charge density with temperature that occurs in crystals that lack a center of symmetry. Pyroelectricity is one source of the strong temperature shift in flatband voltage and threshold voltage of GaN MOS capacitors and MOSFETs. Matocha et al. [88] have demonstrated a clear effect of the pyroelectric charge on MOS capacitor characteristics (see Figure 9). This complicates the interpretation of measurements with varying temperature [96,98] as any interface state density response will also vary with varying temperature.

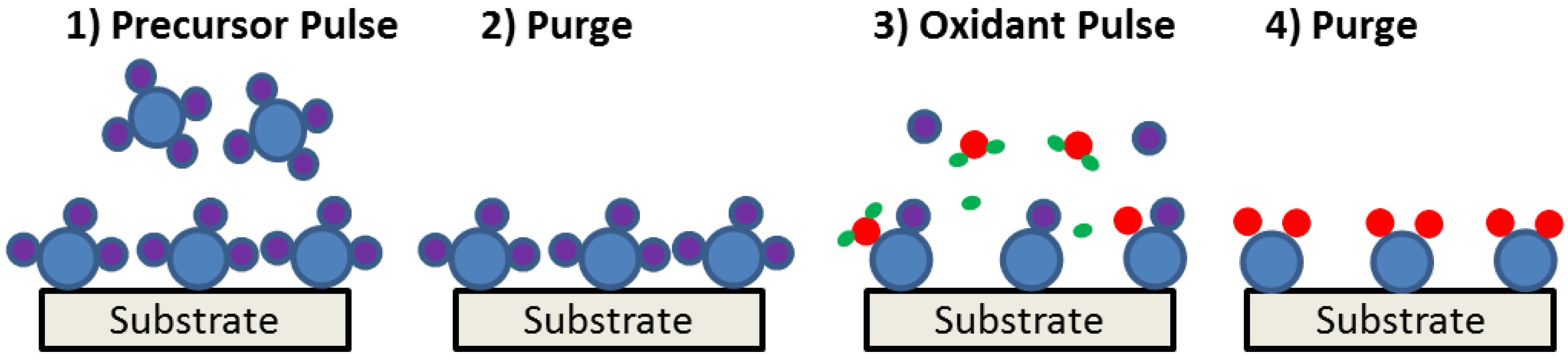

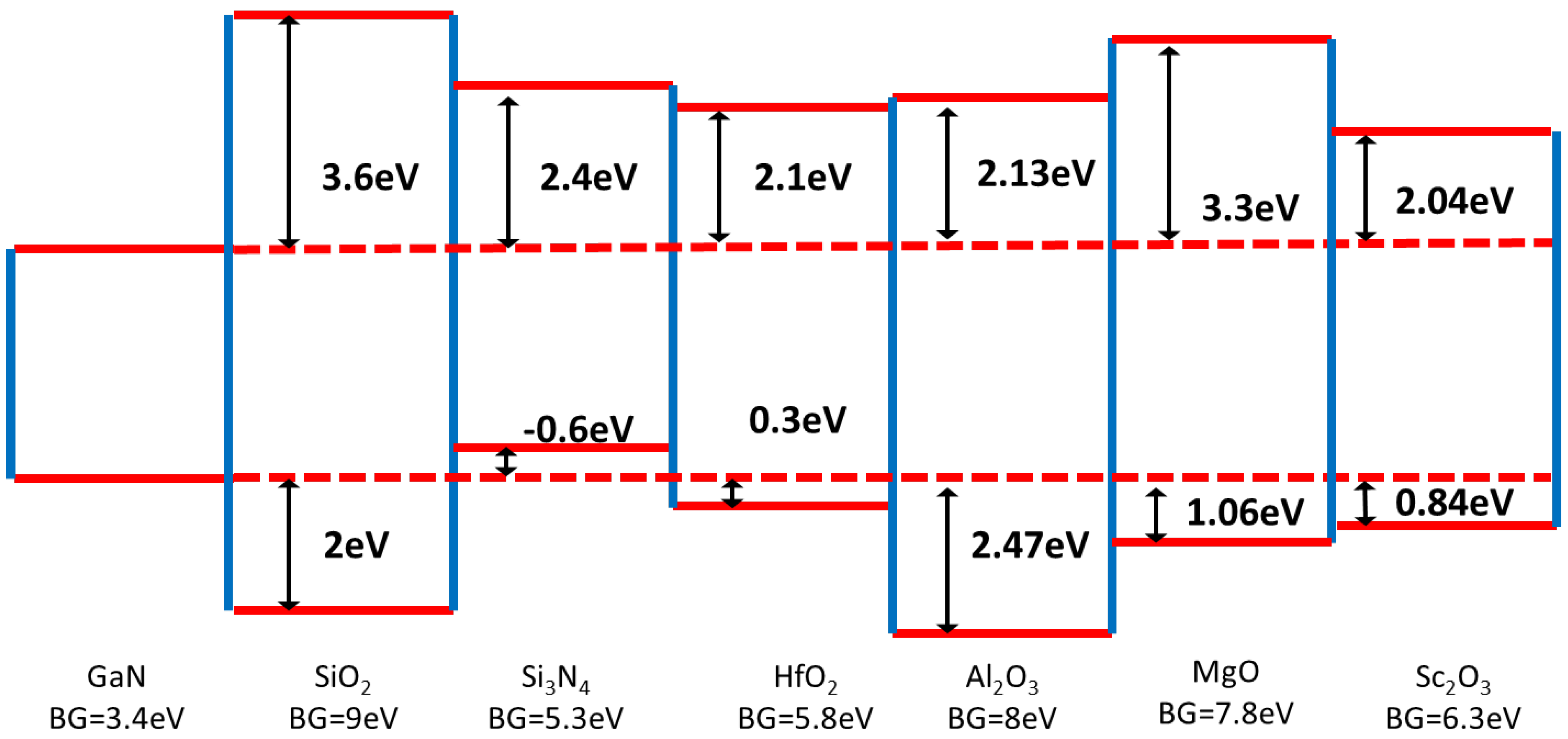

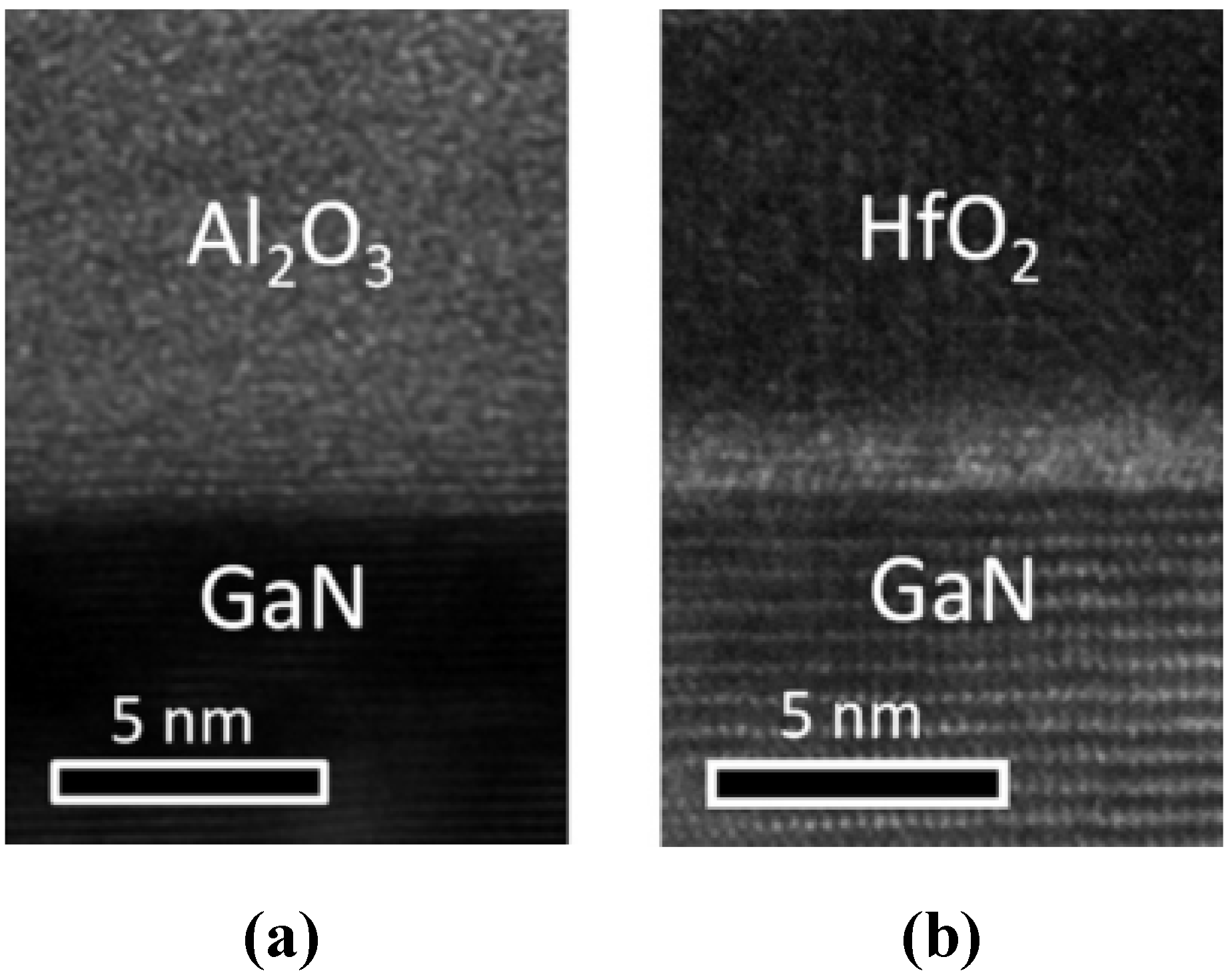

4.2. Choice of Gate Insulator Material and Preferred Deposition Technique

4.3. MOS Devices Reported

- It is clear that the possible dielectrics being adopted for GaN go beyond the SiO2 and SiNx, with atomic layer deposition being the technique of most interest recently (and possibly most relevant to manufacturing).

- It is also clear that the surface cleaning treatments being used vary widely – from in situ vacuum anneals, to ex situ acid and/or base treatments.

- The method for extraction of the interface state density and the densities themselves also vary widely—in general the values presented when extracted using the Terman method are lower. With such variance in the determination of Dit, and the difficulty of quantifying Dit in a relatively large band gap system, it is very difficult to draw solid conclusions from the values presented, and thus to concretely deduce more favorable treatments and dielectric deposition techniques.

| Reference | GaN growth technique | Dielectric | Deposition technique | GaN clean/treatment | Dit extraction method | Dit cm−2 eV−1 |

|---|---|---|---|---|---|---|

| [89] | MOCVD | Al2O3, HfO2 | ALD | None mentioned | Terman | Near Midgap 6–10 × 1011 |

| [94] | MOCVD, MBE | SiO2 | (Electron Cyclotron Resonance-Plasma Enhance CVD) | UV/Ozone oxidation, BOE; thermal anneal at 300°C in UHV | High-low method | 2 × 1011 |

| [120] | – | Al2O3, HfO2 | ALD | None mentioned | Conductance Technique | ~ 1012 |

| [97] | – | HfAlO | MOCVD | 10 min HCl (H2O/HCl = 1:1)(NH4)2S solution for 30 min | Conductance with increased temperature | At midgap: As deposited 2 × 1012; with SiH4+NH3 2 × 1010 |

| [121] | MOCVD | Al2O3 | ALD | 30% HF | Terman | < 1 × 1012 |

| [122] | MOCVDP Type | Oxidized GaN | bias-assisted photo electrochemical oxidation | BOE | Photo assisted CV | Average value 4.18 × 1011 |

| [86] | CVDP Type | SiO2 | Plasma Enhance CVD | RCA-based cleaning process | Terman | 1.1 × 1011 and 6 × 1011 at Ec − ET = 0.2 eV for silane & TEOS; 1.1 ×1011 and 1 × 1012 at ET−EV = 0.2 eV for silane and TEOS |

| [85] | MOCVD | Si3N4 | MOCVD | None mentioned | Modified Photo assisted CV | 5.0 × 1012 at 0.3 eV |

| [117] | MOCVD | Al2O3 | ALD | H2SO4:H2O2 (3:1) for 5 min and HCl:H2O (1:1) for 3 min | Photo assisted + Conductance Technique | 3 × 1012 as deposited |

| [123] | MOCVDP Type | Al2O3, HfO2 | ALD | HCl | Conductance Technique | 4–9 × 1011 near midgap |

| [98] | MOCVD | Al2O3 | ALD | None | Terman | 1 × 1013 at CB edge |

| [107] | MBE | Ga2O3(Gd2O3) | Ebeam | 600 °C UHV | Terman | 1 × 1011 at midgap, |

| [113] | MOCVD | HfO2 | ALD | None | Terman | 2 × 1011 at midgap |

| [95] | MOCVD | Al2O3 | ALD | RCA-based cleaning process | Photo assisted Technique + Terman | Midgap: Terman 5 × 1010 Photoassisted ~ 5 × 1011 |

| [124] | MOCVDN and P Type | SiO2 | Plasma Enhanced CVD | (1:1 H2SO4/H2O2) for 10 min then (1:3 HCl/H2O) for 3 min | Conductance Technique | 6 × 1010 at Ec − 0.2 eV; 1.4 × 1011 (at 0.61 eV) near the valence band; 7.5 × 1010 deeper into the band gap. |

| [106] | HVPE | SiO2 | Remote Plasma Assisted Oxidation/Remote Plasma Enhanced CVD | None mentioned | Terman | Min Dit 1 × 1011 at ~ 0.45 eV below CB |

| [93] | HVPE | SiO2 | Remote Plasma Assisted Oxidation (Nitridation) | 1:5 NH4OH:H2O at 60–80 °C (or in HCl based solutions). | Not Stated | Midgap 1011 |

| [109] | MOCVD | SiO2; SiNx | Remote Plasma Enhance CVD | NH4OH/H2O 1:5 solution at 80 °C for 15 min | High-low and Conductance | mid 1011 at EC-E ~ 0.3 eV |

| [91] | MOCVD | SiO2 | Low Pressure CVD | H2SO4 : H2O2 (1:1) at 70oC for 10 min | Conductance Technique | Best: 1 × 1011 at 0.25 eV below CB edge |

| [125] | HVPE | SiO2 | Remote Plasma Assisted Oxidation | 1:5 NH4OH:H2O solutions at 60–80 °C (or in HCl-based solutions). Exposed to reactive species from a remote N2/He discharge | Terman | Min Dit: 3 × 1011 with RPAO 2 × 1012 without RPAO samples |

| [126] | MBE, MOCVD | SiO2 | Plasma Enhanced CVD | 1 HCl:2 H2O | Terman | Minimum for as deposited 2 × 1011 |

| [118] | MOCVDP Type | Al2O3/TiO2/Al2O3 | RF Sputtering | (NH4)2Sx | Terman | 4 × 1011 Midgap |

| [119] | MOCVDP Type | MgO/TiO2/MgO | RF Sputtering | (NH4)2Sx | Terman | 3 × 1011 Midgap |

5. Discussion

5.1. Matching Reported GaN Bulk and Surface Defects to Reported MOS Characteristics

- From Table 1, there are defect states related to C impurities in the GaN bulk that have energies near the valence band maximum, as do Ga vacancies in GaN.

- From Table 1, Ga dangling bonds and Ga-Ga bonds have defect energies in the upper half and mid to lower half of the bandgap respectively.

- From Table 1, there is a defect level close to the conduction band minimum resulting from N vacancies.

- Combining the information from points 1, 2 and 3, suggests that mid gap, where many of the experimental Dit values in the literature are quoted, is actually where the interface trap density may be relatively low, giving a misleading view of the actual defect density.

- The MOS device literature reviewed herein suggests that defects at the GaN surface do not typically pin the Fermi level, as the maximum capacitance reached experimentally is consistent with ideal predicted values. However, the fact that so many defects with energies near the valence band maximum are experimentally detected suggests a possible difficulty in making functioning inversion mode MOS devices on GaN.

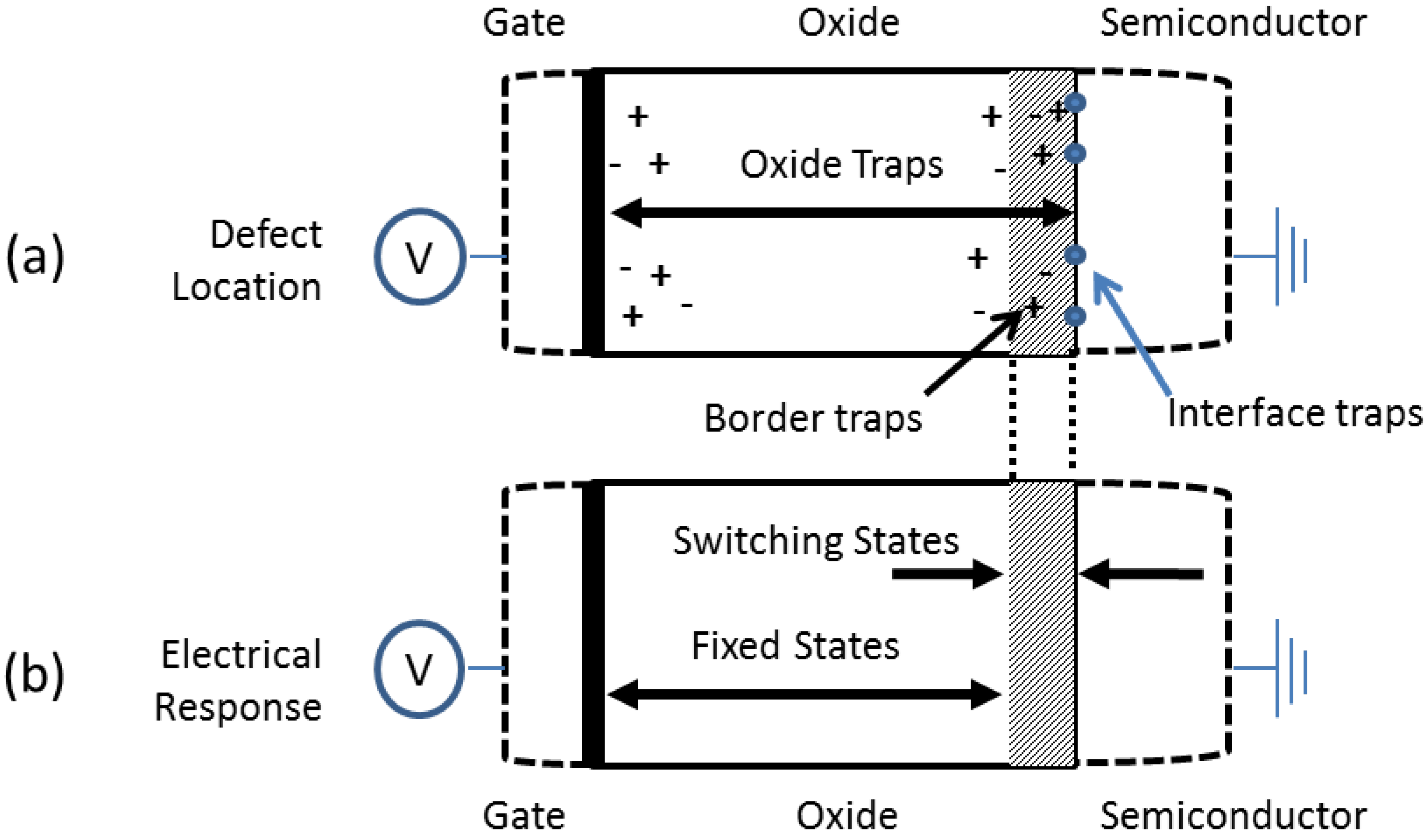

- The Dit values reported in the literature may reflect not only the influence of dielectric/GaN interface defects, but also of defects in the dielectric and in the near-surface region of the GaN substrate.

5.2. Defects at the Dielectric/GaN Interface

5.3. Reduction of Defects at the Dielectric/GaN Interface

5.4. Defects in the Dielectric

5.5. The MOS-HEMT

6. Conclusions

Acknowledgements

References

- Athanasios, D.; Evgeni, G.; Paul, C.M.; Marc, H. Advanced Gate Stacks for High-Mobility Semiconductors; Springer: Berlin, Germany, 2007; p. 230. [Google Scholar]

- Morkoc, H.; Strite, S.; Gao, G.B.; Lin, M.E.; Sverdlov, B.; Burns, M. Large-band-gap SiC, III-V nitride, and II-VI ZnSe-based semiconductor device technologies. J. Appl. Phys. 1994, 76, 1363–1398. [Google Scholar] [CrossRef]

- Translucent, Gallium Nitride on Silicon: vGaNTM. Available online: http://www.translucentinc.com/gan_on_si.php (accessed on 19 July).

- BRIDGELUX. Available online: http://bridgelux.com/media-center/press-releases/bridgelux-demonstrates-dramatic-advancements-in-gan-on-silicon-technology-for-solid-state-lighting/ (accessed on 18 July 2012).

- Lapedus, M. Lidow Returns with “Disruptive” GaN Startup. EE Times. 8 March 2011. Available online: http://www.eetimes.com/electronics-news/4088019/Lidow-returns-with-disruptive-GaN-startup (accessed on 18 July 2012).

- Stevenson, R. The world’s best gallium nitride. IEEE Spectrum 2010, 47, 40–45. [Google Scholar] [CrossRef]

- Plenty of Opportunity in Billion Dollar HB LED Materials Market. SEMI. 3 November 2009. Available online: http://www.semi.org/en/MarketInfo/CTR_032685 (accessed on 18 July 2012).

- Huan, W.; Khan, T.; Chow, T.P. Enhancement-mode n-channel GaN MOSFETs on p and n-GaN/sapphire substrates. Electron. Device Lett. IEEE 2006, 27, 796–798. [Google Scholar] [CrossRef]

- Asbeck, P.M.; Yu, E.T.; Lau, S.S.; Sullivan, G.J.; van Hove, J.; Redwing, J. Piezoelectric charge densities in AlGaN/GaN HFETs. Electron. Lett. 1997, 33, 1081–1083. [Google Scholar]

- Jarndal, A.H. Large-Signal Modelling of GaN Device for High Power Amplifier Design. Ph.D. Dissertation, Universoty of Kassel, Hesse, Germany, 2006. [Google Scholar]

- Ibbetson, J.P.; Fini, P.T.; Ness, K.D.; DenBaars, S.P.; Speck, J.S.; Mishra, U.K. Polarization effects, surface states, and the source of electrons in AlGaN/GaN heterostructure field effect transistors. Appl. Phys. Lett. 2000, 77, 250–252. [Google Scholar] [CrossRef]

- Vetury, R.; Zhang, N.Q.; Keller, S.; Mishra, U.K. The impact of surface states on the DC and RF characteristics of AlGaN/GaN HFETs. IEEE Trans. Electron Devices 2001, 48, 560–566. [Google Scholar] [CrossRef]

- Kim, H.; Thompson, R.; Tilak, V.; Prunty, T.R.; Shealy, J.R.; Eastman, L.F. Effects of SiN passivation and high-electric field on AlGaN-GaN HFET degradation. IEEE Electron Dev. Lett. 2003, 24, 2002–2004. [Google Scholar]

- Gregušová, D.; Stoklas, R.; Mizue, C.H.; Hori, Y.; Novák, J.; Hashizume, T.; Kordoš, P. Trap states in AlGaN/GaN metal-oxide-semiconductor structures with Al2O3 prepared by atomic layer deposition. J. Appl. Phys. 2010, 107, 106104:1–106104:3. [Google Scholar] [CrossRef]

- Liu, C.; Chor, E.F.; Tan, L.S. Enhanced device performance of AlGaN/GaN HEMTs using HfO2 high-k dielectric for surface passivation and gate oxide. Semicond. Sci. Technol. 2007, 22, 522–527. [Google Scholar] [CrossRef]

- Niiyama, Y.; Shinagawa, T.; Ootomo, S.; Kambayashi, H.; Nomura, T.; Kato, S. High-power operation of normally-off GaN MOSFETs. Furukawa Rev. 2009, 36, 1–5. [Google Scholar]

- Chung, J.W.; Roberts, J.C.; Piner, E.L.; Palacios, T. Effect of gate leakage in the subthreshold characteristics of AlGaN/GaN HEMTs. IEEE Electron Dev. Lett. 2008, 29, 1196–1198. [Google Scholar] [CrossRef]

- Ye, P.D.; Yang, B.; Ng, K.K.; Bude, J.; Wilk, G.D.; Halder, S.; Hwang, J.C.M. GaN metal-oxide-semiconductor high-electron-mobility-transistor with atomic layer deposited Al2O3 as gate dielectric. Appl. Phys. Lett. 2005, 86, 063501:1–063501:3. [Google Scholar]

- Bi, Z.; Hao, Y.; Liu, H.; Liu, L.; Feng, Q. Characteristics analysis of gate dielectrics in AlGaN/GaN MIS-HEMT. In Proceedings of IEEE International Conference of Electron Devices and Solid-State Circuits EDSSC, Xian, China, 25–27 December 2009.

- Wu, Y.Q.; Ye, P.D.; Wilk, G.D.; Yang, B. GaN metal-oxide-semiconductor field-effect-transistor with atomic layer deposited Al2O3 as gate dielectric. Mater. Sci. Eng. B 2006, 135, 282–284. [Google Scholar]

- Matocha, K.; Chow, T.P.; Gutmann, R.J. High-voltage normally off GaN MOSFETs on sapphire substrates. IEEE Trans. Electron Devices 2005, 52, 6–10. [Google Scholar] [CrossRef]

- Chang, Y.C.; Chang, W.H.; Chang, Y.H.; Kwo, J.; Lin, Y.S.; Shu, S.H.; Hong, J.M.; Tsai, C.C.; Hong, M. Drain current enhancement and negligible current collapse in GaN MOSFETs with atomic-layer-deposited HfO2 as a gate dielectric. Microelectron. Eng. 2010, 87, 2042–2045. [Google Scholar] [CrossRef]

- International Technology Roadmap for Semiconductors. Available online: http://public.itrs.net/ (accessed on 19 July 2012).

- Xue, Q.K.; Xue, Q.Z.; Bakhtizin, R.Z.; Hasegawa, Y.; Tsong, I.S.T.; Sakurai, T. Structures of GaN(0001)-(2 × 2), -(4 × 4), and -(5 × 5) surface reconstructions. Phys. Rev. Lett. 1999, 82, 3074–3077. [Google Scholar] [CrossRef]

- Morkoç, H. Handbook of Nitride Semiconductors and Devices: GaN-Based Optical and Electronic Devicesitle; Wiley-VCH: Weinheim, Germany, 2009. [Google Scholar]

- Tsai, M.H.; Sankey, O.F.; Schmidt, K.E.; Tsong, I.S.T. Electronic structures of polar and nonpolar GaN surfaces. Mater. Sci. 2002, 88, 40–46. [Google Scholar]

- Kočan, M.; Rizzi, A.; Luth, H.; Keller, S.; Mishra, U.K. Surface potential at as-grown GaN (0001) MBE layers. Phys. Status Solidi 2002, 234, 773–777. [Google Scholar] [CrossRef]

- Koblmüller, G.; Reurings, F.; Tuomisto, F.; Speck, J. Influence of Ga/N ratio on morphology, vacancies, and electrical transport in GaN grown by molecular beam epitaxy at high temperature. Appl. Phys. Lett. 2010, 97, 191915:1–191915:3. [Google Scholar] [CrossRef]

- Wu, J.; Zhao, L.; Wen, D.; Xu, K.; Yang, Z.; Zhang, G.; Li, H.; Zuo, R. New design of nozzle structures and its effect on the surface and crystal qualities of thick GaN using a horizontal HVPE reactor. Appl. Surf. Sci. 2009, 255, 5926–5931. [Google Scholar] [CrossRef]

- Caban, P.; Strupinski, K.W.; Wojcik, M.; Gaca, J.; Szmidt, J.; Ozturk, M.; Ozbay, E. The influence of substrate surface preparation on LP MOVPE GaN epitaxy on differently oriented 4H-SiC substrates. J. Cryst. Growth 2008, 310, 4876–4879. [Google Scholar] [CrossRef] [Green Version]

- Liu, G.R.; Li, X.Y. Some methods to make high quality GaN film by MOCVD. In Proceedins of Advances in Optoelectronics and Micro/Nano-Optics (AOM), 2010 OSA-IEEE-COS, Guang Zhou, China, 3–6 December 2010.

- Lada, M.; Cullis, A.G.; Parbrook, P.J. Effect of anneal temperature on GaN nucleation layer transformation. J. Cryst. Growth 2003, 258, 89–99. [Google Scholar] [CrossRef]

- Hasegawa, H.; Akazawa, M. Current transport, Fermi level pinning, and transient behavior of group-III nitride schottky barriers. J. Korean Phys. Soc. 2009, 55, 1167–1179. [Google Scholar] [CrossRef]

- Matolin, V.; Fabik, S.; Glosik, J.; Bideux, L.; Ould-Metidji, Y.; Gruzza, B. Experimental system for GaN thin films growth and in situ characterisation by electron spectroscopic methods. Vacuum 2004, 76, 471–476. [Google Scholar]

- Rapcewicz, K.; Nardelli, M.B.; Bernholc, J. Theory of surface morphology of wurtzite GaN(0001) surfaces. Phys. Rev. B 1997, 56, 12725–12728. [Google Scholar] [CrossRef]

- Bruno, G.; Losurdo, M.; Kim, T.H.; Brown, A. Adsorption and desorption kinetics of Ga on GaN(0001): Application of wolkenstein theory. Phys. Rev. B 2010, 82, 075326:1–075326:7. [Google Scholar] [CrossRef]

- Liu, X.Y.; Andersson, T.G. Surface roughness of GaN and thin AlGaN layers grown by molecular beam epitaxy. Appl. Surf. Sci. 2004, 226, 331–334. [Google Scholar] [CrossRef]

- Zheng, L.X.; Xie, M.H.; Seutter, S.M.; Cheung, S.H.; Tong, S.Y. Observation of “ghost” islands and surfactant effect of surface gallium atoms during gan growth by molecular beam epitaxy. Phys. Rev. Lett. 2000, 85, 2352–2355. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Xie, M.H.; Gong, M.; Pang, E.K.Y.; Wu, H.S.; Tong, S.Y. Origin of triangular island shape and double-step bunching during GaN growth by molecular-beam epitaxy under excess Ga conditions. Phys. Rev. B 2006, 74, 085314:1–085314:6. [Google Scholar]

- Takeuchi, N.; Selloni, A.; Myers, T.H.; Doolittle, A. Adsorption and diffusion of Ga and N adatoms on GaN surfaces: Comparing the effects of Ga coverage and electronic excitation. Phys. Rev. B 2005, 72, 115307:1–115307:5. [Google Scholar] [CrossRef]

- Hsu, J.W.P.; Manfra, M.J.S.; Chu, N.G.; Chen, C.H.; Pfeiffer, L.N.; Molnar, R.J. Effect of growth stoichiometry on the electrical activity of screw dislocations in GaN films grown by molecular-beam epitaxy. Appl. Phys. Lett. 2001, 78, 3980:1–3908:3. [Google Scholar]

- Moram, M.A.; Ghedia, C.S.; Rao, D.V.S.; Barnard, J.S.; Zhang, Y.; Kappers, M.J.; Humphreys, C.J. On the origin of threading dislocations in GaN films. J. Appl. Phys. 2009, 106, 073513:1–073513:9. [Google Scholar]

- Adelmann, C.; Brault, J.; Mula, G.; Daudin, B. Gallium adsorption on (0001) GaN surfaces. Phys. Rev. B 2003, 67, 165419:1–165419:9. [Google Scholar] [CrossRef]

- Wolkenstein, T.; Peshev, O. The electron factor in the kinetics of chemisorption on semiconductors. J. Catal. 1965, 4, 301–309. [Google Scholar] [CrossRef]

- Manske, W.T.; Ratkovich, A.S.; Lemke, C.J.; Mcellistrem, M.T. Morphology of GaN(0001) and GaN(0001) persistence of surface clusters. J. Vac. Sci. Technol. A 2003, 21, 506–514. [Google Scholar] [CrossRef]

- Rosa, A.; Neugebauer, J. Understanding Si adsorption on GaN(0001) surfaces using first-principles calculations. Phys. Rev. B 2006, 73, 205314:1–205314:12. [Google Scholar]

- Cremades, A.; Görgens, L.; Ambacher, O.; Stutzmann, M.; Scholz, F. Structural and optical properties of Si-doped GaN. Phys. Rev. B 2000, 61, 2812–2818. [Google Scholar] [CrossRef]

- Bermudez, V.; Koleske, D.; Wickenden, A. The dependence of the structure and electronic properties of wurtzite GaN surfaces on the method of preparation. Appl. Surf. Sci. 1998, 126, 69–82. [Google Scholar] [CrossRef]

- Tsuruoka, T.; Kawasaki, M.; Ushioda, S.; Franchy, R.; Naoi, Y.; Sugahara, T.; Sakai, S.; Shintani, Y. Combined HREELS/LEED study on the oxidation of GaN surfaces. Surf. Sci. 1999, 428, 257–261. [Google Scholar] [CrossRef]

- Chua, S.J.; Choi, H.W.; Zhang, J.; Li, P. Vacancy effects on plasma-induced damage to n-type GaN. Phys. Rev. B 2001, 64, 205302:1–205302:5. [Google Scholar] [CrossRef]

- Nouet, G.; Ruterana, P.; Chen, J.; Lei, B.; Ye, H.; Yu, G.; Qi, M.; Li, A. Characterization of thick HVPE GaN films. Superlattice Microstruct. 2004, 36, 417–424. [Google Scholar] [CrossRef]

- Li, X.; Yu, T.; Tao, Y.; Deng, J.; Xu, C.; Zhang, G. Epitaxial lateral overgrowth of InGaN/GaN multiple quantum wells on HVPE GaN template. Phys. Status Solid C 2011, 9, 445–448. [Google Scholar] [CrossRef]

- Danielsson, E.; Zetterling, C.M.; Östling, M.; Nikolaev, A.; Nikitina, I.P.; Dmitriev, V. Fabrication and characterization of heterojunction diodes with HVPE-grown GaN on 4H-SiC. IEEE Trans. Electron Devices 2001, 48, 444–449. [Google Scholar] [CrossRef]

- Hattori, A.N.; Endo, K.; Hattori, K.; Daimon, H. Applied surface science surface treatments toward obtaining clean GaN(0001) from commercial hydride vapor phase epitaxy and metal-organic chemical vapor deposition substrates in ultrahigh vacuum. Appl. Surf. Sci. 2010, 256, 4745–4756. [Google Scholar] [CrossRef]

- Smith, A.R.; Feenstra, R.M.; Greve, D.W.; Neugebauer, J.; Northrup, J.E. Reconstructions of the GaN(0001) Surface. Phys. Rev. Lett. 1997, 79, 3934–3937. [Google Scholar] [CrossRef]

- Smith, A.; Ramachandran, V.; Feenstra, R.; Greve, D.W.; Shin, M.S.; Skowronski, M.; Neugebauer, J.; Northrup, J.E. Wurtzite GaN surface structures studied by scanning tunneling microscopy and reflection high energy electron diffraction. J. Vac. Sci. Technol. A 1998, 16, 1641–1645. [Google Scholar] [CrossRef]

- Oliver, R.A.; Nörenberg, C.; Martin, M.G.; Crossley, A.; Castell, M.R.; Briggs, G.A.D. Gallium nitride surface preparation optimised using in situ scanning tunnelling microscopy. Appl. Surf. Sci. 2003, 214, 1–10. [Google Scholar] [CrossRef]

- Smith, A.R.; Feenstra, R.M.; Greve, D.W.; Shin, M.S.; Skowronski, M.; Neugebauer, J.; Northrup, J.E. GaN(0001) surface structures studied using scanning tunneling microscopy and first-principles total energy calculations. Surf. Sci. 1999, 423, 70–84. [Google Scholar] [CrossRef]

- Christou, A.; Fantini, F. Introduction to the special issue on GaN and related nitride compound device reliability. IEEE Trans. Device Mater. Relia. 2008, 8, 239–239. [Google Scholar] [CrossRef]

- Van de Walle, C.G.; Janotti, A. Advances in electronic structure methods for defects and impurities in solids. Phys. Status Solidi B 2011, 248, 19–27. [Google Scholar] [CrossRef]

- Wang, F.H.; Kruger, P.; Pollmann, J. Electronic structure of 1 × 1 GaN(0001) and GaN(0001) surfaces. Phys. Rev. 2011, 64, 035305:1–035305:8. [Google Scholar]

- Van de Walle, C.G.; Segev, D. Microscopic origins of surface states on nitride surfaces microscopic origins of surface states on nitride surfaces. J. Appl. Phys. 2005, 101, 081704:1–081704:6. [Google Scholar]

- Reshchikov, M.A.; Morkoç, H. Luminescence properties of defects in GaN. J. Appl. Phys. 2005, 97, 061301:1–061305:95. [Google Scholar] [CrossRef]

- Petravic, M.; Coleman, V.A.; Kim, K.J.; Kim, B.; Li, G. Defect acceptor and donor in ion-bombarded GaN. J. Vac. Sci. Technol. A 2005, 23, 1340–1345. [Google Scholar] [CrossRef]

- Arehart, A.R.; Corrion, A.; Poblenz, C.; Speck, J.S.; Mishra, U.K.; Ringel, S.A. Deep level optical and thermal spectroscopy of traps in n-GaN grown by ammonia molecular beam epitaxy. Appl. Phys. Lett. 2008, 93, 112101:1–112101:3. [Google Scholar] [CrossRef]

- Armstrong, A.; Arehart, A.R.; Moran, B.; DenBaars, S.P.; Mishra, U.K.; Speck, J.S.; Ringel, S.A. Impact of carbon on trap states in n-type GaN grown by metalorganic chemical vapor deposition. Appl. Phys. Lett. 2004, 84, 374–376. [Google Scholar] [CrossRef]

- Segev, D.; van de Walle, C.G. Origins of Fermi-level pinning on GaN and InN polar and nonpolar surfaces. Europhys. Lett. 2006, 76. [Google Scholar] [CrossRef]

- Plucinski, L.; Colakerol, L.; Bernardis, S.; Zhang, Y.; Wang, S.; O’Donnell, C.; Smith, K.E.; Friel, I.; Moustakas, T.D. Photoemission study of sulfur and oxygen adsorption on GaN(0001). Surf. Sci. 2006, 600, 116–123. [Google Scholar] [CrossRef]

- Cao, X.A.; Pearton, S.J.; Dang, G.; Zhang, A.; Ren, F.; van Hove, J.M. Effects of interfacial oxides on schottky barrier contacts to n- and p-type GaN. Appl. Phys. Lett. 1999, 75, 4130–4132. [Google Scholar] [CrossRef]

- Hashizume, T.; Nakasaki, R.; Ootomo, S.; Oyama, S.; Hasegawa, H. Surface characterization of GaN and AlGaN layers grown by MOVPE. Mater. Sci. Eng. B 2001, 80, 309–312. [Google Scholar] [CrossRef]

- Edwards, N.V.; Bremser, M.D.; Weeks, T.W.; Kern, R.S.; Davies, R.F.; Aspnes, D.S. Real-time assessment of overlayer removal on GaN, AlN, and AlGaN surfaces using spectroscopic ellipsometry. Appl. Phys. Lett. 1996, 69, 2065–2067. [Google Scholar] [CrossRef]

- King, S.; Barnak, J.P.; Bremser, M.D.; Tracy, K.M.; Ronning, C.; Davis, R.F.; Nemanich, R.J. Cleaning of AlN and GaN surfaces. J. Appl. Phys. 1998, 84, 5248–5260. [Google Scholar] [CrossRef]

- Sivasubramani, P.; Park, T.J.; Coss, B.E.; Lucero, A.; Huang, J.; Brennan, B.; Cao, Y.; Jena, D.; Xing, H.; Wallace, R.M.; Kim, J. In situ X-ray photoelectron spectroscopy of trimethyl aluminum and water half-cycle treatments on HF-treated and O3-oxidized GaN substrates. Phys. Status Solidi Rapid Res. Lett. 2011, 6, 22–24. [Google Scholar] [CrossRef]

- Diale, M.; Auret, F.; van der Berg, N.; Odendaal, R.; Roos, W. Analysis of GaN cleaning procedures. Appl. Surf. Sci. 2005, 246, 279–289. [Google Scholar] [CrossRef]

- Martinez, G.L.; Curiel, M.R.; Skromme, B.J.; Molnar, R.J. Surface recombination and sulfide passivation of GaN. J. Electron. Mater. 2000, 29, 325–331. [Google Scholar] [CrossRef]

- Maffeis, T.G.G.; Simmonds, M.C.; Clark, S.A.; Peiro, F.; Haines, P.; Parbrook, P.J. Influence of premetallization surface treatment on the formation of Schottky Au-nGaN contacts. J. Appl. Phys. 2002, 92, 3179:1–3179:8. [Google Scholar] [CrossRef]

- Lee, K.; Donovan, S.M.; Gila, B.; Overberg, M.; Mackenzie, J.D.; Abernathy, C.R.; Wilson, R.G. Surface chemical treatment for the cleaning of AlN and GaN surfaces. J. Electrochem. Soc. 2000, 147, 3087–3090. [Google Scholar] [CrossRef]

- Hattori, A.; Kawamura, F.; Yoshimura, M.; Kitaoka, Y.; Mori, Y.; Hattori, K.; Daimon, H.; Endo, K. Chemical etchant dependence of surface structure and morphology on GaN (0001) substrates. Surf. Sci. 2010, 604, 1247–1253. [Google Scholar] [CrossRef]

- Zhou, J.; Reddic, J.; Sinha, M.; Ricker, W.; Karlinsey, J.; Yang, J.W.; Khan, M.A.; Chen, D.A. Surface morphologies of MOCVD-grown GaN films on sapphire studied by scanning tunneling microscopy. Appl. Surf. Sci. 2002, 202, 131–138. [Google Scholar] [CrossRef]

- Tracy, K.; Mecouch, W.; Davis, R.; Nemanich, R.J. Preparation and characterization of atomically clean, stoichiometric surfaces of n-and p-type GaN(0001). J. Appl. Phys. 2003, 94, 3163:1–3163:10. [Google Scholar]

- Grabow, L.C.; Uhlrich, J.J.; Kuech, T.F.; Mavrikakis, M. Surface Science Effectiveness of in situ NH3 annealing treatments for the removal of oxygen from GaN surfaces. Appl. Surf. Sci. 2009, 603, 387–399. [Google Scholar] [CrossRef]

- Koyama, Y.; Hashizume, T.; Hasegawa, H. Formation processes and properties of Schottky and Ohmic ontacts on n-type GaN for field effect transistor applications. Solid State Electron. 1999, 43, 1483–1488. [Google Scholar] [CrossRef]

- Benbakhti, B.; Ayubi-Moak, J.S.; Kalna, K.; Lin, D.; Hellings, G.; Brammertz, G.; de Meyerb, K.; Thayne, I.; Asenov, A. Impact of interface state trap density on the performance characteristics of different III–V MOSFET architectures. Microelectron. Rel. 2010, 50, 360–364. [Google Scholar] [CrossRef]

- Nicollian, E.H.; Brews, J.R. MOS Physics and Technology; Wiley: Hoboken, NJ, USA, 2003. [Google Scholar]

- Swenson, B.L.; Mishra, U.K. Photoassisted high-frequency capacitance-voltage characterization of the Si3N4/GaN interface. J. Appl. Phys. 2009, 106, 064902:1–064902:5. [Google Scholar] [CrossRef]

- Placidi, M.; Constant, A.; Fontserè, A.; Pausas, E.; Cortes, I.; Cordier, Y.; Mestres, N.; Pérez, R.; Zabala, M.; Millán, J.; Godignon, P.; Pérez-Tomás, A. Deposited thin SiO2 for gate oxide on n-type and p-type GaN. J. Electrochem. Soc. 2010, 157, H1008–H1013. [Google Scholar] [CrossRef]

- Alam, E.A.; Cortés, I.; Besland, M.P.; Regreny, P.; Goullet, A.; Morancho, F.; Cazarré, A.; Cordier, Y.; Isoird, K.; Olivié, F. Comparison of GaN-based MOS structures with different interfacial layer treatments. In Proceedings of the 2010 27th International Conference on Microelectronics, Nis, Serbia, 16–19 May 2010.

- Matocha, K.; Tilak, V.; Dunne, G. Comparison of metal-oxide-semiconductor capacitors on c- and m-plane gallium nitride. Appl. Phys. Lett. 2007, 90, 123511:1–123511:2. [Google Scholar] [CrossRef]

- Chang, Y.C.; Huang, M.L.; Chang, Y.H.; Lee, Y.J.; Chiu, H.C.; Kwo, J.; Hong, M. Atomic-layer-deposited Al2O3 and HfO2 on GaN: A comparative study on interfaces and electrical characteristics. Microelectron. Eng. 2011, 88, 1207–1210. [Google Scholar] [CrossRef]

- Gray, P.V.; Brown, D.M. Density of SiO2/Si Interface States. Appl. Phys. Lett. 1966, 8, 31–33. [Google Scholar] [CrossRef]

- Matocha, K.; Gutmann, R.J.; Chow, T.P. Effect of annealing on GaN-insulator interfaces characterized by metal-insulator-semiconductor capacitors. IEEE Trans. Electron Devices 2003, 50, 1200–1204. [Google Scholar] [CrossRef]

- Terman, L. An investigation of surface states at a silicon/silicon oxide interface employing metal-oxide-silicon diodes. Solid State Electron. 1962, 5, 285–299. [Google Scholar] [CrossRef]

- Bae, C.; Lucovsky, G. Reductions in interface defects, Dit, by post oxidation plasma-assisted nitridation of GaN-SiO2 interfaces in MOS devices. Appl. Surf. Sci. 2004, 234, 475–479. [Google Scholar] [CrossRef]

- Alam, E.A.; Cortes, I.; Besland, M.P.; Goullet, A.; Lajaunie, L.; Regreny, P.; Cordier, Y.; Brault, J.; Cazarre, A.; Isoird, K.; Sarrabayrouse, G.; Morancho, F. Effect of surface preparation and interfacial layer on the quality of SiO2/GaN interfaces. J. Appl. Phys. 2011, 109, 084511:1–08455:9. [Google Scholar] [CrossRef]

- Wu, Y.Q.; Shen, T.; Ye, P.D.; Wilk, G.D. Photo-assisted capacitance-voltage characterization of high-quality atomic-layer-deposited Al2O3∕GaN metal-oxide-semiconductor structures. Appl. Phys. Lett. 2007, 90, 143504:1–143504:3. [Google Scholar]

- Nakano, Y.; Jimbo, T. Interface properties of SiO2/n-GaN metal-insulator—Semiconductor structures. Appl. Phys. Lett. 2002, 80, 4756:1–4756:3. [Google Scholar] [CrossRef]

- Liu, X.; Chin, H.C.; Tan, L.S.; Yeo, Y.C. In situ surface passivation of gallium nitride for metal-organic chemical vapor deposition of high-permittivity gate dielectric. IEEE Trans. Electron Devices 2011, 58, 95–102. [Google Scholar] [CrossRef]

- Ooyama, K.; Kato, H.; Miczek, M.; Hashizume, T. Temperature-dependent interface-state response in an Al2O3/n-GaN Structure. Jpn. Appl. Phys. 2008, 47, 5426–5428. [Google Scholar] [CrossRef]

- Törndahl, T.; Ottosson, M.; Carlsson, J.O. Growth of copper metal by atomic layer deposition using copper(I) chloride, water and hydrogen as precursors. Thin Solid Films 2004, 458, 129–136. [Google Scholar] [CrossRef]

- Mueller, S.; Waechtler, T.; Hofmann, L.; Tuchscherer, A.; Mothes, R.; Gordan, O.; Lehmann, D.; Haidu, F.; Ogiewa, M.; Gerlich, L.; Ding, S.F.; Schulz, S.E.; Gessner, T.; Lang, H.; Zahn, D.R.T.; Qu, X.P. Thermal ALD of Cu via reduction of CuxO films for the advanced metallization in spintronic and ULSI interconnect systems. In Proceedings of Semiconductor Conference Dresden (SCD), Dresden, Germany, 27–28 September 2011.

- Li, Z.; Rahtu, A.; Gordon, R.G. Atomic layer deposition of ultrathin copper metal films from a liquid copper(i) amidinate precursor. J. Electrochem. Soc. 2006, 153, C787–C794. [Google Scholar] [CrossRef]

- Pérez-Tomás, A.; Placidi, M.; Perpiñà, X.; Constant, A.; Godignon, P.; Jordà, X.; Brosselard, P.; Millán, J. GaN metal-oxide-semiconductor field-effect transistor inversion channel mobility modeling. J. Appl. Phys. 2009, 105, 114510:1–114510:6. [Google Scholar] [CrossRef] [Green Version]

- Cook, T.E.; Fulton, C.C.; Mecouch, W.J.; Davis, R.F.; Lucovsky, G.; Nemanich, R.J. Band offset measurements of the Si3N4/GaN(0001) interface. J. Appl. Phys. 2003, 94, 3949–3954. [Google Scholar] [CrossRef]

- Cook, T.E., Jr.; Fulton, C.C.; Mecouch, W.J.; Tracy, K.M.; Davis, R.F.; Hurt, E.H.; Lucovsky, G.; Nemanich, R.J. Measurement of the band offsets of SiO2 on clean n- and p-type GaN(0001). J. Appl. Phys. 2003, 93, 3995–4004. [Google Scholar] [CrossRef]

- Therrien, R.; Niimi, H.; Gehrke, T.; Lucovsky, G.; Davis, R. Charge redistribution at GaN-Ga2O3 interfaces: A microscopic mechanism for low defect density interfaces in remote plasma processed MOS devices prepared on polar GaN faces. Microelectron. Eng. 1999, 48, 303–306. [Google Scholar] [CrossRef]

- Bae, C.; Lucovsky, G. Low-temperature preparation of GaN-SiO2 interfaces with low defect density. I. Two-step remote plasma-assisted oxidation-deposition process. J. Vac. Sci. Technol. A 2004, 22, 2402–2410. [Google Scholar] [CrossRef]

- Chang, Y.; Lee, Y.J.; Chiu, Y.N.; Lin, T.D.; Wu, S.Y.; Chiu, H.C.; Kwo, J.Y.; Wang, H.; Hong, M. MBE grown high κ dielectrics Ga2O3(Gd2O3) on GaN. J. Crys. Growth 2007, 301, 390–393. [Google Scholar] [CrossRef]

- Lee, M.L.; Mue, T.S.; Sheu, J.K.; Chang, K.H.; Tu, S.J.; Hsueh, T.H. Effect of thermal annealing on the GaN metal-oxide-semiconductor capacitors with gallium oxide gate layer. J. Electrochem. Soc. 2010, 157, H1019–H1022. [Google Scholar] [CrossRef]

- Bae, C.; Krug, C.; Lucovsky, G.; Chakraborty, A.; Mishra, U. Surface passivation of n-GaN by nitrided-thin-Ga2O3∕SiO2 and Si3N4 films. J. Appl. Phys. 2004, 96, 2674–2680. [Google Scholar] [CrossRef]

- Herrero, A.M.; Gila, B.P.; Gerger, A.; Scheuermann, A.; Davies, R.; Abernathy, C.R.; Pearton, S.J.; Ren, F. Environmental stability of candidate dielectrics for GaN-based device applications. J. Appl. Phys. 2009, 106, 074105:1–074105:9. [Google Scholar] [CrossRef]

- Chen, J.J.; Gila, B.P.; Hlad, M.; Gerger, A.; Ren, F.; Abernathy, C.R.; Pearton, S.J. Determination of MgO∕GaN heterojunction band offsets by X-ray photoelectron spectroscopy. Appl. Phys. Lett. 2006, 88, 042113:1–042113:3. [Google Scholar]

- Liu, C.E.; Chor, F.; Tan, L.S.; Dong, Y. Band offset measurements of the pulsed-laser-deposition-grown Sc2O3(111)/GaN(0001) heterostructure by X-ray photoelectron spectroscopy. Phys. Status Solidi C 2007, 4, 2330–2333. [Google Scholar] [CrossRef]

- Chang, Y.C.; Chiu, H.C.; Lee, Y.J.; Huang, M.L.; Lee, K.Y.; Hong, M.; Chiu, Y.N.; Kwo, J.; Wang, Y.H. Structural and electrical characteristics of atomic layer deposited high κ HfO2 on GaN. Appl. Phys. Lett. 2007, 90, 232904:1–232904:3. [Google Scholar]

- Frank, M.M.; Wilk, G.D.; Starodub, D.; Gustafsson, T.; Garfunkel, E.; Chabal, Y.J.; Grazul, J.; Muller, D.A. HFO2 and Al2O3 gate dielectrics on GaAs grown by atomic layer deposition. Appl. Phys. Lett. 2005, 86, 152904:1–152904:3. [Google Scholar] [CrossRef]

- Cook, T.E.; Fulton, C.C.; Mecouch, W.J.; Davis, R.F.; Lucovsky, G.; Nemanich, R.J. Band offset measurements of the GaN(0001)/HfO2 interface. J. Appl. Phys. 2003, 94, 7155:1–7155:4. [Google Scholar]

- Esposto, M.; Krishnamoorthy, S.; Nath, D.N.; Bajaj, S.; Hung, T.H.; Rajan, S. Electrical properties of atomic layer deposited aluminum oxide on gallium nitride. Appl. Phys. Lett. 2011, 99, 133503:1–133503:3. [Google Scholar] [CrossRef]

- Ostermaier, C.; Lee, H.C.; Hyun, S.Y.; Ahn, S.I.; Kim, K.W.; Cho, H.I.; Ha, J.B.; Lee, J.H. Interface characterization of ALD deposited Al2O3 on GaN by CV method. Phys. Status Solidi C 2008, 5, 1992–1994. [Google Scholar] [CrossRef]

- Lee, K.T.; Huang, C.F.; Gong, J.; Liou, B.H. Electrical characteristics of Al2O3/TiO2/Al2O3 nanolaminate MOS capacitor on p-GaN with post metallization annealing and (NH4) 2SX treatments. IEEE Electron. Device Lett. 2009, 30, 907–909. [Google Scholar] [CrossRef]

- Lee, K.T.; Huang, C.F.; Gong, J. High-quality MgO/TiO2/MgO nanolaminates on p-GaNMOS capacitor. IEEE Electron. Device Lett. 2010, 31, 558–560. [Google Scholar] [CrossRef]

- Hossain, T.; Wei, D.; Edgar, J.H. Electrical characteristics of GaN and Si Based metal-oxide-semiconductor (MOS) capacitors. ECS Trans. 2011, 41, 429–437. [Google Scholar]

- Hori, Y.; Mizue, C.; Hashizume, T. Process conditions for improvement of electrical properties of Al2O3/n-GaN structures prepared by atomic layer deposition. Jpn. J. Appl. Phys. 2010, 49, 080201:1–080201:3. [Google Scholar]

- Chiou, Y.L.; Huang, L.H.; Lee, C.T. GaN-based p-type metal-oxide—Semiconductor devices with a gate oxide layer grown by a bias-assisted photoelectrochemical oxidation method. Semicond. Sci. Technol. 2010, 25. [Google Scholar] [CrossRef]

- Chang, Y.C.; Chang, W.H.; Chiu, H.C.; Tung, L.T.; Lee, C.H.; Shiu, K.H.; Hong, M.; Kwo, J.; Hong, J.M.; Tsai, C.C. Inversion-channel GaN metal-oxide-semiconductor field-effect transistor with atomic-layer-deposited Al2O3 as gate dielectric. Appl. Phys. Lett. 2008, 93, 053504:1–053504:3. [Google Scholar]

- Huang, W.; Khan, T.; Paul Chow, T. Comparison of MOS capacitors on n- and p-type GaN. J. Electron. Mater. 2006, 35, 726–732. [Google Scholar] [CrossRef]

- Bae, C.; Rayner, G.B.; Lucovsky, G. Device-quality GaN–dielectric interfaces by 300 °C remote plasma processing. Appl. Surf. Sci. 2003, 216, 119–123. [Google Scholar] [CrossRef]

- Sawada, T.; Ito, Y.; Imai, K.; Suzuki, K.; Tomozawa, H.; Sakai, S. Electrical properties of metal/GaN and SiO2/GaN interfaces and effects of thermal annealing. Appl. Surf. Sci. 2000, 159–160, 449–455. [Google Scholar]

- Nepal, N.; Garces, N.Y.; Meyer, D.J.; Hite, J.K.; Mastro, M.A.; Eddy, C.R., Jr. Assessment of GaN surface pretreatment for atomic layer deposited high-k dielectrics. Appl. Phys. Express 2011, 4, 055802:1–055802:3. [Google Scholar] [CrossRef]

- Sze, S.M.; NG, K.K. Physics of Semicondutor Devices, 3rd ed.; Wiley: Hoboken, NJ, USA, 2007. [Google Scholar]

- Alam, E.A.; Cortes, I.; Besland, M.P.; Goullet, A.; Lajaunie, L.; Regreny, P.; Cordier, Y.; Brault, J.; Cazarre, A.; Isoird, K.; Sarrabayrouse, G.; Morancho, F. Effect of surface preparation and interfacial layer on the quality of SiO2/GaN interfaces. J. Appl. Phys. 2011, 109, 084511:1–084511:9. [Google Scholar]

- Kim, E.J.; Wang, L.P.; Asbeck, M.; Saraswat, K.C.; McIntyre, P.C. Border traps in Al2O3/In0.53Ga0.47 As (100) gate stacks and their passivation by hydrogen anneals. Appl. Phys. Lett. 2010, 96, 012906:1–012906:3. [Google Scholar]

- Fleetwood, D.M. Fast and slow border traps in MOS devices. IEEE Trans. Nucl. Sci. 1996, 43, 779–786. [Google Scholar] [CrossRef]

- Bhat, N.; Saraswat, K.C. Characterization of border trap generation in rapid thermally annealed oxides deposited using silane chemistry. J. Appl. Phys. 1998, 84, 2722:1–2722:5. [Google Scholar] [CrossRef]

- Mehta, R. Gallium nitride alternative to silicon for more powerful electronics. Mater. World 2008, 16, 4–7. [Google Scholar]

- Gusev, E.P.; Narayanan, V.; Frank, M.M. Advanced high-κ dielectric stacks with polySi and metal gates: Recent progress and current challenges. IBM J. Res. 2006, 50, 387–410. [Google Scholar] [CrossRef]

- Kaushik, V.; O’Sullivan, B.; Pourtois, G.; van Hoornick, N.A.; Delabie, S.; van Elshocht, W.; Deweerd, T.; Schram, L.; Pantisano, E.; Rohr, L.A.; de Gendt, S.; Heyns, M. Estimation of fixed charge densities in hafnium-silicate gate dielectrics. IEEE Trans. Electron Devices 2006, 53, 2627–2633. [Google Scholar] [CrossRef]

- Park, H.; Hasan, M.; Jo, M.; Hwang, H. Metal gate and high-k gate dielectrics for sub 50 nm high performance MOSFETs. Electron. Mater. Sci. 2007, 3, 75–85. [Google Scholar]

- Lin, C.W.; Yang, C.W.; Chen, C.-H.; Lin, C.K.; Chiu, H.C. Device performance of AlGaN/GaN MOS-HEMTs using La2O3 high-k oxide gate insulator. In Proceedings of Solid State Device Research Conference ESSDERC 09 of the European, Athens, Greece, 14–18 September 2009.

- Chiu, H.C.; Yang, C.W.; Lin, Y.H.; Lin, R.M.; Chang, L.B.; Horng, K.Y. Device characteristics of AlGaN/GaN MOS-HEMTs using high-k praseodymium oxide layer. IEEE Trans. Electron. Devices 2008, 55, 3305–3309. [Google Scholar] [CrossRef]

- Saadat, O.I.; Chung, J.W.; Piner, E.L.; Palacios, T. Gate-first AlGaN/GaN HEMT technology for high-frequency applications. IEEE Electron. Device Lett. 2009, 30, 1254–1256. [Google Scholar] [CrossRef]

- Dora, Y.; Han, S.; Klenov, D.; Hansen, P.J.; No, K.; Mishra, U.K.; Stemmer, S.; Speck, J.S. ZrO2 gate dielectrics produced by ultraviolet ozone oxidation for GaN and AlGaN/GaN transistors. J. Vac. Sci. Technol. B 2006, 24, 575–581. [Google Scholar] [CrossRef]

- Chen, C.; Liu, X.; Tian, B.; Shu, P.; Chen, Y.; Zhang, W.; Jiang, H.; Li, Y. Fabrication of enhancement-mode AlGaN/GaN MISHEMTs by using fluorinated Al2O3 as gate dielectrics. IEEE Electron. Device Lett. 2011, 32, 1373–1375. [Google Scholar] [CrossRef]

- Tian, F.; Chor, E.F. Impact of Al2O3 incorporation on device performance of HfO2 gate dielectric AlGaN/GaN MIS-HFETs. Phys. Status Solidi C 2010, 7, 1941–1943. [Google Scholar] [CrossRef]

- Park, K.Y.; Cho, H.I.; Lee, J.H.; Bae, S.B.; Jeon, C.M.; Lee, J.L.; Kim, D.Y.; Lee, C.S.; Lee, J.H. Fabrication of AlGaN/GaN MIS-HFET using an Al2O3 highk dielectric. Phys. Status Solidi C 2003, 2354, 2351–2354. [Google Scholar] [CrossRef]

- Yue, Y.; Hao, Y.; Zhang, J.; Ni, J.; Mao, W.; Feng, Q.; Liu, L. AlGaN/GaN MOS-HEMT With HfO2 Dielectric and Al2O3 interfacial passivation layer grown by atomic layer deposition. IEEE Electron. Device Lett. 2008, 29, 838–840. [Google Scholar] [CrossRef]

- Hashizume, T.; Anantathanasarn, S.; Negoro, N.; Sano, E.; Hasegawa, H.; Kumakura, K.; Makimoto, T. Al2O3 insulated-gate structure for AlGaN/GaN heterostructure field effect transistors having thin AlGaN barrier layers. Jpn. J. Appl. Phys. 2004, 43, L777–L779. [Google Scholar] [CrossRef]

- Shimizua, S.Y.M.; Okumuraa, H.; Ohashia, H.; Araia, K.; Yanob, Y.; Akutsub, N. 1.8 kV AlGaN/GaN HEMTs with high-k/Oxide/SiN MIS structure. In Proceedings of the 19th International Symposium on Power Semiconductor Devices & ICs, Jeju, Korea, May 27–30, 2007.

© 2012 by the authors; licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution license (http://creativecommons.org/licenses/by/3.0/).

Share and Cite

Long, R.D.; McIntyre, P.C. Surface Preparation and Deposited Gate Oxides for Gallium Nitride Based Metal Oxide Semiconductor Devices. Materials 2012, 5, 1297-1335. https://doi.org/10.3390/ma5071297

Long RD, McIntyre PC. Surface Preparation and Deposited Gate Oxides for Gallium Nitride Based Metal Oxide Semiconductor Devices. Materials. 2012; 5(7):1297-1335. https://doi.org/10.3390/ma5071297

Chicago/Turabian StyleLong, Rathnait D., and Paul C. McIntyre. 2012. "Surface Preparation and Deposited Gate Oxides for Gallium Nitride Based Metal Oxide Semiconductor Devices" Materials 5, no. 7: 1297-1335. https://doi.org/10.3390/ma5071297