OPEN ACCESS materials ISSN 1996-1944 www.mdpi.com/journal/materials

Article

# A Self-Aligned a-IGZO Thin-Film Transistor Using a New Two-Photo-Mask Process with a Continuous Etching Scheme

Ching-Lin Fan <sup>1,2,\*</sup>, Ming-Chi Shang <sup>1</sup>, Bo-Jyun Li <sup>1</sup>, Yu-Zuo Lin <sup>2</sup>, Shea-Jue Wang <sup>3</sup> and Win-Der Lee <sup>4</sup>

- <sup>1</sup> Graduate Institute of Electro-Optical Engineering, National Taiwan University of Science and Technology, Taipei City 106, Taiwan; E-Mails: d10019004@mail.ntust.edu.tw (M.-C.S.); m10019004@mail.ntust.edu.tw (B.-J.L.)

- <sup>2</sup> Department of Electronic Engineering, National Taiwan University of Science and Technology, Taipei City 106, Taiwan; E-Mail: D9802312@mail.ntust.edu.tw

- <sup>3</sup> Institute of Materials Science and Engineering, National Taipei University of Technology, Taipei City 106, Taiwan; E-Mail: sjwang@ntut.edu.tw

- <sup>4</sup> Department of Electrical Engineering, Lee-Ming Institute of Technology, New Taipei City 243, Taiwan; E-Mail: leewd@mail.lit.edu.tw

- \* Author to whom correspondence should be addressed; E-Mail: clfan@mail.ntust.edu.tw; Tel.: +886-2-2737-6374; Fax: +886-2-2737-6424.

Received: 26 June 2014; in revised form: 24 July 2014 / Accepted: 30 July 2014 / Published: 11 August 2014

**Abstract:** Minimizing the parasitic capacitance and the number of photo-masks can improve operational speed and reduce fabrication costs. Therefore, in this study, a new two-photo-mask process is proposed that exhibits a self-aligned structure without an etching-stop layer. Combining the backside-ultraviolet (BUV) exposure and backside-lift-off (BLO) schemes can not only prevent the damage when etching the source/drain (S/D) electrodes but also reduce the number of photo-masks required during fabrication and minimize the parasitic capacitance with the decreasing of gate overlap length at same time. Compared with traditional fabrication processes, the proposed process yields that thin-film transistors (TFTs) exhibit comparable field-effect mobility (9.5 cm<sup>2</sup>/V·s), threshold voltage (3.39 V), and subthreshold swing (0.3 V/decade). The delay time of an inverter fabricated using the proposed process was considerably decreased.

**Keywords:** amorphous indium–gallium–zinc–oxide (a-IGZO); back-side exposure; self-aligned process; thin-film transistor (TFT); two-photo-mask process; backside-lift-off (BLO)

#### 1. Introduction

Numerous recent studies have focused on oxide semiconductors, such as amorphous indium–gallium–zinc oxide (a-IGZO). Because of their high mobility and transparency, these semiconductors have been applied as active channel layers in thin-film transistors (TFTs) [1–3]. Regarding traditional silicon-based TFTs, amorphous silicon (a-Si:H) exhibits low carrier mobility (0.5–1 cm<sup>2</sup>/V·s), whereas polycrystalline silicon (poly-Si) requires high-temperature fabrication processes (>500 °C) [4,5]. Conversely, a-IGZO TFTs can be fabricated on plastic substrates at low temperatures and exhibit excellent electrical characteristics [6,7].

The a-IGZO TFTs that are employed in displays are typically fabricated using back-channel-etching structure and five photomasks, including the definition of an etching-stop (ES) layer to protect the a-IGZO active layer from damage caused by etching the source/drain (S/D) electrodes [8]. However, thin-film transistors (TFTs) that involve an ES require a misalignment margin for the ES to ensure the good contact between the S/D and the induced channel; thus, high parasitic capacitances which between the source/drain (S/D) electrodes and gate electrode ( $C_{gd}$ ,  $C_{gs}$ ) could occur, decreasing the operational speed of the TFT circuit [9].

To reduce the parasitic capacitance of TFTs with ES, Geng *et al.* proposed a self-aligned process employing backside-ultraviolet (BUV) exposure through a metal-gate-electrode to define the ES area, thereby reducing the misalignment margin [10]. However, four or five-photo-masks were used during fabrication. To reduce the fabrication costs and prevent hydrogen-based material from affecting the a-IGZO active layer during ES deposition [11], Uhm *et al.* proposed a two-photo-mask scheme that employed a gray-tone photomask to fabricate TFT devices [12]; however, the lack of an ES layer can cause damage to the a-IGZO active island when etching the S/D electrodes. In addition, the ZnO TFT with three photomasks was also proposed [13]. However, the continuous etching of S/D metal, IGZO and gate insulator were not considered in that report. The Table 1 lists the comparisons between these reports and this study.

| Reference | Channel<br>material | Self-aligned | Mask<br>number | S/D Etching<br>damage | a-IGZO Degradation due to<br>ES-layer deposition |

|-----------|---------------------|--------------|----------------|-----------------------|--------------------------------------------------|

| [10]      | IGZO                | Yes          | 4              | No                    | Yes                                              |

| [12]      | IGZO                | No           | 2              | Yes                   | No                                               |

| [13]      | ZnO                 | Yes          | 3              | No                    | No                                               |

| this work | IGZO                | Yes          | 2              | No                    | No                                               |

**Table 1.** Summary of indium–gallium–zinc oxide (IGZO)-based thin-film transistors (TFTs) using different process.

## 2. Device Fabrication

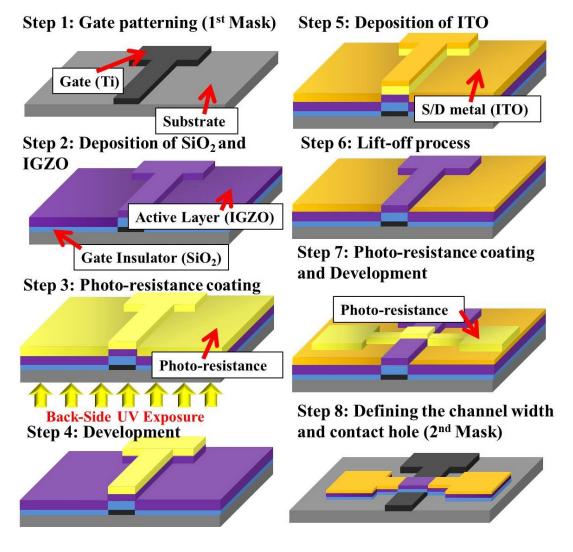

Figure 1 shows the proposed two-mask process for fabricating a-IGZO TFTs. A 160-nm-thick Ti layer was first deposited onto a glass substrate by using thermal evaporation, and then patterned to form the gate electrode by the first photomask. Subsequently, a 200-nm-thick silicon dioxide (SiO<sub>2</sub>) was deposited using plasma enhanced chemical vapor deposition at 300 °C, forming the gate insulator. Subsequently, a 20-nm a-IGZO layer was deposited at 200 °C by a radio frequency (RF) sputtering system using a target of In:Ga:Zn = 1:1:1 in atomic ratio. The backside-lift-off (BLO) process is detailed as follows. First, a photo-resist (PR) was spin-coated onto IGZO and subjected to BUV exposure through the Ti gate as a photomask, as shown in Figure 1. Second, a 350-nm-thick Indium-Tin Oxide (ITO) was deposited using RF sputtering. Subsequently, the BLO scheme was applied to define the channel length of the self-aligned structure. Following the BLO process, the second photomask were used to define the channel width. Reactive-ion etching (RIE) with CF<sub>4</sub> gas was used to continuously etch ITO, IGZO and SiO<sub>2</sub> under the pressure of 80 mtorr. Finally, the devices were annealed at 200 °C for 30 min in a vacuum chamber. To compare the proposed devices, we used a traditional four-photo-mask process to fabricate devices that exhibited various overlap lengths between the gates and S/D electrodes [11].

**Figure 1.** Two-Mask process flow of amorphous indium–gallium–zinc–oxide (a-IGZO) thin-film transistors (TFTs) with self-aligned structure.

#### 3. Results and Discussion

In this study, a new two-photo-mask process with continuous-etching scheme was proposed for fabricating a-IGZO TFTs that exhibit self-aligned structures without ES layers. The ITO metal was designed as S/D metal to meet the requirement of the continuous etching process. Thus, S/D metal, IGZO and gate insulator can simultaneously be etched. Combining the BUV exposure and backside-lift-off (BLO) schemes can not only prevent the damage when etching the S/D electrodes but also reduce the number of photo-masks required during fabrication and minimize the parasitic capacitance at same time.

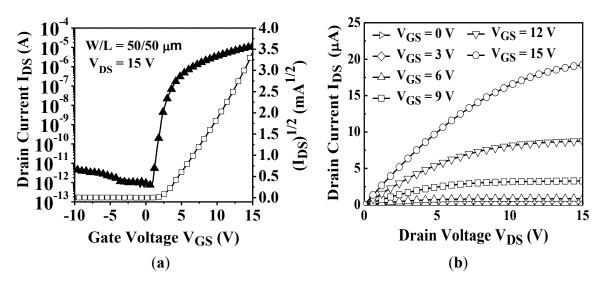

Figure 2a,b shows the transfer and output characteristics of the proposed a-IGZO TFTs with self-aligned structure for channel width (W) of 50  $\mu$ m and channel length (L) of 50  $\mu$ m, respectively. A total of 20 devices were measured at various positions across the substrate by using a semiconductor parameter analyzer (HP4145B Hewlett Packard, Palo Alto, CA, USA). The extracted saturation field-effect mobility ( $\mu_{sat}$ ), threshold voltage ( $V_T$ ), subthreshold swing (S), and on-off current ratio ( $I_{on}/I_{off}$ ) are 9.50 cm<sup>2</sup>/V·s, 3.39 V, 0.3 V/decade, and 4 × 10<sup>7</sup>, respectively.  $\mu_{sat}$  and  $V_T$  are extracted from the slope and linear extrapolations of the plot of the square root of the drain current as a function of the gate voltage, respectively [14–16]. Moreover, the output characteristics show that current crowding did not occur in the linear region to reveal the contact resistance of the S/D regions can satisfy the requirement of transportation current [17].

**Figure 2.** (a) Transfer characteristic ( $V_{DS} = 15$  V) and (b) output characteristic of a-IGZO TFT with self-aligned structure ( $W/L = 50 \ \mu m/50 \ \mu m$ ).

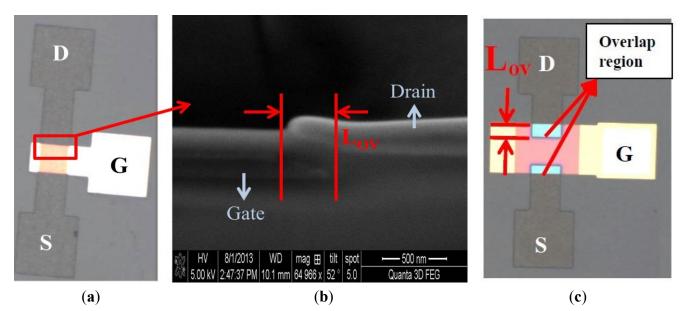

The devices were fabricated using the traditional four-photo-mask process, yielding various overlap lengths ( $L_{ov} = 100$  and 200 µm) between the gate and S/D electrodes. Figure 3 shows optical microscopy images and scanning electron microscopy images of the a-IGZO TFTs, which exhibit self-aligned and overlapping structures. In Figure 3a,b, the overlapping region less than 0.5 µm could be observed in scanning electron microscopy images. The overlapping region was clearly observable among the devices fabricated using the traditional four-photo-mask process in Figure 3c, which yielded parasitic capacitance between S/D and gate electrodes ( $C_{gd}$ ,  $C_{gs}$ ). The parasitic capacitance was proportional to

the area of overlapping region ( $W \times L_{ov}$ ), yielding increased feed-through voltage, noise, and circuit delay in devices typically used in displays applications [12].

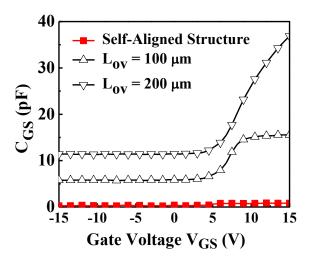

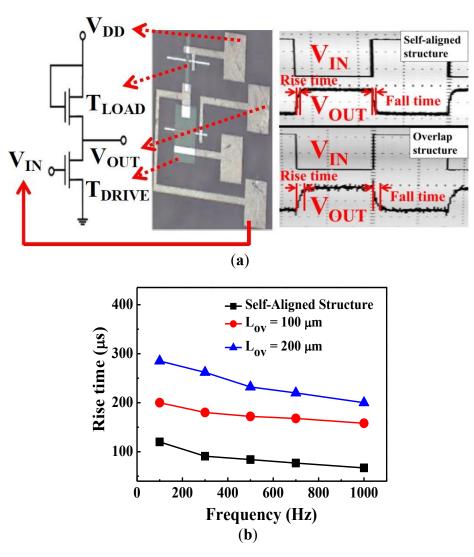

To analyze the parasitic capacitance between the S/D and gate electrodes, the capacitance-voltage of the fabricated a-IGZO TFTs was measured using an Inductance-Resistance-Capacitance (LCR) meter (HP4284A, Hewlett Packard, Palo Alto, CA, USA; Figure 4). The capacitance markedly increased in conjunction with the overlap length  $(L_{ov})$  (*i.e.*, the area of overlapping region). The device that was fabricated using the traditional four-photo-mask process (i.e., Lov of 200 µm) exhibited a minimal capacitance of 11.46 pF, which was considerably higher compared with that of the device fabricated using the proposed method (0.25 pF). Hence, the self-aligned structure reduced the parasitical capacitance between the S/D and gate electrodes. To examine the effects of parasitic capacitance, two types of the inverters were fabricated (Figure 5a); the first comprised the proposed two-mask process with self-aligned structures, and the second comprised overlapping structures (both types employed an N-type metal-oxide-semiconductor configuration as the active load). Figure 5a also shows the dynamic state measurements for the inverters. Various square wave frequencies  $(V_{\rm IN})$  were input into the inverters, and the output signals ( $V_{OUT}$ ) were measured using oscilloscope. The rise time of the output signal was defined as the time required by the signal to rise from 10% to 90% of the step height; this time is related to the parasitic capacitance of TFTs due to the Resistance-Capacitance (RC) delay for inverter circuit operation. Figure 5b indicates that the rise time (delay time) increased in conjunction with the overlap length ( $L_{ov}$ ), (*i.e.*, the parasitic capacitances). Compared with inverter with  $L_{ov}$  of 200  $\mu$ m, the inverter that comprised the proposed two-mask schemes with self-aligned structure exhibited a substantial decrease in delay time from 230 to 78 µs (the input frequency is 500 Hz).

Figure 3. (a) Optical microscopy images of a-IGZO TFTs with self-aligned structures;

(b) Scanning electron microscopy images of a-IGZO TFTs with self-aligned structures;

(c) Optical microscopy images of a-IGZO TFTs with overlap structures.

**Figure 4.** Gate-to-source capacitance ( $C_{gs}$ ) of a-IGZO TFTs with self-aligned structure and overlap structure for different  $L_{ov}$  ( $W = 200 \mu m$ ).

**Figure 5.** (a) Inverter composed of the fabricated a-IGZO TFTs ( $V_{DD} = 20$  V,  $W_{Drive} = 200 \mu m$ ,  $L_{Drive} = 10 \mu m$ ,  $W_{Load} = 40 \mu m$ , and  $L_{Load} = 10 \mu m$ ); (b) The extracted rise time for inverters composed of a-IGZO TFTs with self-aligned structure and overlap structure for  $L_{ov} = 100$  and 200  $\mu m$ .

#### 4. Conclusions

In this study, a novel two-photo-mask process was proposed for fabricating a-IGZO TFTs that exhibit a self-aligned structure. Combining the BUV exposure and BLO schemes reduced both the parasitic capacitance and number of photo-masks required for fabrication. In addition, the proposed devices that lack ES layers yield an undamaged a-IGZO active layer, facilitating superior performance levels (such as a field-effect mobility of  $9.5 \text{ cm}^2/\text{V} \cdot \text{s}$ , a threshold voltage of 3.39 V, and a subthreshold swing of 0.3 V/decade). Compared with using a traditional four-photo-mask process and no ES layer, the proposed process can be used to fabricate a-IGZO TFTs that exhibit fair performance levels. Moreover, the reduced parasitic capacitance yielded a marked decrease in delay time in an inverter fabricated using the proposed method. Thus, the proposed process is a suitable candidate for use in a-IGZO TFT applications, such as active-matrix organic light-emitting diodes (AMOLED), because it achieves high operational speeds and reduces fabrication costs.

### Acknowledgments

The authors would like to acknowledge the financial support of the National Science Council of Taiwan under contract No. NSC 101-2221-E-011-070 and NSC 102-2221-E-011-112-MY2.

### **Author Contributions**

Ching-Lin Fan advised the study and work; Ching-Lin Fan and Bo-Jyun Li designed the research; Bo-Jyun Li and Ming-Chi Shang performed the experimental work; Ming-Chi Shang wrote the manuscript. All authors discussed, edited and approved the final version.

## **Conflicts of Interest**

The authors declare no conflict of interest.

#### References

- Hirao, T.; Furuta, M.; Hiramatsu, T.; Matsuda, T.; Li, C.; Furuta, H.; Hokari, H.; Yoshida, M.; Ishii, H.; Kakegawa, M. Bottom-gate zinc oxide thinfilm transistors (ZnO TFTs) for AM-LCDs. *IEEE Trans. Electron Devices* 2008, 55, 3136–3142.

- 2. Paine, D.; Yaglioglu, B.; Beiley, Z.; Lee, S.H. Amorphous IZO based transparent thin film transistors. *Thin Solid Films* **2008**, *516*, 5894–5898.

- 3. Kumomi, H.; Nomura, K.; Kamiya, T.; Hosono, H. Amorphous oxide channel TFTs. *Thin Solid Films* **2008**, *516*, 1516–1522.

- Ukai, Y. TFT-LCD manufacturing technology—Current status and futureprospect. In Proceedings of International Workshop on Physics of Semiconductor Devices, Mumbai, India, 16–20 December 2007; pp. 29–34.

- 5. Choi, Y.W.; Lee, J.N.; Jang, T.W. Thin-film transistors fabricated with Poly-Si films crystallized at low temperature by microwave annealing. *IEEE Electron Device Lett.* **1999**, *20*, 2–4.

- 6. Nomura, K.; Ohta, H.; Ueda, K.; Kamiya, T.; Hirano, M.; Hosono, H. Thin-film transistor fabricated in single-crystalline transparent oxide emiconductor. *Science* **2003**, *300*, 1269–1272.

- Nomura, K.; Ohta, H.; Takagi, A.; Kamiya, T.; Hirano, M.; Hosono, H. Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductor. *Nature* 2004, 432, 488–492.

- Liu, S.; Yu, M.; Lin, C.; Ho, G.; Cheng, C.; Lai, C.; Lin, C.; King, Y.; Yeh, Y. Influence of passivation layers on characteristics of a-InGaZnO thin-film transistors. *IEEE Electron Device Lett.* 2011, *32*, 161–163.

- Kodkani, R.M.; Larson, L.E. A 25 GHz quadrature voltage controlled ring oscillator in 0.12 μm Si Ge HBT. In Proceedings of the IEEE Topical Meeting on Silicon Monolithic Integrated Circuits in RF Systems, San Diego, CA, USA, 18–20 January 2006; pp. 383–386.

- Geng, D.; Kang, D.H.; Jang, J. High-performance amorphous indium-gallium-zinc-oxide thin-film transistor with a self-aligned etch stopper patterned by back-side UV exposure. *IEEE Electron Device Lett.* 2011, 32, 758–760.

- 11. Park, J.; Kim, S.; Kim, C. High-performance amorphous gallium indium zinc oxide thin-film transistors through N<sub>2</sub>O plasma passivation. *Appl. Phys. Lett.* **2008**, *93*, 053505:1–053505:3.

- 12. Uhm, H.; Lee, S.; Kim, W.; Park, J. A two-mask process for fabrication of bottom-gate IGZO-based TFTs. *IEEE Electron Device Lett.* **2012**, *33*, 543–545.

- 13. Mourey, D.A.; Zhao, D.A.; Jackson, T.N. Self-aligned-gate ZnO TFT circuits. *IEEE Electron Device Lett.* 2010, *31*, 326–328.

- 14. Chen, T.L.; Hsu, T.Y.; Lin, H.Y.; Chou, C.H.; Lin, H.H.; Liu, C.W. Enhanced current drive of double-gate α-IGZO thin-film transistors. *IEEE Electron Device Lett.* **2013**, *34*, 417–419.

- 15. Kamiya, T.; Nomura, K.; Hosono, H. Present status of amorphous In–Ga–Zn–O thin-film transistors. *Sci. Technol. Adv. Mater.* **2010**, *11*, 044305:1–044305:23.

- 16. Seok, M.J.; Choi, M.H.; Mativenga, M.; Kim, D.Y.; Jang, J. A full-swing a-IGZO TFT-based inverter with a Top-Gate-Bias-Induced depletion load. *IEEE Electron Device Lett.* 2011, *32*, 1089–1091.

- Han, D.-S.; Kang, Y.-J.; Park, J.-H.; Jeon, H.-T.; Park, J.-W. Influence of molybdenum source/drain electrode contact resistance in amorphous zinc–tin-oxide (a-ZTO) thin film transistors. *Mater. Res. Bull.* 2014, 2014, doi:10.1016/j.materresbull.2014.05.009.

© 2014 by the authors; licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution license (http://creativecommons.org/licenses/by/3.0/).