Article

# Semi-Automated Extraction of the Distribution of Single Defects for nMOS Transistors

Bernhard Stampfer 1,\* D, Franz Schanovsky 2, Tibor Grasser 1 and Michael Waltl 1 D

- <sup>1</sup> Institute for Microelectronics, Technische Universität Wien, Gusshausstraße 27-29/E360, 1040 Wien, Austria; grasser@iue.tuwien.ac.at (T.G.); waltl@iue.tuwien.ac.at (M.W.)

- Global TCAD Solutions, Bösendorferstraße 1/12, 1010 Wien, Austria; f.schanovsky@globaltcad.com

- \* Correspondence: stampfer@iue.tuwien.ac.at; Tel.: +43-1-58801-36014

Received: 26 March 2020; Accepted: 15 April 2020; Published: 23 April 2020

**Abstract:** Miniaturization of metal-oxide-semiconductor field effect transistors (MOSFETs) is typically beneficial for their operating characteristics, such as switching speed and power consumption, but at the same time miniaturization also leads to increased variability among nominally identical devices. Adverse effects due to oxide traps in particular become a serious issue for device performance and reliability. While the average number of defects per device is lower for scaled devices, the impact of the oxide defects is significantly more pronounced than in large area transistors. This combination enables the investigation of charge transitions of single defects. In this study, we perform random telegraph noise (RTN) measurements on about 300 devices to statistically characterize oxide defects in a Si/SiO<sub>2</sub> technology. To extract the noise parameters from the measurements, we make use of the Canny edge detector. From the data, we obtain distributions of the step heights of defects, i.e., their impact on the threshold voltage of the devices. Detailed measurements of a subset of the defects further allow us to extract their vertical position in the oxide and their trap level using both analytical estimations and full numerical simulations. Contrary to published literature data, we observe a bimodal distribution of step heights, while the extracted distribution of trap levels agrees well with recent studies.

**Keywords:** MOSFET; reliability; random telegraph noise; oxide defects; SiO<sub>2</sub>

## 1. Introduction

The amorphous SiO<sub>2</sub> used as the insulator material in silicon metal-oxide-semiconductor field effect transistors (MOSFETs) contains electrically active defects, often referred to as traps. These traps cause a number of effects detrimental to the operating characteristics and reliability of the devices [1,2]. The most prominent reliability issues in these devices related to charge trapping are the so called bias temperature instabilities (BTI) [3–5] and random telegraph noise (RTN) [6–8]. While BTI can be observed in large-area and nanoscale devices, RTN is mainly studied on scaled technologies.

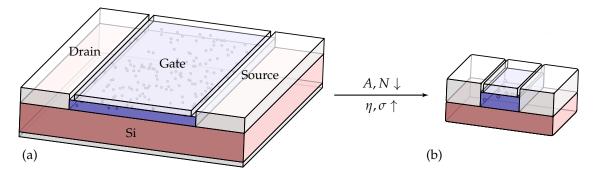

With shrinking of the gate area of a MOSFET, the average number of defects present in the oxide decreases, see Figure 1. The smaller number of defects, however, does not lead to a reduction in threshold voltage shift or noise power, as one might intuitively expect. This is due to the larger influence defects in scaled devices have on the channel [9,10]. Below a certain gate area, single charge transitions can be observed as discrete steps in the drain current, enabling the characterization of RTN. While for large-area and nanoscale devices a similar average degradation of the threshold voltage can be observed, device-to-device variability is seriously affected by device scaling [11,12]. As a consequence, accurate characterization of nanoscale devices requires a higher number of samples than required for large area device studies. For this, we measure RTN on more than 300 scaled devices to evaluate the impact of defects on these devices. We further analyze part of the defects in more detail

Micromachines 2020, 11, 446 2 of 11

using an analytical approximation, to determine their distribution in depth and energy. Finally, we use numerical defect simulation to reproduce some of the defects' charge trapping kinetics and compare the obtained distributions to the distributions from the analytical approximation and literature data.

**Figure 1.** Illustration of oxide defects in (a) large- and (b) small area devices. As the gate area A is reduced, fewer defects N will be present in the device, but on average each defect will have a larger impact  $\eta$  on the overall degradation. This increases variability  $\sigma$  among nominally identical devices, but also allows characterization of single defects using methods such as random telegraph noise (RTN) analysis and time-dependent defect spectroscopy (TDDS).

### 2. Materials and Methods

In the following, the devices used in this work and the measurements carried out are discussed. Afterwards, an efficient method to analyze the recorded data is given. Finally, an analytical approximation for the trap level and the trap position is discussed. Using the proposed methodology the trap bands can be extracted from the measurement data. While the focus of this study is on  $\text{Si/SiO}_2$  devices, the methodology is possible on other technologies, given that small devices are available which are also stable enough to record RTN in a reproducible fashion [13–15].

### 2.1. Devices and Measurements

The devices investigated in this study are planar Si/SiO<sub>2</sub> devices with an effective gate area of  $A \approx 0.15 \, \mu \text{m}^2$ . For all measurements, we use a custom defect probing instrument (DPI) [16] which is configured with three voltage sources for the gate, drain, and bulk terminals of the transistor and a low-noise trans-impedance amplifier with switchable amplification, in combination with a sampling input for measuring drain-source current  $I_{DS}$ , connected to the source of the device. The devices are contacted using a Cascade/FormFactor PA300 semi-automatic wafer prober (FormFactor, Inc., Livermore, CA, USA), which is fully shielded. Electrical connections between the prober and the measurement instrument are made with double shielded TRIAX cables (Keithley Instruments, Solon, OH, USA) to further reduce spurious noise.

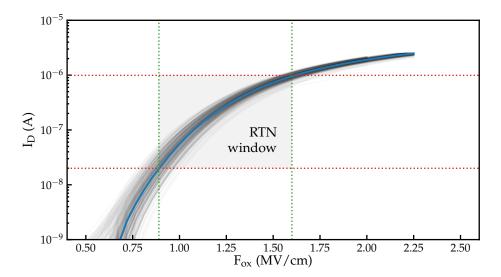

To obtain statistics about the defects active in the devices, automated measurements are performed on around 300 devices. In our measurement scheme, the transfer characteristic is recorded for each device, followed by RTN measurements. The initial  $I_{\rm D}(V_{\rm G})$  curve is used to verify proper operation of the tested device, to determine at which voltages the RTN signals are measured, and to map the recorded  $I_{\rm D}(t)$  RTN data to  $\Delta V_{\rm th}(t)$ . In order to minimize stress to the device prior the RTN measurement, the initial  $I_{\rm D}(V_{\rm G})$  characteristics are recorded within a narrow gate bias window; see Figure 2.

Micromachines 2020, 11, 446 3 of 11

**Figure 2.** Transfer characteristics measured on approximately 300 nominally identical devices, with the average characteristic indicated in blue. The bias range (green) and current range (red) used for RTN measurements in this work is indicated using dotted lines.

The RTN traces are recorded at the gate voltages corresponding to 20, 50, 100, 300, and 1000 nA for each device. These values are selected to achieve maximum current resolution for the measurements ranges available. The drain-source voltage used for both the  $I_D(V_G)$  and RTN measurements is  $-100 \,\mathrm{mV}$ .

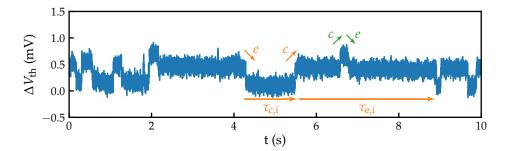

For each gate bias point, one long and five short RTN traces are recorded. The long traces feature a sampling time of  $T_{\rm s}=10\,{\rm ms}$  and a total recording time of  $t_{\rm r}=1\,{\rm ks}$ , while the short traces are sampled with  $T_{\rm s}=100\,{\rm \mu s}$  for  $t_{\rm r}=10\,{\rm s}$ . This allows us to characterize defects with a wider range of transition times, while keeping the number of samples per trace manageable [17]. An example of a fast-sampled RTN trace recorded is shown in Figure 3. The trace was mapped from  $I_{\rm D}(t)$  to  $\Delta V_{\rm th}(t)$ . For this, each  $I_{\rm D}$  value in the trace is replaced with the corresponding  $V_{\rm G}$  from the initial  $I_{\rm D}(V_{\rm G})$ , and finally subtracted from the applied  $V_{\rm G}$  [18].

**Figure 3.** Random telegraph noise traces recorded on a device with  $T_{\rm s}=100\,\mu \rm s$ . Two active defects with similar step heights are clearly visible. The arrows show steps and dwelling times linked to charge capture (c) and charge emission (e) events of the defects.

To characterize individual defects in detail, additional RTN measurements are performed on selected devices, with measurement parameters tailored to the defects under investigation. All measurements are performed at  $30\,^{\circ}\text{C}$  unless indicated otherwise.

# 2.2. Noise Parameter Extraction

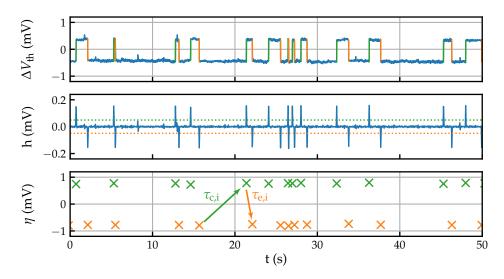

To obtain the average step heights  $\eta$  as well as the charge capture and charge emission times  $\tau_{c,e}$  of the defect signals comprising the recorded traces, a 1D variant of the Canny edge detector [19,20] is first applied on the  $\Delta V_{th}$  data. This method is chosen because (i) there are only few defects per device

Micromachines 2020, 11, 446 4 of 11

on average, (ii) the signal-to-noise ratio is reasonably high, and (iii) the method requires little manual interaction. Other methods which could be used for this step include time-lag methods [21,22] or methods based on hidden Markov models [23,24].

To determine the positions of the steps, the  $\Delta V_{\text{th}}(t)$  data is convoluted with the first derivative of a Gaussian pulse with a chosen standard deviation  $\sigma_g$ , truncated in time to  $\pm L = 5\sigma_g$ :

$$h(t) = \Delta V_{\text{th}}(t) * g(t) = \int_{-L}^{L} \Delta V_{\text{th}}(t - \delta) g(\delta) d\delta$$

(1)

The resulting signal is then compared to a threshold value, which is chosen to suppress spurious responses. Local maxima in the signal above this threshold level then give the locations of steps  $t_i$  in the original trace. With the positions of the steps, their height  $\eta_i$  can be determined from the original signal, resulting in a list of steps ( $t_i$ ,  $\eta_i$ ) as shown in Figure 4. From the list of steps, the average step heights and transition times of the defect responses can be determined, given the defects are distinguishable in step height. If this is not the case, i.e., multiple defects with similar step heights contribute to a trace, this may lead to erroneous results. This is indicated in the data by successive positive or negative steps and a non-exponential distribution of the calculated transition times.

**Figure 4.** Noise parameter extraction using the Canny algorithm. To find steps in a  $\Delta V_{\rm th}$  trace, it is convoluted with the first derivative of a Gaussian pulse. This yields a signal h, as shown in the center panel, with peaks at the positions of the steps. Thresholding is then applied to h to suppress noise. Finally, the positions of the steps are obtained from the positions of the local maxima in h. The height of the steps may be obtained either from the peaks in h or from the original trace. The result is a list of steps  $(t_i, \eta_i)$  from which, ideally, the average step height  $\eta$ , capture time  $\tau_c$ , and emission time  $\tau_e$  for each defect can be extracted.

## 2.3. Defect Parameter Estimation

From defects which are close to the Fermi level at measurement conditions, spatial and energetic positions can be estimated from their capture and emission times measured at a number of voltages [6,25,26]. The central assumption for this estimation is that a defect at the Fermi level  $E_t = E_f$  has an occupancy of 50%, i.e.,  $\tau_c = \tau_e$ . It is further assumed that the rate equations for charge capture from the channel, and charge emission to the channel can be written in the form:

$$k_{\text{c,e}} = k_{\text{0c,e}} \exp\left(-\frac{\mathcal{E}_{\text{c,e}}}{k_{\text{B}}T}\right),\tag{2}$$

Micromachines **2020**, 11, 446 5 of 11

with the capture and emission rates  $k_{c,e} = 1/\tau_{c,e}$ , prefactors  $k_{0c,e}$ , energy barriers for capture and emission  $\mathcal{E}_{c,e}$ , the Boltzmann constant  $k_{B}$ , and the device temperature T. From the logarithm of Equation (2):

$$\ln k_{c,e} = \ln k_{0c,e} - \frac{\mathcal{E}_{c,e}}{k_{\rm B}T}$$

(3)

its dependence on the gate bias is expressed:

$$\frac{\partial \ln k_{\text{c,e}}}{\partial V_{\text{G}}} = \frac{\partial \ln k_{\text{0c,e}}}{\partial V_{\text{G}}} - \frac{1}{k_{\text{B}}T} \frac{\partial \mathcal{E}_{\text{c,e}}}{\partial V_{\text{G}}}.$$

(4)

Assuming the bias dependence of the prefactor can be neglected, and subtracting Equation (4) for capture and emission yields

$$\frac{\partial \ln k_{\rm c}/k_{\rm e}}{\partial V_{\rm G}} = -\frac{1}{k_{\rm B}T} \frac{\partial (\mathcal{E}_{\rm c} - \mathcal{E}_{\rm e})}{\partial V_{\rm G}} = -\frac{1}{k_{\rm B}T} \frac{\partial E_{\rm t}}{\partial V_{\rm G}}.$$

(5)

Here,  $\partial(\mathcal{E}_c - \mathcal{E}_e)$  is replaced by the change in trap level  $\partial \mathcal{E}_t$ . This is possible due to

$$\mathcal{E}_{c} - \mathcal{E}_{e} = (E_{\text{max}} - E_{r}) - (E_{\text{max}} - E_{t}) = E_{t} - E_{r}$$

(6)

where the bias independent reservoir energy  $E_{\rm r}$  and the peak of the energetic barrier  $E_{\rm max}$  [27]. Note that this makes no assumptions on the shape of the energetic barriers between the two states of the system. Assuming the device is operating in inversion and a homogeneous oxide field is applied, the change in effective trap energy with gate voltage can be expressed with the position of the defect in the oxide as

$$\frac{\partial E_{\rm t}}{\partial V_{\rm G}} = -q \frac{d}{t_{\rm ox}}.\tag{7}$$

Equations (5) and (7) yield the relative position of the defect in the oxide

$$\frac{d}{t_{\rm ox}} = -\frac{k_{\rm B}T}{q} \left( \frac{\partial \ln \tau_{\rm c} / \tau_{\rm e}}{\partial V_{\rm G}} \right),\tag{8}$$

written with  $\tau_{c,e} = 1/k_{c,e}$ . Integrating Equation (7) gives the thermodynamic trap level of the defect:

$$E_{\rm t} = -q \frac{d}{t_{\rm ox}} V_{\rm G} + C. \tag{9}$$

At the gate voltage  $V_{G,i}$ , where the measured capture and emission times intersect, the trap level is equal to the channel Fermi level at this voltage  $E_t = E_{f,i}$ .:

$$E_{f,i} = -q \frac{d}{t_{ox}} (V_{G,i}) + C.$$

(10)

Finally, substituting C from Equation (10) in Equation (9) and evaluating at  $V_G = -V_{FB} - V_S$  yields the trap level at zero field

$$E_{t,0} = E_{f,i} + q \frac{d}{t_{ox}} (V_{G,i} - \phi_s - V_{FB}),$$

(11)

with the oxide electric field  $F_{ox}$ , the surface potential  $\phi_s$  and flatband voltage  $V_{FB}$ .

# 3. Results

Based on the methodology presented above, the recorded RTN traces are analyzed. The extracted noise parameters are used to find the distributions of step height, vertical defect position and energy level.

*Micromachines* **2020**, *11*, 446

# 3.1. Threshold Voltage Shift and Number of Defects

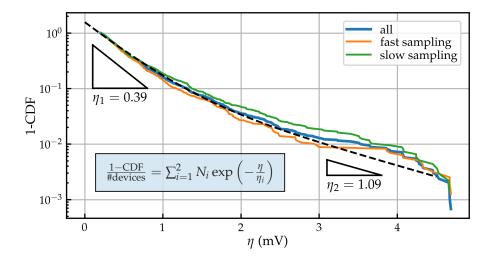

A plot showing the complimentary cumulative density function (1-CDF, or CCDF) of the step heights extracted from the measurement data of approximately 300 devices is shown in Figure 5. For a single defect distribution, an exponential distribution of step heights, i.e., a straight line in the CCDF plot, is expected [28]. In this case, however, the measurements seems to comprise two separate distributions of defects. As a consequence, defects with responses between 3 mV to 5 mV seem slightly more common than expected.

**Figure 5.** Complementary cumulative density function (1-CDF) of the step heights  $\eta$  extracted from our measurements, shown for both the slow and the fast sampled data. The distribution seems to be bimodal, composed of a defect distribution with a smaller average impact  $\eta_1$  and a distribution with a larger impact  $\eta_2$ .

# 3.2. Energy and Position

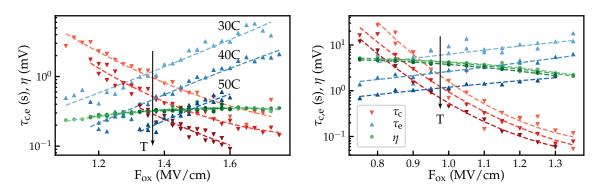

Examples of defects characterized in more detail are shown in Figure 6. Using the method described in Section 2.3, trap levels and positions of defects are estimated for around 100 defects.

**Figure 6.** Two defects characterized in detail. From the intersection points and the steepness of the charge capture and emission times, the positions and the trap levels of the defects can be estimated.

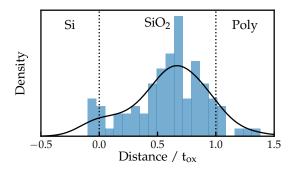

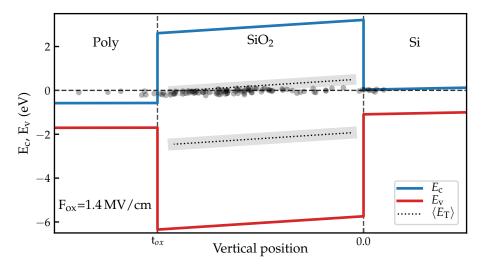

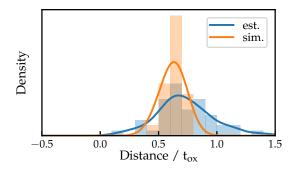

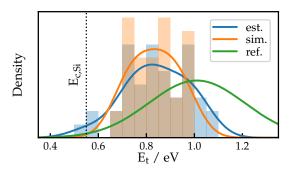

The results are shown in histograms for distance and trap level in Figure 7. Most of the defects which have been characterized are found between  $0.5\,t_{\rm ox}$  and  $0.8\,t_{\rm ox}$ , which seems to be the depth at which the electron defect band corresponds with the Fermi level at the measurement bias. This places the trap level of the extracted defects around 0.4 eV above the Fermi level, which according to our numerical device simulations is close to the Si conduction band.

Micromachines **2020**, 11, 446 7 of 11

**Figure 7.** Distributions of positions and trap levels extracted using Equation (8) and Equation (11). Note that the measured distribution in position should not be interpreted as the complete distribution of defects in the device. It is rather a result of the energetic distribution of the defects in conjunction with the characterization window, which is diagonal in energy and distance, given by the Fermi level at measurement conditions.

As can further be seen in Figure 7, the estimation given by Equation (8) suggests some defects to be located outside the oxide. This is due to a number of shortcomings in this methodology:

- (i) The estimation only accounts for interaction with the channel, defects interacting primarily with the gate might have inverted capture and emission time behavior which results in a negative distance.

- (ii) The prefactor which is assumed as constant in the estimation does change with the logarithm of the channel carrier density. This leads to some overestimation of the distance.

- (iii) The estimation is based on the values and first derivatives of the capture and emission times at the intersection point. Measurements which do not show  $\tau_c = \tau_e$  within the measurement window need to be extrapolated, which leads to inaccuracies.

- (iv) Some defects may not be adequately described using a two state model [29].

In Figure 8, the extracted defects are shown in a simulated band diagram. Furthermore, defect bands which were obtained from positive bias temperature instability (PBTI) and negative bias temperature instability (NBTI) experiments on n- and pMOS transistors, respectively, are indicated at energy values taken from [30].

**Figure 8.** Simulated band diagram showing the locations of defects extracted using Equation (8) and Equation (11). In addition, defect bands as given in [30] are shown in comparison. Notice how some defects appear located outside of the  $SiO_2$  layer. This shows the shortcomings of the estimation used. The estimation does not account for defect interaction with the gate, which often results in negative  $d/t_{ox}$  and it generally overestimates the distance of the defects due to the neglected prefactor.

Micromachines 2020, 11, 446 8 of 11

For the electron trap band this is around 0.5 eV above the conduction band, which is around 0.1 eV higher than the values we extract from the measured defects. This might be due to defects closer to the gate interacting primarily with the gate instead of the channel, effectively limiting our measurement range in energy. A number of defects show up with distances around zero, i.e., with very small bias dependencies of their  $\tau_c/\tau_e$  ratios. They may be located close to either the Si/SiO<sub>2</sub> interface or to the SiO<sub>2</sub>/poly interface.

#### 3.3. Simulation

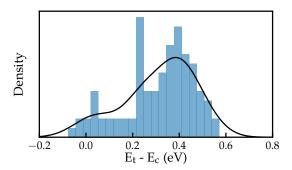

To obtain more accurate data, the capture and emission time behavior for a subset of the defects characterized using the estimation formulas is replicated using technology computer aided design (TCAD) simulation [31]. For the simulations, an effective two-state nonradiative multi phonon (NMP) model is used. Only those measurements are used where the intersection point lies within the measurement range. This removes the peak close to the interface observed in Figures 7 and 8. The distributions for the resulting distances and energies are shown in Figure 9.

**Figure 9.** Distributions of positions and trap levels from technology computer aided design (TCAD) simulations compared to the estimations made for the same defects. Energies are referenced from Si-midgap, with  $E_{f,i}$  taken from the simulation. The electron defect band at  $E_t = 1.01 \,\text{eV}$  from [30] is shown for comparison. The defects we observe are distributed mainly in the lower half of this band.

It can be seen that the simulation results are in good agreement with the data obtained from the estimations. The average depth assigned to the measured defects is slightly lower in the simulation and all defects are confined to the oxide. It can be further observed that the average of the energy distribution is slightly lower compared to the estimation. Compared to the electron defect band at  $E_t = 1.01 \, \text{eV} \pm 0.218 \, \text{eV}$  from [30], which was obtained from PBTI experiments on nMOS transistors, we extract only defects in the lower half of this band, as only those can contribute to the measured RTN.

# 4. Discussion

The distributions of step heights in Si/SiO<sub>2</sub> devices which have been reported in literature can commonly be explained using a single exponential distribution. However, in the underlying work we clearly observe a bimodal distribution of the measured step heights, which one would not expect for Si/SiO<sub>2</sub> devices. Bimodal distributions are commonly observed for PBTI only in high-k devices, where they are thought to originate from traps in both the bulk high-k layer and the interstitial layer [32–34]. A simple approximation of the threshold voltage shift expected is possible using the charge sheet approximation, which gives values below 0.2 mV for these devices. This agrees within the limits of this approximation to the smaller  $\eta_1$  observed. However, the origin of the larger  $\eta_2$  in this technology needs further investigation.

In this work, we use an analytical approximation to extract the trap levels and spatial distribution from a large set of RTN measurements and compare the results to TCAD simulations. The results for the energetic and spatial distributions show good agreement between the estimated and the simulated

Micromachines **2020**, 11, 446 9 of 11

parameters, considering the approximations made in the estimation. The energetic distribution of the extracted defects covers the lower half of an electron defect band obtained from simulations reported recently. Due to the limited scanning range of the RTN measurements performed, no defects could be measured in the upper half of this band. A possibility to extend the energetic range of the investigations in a future work could be the combination of the obtained RTN data with data obtained from TDDS measurements.

**Author Contributions:** Conceptualization, all; methodology, B.S. and F.S.; software, B.S. and M.W.; validation, B.S., M.W. and T.G.; formal analysis, B.S.; investigation, B.S. and M.W.; resources, M.W. and T.G.; data curation, B.S. and M.W.; writing–original draft preparation, B.S.; writing–review and editing, all; visualization, B.S.; supervision, M.W. and T.G.; project administration, T.G.; funding acquisition, T.G. All authors have read and agreed to the published version of the manuscript.

Funding: This research received no external funding.

**Conflicts of Interest:** The authors declare no conflict of interest.

#### References

- 1. Lenahan, P. Atomic Scale Defects Involved in MOS Reliability Problems. *Microelectron. Eng.* **2003**, *69*, 173–181. [CrossRef]

- 2. Rzepa, G.; Waltl, M.; Goes, W.; Kaczer, B.; Grasser, T. Microscopic Oxide Defects Causing BTI, RTN, and SILC on High-k FinFETs. In Proceedings of the 2015 International Conference on Simulation of Semiconductor Processes and Devices (SISPAD), Washington, DC, USA, 9–11 September 2015; pp. 144–147.

- 3. Denais, M.; Huard, V.; Parthasarathy, C.; Ribes, G.; Perrier, F.; Revil, N.; Bravaix, A. Interface Trap Generation and Hole Trapping under NBTI and PBTI in Advanced CMOS Technology with a 2-nm Gate Oxide. *IEEE Trans. Devices Mater. Reliab.* **2004**, *4*, 715–722. [CrossRef]

- 4. Grasser, T.; Kaczer, B.; Gös, W.; Reisinger, H.; Aichinger, T.; Hehenberger, P.; Wagner, P.J.; Franco, J.; Toledano-Luque, M.; Nelhiebel, M. The Paradigm Shift in Understanding the Bias Temperature Instability: From Reaction-Diffusion to Switching Oxide Traps. *IEEE Trans. Electron Devices* **2011**, *58*, 3652–3666. [CrossRef]

- 5. Stathis, J.H.; Mahapatra, S.; Grasser, T. Controversial Issues in Negative Bias Temperature Instability. *Microelectron. Reliab.* **2018**, *81*, 244–251. [CrossRef]

- 6. Ralls, K.S.; Skocpol, W.J.; Jackel, L.D.; Howard, R.E.; Fetter, L.A.; Epworth, R.W.; Tennant, D.M. Discrete Resistance Switching in Submicrometer Silicon Inversion Layers: Individual Interface Traps and Low-Frequency (\frac{1}{7}) Noise. *Phys. Rev. Lett.* **1984**, *52*, 228–231. doi:10.1103/PhysRevLett.52.228. [CrossRef]

- 7. Uren, M.; Day, D.; Kirton, M. 1/f and Random Telegraph Noise in Silicon Metal-Oxide-Semiconductor Field-effect Transistors. *Appl. Phys. Lett.* **1985**, *47*, 1195–1197. [CrossRef]

- 8. Ghetti, A.; Compagnoni, C.; Spinelli, A.; Visconti, A. Comprehensive Analysis of Random Telegraph Noise Instability and Its Scaling in Deca–Nanometer Flash Memories. *IEEE Trans. Electron Devices* **2009**, 56, 1746–1752. [CrossRef]

- 9. Fukuda, K.; Shimizu, Y.; Amemiya, K.; Kamoshida, M.; Hu, C. Random Telegraph Noise in Flash Memories-Model and Technology Scaling. In Proceedings of the 2007 IEEE International Electron Devices Meeting, Washington, DC, USA, 10–12 December 2007; IEEE: Piscataway, NJ, USA, 2007; pp. 169–172.

- 10. Kükner, H.; Weckx, P.; Franco, J.; Toledano-Luque, M.; Cho, M.; Kaczer, B.; Raghavan, P.; Jang, D.; Miyaguchi, K.; Bardon, M.G.; et al. Scaling of BTI Reliability in Presence of Time-Zero Variability. In Proceedings of the 2014 IEEE International Reliability Physics Symposium, Waikoloa, HI, USA, 1–5 June 2014; IEEE: Piscataway, NJ, USA, 2014; p. CA-5.

- 11. Kaczer, B.; Grasser, T.; Roussel, P.J.; Franco, J.; Degraeve, R.; Ragnarsson, L.; Simoen, E.; Groeseneken, G.; Reisinger, H. Origin of NBTI Variability in Deeply Scaled pFETs. In Proceedings of the 2010 IEEE International Reliability Physics Symposium, Anaheim, CA, USA, 2–6 May 2010; pp. 26–32. doi:10.1109/IRPS.2010.5488856. [CrossRef]

- 12. Toledano-Luque, M.; Kaczer, B.; Roussel, P.; Cho, M.; Grasser, T.; Groeseneken, G. Temperature Dependence of the Emission and Capture Times of SiON Individual Traps after Positive Bias Temperature Stress. *J. Vac. Sci. Technol. B* **2011**, *29*, 01AA04. [CrossRef]

Micromachines **2020**, 11, 446

13. Park, S.; Lee, S.; Kang, Y.; Park, B.G.; Lee, J.H.; Lee, J.; Jin, G.; Shin, H. Extracting Accurate Position and Energy Level of Oxide Trap Generating Random Telegraph Noise (RTN) in Recessed Channel MOSFET's. In Proceedings of the 40th European Solid-State Device Research Conference (ESSDERC), Seville, Spain, 14–16 September 2010; pp. 337–340.

- 14. Grill, A.; Stampfer, B.; Waltl, M.; Im, K.S.; Lee, J.H.; Ostermaier, C.; Ceric, H.; Grasser, T. Characterization and Modeling of Single Defects in GaN/AlGaN fin-MIS-HEMTs. In Proceedings of the 2017 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 2–6 April 2017; p. 3B–5.

- 15. Stampfer, B.; Zhang, F.; Illarionov, Y.Y.; Knobloch, T.; Wu, P.; Waltl, M.; Grill, A.; Appenzeller, J.; Grasser, T. Characterization of Single Defects in Ultrascaled MoS2 Field-Effect Transistors. *ACS Nano* **2018**, *12*, 5368–5375, doi:10.1021/acsnano.8b00268. [CrossRef]

- 16. Waltl, M. Ultra-Low Noise Defect Probing Instrument for Defect Spectroscopy of MOS Transistors. *Trans. Elec. Dev.* **2020**, submitted. [CrossRef]

- 17. Kapila, G.; Reddy, V. Impact of Sampling Rate on RTN Time Constant Extraction and its Implications on Bias Dependence and Trap Spectroscopy. *IEEE Trans. Device Mater. Reliab.* **2014**, *14*, 616–622.

- 18. Grasser, T.; Wagner, P.J.; Hehenberger, P.; Goes, W.; Kaczer, B. A Rigorous Study of Measurement Techniques for Negative Bias Temperature Instability. *IEEE Trans. Device Mater. Reliab.* **2008**, *8*, 526–535. [CrossRef]

- 19. Canny, J. A Computational Approach to Edge Detection. In *Readings in Computer Vision*; Elsevier: Amsterdam, The Netherlands, 1987; pp. 184–203.

- 20. McIlhagga, W. The Canny Edge Detector Revisited. Int. J. Comput. Vis. 2011, 91, 251–261. [CrossRef]

- 21. Martin-Martinez, J.; Diaz, J.; Rodriguez, R.; Nafria, M.; Aymerich, X. New Weighted Time Lag Method for the Analysis of Random Telegraph Signals. *IEEE Electron Device Lett.* **2014**, *35*, 479–481. doi:10.1109/LED.2014.2304673. [CrossRef]

- 22. Maestro, M.; Diaz, J.; Crespo-Yepes, A.; Gonzalez, M.; Martin-Martinez, J.; Rodriguez, R.; Nafria, M.; Campabadal, F.; Aymerich, X. New High Resolution Random Telegraph Noise (RTN) Characterization Method for Resistive RAM. *Solid-State Electron.* **2016**, *115*, 140–145. [CrossRef]

- 23. Ghahramani, Z.; Jordan, M.I. Factorial Hidden Markov Models. In *Advances in Neural Information Processing Systems 9, Proceedings of the 1996 Conference*; MIT Press: Cambridge, MA, USA, 1996; pp. 472–478.

- 24. Frank, D.J.; Miki, H. Analysis of Oxide Traps in Nanoscale MOSFETs Using Random Telegraph Noise. In *Bias Temperature Instability for Devices and Circuits*; Springer: Berlin, Germany, 2014; pp. 111–134.

- 25. Kirton, M.; Uren, M. Noise in Solid-State Microstructures: A New Perspective on Individual Defects, Interface States and Low-Frequency (1/f) Noise. *Adv. Phys.* **1989**, *38*, 367–468. [CrossRef]

- 26. Nagumo, T.; Takeuchi, K.; Hase, T.; Hayashi, Y. Statistical Characterization of Trap Position, Energy, Amplitude and Time Constants by RTN Measurement of Multiple Individual Traps. In Proceedings of the 2010 International Electron Devices Meeting, San Francisco, CA, USA, 6–8 December 2010; IEEE: Piscataway, NJ, USA, 2010; pp. 28–30.

- 27. Goes, W.; Wimmer, Y.; El-Sayed, A.M.; Rzepa, G.; Jech, M.; Shluger, A.; Grasser, T. Identification of Oxide Defects in Semiconductor Devices: A Systematic Approach Linking DFT to Rate Equations and Experimental Evidence. *Microelectron. Reliab.* 2018, 87, 286–320. [CrossRef]

- 28. Kaczer, B.; Roussel, P.; Grasser, T.; Groeseneken, G. Statistics of Multiple Trapped Charges in the Gate Oxide of Deeply Scaled MOSFET Devices-Application to NBTI. *IEEE Electron Device Lett.* **2010**, *31*, 411–413. [CrossRef]

- 29. Grasser, T. Stochastic Charge Trapping in Oxides: From Random Telegraph Noise to Bias Temperature Instabilities. *Microelectron. Reliab.* **2012**, *52*, 39–70. [CrossRef]

- 30. Rzepa, G.; Franco, J.; O'Sullivan, B.; Subirats, A.; Simicic, M.; Hellings, G.; Weckx, P.; Jech, M.; Knobloch, T.; Waltl, M.; et al. Comphy—A Compact-Physics Framework for Unified Modeling of BTI. *Microelectron. Reliab.* **2018**, *85*, 49–65. [CrossRef]

- 31. Global TCAD Solutions. GTS Framework. Available online: http://www.globaltcad.com/framework (accessed on 17 April 2020).

- 32. Weckx, P.; Kaczer, B.; Chen, C.; Franco, J.; Bury, E.; Chanda, K.; Watt, J.; Roussel, P.J.; Catthoor, F.; Groeseneken, G. Characterization of Time-dependent Variability using 32k Transistor Arrays in an Advanced HK/MG Technology. In Proceedings of the 2015 IEEE International Reliability Physics Symposium, Monterey, CA, USA, 19–23 April 2015; pp. 3B.1.1–3B.1.6. doi:10.1109/IRPS.2015.7112702. [CrossRef]

Micromachines **2020**, 11, 446

33. Oshima, A.; Komawaki, T.; Kobayashi, K.; Kishida, R.; Weckx, P.; Kaczer, B.; Matsumoto, T.; Onodera, H. Physical-based RTN Modeling of Ring Oscillators in 40-nm SiON and 28-nm HKMG by Bimodal Defect-Centric Behaviors. In Proceedings of the 2016 International Conference on Simulation of Semiconductor Processes and Devices (SISPAD), Nuremberg, Germany, 6–8 September 2016; IEEE: Piscataway, NJ, USA, 2016; pp. 327–330.

34. Waltl, M.; Rzepa, G.; Grill, A.; Goes, W.; Franco, J.; Kaczer, B.; Witters, L.; Mitard, J.; Horiguchi, N.; Grasser, T. Superior NBTI in High-*k* SiGe Transistors - Part I: Experimental. *IEEE Trans. Electron Devices* **2017**, *64*, 2092–2098. doi:10.1109/TED.2017.2686086. [CrossRef]

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).