# Investigation of Anomalous Degradation Tendency of Low-Frequency Noise in Irradiated SOI-NMOSFETs

Rui Liu <sup>1,2,3</sup>, Linchun Gao <sup>1,3</sup>, Juanjuan Wang <sup>1,3</sup>, Tao Ni <sup>1,3</sup>, Yifan Li <sup>1,2,3</sup>, Runjian Wang <sup>1,2,3</sup>, Duoli Li <sup>1,3</sup>, Jianhui Bu <sup>1,3</sup>, Chuanbin Zeng <sup>1,3,\*</sup>, Bo Li <sup>1,3</sup> and Jiajun Luo <sup>1,3,\*</sup>

- <sup>1</sup> Institute of Microelectronics, Chinese Academy of Sciences, Beijing 100029, China

- <sup>2</sup> University of Chinese Academy of Sciences, Beijing 100049, China

- <sup>3</sup> Key Laboratory of Science and Technology on Silicon Devices, Chinese Academy of Sciences, Beijing 100029, China

- Correspondence: chbzeng@ime.ac.cn (C.Z.); luojj@ime.ac.cn (J.L.)

**Abstract:** In this work, we present new evidence of the physical mechanism behind the generation of low-frequency noise with high interface-trap density by measuring the low-frequency noise magnitudes of partially depleted (PD) silicon-on-insulator (SOI) NMOSFETs as a function of irradiation dose. We measure the DC electrical characteristics of the devices at different irradiation doses and separate the threshold-voltage shifts caused by the oxide-trap charge and interface-trap charge. Moreover, the increased densities of the oxide-trap charge projected to the Si/SiO<sub>2</sub> interface and interface-trap charge are calculated. The results of our experiment suggest that the magnitudes of low-frequency noise do not necessarily increase with the increase in border-trap density. A novel physical explanation for the low-frequency noise in SOI-NMOSFETs with high interface-trap density is proposed. We reveal that the presence of high-density interface traps after irradiation has a repressing effect on the generation of low-frequency noise. Furthermore, the exchange of some carriers between border traps and interface traps can cause a decrease in the magnitude of low-frequency noise when the interface-trap density is high.

check for **updates**

Citation: Liu, R.; Gao, L.; Wang, J.; Ni, T.; Li, Y.; Wang, R.; Li, D.; Bu, J.; Zeng, C.; Li, B.; et al. Investigation of Anomalous Degradation Tendency of Low-Frequency Noise in Irradiated SOI-NMOSFETs. *Micromachines* **2023**, *14*, 602. https://doi.org/10.3390/ mi14030602

Academic Editors: Yiqiang Chen, Yi Liu and Changqing Xu

Received: 16 February 2023 Revised: 1 March 2023 Accepted: 3 March 2023 Published: 4 March 2023

**Copyright:** © 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https:// creativecommons.org/licenses/by/ 4.0/). **Keywords:** low-frequency noise; ionizing radiation; radiation effects; partially depleted silicon-oninsulator (PDSOI); MOSFET; border trap; interface trap

## 1. Introduction

Recently, silicon-on-insulator (SOI) technology has become increasingly important in radiation-exposed environments such as space and military electronics due to its greater immunity to single-event effect (SEE) and suppression of the latch-up effect [1–3]. Furthermore, due to their strong anti-interference properties, high integration density, and fast operation speed, SOI MOSFETs have been found to be applicable to signal processing circuits, especially in radiation-exposed settings [4,5]. It is well known that low-frequency noise plays a substantial role in the performance of low-noise signal processing circuits [6]. However, as devices become increasingly scaled down, noise emerges as a crucial factor affecting device and circuit performance. Thus, exploring the electrical characteristics and low-frequency noise of SOI MOSFETs under irradiation, in addition to the underlying physical mechanisms, is of critical importance. As devices are miniaturized, it has been observed that thinner gate oxide becomes less susceptible to the total ionizing dose (TID) effect, leading to decreased threshold-voltage shifts and leakage current [7]. Despite this, TID still affects the low-frequency noise of smaller devices, related to interface traps at the  $Si/SiO_2$  interface and border traps in oxide near the interface (2–3 nm). Some studies have focused on the low-frequency noise of MOSFETs under irradiation [7–15]. However, most of these studies only compared the low-frequency noise of devices before and after irradiation with a certain dose, and few have studied the degradation trend of the low-frequency noise of devices in a wider range of radiation doses.

Two mechanisms are mainly responsible for the low-frequency noise in semiconductor devices: the mobility fluctuation model and the carrier number fluctuation model. The low-frequency noise due to fluctuation of carrier mobility in the channel caused by various scattering processes, referred to as fundamental 1/f noise, and the low-frequency noise due to fluctuation of the carrier number caused by defects traps, referred to as nonfundamental 1/f noise, are observed in MOSFETs. Nonfundamental 1/f noise usually has a much larger magnitude than fundamental 1/f noise. Moreover, fundamental 1/f noise dominates only when the defect density is reduced enough to ignore nonfundamental 1/f noise [16]. Therefore, it is generally assumed that the low-frequency noise in MOSFETs is caused by the fluctuation of carrier number. The theoretical sources of the fluctuation in carrier number mainly comprise the following [17]. McWhorter suggested that tunneling exchange of carriers between the channel and border traps of the same energy level is the primary generator of low-frequency noise [18]. Sah et al. then proposed an alternative tunneling model, which utilized interface traps as intermediate states during the tunneling process [19]. Apart from the tunneling model, Dutta and Horn determined that low-frequency noise also could be attributed to the trapping of carriers thermally activated by border traps [20]. However, tunneling and Dutta-Horn models both fail to explain low-frequency noise of a clean silicon surface in a vacuum environment [21]. To explain the low-frequency noise generated without an oxide layer or suitable traps inside the oxide layer, Jäntsch suggested that low-frequency noise is generated through the random walk of electrons at the interface [22]. As mentioned above, both border traps and interface traps contribute to low-frequency noise in MOSFETs. Moreover, the tunneling theory remains widely accepted.

The work of Sah et al. demonstrates that carriers liberated by interface traps can be caught by border traps [19]. Additionally, the random walk theory exhibits that the time constants of interface traps can be modulated to be close to that of border traps by carriers randomly walking at the interface [22]. These previous investigations have given the physical basis of carriers exchanging between interface traps and border traps. However, few research addresses the effect of increasing interface traps on the low-frequency noise of MOSFETs after irradiation.

In this paper, the measurements of low-frequency noise behavior and DC electrical characteristics of SOI NMOSFETs of different sizes and gate oxide thicknesses at irradiation doses are presented, serving as a valuable reference for circuit design applications that necessitate good noise performance in radiation conditions. Furthermore, analysis of the low-frequency noise magnitudes post-irradiation is conducted. Additionally, a novel physical mechanism is suggested for low-frequency noise in NMOSFETs with a high density of interface traps.

## 2. Devices and Experimental Details

#### 2.1. Devices under Test

The devices we tested were SOI-NMOSFETs with an operating voltage of 1.8 V and 5 V, which were fabricated using a 0.18- $\mu$ m PD-SOI CMOS process. The gate lengths  $L = 0.18 \mu$ m and 10  $\mu$ m for 1.8 V devices and  $L = 0.5 \mu$ m and 10  $\mu$ m for 5 V devices. Table 1 outlines the main parameters of the device under test.

| Table 1. Main parameters of the SOI-NMOSFETS under t | æst. |

|------------------------------------------------------|------|

|------------------------------------------------------|------|

| Parameter                              | Value of 1.8 V Devices            | Value of 5 V Devices              |

|----------------------------------------|-----------------------------------|-----------------------------------|

| Operating Voltage                      | 1.8 V                             | 5 V                               |

| Gate Length(L)                         | 0.18 μm, 10 μm                    | 0.5 μm, 10 μm                     |

| Gate Width (W)                         | 1.8 μm, 10 μm                     | 10 µm                             |

| Gate Oxide thickness $(T_{ox})$        | 4 nm                              | 12.5 nm                           |

| Channel Doping (N <sub>channel</sub> ) | $1	imes 10^{18}~\mathrm{cm}^{-3}$ | $2	imes 10^{17}~\mathrm{cm}^{-3}$ |

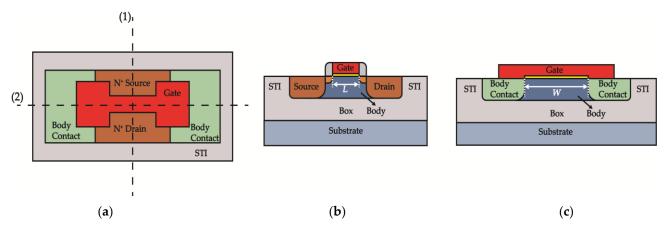

The layout and its corresponding cross-sectional view of these SOI NMOSFETs are illustrated in Figure 1. The layout of the measured devices employs an edgeless H-gate structure, hence no overlap between the gate and the shallow trench isolation (STI) is present, thereby eliminating the influence STI may have on the channel after irradiation. Additionally, each device has a body contact to eliminate the floating-body effect.

**Figure 1.** (**a**) Layout of measured devices. (**b**) Cross-sectional view of measured devices along the dashed line (1) in (**a**). (**c**) Cross-sectional view of measured devices along the dashed line (2) in (**a**).

#### 2.2. Experimental Details

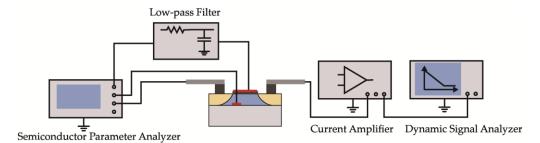

To minimize experimental error and increase the reliability of the results, we tested three devices of each size in the following experiments. All devices were irradiated to 1 Mrad (Si) of  $\gamma$ -rays from a <sup>60</sup>Co source at a dose rate of 100 rad (Si)/s and a temperature of ~298 K. During irradiation, all devices were biased in an ON-state, with the gate held at  $V_{DD}$ and the other terminals grounded. The electrical and noise performance measurements were conducted within two hours after each exposure step. The electrical characterization was measured using the Keithley 4200-SCS Semiconductor Parameter Analyzer at room temperature. The threshold voltage ( $V_{\text{th}}$ ) was obtained via linear extrapolation (LE) [23], whereby the  $V_{g}$  axis intercept of the linear extrapolation of the  $I_{d}$ - $V_{gs}$  curve at the point with the largest first derivative was calculated when the device was in the linear region  $(V_{\rm ds} = 100 \text{ mV})$ , such that  $V_{\rm th}$  equaled the intercept minus  $V_{\rm ds}/2$ . Moreover, the thresholdvoltage shift ( $\Delta V_{\text{th}}$ ) of the device after irradiation was partitioned into the components due to trapped charge in oxide traps ( $\Delta V_{ot}$ ) and interface traps ( $\Delta V_{it}$ ), per the midgap charge method presented by McWhorter [24]. Additionally, the drain-current noise power density spectral S<sub>id</sub> of the devices was measured with a noise measurement system at room temperature. The drain-current noise signal was amplified by the low-noise current amplifier SR570 and then measured by the HP35670 dynamic signal analyzer. Figure 2 illustrates the schematic diagram of the noise measurement system used in this experiment.

Figure 2. Illustration of the low-frequency noise measurement system.

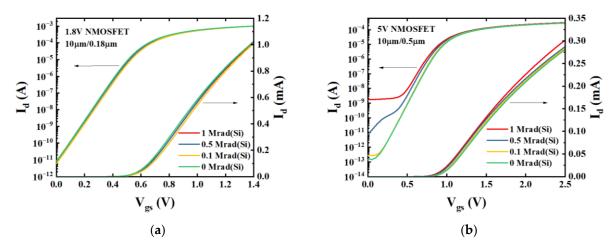

Figure 3 displays the linear and logarithmic coordinates of the  $I_d$ - $V_{gs}$  electrical characteristics of NMOSFETs in the linear region ( $V_{ds} = 0.1$  V) for operating voltages of 1.8 V and 5 V. The  $I_d$ - $V_{gs}$  curves of 1.8 V NMOSFETs with H-gate have been observed to remain insensitive to increasing radiation dose up to 1 Mrad. In contrast, the off-state current of 5 V NMOSFETs with H-gate has been found to vary more significantly in response to a radiation dose of up to 1 Mrad.

**Figure 3.**  $I_d$ – $V_{gs}$  curves in the linear region ( $V_{ds} = 0.1$  V) of (**a**) 1.8 V NMOSFETs for geometry:  $W/L = 10 \ \mu m/0.18 \ \mu m$  and (**b**) 5 V NMOSFETs for geometry:  $W/L = 10 \ \mu m/0.5 \ \mu m$ . All devices were irradiated up to 1 Mrad(Si) under the "on" bias condition.

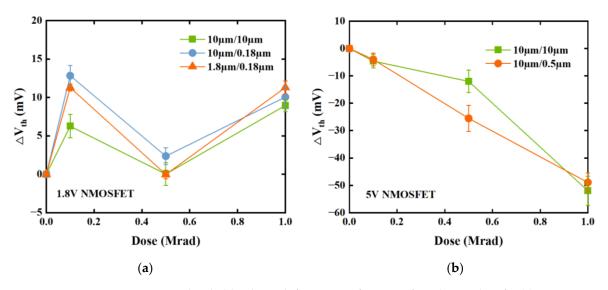

The  $V_{\text{th}}$  of all the devices tested are calculated using linear extrapolation (LE) [23]. Figure 4 shows the  $\Delta V_{\text{th}}$  of 1.8 V and 5 V devices of different sizes as a function of irradiation dose. Figure 4a demonstrates that the  $\Delta V_{\text{th}}$  of each 1.8 V device rises from pre-irradiation up to 0.1 Mrad, then falls from 0.1 Mrad to 0.5 Mrad before increasing once more from 0.5 Mrad to 1 Mrad. Figure 4b reveals that the  $\Delta V_{\text{th}}$  of each 5 V device decreases with the increase in doses. Overall, it was determined that the  $\Delta V_{\text{th}}$  of 1.8 V devices are comparatively less significant than those of 5 V devices.

**Figure 4.** Threshold-voltage shift  $\Delta V_{\text{th}}$  as a function of irradiation dose for (**a**) 1.8 V NMOSFETs with geometries  $W/L = 10 \ \mu\text{m}/10 \ \mu\text{m}$ ,  $10 \ \mu\text{m}/0.18 \ \mu\text{m}$ , and  $1.8 \ \mu\text{m}/0.18 \ \mu\text{m}$  and (**b**) 5 V NMOSFETs with geometries  $W/L = 10 \ \mu\text{m}/10 \ \mu\text{m}$  and  $10 \ \mu\text{m}/0.5 \ \mu\text{m}$ . All devices were irradiated up to 1 Mrad(Si) under the "on" bias condition.

$\Delta V_{\text{th}}$  is contributed by both the interface-trap and oxide-trap charge, as demonstrated by the equation below.:

$$\Delta V_{\rm th} = \Delta V_{\rm it} + \Delta V_{\rm ot} \tag{1}$$

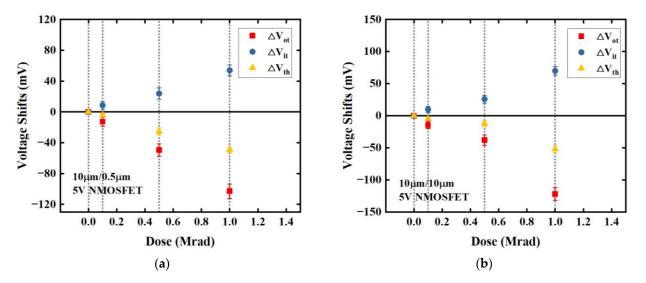

where  $\Delta V_{it}$  is the threshold-voltage shift due to net interface-trap charge and  $\Delta V_{ot}$  is the threshold-voltage shift due to net oxide-trap charge. We split the threshold-voltage shift into  $\Delta V_{it}$  and  $\Delta V_{ot}$  using the midgap charge method [23]. However, the midgap voltage of the 1.8 V device is barely detectable due to the trivial variation between the subthreshold-current curves of different irradiation doses. Figure 5 depicts the threshold-voltage shifts caused by net oxide-trap and interface-trap charge as a function of irradiation dose for 5 V NMOSFETs with geometries of (a)  $W/L = 10 \ \mu m/0.5 \ \mu m$  and (b)  $10 \ \mu m/10 \ \mu m$ .

**Figure 5.** Net threshold-voltage shifts and components due to oxide-trap charge and interface-trap charge as a function of irradiation dose for the 5 V NMOSFETs (**a**) with a width of 10  $\mu$ m and a length of 0.5  $\mu$ m, as well as those (**b**) with a width of 10  $\mu$ m and a length of 10  $\mu$ m. All devices were irradiated up to 1 Mrad(Si) under the "on" bias condition.

Once the  $\Delta V_{it}$  due to the net interface-trap charge has been obtained, the increased density of interface-trap charge can be calculated using the following equation:

$$\Delta N_{\rm it} = \frac{\Delta V_{\rm it} C_{\rm ox}}{q} \tag{2}$$

where  $C_{\text{ox}}$  is the capacitance per unit area of the gate oxide, and *q* is the electron charge. Similarly, once the  $\Delta V_{\text{ot}}$  due to the net oxide-trap charge is obtained, the increased density of the oxide-trap charge projected to the Si/SiO<sub>2</sub> interface can be calculated using the following equation:

$$\Delta N_{\rm ot} = \frac{\Delta V_{\rm ot} C_{\rm ox}}{q} \tag{3}$$

Although the  $\Delta V_{\text{th}}$  of a 5 V device became increasingly negative with an increasing irradiation dose, the  $\Delta V_{\text{it}}$  due to interface traps became correspondingly more positive. This implies that the densities of both interface traps and oxide traps increase with the rising irradiation dose. Table 2 displays the corresponding values of  $\Delta N_{\text{it}}$  and  $\Delta N_{\text{ot}}$  calculated from the  $\Delta V_{\text{it}}$  and  $\Delta V_{\text{ot}}$  in Figure 5.

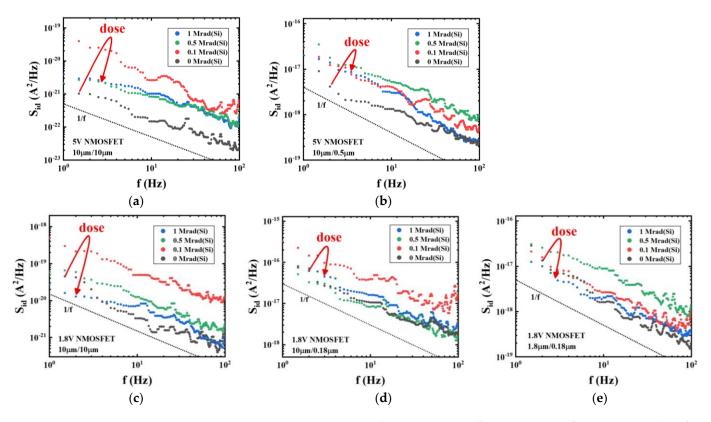

Figure 6 shows the drain-current noise power density spectrum of 1.8 V and 5 V NMOSFETs with different dimensions before and after irradiation with different doses. We measured the low-frequency noise between 1 Hz and 100 Hz in the linear region of device response where drain voltage  $V_{ds} = 0.1$  V and gate voltage  $V_{gt} = V_{gs} - V_{th} = 0.3$  V. The low-frequency noise of all measured devices is characterized by 1/f noise. By comparing the pre-irradiation drain-current low-frequency noise magnitudes of the devices in Figure 6a,b, and those in Figure 6c,d, it can be seen that the device with the shorter gate length exhibits

a higher low-frequency noise at the same gate width. Similarly, comparison of the preirradiation drain-current low-frequency noise magnitudes of the devices in Figure 6d,e reveals that the device with the wider gate width exhibits a higher low-frequency noise at the same gate length. These correlations observed between the device dimensions and the low-frequency noise are consistent with the previous physical explanation that low-frequency noise in MOSFETs originates from the exchange of carriers between the channel and border traps [18,25,26]. The trend of low-frequency noise as a function of the irradiation dose is largely similar for all measured devices in Figure 6. The noise magnitudes of all devices reach a peak at a comparatively low irradiation dose, which is 0.5 Mrad for the 5 V device with geometry  $W/L = 10 \ \mu m \ /0.5 \ \mu m$  and 1.8 V device with geometry  $W/L = 1.8 \ \mu m / 0.18 \ \mu m$ , and 0.1 Mrad for the other devices. Furthermore, the noise magnitudes at higher irradiation doses are generally lower than those at lower doses, even though the density of border traps in the oxide tends to increase at higher radiation doses. Interestingly, this trend appears to contradict the previously proposed physical mechanism of low-frequency noise that carriers exchange between the channel and border traps [18–20].

| W/L          | Dose (Mrad) | $\Delta N_{ m it}$ (10 <sup>10</sup> cm <sup>-2</sup> ) | $\Delta N_{ m ot}$ (10 $^{10}~ m cm^{-2}$ ) |

|--------------|-------------|---------------------------------------------------------|---------------------------------------------|

|              | 0.1         | 1.72                                                    | 2.52                                        |

| 10 μm/10 μm  | 0.5         | 4.83                                                    | 6.58                                        |

|              | 1           | 12                                                      | 21.4                                        |

|              | 0.1         | 1.52                                                    | 2.22                                        |

| 10 μm/0.5 μm | 0.5         | 4.18                                                    | 8.65                                        |

|              | 1           | 9.44                                                    | 18                                          |

**Table 2.**  $\Delta N_{\rm it}$  and  $\Delta N_{\rm ot}$  of devices in Figure 5.

The tunneling model for low-frequency noise can be expressed by a first-order expression, as outlined by its physical mechanism, which indicates that carriers transition between the channel and border traps. This is expressed as follows: [27,28]:

$$S_{\rm vd} = \frac{q^2}{C_{\rm ox}^2} \frac{V_{\rm D}^2}{(V_{\rm G} - V_{\rm tb})^2} \frac{k_{\rm B} T D_{\rm bt}(E_{\rm f})}{L W \ln(\tau_1 / \tau_0)} \frac{1}{f}$$

(4)

where  $S_{vd}$  is drain-voltage noise power density spectrum,  $k_B$  is Boltzmann's constant, T is absolute temperature,  $D_{bt}(E_f)$  is the density of border traps in oxide near the interface (2–3 nm) at Fermi level, f is frequency, and  $\tau_0$  and  $\tau_1$  are minimum and maximum tunneling time respectively. In the linear region of a device, the relationship between drain-voltage noise power density spectrum  $S_{vd}$  and drain-current noise power density spectrum  $S_{id}$  is given by:

$$S_{\rm id} = \frac{I_{\rm ds}^2}{V_{\rm ds}^2} S_{\rm vd} \tag{5}$$

where  $I_{ds}$  is drain-current, and  $V_{ds}$  is drain-voltage.

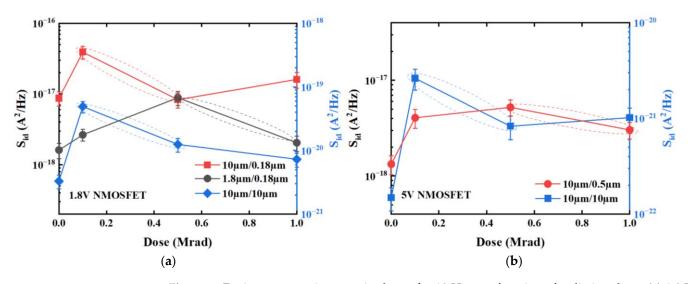

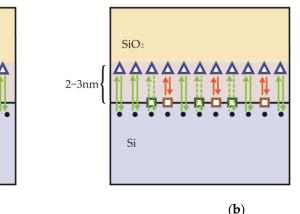

According to the first-order expression of the tunneling model, as the border traps increase with increasing irradiation dose, the  $S_{id}$  should have increased accordingly. However, Figure 6 appears to contradict this prediction, as noise magnitudes at higher irradiation doses decrease. This phenomenon is further demonstrated in Figure 7 which shows that drain-current noise magnitudes of 1.8 V and 5 V NMOSFETs at a frequency of 10 Hz reach a maximum at a certain irradiation dose before decreasing with further increases in radiation exposure. Figure 7 shows that the magnitude of the 10 Hz drain-current noise of a 1.8 V NMOSFET with a size of  $W/L = 10 \ \mu m/0.18 \ \mu m$  reaches its maximum value  $3.91 \times 10^{-17} \ A^2/Hz$  at 0.1 Mrad, then decreases to  $8.30 \times 10^{-18} \ A^2/Hz$  at 0.5 Mrad; for a 1.8 V NMOSFET with a size of  $W/L = 10 \ \mu m/10 \ \mu m$ , the maximum value is  $4.91 \times 10^{-20} \ A^2/Hz$  at 0.1 Mrad and decreases to  $1.25 \times 10^{-20} \ A^2/Hz$  at 0.5 Mrad;

for a 1.8 V NMOSFET with a size of  $W/L = 1.8 \ \mu m/0.18 \ \mu m$ , the maximum value is  $8.88 \times 10^{-18} \ A^2/Hz$  at 0.5 Mrad and decreases to  $2.04 \times 10^{-18} \ A^2/Hz$  at 1 Mrad; for a 5 V NMOSFET with a size of  $W/L = 10 \ \mu m / 10 \ \mu m$ , the maximum value is  $2.62 \times 10^{-21} \ A^2/Hz$  at 0.1Mrad and decreases to  $8.28 \times 10^{-22} \ A^2/Hz$  at 0.5 Mrad; finally, for a 5 V NMOSFET with a size of  $W/L = 10 \ \mu m / 0.5 \ \mu m$ , the maximum value is  $5.22 \times 10^{-21} \ A^2/Hz$  at 0.5Mrad dose and decreases to  $3.03 \times 10^{-18} \ A^2/Hz$  at 1 Mrad. Therefore, it appears that factors beyond those accounted for by carriers exchanging between border traps and the channel may be influencing the noise magnitude. We shall further analyze the generation mechanism of low-frequency noise at higher interface-trap densities.

**Figure 6.** Drain-current noise power density spectrum of 5 V NMOSFETs for geometries: (**a**)  $W/L = 10 \,\mu\text{m}/10 \,\mu\text{m}$  and (**b**)  $W/L = 10 \,\mu\text{m}/0.5 \,\mu\text{m}$  and 1.8 V NMOSFETs for geometries: (**c**)  $W/L = 10 \,\mu\text{m}/10 \,\mu\text{m}$ , (**d**)  $W/L = 10 \,\mu\text{m}/0.18 \,\mu\text{m}$  and (**e**)  $W/L = 1.8 \,\mu\text{m}/0.18 \,\mu\text{m}$  at different irradiation doses. All devices were irradiated up to 1 Mrad(Si) under the "on" bias condition. Noise measurements were carried out when  $V_{\rm gs} - V_{\rm th} = 0.3$ V and  $V_{\rm ds} = 0.1$ V.

The origin of low-frequency noise has been attributed to the number fluctuations of carriers in the channel [18,29]. However, there are various theories regarding the physical mechanism that is responsible for this fluctuation. One theory suggests that carriers are temporarily captured by border traps located in the oxide near the Si/SiO<sub>2</sub> interface (2–3 nm) before they are released back into the channel, which is widely accepted [26,30,31]. According to this theory, a positively charged border trap after irradiation is believed to be a stable state that can exchange a carrier with the channel [32,33]. However, this theory does not take into account the effect of interface traps on the exchange of carriers between border traps and the channel. Another theory proposes that carriers are captured by interface traps with a short time constant and emitted into their vicinity where they randomly wander for an extended period until they are recaptured by an interface trap and eventually released back into the channel [22]. However, this random walk concept only considers cases where there is no presence of an oxide layer or suitable traps in oxide layer, disregarding any effect from border traps.

**Figure 7.** Drain-current noise magnitudes at f = 10 Hz as a function of radiation dose. (a) 1.8 V NMOSFETs for geometries:  $W/L = 10 \ \mu\text{m}/10 \ \mu\text{m}$ ,  $10 \ \mu\text{m}/0.18 \ \mu\text{m}$  and  $1.8 \ \mu\text{m}/0.18 \ \mu\text{m}$ , and (b) 5 V NMOSFETs for geometries:  $W/L = 10 \ \mu\text{m}/10 \ \mu\text{m}$  and  $10 \ \mu\text{m}/0.5 \ \mu\text{m}$ . All devices were irradiated up to 1 Mrad(Si) in the "on" bias condition. Noise measurements were carried out when  $V_{\rm gs} - V_{\rm th} = 0.3$  V and  $V_{\rm ds} = 0.1$  V.

In our experiments, the magnitude of the low-frequency noise after irradiation is indeed higher than before irradiation, which can indicate that the low-frequency noise is related to the increased border traps in the oxide layer [18–20]. However, the experimental phenomenon that the magnitudes of low-frequency noise at high irradiation doses are lower than those at low irradiation doses cannot be explained by border traps in the oxide layer alone. Table 2 shows that as the irradiation dose increases, the number of both oxide traps and interface traps increase. Combining with the previous theoretical basis [19,22], we propose a new physical mechanism of low-frequency noise at high interface-trap density, which combines the roles of interface traps and border traps.

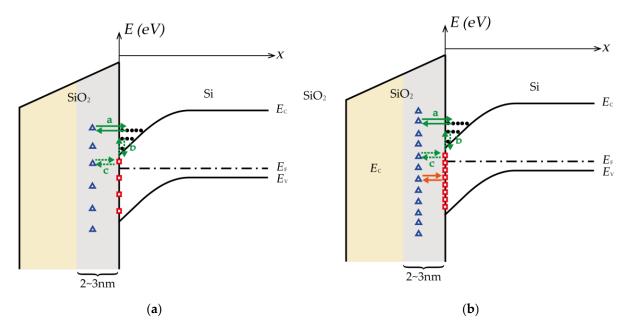

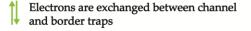

Figure 8 shows the physical processes of the origin of low-frequency noise in NMOS-FETs when exposed to pre-irradiation/lower-dose irradiation and higher-dose irradiation, as depicted in the energy band diagram. Figure 8a illustrates the mechanism of low-frequency noise generation under pre-irradiation/low-dose irradiation, wherein the interface-trap density is relatively low, and the source of low-frequency noise mainly originates from carrier exchange between the channel and border traps, resulting in fluctuation of carrier number in the channel. Consequently, at lower doses of irradiation, the factor that leads to an increase in the magnitude of low-frequency noise relative to before irradiation is mainly due to increased border traps. Figure 8b shows the mechanism of low-frequency noise generation at higher doses of irradiation, where both interface traps and border traps increase with increasing doses, which makes it more likely for carriers to exchange between interface traps and border traps. This kind of carrier exchange between interface trap and border trap is equivalent to reducing the number of border trap that should have exchanged carriers with the channel. Therefore, at higher doses of irradiation, increased interface trap has a certain degree of inhibitory effect on the low frequency noise generated by border trap.

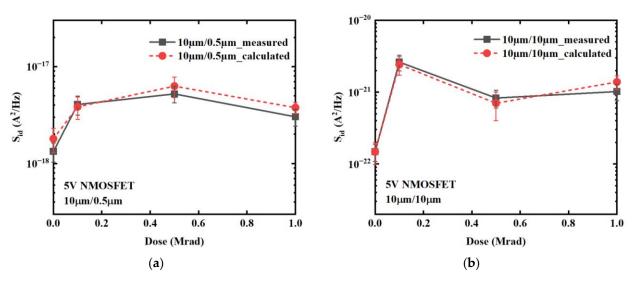

Figure 9 illustrates the schematic of low-frequency noise generation in nMOSFETs. Figure 9a displays the situation where interface traps have not yet inhibited the exchange of electrons between the channel and border traps, with the border-trap density alone resulting in the generation of low-frequency noise before/under lower-dose irradiation. Figure 9b depicts the situation under higher-dose irradiation, where interface traps have already hindered electron exchange between the channel and border traps, such that the density of border traps which actually contribute to generation of low-frequency noise is

equal to the total density of border traps minus the part which undergoes electron exchange with interface traps, as shown in Equation (6):

$$N'_{\rm bt} = N_{\rm bt} - P \cdot N_{\rm it} \tag{6}$$

where  $N'_{bt}$  is the density of border traps which actually contribute to generation of lowfrequency noise,  $N_{bt}$  is the total border-trap density,  $N_{it}$  is the interface-trap density, and Pis the proportion of interface traps that exchange electrons with border traps to the total interface traps.

- $\triangle$  border trap  $\implies$  a Tunneling between the channel and border traps.

- interface trap

• electron

**Tunneling between the channel and border traps** with interface traps which act as intermediate states.

Tunneling between interface traps and border traps.

**Figure 8.** The physical processes of the origin of low-frequency noise in NMOSFETs under (**a**) preirradiation/lower-dose irradiation and (**b**) higher-dose irradiation in the energy band diagram.

Therefore, based on the physical mechanism of low-frequency noise generation described above in the case of high interface-trap density, the first-order tunneling model of low-frequency noise at high interface-trap density should be modified accordingly. The  $D_{bt}(E_f)$  in Equation (4) should be replaced with the  $D_{bt}'(E_f)$  which is the density of border traps that truly contribute to low-frequency noise at Fermi level, as shown in the following equation:

$$D'_{\rm bt}(E_{\rm f}) \approx \frac{N'_{\rm bt}}{E_{\rm g}}$$

(7)

where  $N_{bt}$  is the density of border traps that truly contribute to low-frequency noise, as shown in Equation (6), and  $E_g$  is the energy band gap width. Then the expression of first-order tunneling model should accordingly be modified to the following expression:

$$S_{\rm vd} = \frac{q^2}{C_{\rm ox}^2} \frac{V_{\rm D}^2}{(V_{\rm G} - V_{\rm th})^2} \frac{k_{\rm B} T D_{\rm bt}'(E_{\rm f})}{L W \ln(\tau_1 / \tau_0)} \frac{1}{f}$$

(8)

- Electrons are exchanged between channel

- and border traps with intermediate states

- Electrons are exchanged between interface traps and border traps

Si

(a)

- Electrons

- A Border traps

- Interface traps that exchange electrons with border traps

- □ Interface traps that are intermediate states when electrons are exchanged between the channel and border traps

D)

**Figure 9.** Illustration of low-frequency noise generation in NMOSFETs (**a**) before/under lower-dose irradiation, (**b**) under higher-dose irradiation.

Equations (6)–(8) indicate that two additional parameters, P and  $N_{bt}$ , are required to quantify the magnitude of low-frequency noise. It has been observed that the trend of  $\Delta N_{bt}$  and  $\Delta N_{ot}$  both increase with increasing irradiation dose, implying that the ratio of  $\Delta N_{bt}$  to  $\Delta N_{ot}$  is a constant value [34]. Here, we use the  $\Delta N_{bt}/\Delta N_{bt}$  of 18% to characterize the low-frequency noise magnitude of 5 V devices, which is consistent with previous measurements [34]. Additionally, as irradiation dose increases, P, the proportion of interface traps that exchange electrons with border traps to the total interface traps also increases. The P and  $\Delta N_{bt}/\Delta N_{ot}$  used for validating our low-frequency noise mechanism are provided in Table 3.

**Table 3.**  $\Delta N_{\rm bt}/\Delta N_{\rm ot}$  of the 5 V NMOSFETs under test and proportion of interface traps that exchange carriers with border traps to the total interface traps.

| Dose (Mrad) | $\Delta N_{\rm bt}/\Delta N_{\rm ot}$ | Р   |

|-------------|---------------------------------------|-----|

| 0.1         | 18%                                   | 5%  |

| 0.5         | 18%                                   | 22% |

| 1           | 18%                                   | 31% |

The border-trap density,  $N_{bt}$ , can be expressed as  $N_{bt} = N_{bt0} + \Delta N_{bt}$ , where  $N_{bt0} \approx N_{bt0'}$ is the initial density of border traps before irradiation and can be calculated using Equations (7) and (8) with pre-irradiation noise magnitude and an assumed  $\tau_1/\tau_0$  ratio of ~10<sup>12</sup> [9]. For 10 µm/10 µm and 10 µm/0.5 µm devices, the values of  $N_{bt0}$  are  $2.40 \times 10^8 \text{ cm}^{-2}$  and  $1.71 \times 10^9 \text{ cm}^{-2}$  respectively. The interface-trap density is rough ~10<sup>9</sup> cm<sup>-2</sup> prior to irradiation, which is an order of magnitude smaller than after irradiation, thus  $N_{it} \approx \Delta N_{it}$  post irradiation. By utilizing Equations (5)–(8), the low-frequency noise magnitude as a function of dose was calculated using the low-frequency noise magnitude before irradiation, data from Table 2, and parameters from Table 3. Figure 10 presents the magnitude of noise at 10 Hz for 5 V NMOSFETs as a function of radiation dose, which were both measured and calculated under the physical mechanism established in this study. Figure 10 demonstrates that the trend of low-frequency noise magnitudes calculated

through this physical mechanism is consistent with that observed in the measured values, thus confirming the correctness and efficacy of this proposed physical mechanism.

**Figure 10.** Noise magnitudes at f = 10 Hz of 5 V NMOSFETs for geometries: (a)  $W/L = 10 \mu m/0.5 \mu m$  and (b) 10  $\mu m/10 \mu m$  as a function of irradiation dose which are measured and calculated under the modified physical mechanism.

Therefore, this new physical mechanism can explain the low-frequency noise magnitude as a function of irradiation dose in our experiment. Before irradiation and at a dose of 0.1 Mrad, the low-density interface traps had little effect on the exchange of carriers between the channel and border traps, thus making the main source of impact on low-frequency noise still that of increased border traps. As the dose increased, however, this exchange was partially suppressed by the increased interface traps, resulting in lower magnitudes of low-frequency noise at higher doses compared to those seen at lower doses. Furthermore, for certain devices, the dose at which their noise magnitude attained its maximum is greater than that observed for other devices. This is due to the fact that, despite some carriers exchanging between border traps and interface traps at this dose, the density of border traps that truly contributed to carrier number fluctuation in the channel at this dose is higher than that at lower doses. The low-frequency noise magnitudes of some devices increase at 1 Mrad for the same reason.

### 4. Conclusions

We have conducted a comprehensive investigation into the low-frequency noise of SOI-NMOSFETs across varied irradiation doses. The measurements indicate that the low-frequency noise magnitudes of all devices tend to see an increase, then decrease with increasing irradiation dose, suggesting that the density of border traps is no longer the only deciding factor in the low-frequency noise magnitude at higher irradiation doses. We point out that the enhanced interface traps cause more carriers to exchange between the interface traps and border traps, thereby suppressing the exchange of carriers between the channel and border traps, which results in the lower magnitude of low-frequency noise at higher irradiation doses. This research provides an important understanding of the physical mechanism of low-frequency noise with high interface-trap density, as well as relevant guidance for low-noise circuit designs in irradiated environments.

Author Contributions: Conceptualization, R.L. and J.B.; methodology, R.L., J.W., T.N. and L.G.; validation, R.L., D.L. and C.Z.; formal analysis, R.L.; investigation, R.L.; resources, C.Z.; data curation, R.L.; writing—original draft preparation, R.L.; writing—review and editing, R.L., Y.L., R.W., B.L. and C.Z.; supervision, J.L.; project administration, J.L. and C.Z. All authors have read and agreed to the published version of the manuscript.

12 of 13

Funding: This research received no external funding.

**Conflicts of Interest:** The authors declare no conflict of interest.

# References

- Simoen, E.; Gaillardin, M.; Paillet, P.; Reed, R.A.; Schrimpf, R.D.; Alles, M.L.; El-Mamouni, F.; Fleetwood, D.M.; Griffoni, A.; Claeys, C. Radiation Effects in Advanced Multiple Gate and Silicon-on-Insulator Transistors. *IEEE Trans. Nucl. Sci.* 2013, 60, 1970–1991. [CrossRef]

- 2. de Boissac, C.L.-M.; Abouzeid, F.; Malherbe, V.; Gasiot, G.; Roche, P.; Autran, J.-L. Influence of Supply Voltage and Body Biasing on Single-Event Upsets and Single-Event Transients in UTBB FD-SOI. *IEEE Trans. Nucl. Sci.* **2021**, *68*, 850–856. [CrossRef]

- Aditya, K.; Jha, C.K.; Basra, S.; Jatana, H.S.; Dixit, A. Transient Response of 0.18 Mm SOI MOSFETs and SRAM Bit-Cells to Heavy-Ion Irradiation for Variable SOI Film Thickness. *IEEE Trans. Electron Devices* 2018, 65, 4826–4833. [CrossRef]

- 4. Haraszti, T.P.; Pancholy, R.; Chona, J.; Schober, R.; Hunt, K. Novel SOI-Specific Circuit Form High-Speed Radiation-Hardened Memories. In Proceedings of the 2008 IEEE International SOI Conference, New Paltz, NY, USA, 6–9 October 2008; pp. 133–134.

- Richards, E.W.; Loveless, T.D.; Kauppila, J.S.; Haeffner, T.D.; Holman, W.T.; Massengill, L.W. Radiation Hardened by Design Subsampling Phase-Locked Loop Techniques in PD-SOI. *IEEE Trans. Nucl. Sci.* 2020, 67, 1144–1151. [CrossRef]

- 6. Šiprak, D.; Tiebout, M.; Zanolla, N.; Baumgartner, P.; Fiegna, C. Noise Reduction in CMOS Circuits through Switched Gate and Forward Substrate Bias. *IEEE J. Solid-State Circuits* **2009**, *44*, 1959–1967. [CrossRef]

- Bonaldo, S.; Mattiazzo, S.; Enz, C.; Baschirotto, A.; Fleetwood, D.M.; Paccagnella, A.; Gerardin, S. Ionizing-Radiation Response and Low-Frequency Noise of 28-Nm MOSFETs at Ultrahigh Doses. *IEEE Trans. Nucl. Sci.* 2020, 67, 1302–1311. [CrossRef]

- Bonaldo, S.; Gorchichko, M.; Zhang, E.X.; Ma, T.; Mattiazzo, S.; Bagatin, M.; Paccagnella, A.; Gerardin, S.; Schrimpf, R.D.; Reed, R.A.; et al. TID Effects in Highly Scaled Gate-All-around Si Nanowire CMOS Transistors Irradiated to Ultrahigh Doses. *IEEE Trans. Nucl. Sci.* 2022, 69, 1444–1452. [CrossRef]

- 9. Ding, J.; Zhang, E.X.; Li, K.; Luo, X.; Gorchichko, M.; Fleetwood, D.M. Aging Effects and Latent Interface-Trap Buildup in MOS Transistors. *IEEE Trans. Nucl. Sci.* 2021, *68*, 2724–2735. [CrossRef]

- Gorchichko, M.; Cao, Y.R.; Zhang, E.X.; Yan, D.W.; Gong, H.Q.; Zhao, S.M.E.; Wang, P.; Jiang, R.; Liang, C.D.; Fleetwood, D.M.; et al. Total-Ionizing-Dose Effects and Low-Frequency Noise in 30-Nm Gate-Length Bulk and SOI FinFETs with SiO2/HfO2 Gate Dielectrics. *IEEE Trans. Nucl. Sci.* 2020, 67, 245–252. [CrossRef]

- 11. Ratti, L.; Gaioni, L.; Manghisoni, M.; Traversi, G.; Pantano, D. Investigating Degradation Mechanisms in 130 nm and 90 nm Commercial CMOS Technologies Exposed to up to 100 Mrad Ionizing Radiation Dose. *Proc. Eur. Conf. Radiat. Its Eff. Compon. Syst. RADECS* 2007, 55, 1992–2000. [CrossRef]

- 12. Re, V.; Gaioni, L.; Manghisoni, M.; Ratti, L.; Traversi, G. Comprehensive Study of Total Ionizing Dose Damage Mechanisms and Their Effects on Noise Sources in a 90 Nm CMOS Technology. *IEEE Trans. Nucl. Sci.* **2008**, *55*, 3272–3279. [CrossRef]

- 13. Ratti, L.; Gaioni, L.; Manghisoni, M.; Re, V.; Traversi, G. TID-Induced Degradation in Static and Noise Behavior of Sub-100 Nm Multifinger Bulk NMOSFETs. *IEEE Trans. Nucl. Sci.* 2011, 58, 776–784. [CrossRef]

- 14. Li, K.; Zhang, E.X.; Gorchichko, M.; Wang, P.F.; Reaz, M.; Zhao, S.E.; Hiblot, G.; Van Huylenbroeck, S.; Jourdain, A.; Alles, M.L.; et al. Impacts of Through-Silicon Vias on Total-Ionizing-Dose Effects and Low-Frequency Noise in FinFETs. *IEEE Trans. Nucl. Sci.* **2021**, *68*, 740–747. [CrossRef]

- 15. Re, V.; Gaioni, L.; Manghisoni, M.; Ratti, L.; Riceputi, E.; Traversi, G. Ionizing Radiation Effects on the Noise of 65 Nm CMOS Transistors for Pixel Sensor Readout at Extreme Total Dose Levels. *IEEE Trans. Nucl. Sci.* **2018**, *65*, 550–557. [CrossRef]

- 16. Van Der Ziel, A. Unified Presentation of 1/f Noise in Electronic Devices: Fundamental 1/f Noise Sources. *Proc. IEEE* **1988**, *76*, 233–258. [CrossRef]

- 17. Simoen, E.; Claeys, C. On the Flicker Noise in Submicron Silicon MOSFETs. Solid. State. Electron. 1999, 43, 865–882. [CrossRef]

- 18. McWhorter, A.L. 1/f Noise and Germanium Surface Properties. Semicond. Surf. Phys. 1957, 207, 207–228.

- 19. Fu, H.S.; Sah, C.T. Theory and Experiments on Surface 1/f Noise. IEEE Trans. Electron Devices 1972, 19, 273–285. [CrossRef]

- 20. Dutta, P.; Horn, P.M. Low-Frequency Fluctuations in Solids: 1/f Noise. Rev. Mod. Phys. 1981, 53, 497-516. [CrossRef]

- 21. Jäntsch, O. A Theory of 1/f Noise at Semiconductor Surfaces. Solid State Electron. 1968, 11, 267–272. [CrossRef]

- 22. Jäntsch, O. Flicker (1/f) Noise Generated by a Random Walk of Electrons in Interfaces. *IEEE Trans. Electron Devices* **1987**, 34, 1100–1115. [CrossRef]

- 23. Ortiz-Conde, A.; Garcia-Sanchez, F.J.; Muci, J.; Barrios, A.T.; Liou, J.J.; Ho, C.-S. Revisiting MOSFET Threshold Voltage Extraction Methods. *Microelectron. Reliab.* **2013**, *53*, 90–104. [CrossRef]

- 24. McWhorter, P.J.; Winokur, P.S. Simple Technique for Separating the Effects of Interface Traps and Trapped-Oxide Charge in Metal-Oxide-Semiconductor Transistors. *Appl. Phys. Lett.* **1986**, *48*, 133–135. [CrossRef]

- 25. Fleetwood, D.M. Reliability Limiting Defects in MOS Gate Oxides: Mechanisms and Modeling Implications. *IEEE Int. Reliab. Phys. Symp. Proc.* **2019**, 1–10.

- 26. Scofield, J.H.; Fleetwood, D.M. Physical Basis for Nondestructive Tests of MOS Radiation Hardness. *IEEE Trans. Nucl. Sci.* **1991**, 38, 1567–1577. [CrossRef]

- 27. Fleetwood, D.M. Total-Ionizing-Dose Effects, Border Traps, and 1/f Noise in Emerging MOS Technologies. *IEEE Trans. Nucl. Sci.* **2020**, *67*, 1216–1240. [CrossRef]

- Fleetwood, D.M.; Meisenheimer, T.L.; Schofield, J.H. 1/f Noise and Radiation Effects in MOS Devices. *IEEE Trans. Electron Devices* 1994, 41, 1953–1964. [CrossRef]

- 29. Chang, J.; Abidi, A.A.; Viswanathan, C.R. Flicker Noise in CMOS Transistors from Subthreshold to Strong Inversion at Various Temperatures. *IEEE Trans. Electron Devices* **1994**, *41*, 1965–1971. [CrossRef]

- Christensson, S.; Lundstrm, I.; Svensson, C. Low Frequency Noise in MOS Transistors—I Theory. Solid. State. Electron. 1968, 11, 797–812. [CrossRef]

- Hsu, S.T.; Fitzgerald, D.J.; Grove, A.S. Surface-state Related l/f Noise in P-n Junctions and MOS Transistors. *Appl. Phys. Lett.* 1968, 12, 287–289. [CrossRef]

- Lelis, A.J.; Oldham, T.R.; Boesch, H.E.; McLean, F.B. The Nature of the Trapped Hole Annealing Process. *IEEE Trans. Nucl. Sci.* 1989, 36, 1808–1815. [CrossRef]

- 33. Grasser, T. Stochastic Charge Trapping in Oxides: From Random Telegraph Noise to Bias Temperature Instabilities. *Microelectron. Reliab.* **2012**, *52*, 39–70. [CrossRef]

- 34. Fleetwood, D.M.; Shaneyfelt, M.R.; Schwank, J.R. Estimating Oxide-Trap, Interface-Trap, and Border-Trap Charge Densities in Metal-Oxide-Semiconductor Transistors. *Appl. Phys. Lett.* **1994**, *64*, 1965–1967. [CrossRef]

**Disclaimer/Publisher's Note:** The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content.