Simulation Model Development for Packaged Cascode Gallium Nitride Field-Effect Transistors

Abstract

:1. Introduction

2. Materials and Methods

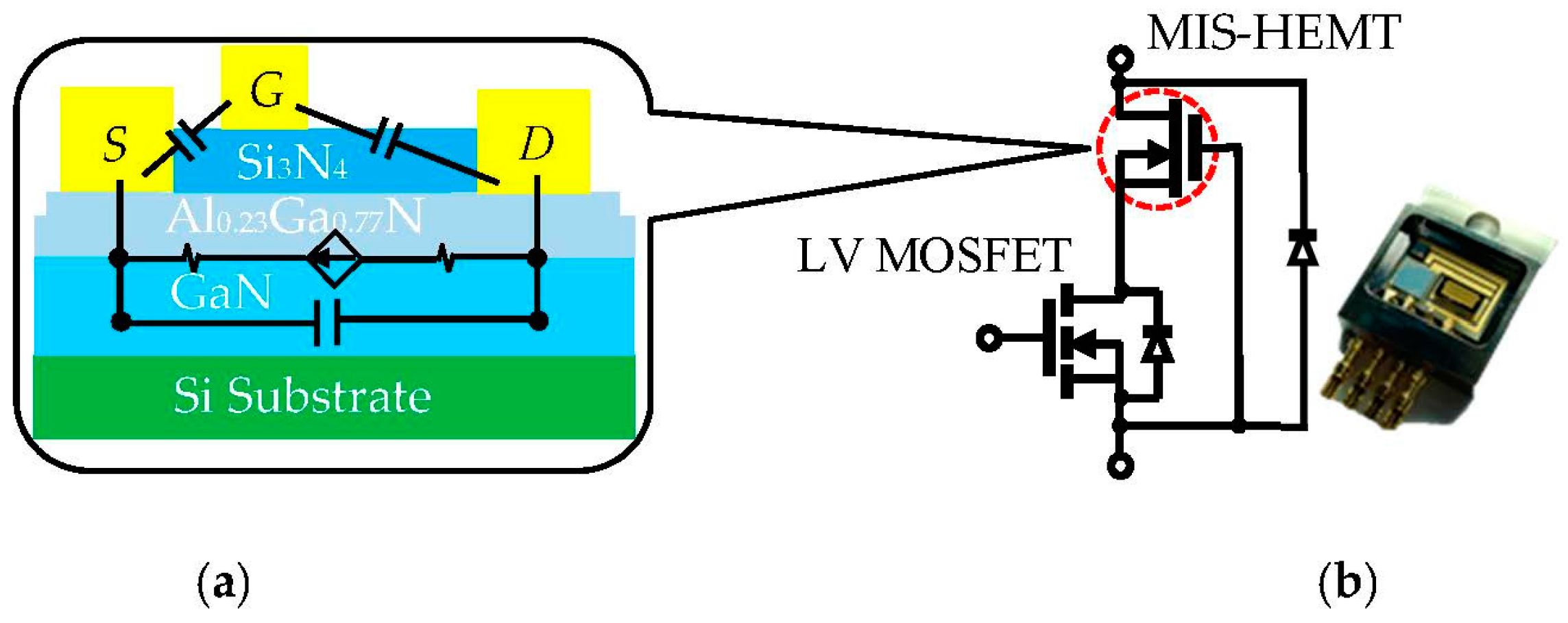

2.1. Device Structure of the Fabricated MIS-HEMT and Cascode Package

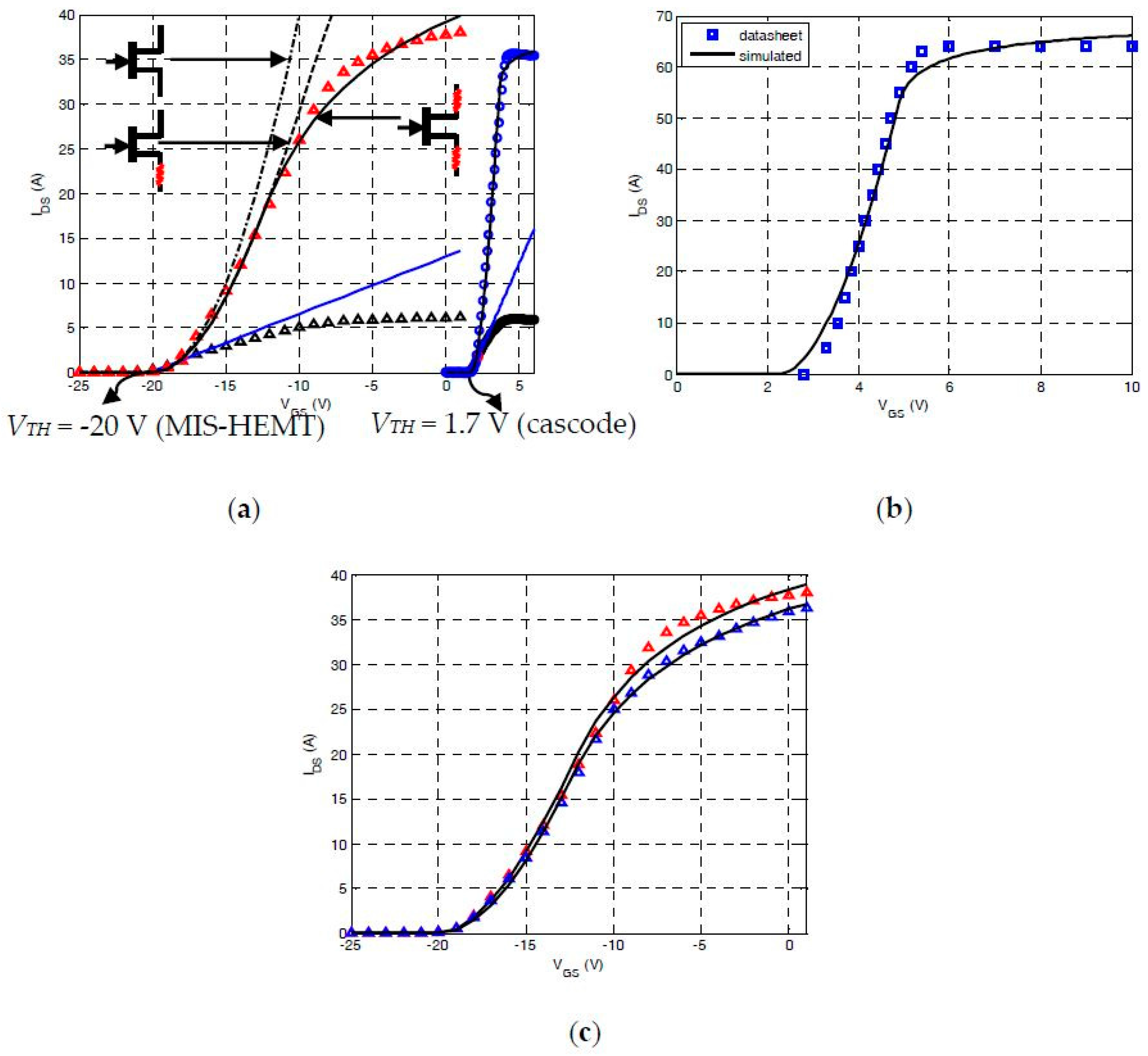

2.2. Static Characteristics

2.2.1. MIS-HEMT and LV MOSFET Transfer Curve Characteristics

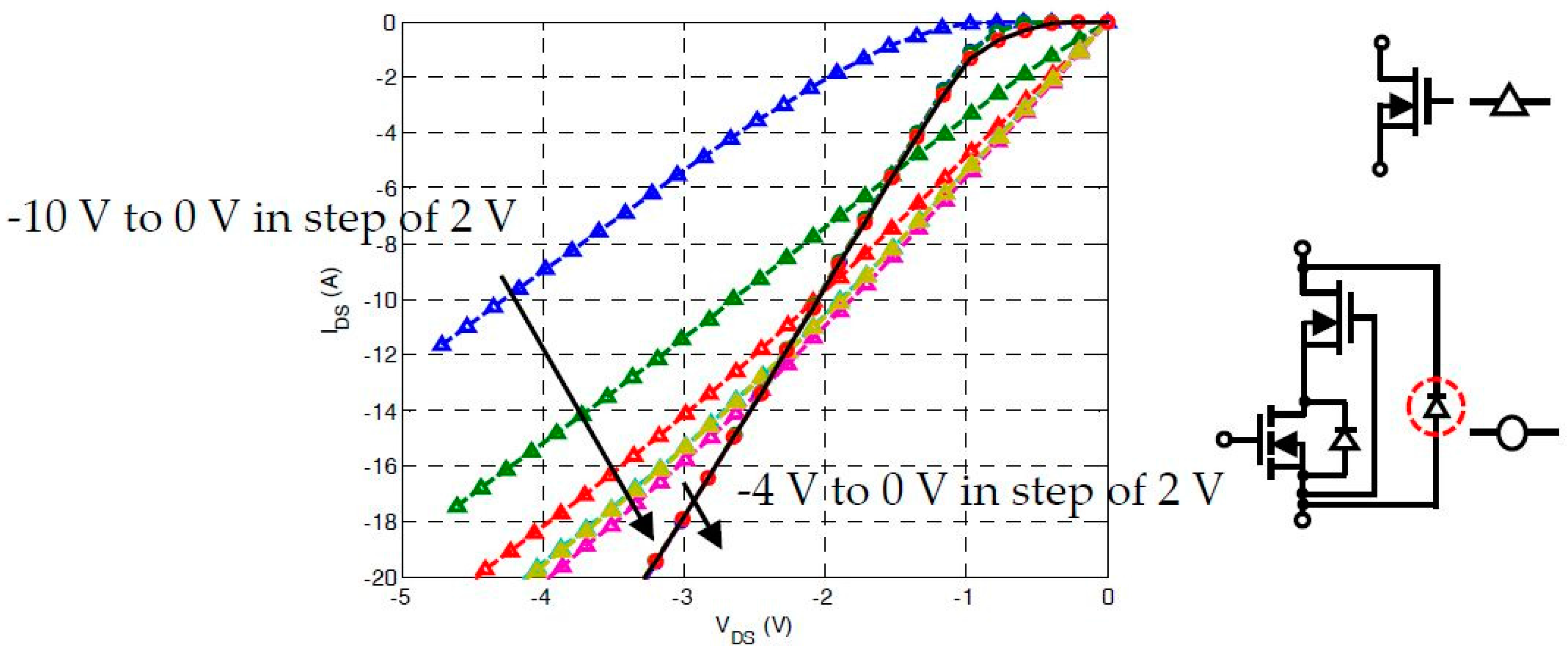

2.2.2. Third-Quadrant Characteristics

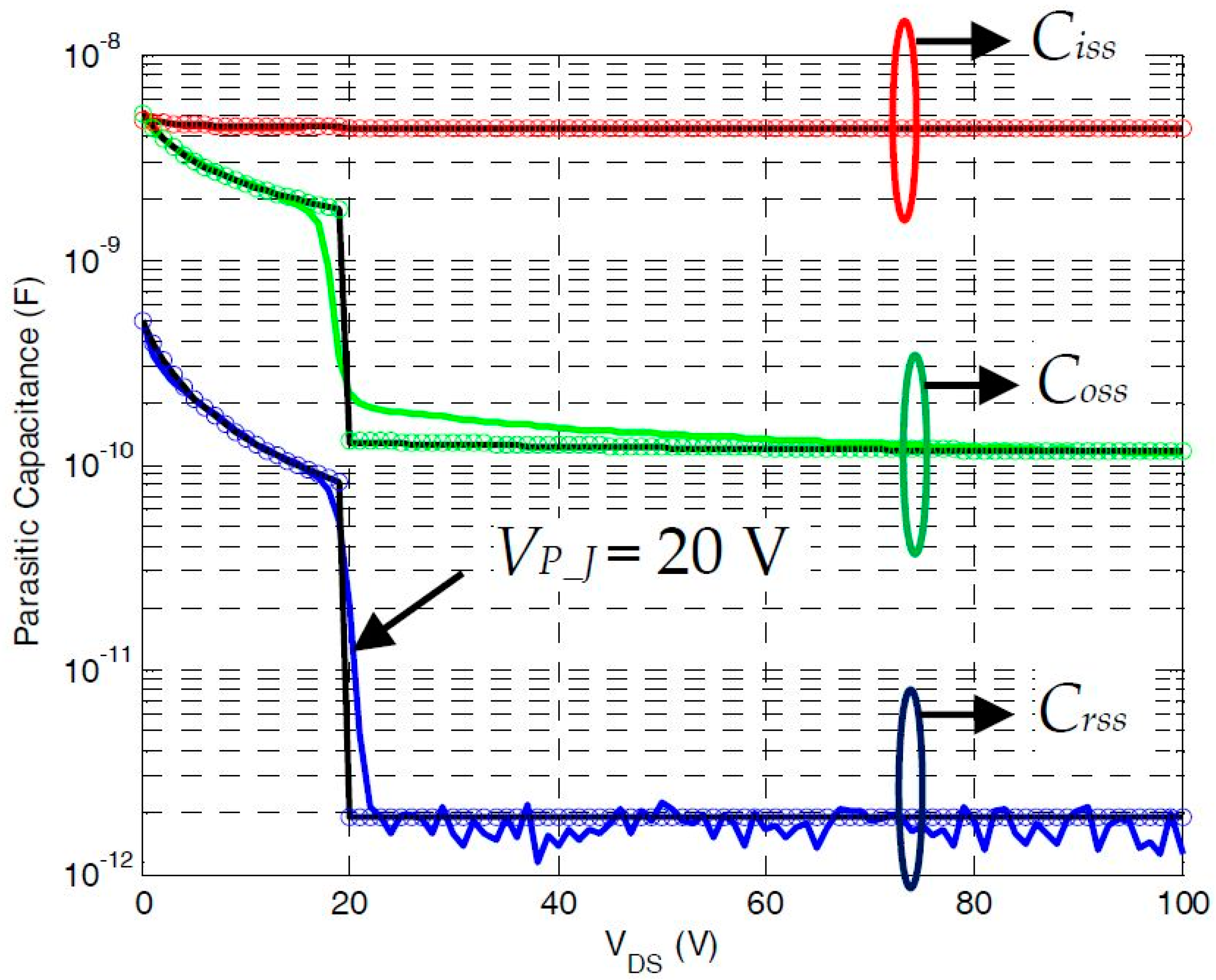

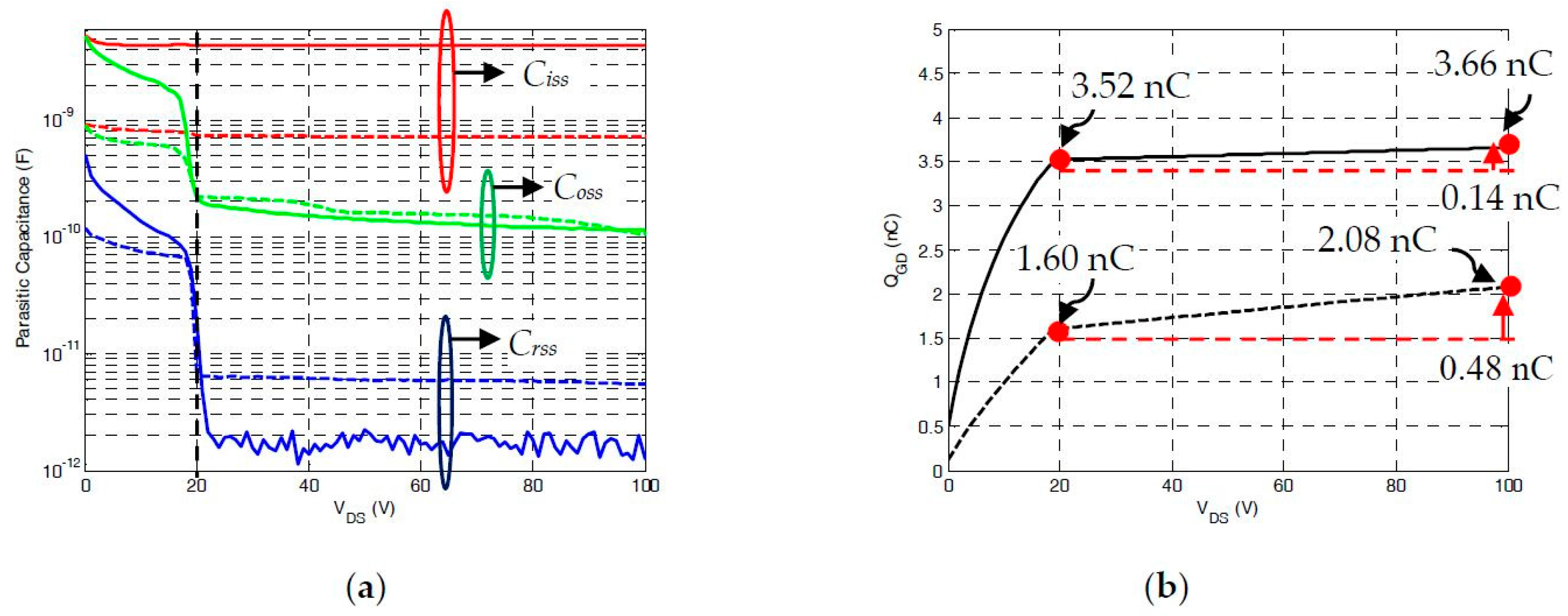

2.2.3. Parasitic Capacitances

2.3. Analysis of the Cascode Parasitic Capacitances

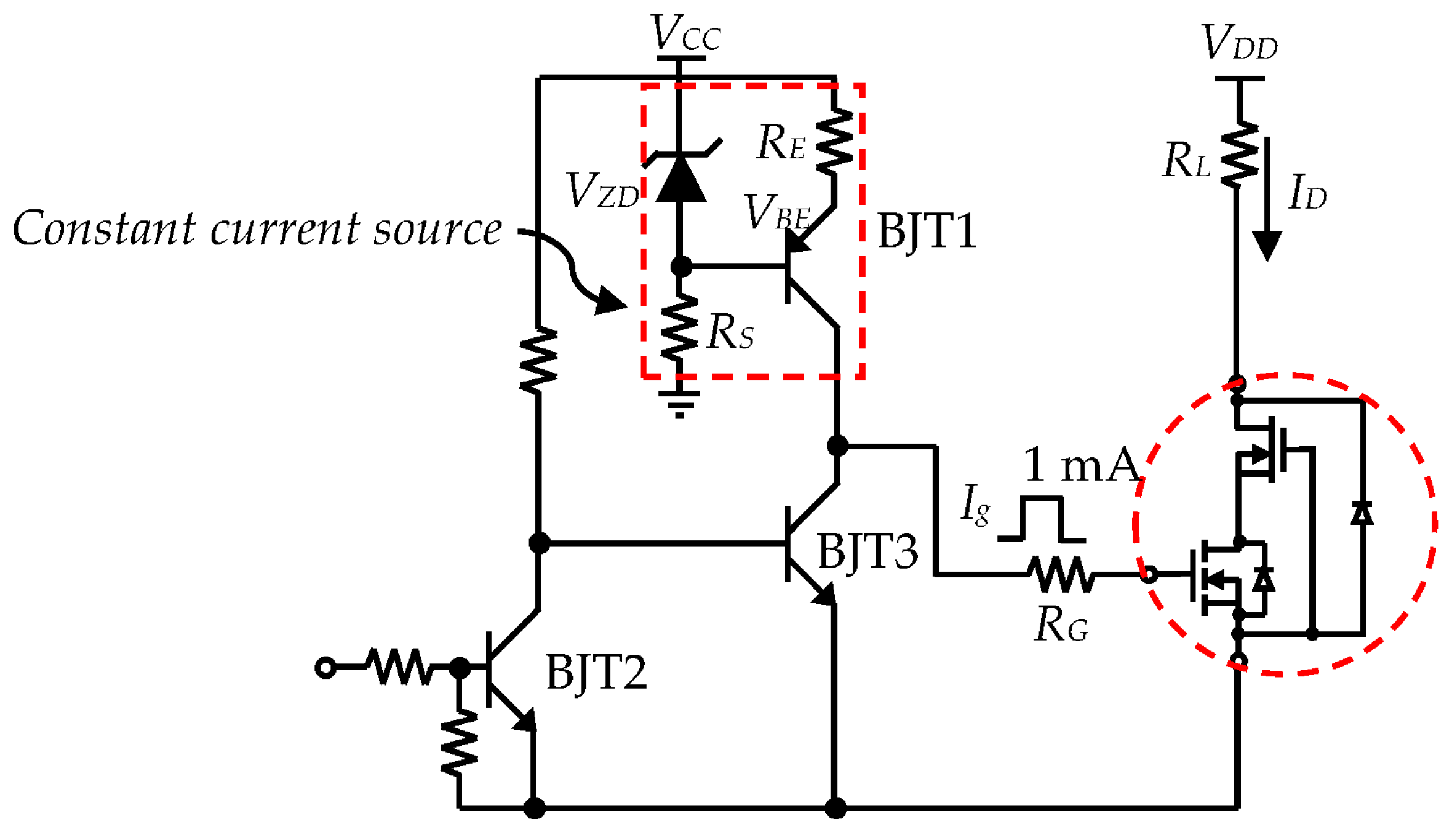

2.4. Dynamic Characteristics

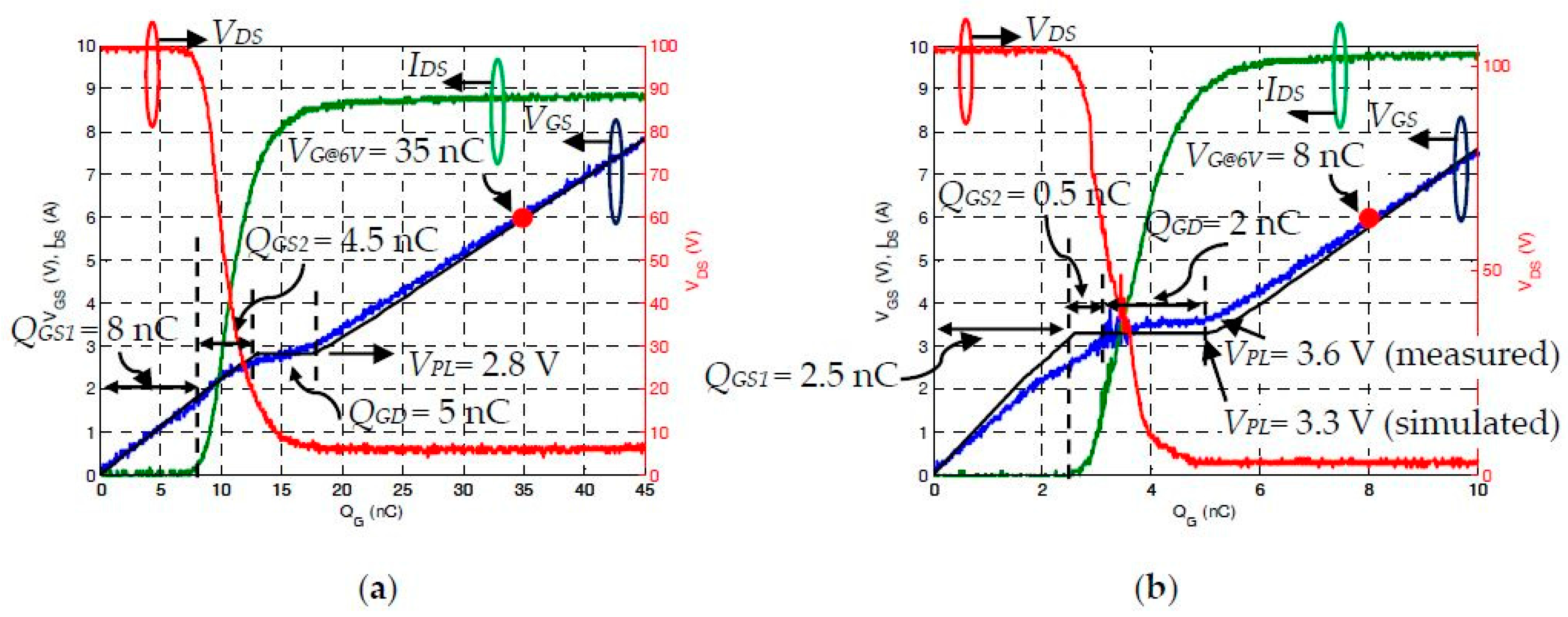

2.4.1. Gate Charge Curve (VGS–QGS)

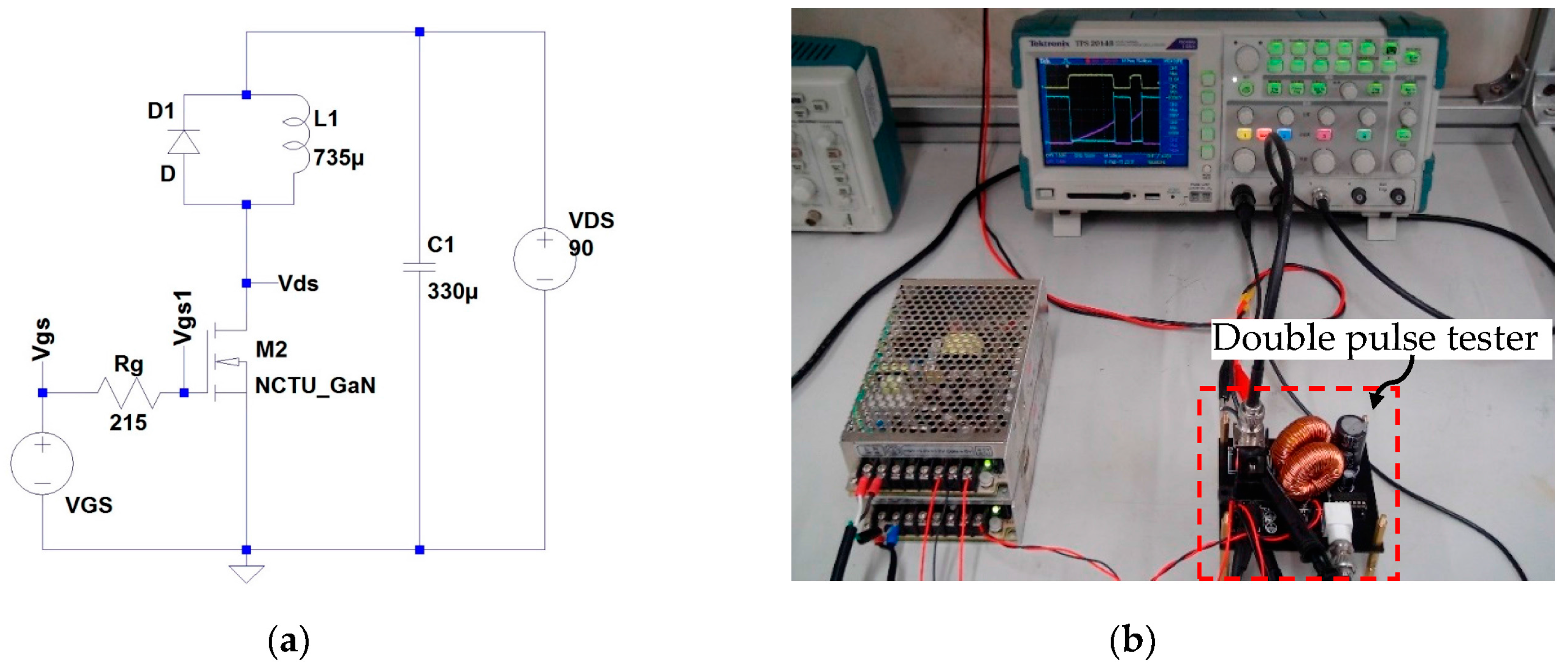

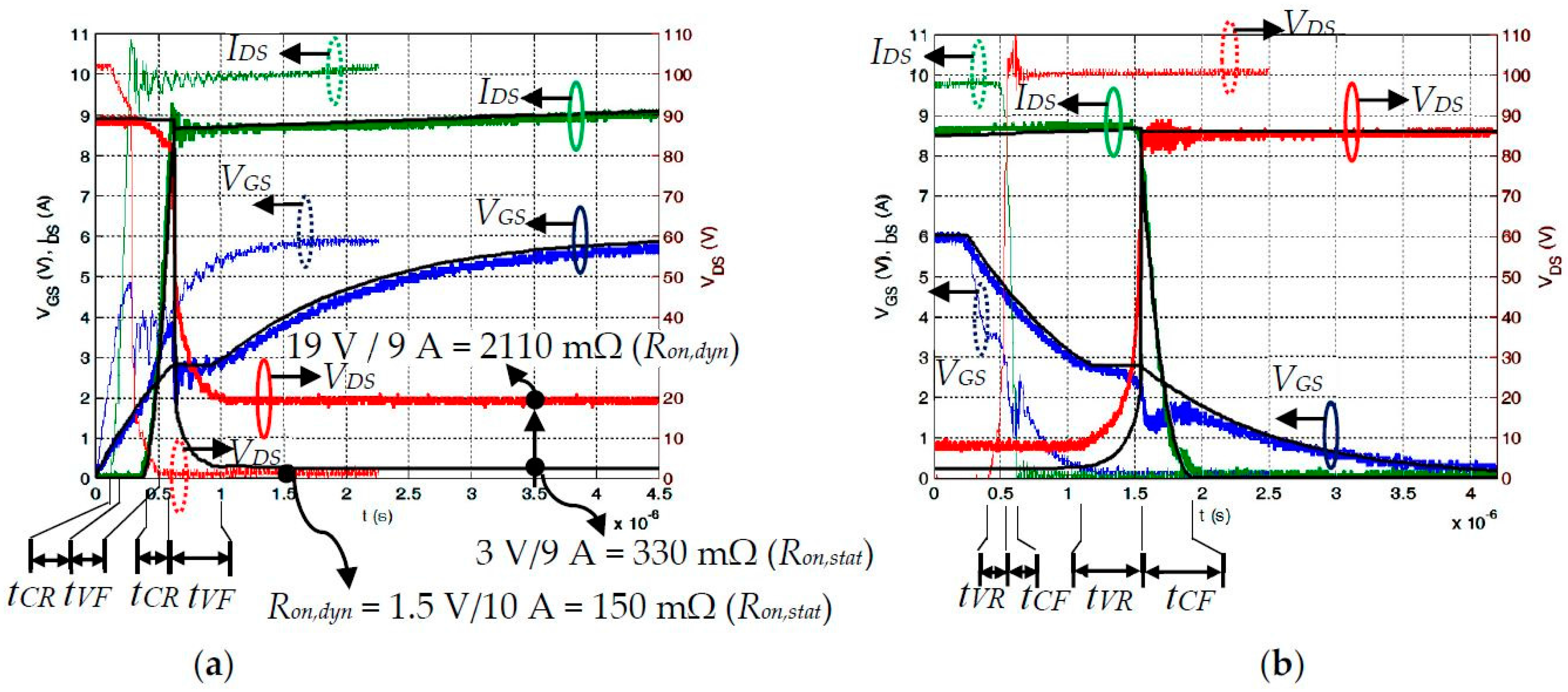

2.4.2. Switching Performance with the Double-Pulse Tester

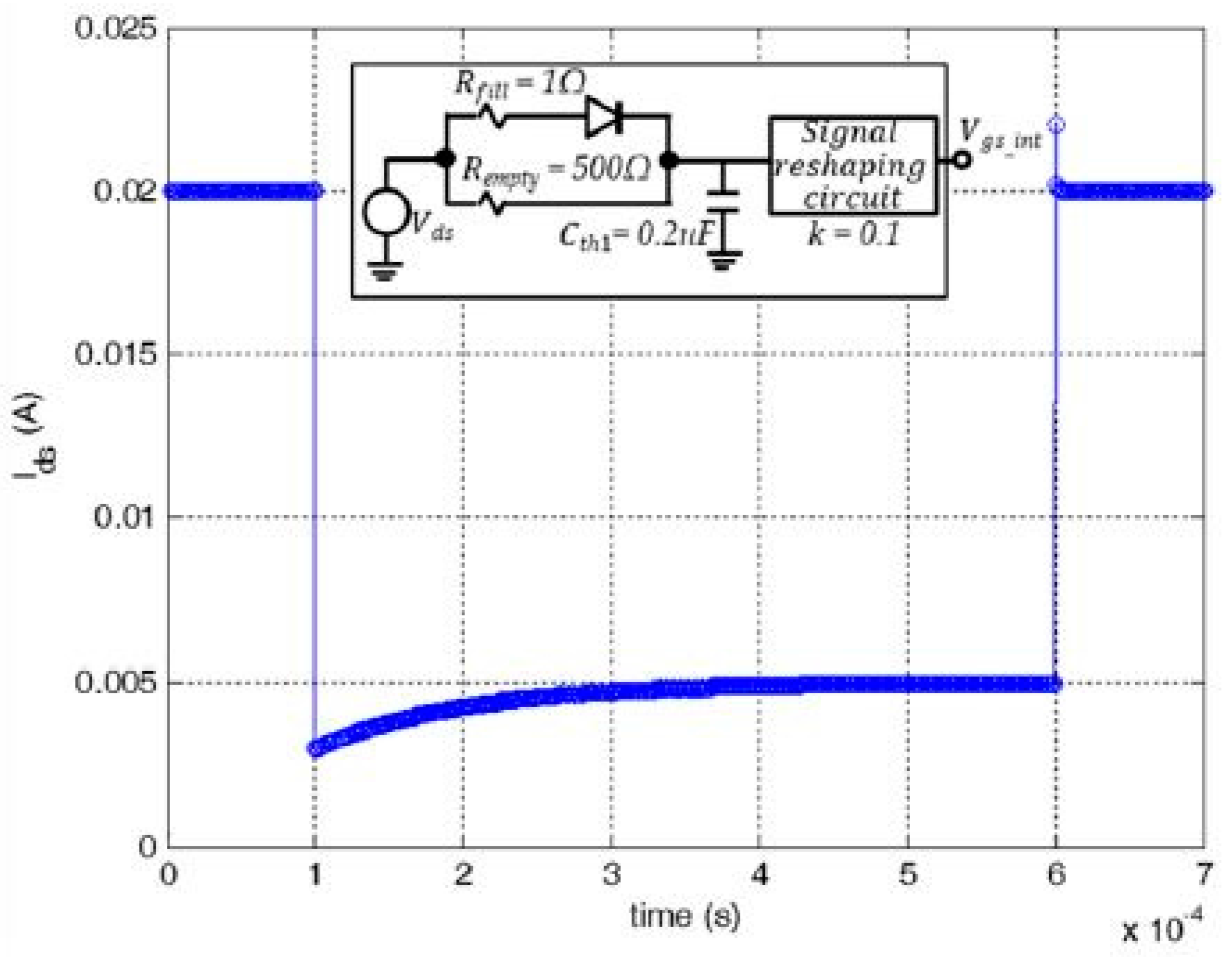

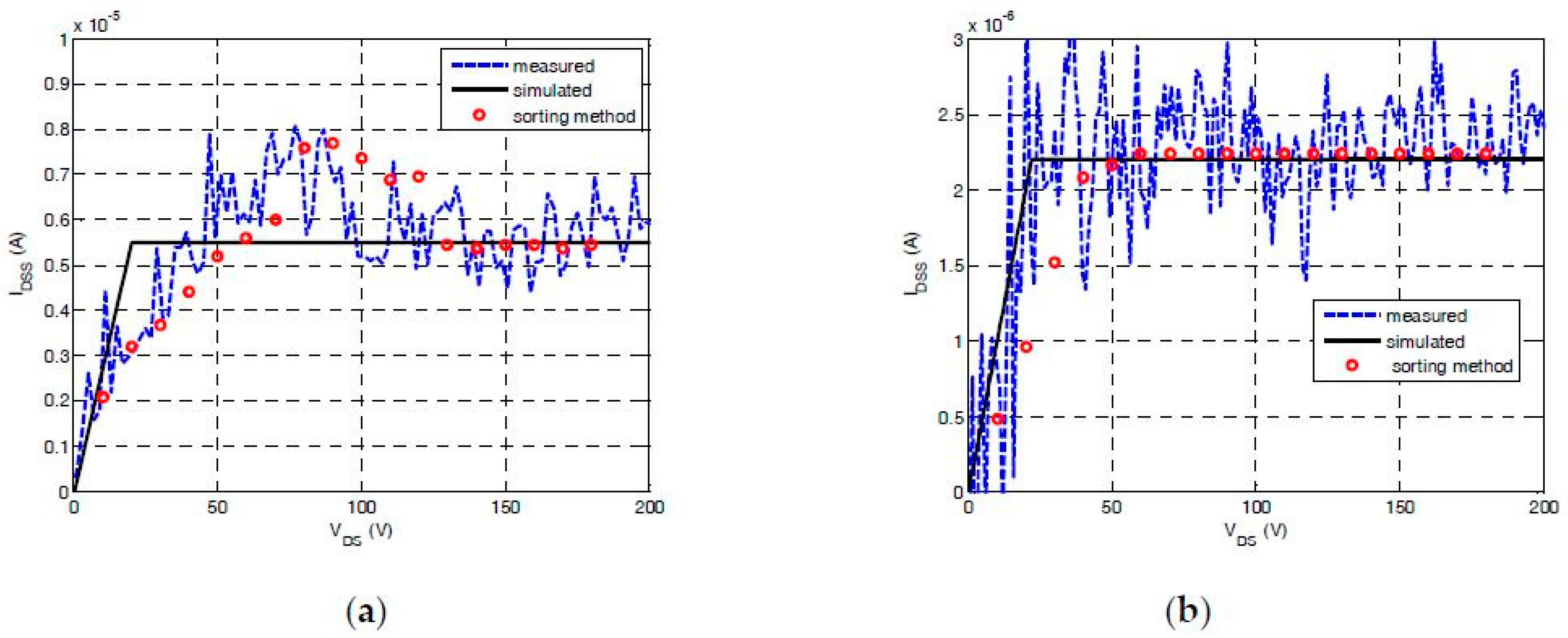

2.4.3. Leakage Current and Turn-Off Resistance

3. Discussion

4. Conclusions

Acknowledgments

Author Contributions

Conflicts of Interest

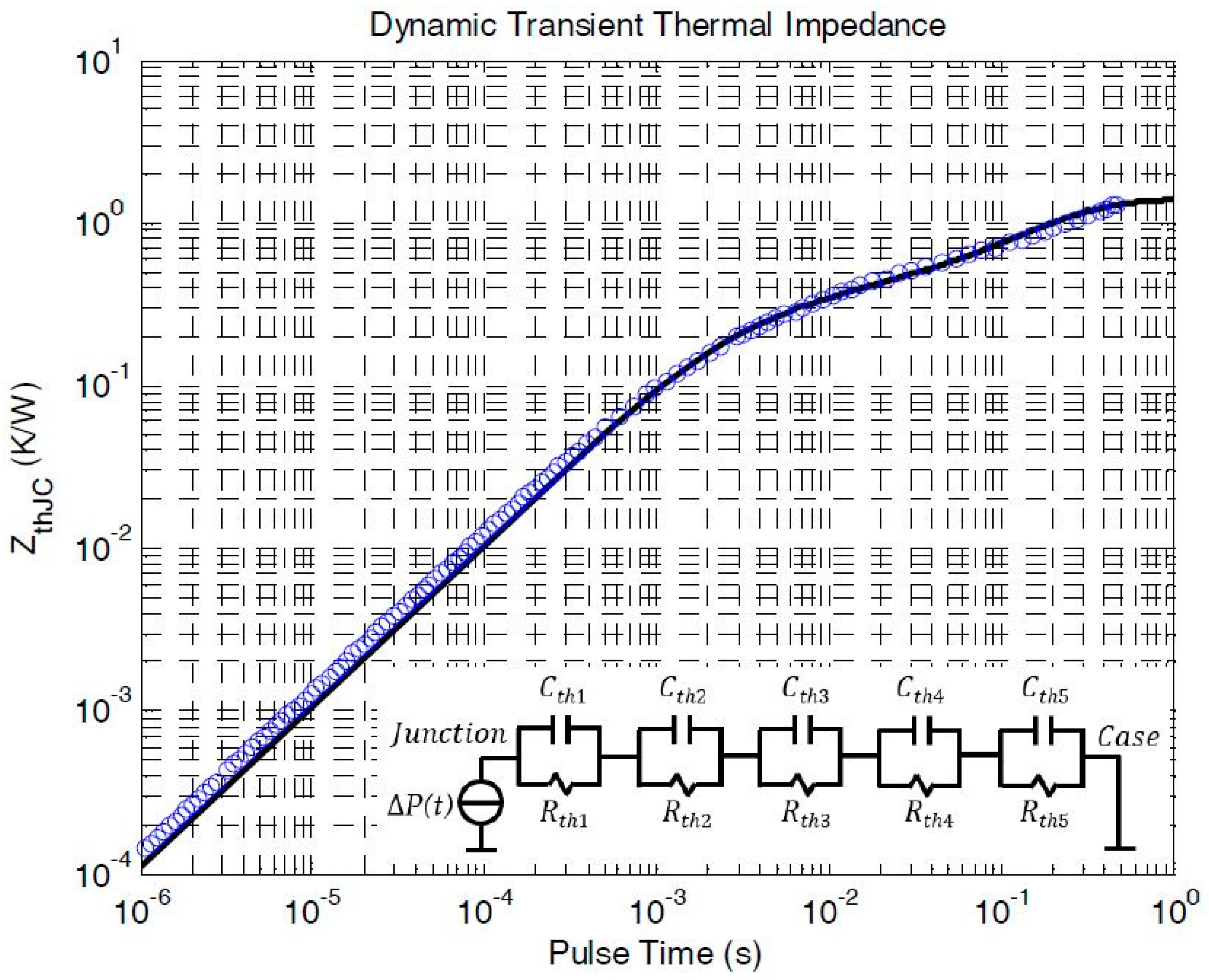

Appendix A

| 1 | 2 | 3 | 4 | 5 | |

|---|---|---|---|---|---|

| Rth (Ω) | 0.1596 | 0.1869 | 0.2476 | 0.3043 | 0.5016 |

| Cth (F) | 0.0083 | 0.0021 | 0.2066 | 0.2065 | 0.2092 |

Appendix B

| Sym. | Parameter | Test Conditions | Typ. | Unit |

|---|---|---|---|---|

| Static | ||||

| VDSS-MAX | Maximum Drain-Source Voltage | VGS = 0 V | 600 (Min) | V |

| ID25 °C | Continuous Drain Current @ TC = 25 °C | - | 17 | A |

| VGS(th) | Gate Threshold Voltage | VDS = VGS, ID = 1 mA | 1.8 | V |

| RDS(on) | Drain-Source On-Resistance (TJ = 25 °C) | VGS = 8 V, ID = 11 A, TJ = 25 °C | 0.15 | Ω |

| Dynamic | ||||

| CISS | Input Capacitance | VGS = 0 V, VDS = 100 V, f = 1 MHz | 740 | pF |

| COSS | Output Capacitance | 133 | ||

| CRSS | Reverse Transfer Capacitance | 3.6 | ||

| Qg | Total Gate Charge | VDS = 100 V, VGS = 0–4.5 V, ID = 11 A | 6.2 | nC |

| Qgs | Gate-Source Charge | 2.1 | ||

| Qgd | Gate-Drain Charge | 2.2 | ||

Appendix C

References

- Jones, E.A.; Wang, F.F.; Costinett, D. Review of Commercial GaN Power Devices and GaN-Based Converter Design Challenges. IEEE J. Emerg. Sel. Top. Power Electron. 2016, 4, 707–719. [Google Scholar] [CrossRef]

- Santi, E.; Peng, K.; Mantooth, H.A.; Hudgins, J.L. Modeling of Wide-Bandgap Power Semiconductor Devices—Part II. IEEE Trans. Electron Devices 2015, 62, 434–442. [Google Scholar] [CrossRef]

- Shah, K.; Shenai, K. Simple and accurate circuit simulation model for gallium nitride power transistors. IEEE Trans. Power Devices 2012, 59, 2735–2741. [Google Scholar] [CrossRef]

- Huang, X.; Liu, Z.; Lee, F.C.; Li, Q. Characterization and enhancement of high-voltage cascode GaN devices. IEEE Trans. Electron Devices 2015, 62, 270–277. [Google Scholar] [CrossRef]

- Ji, D.; Yue, Y.; Gao, J.; Chowdhury, S. Dynamic Modeling and Power Loss Analysis of High-Frequency Power Switches Based on GaN CAVET. IEEE Trans. Electron Devices 2016, 63, 4011–4017. [Google Scholar] [CrossRef]

- Peng, K.; Eskandari, S.; Santi, E. Characterization and modeling of a gallium nitride power HEMT. IEEE Trans. Ind. Appl. 2016, 52, 4965–4975. [Google Scholar] [CrossRef]

- Chen, K.; Zhao, Z.; Yuan, L.; Lu, T.; He, F. The impact of nonlinear junction capacitance on switching transient and its modeling for SiC MOSFET. IEEE Trans. Electron Devices 2015, 62, 333–337. [Google Scholar] [CrossRef]

- Pozo Arribas, A.; Krishnamurthy, M.; Shenai, K. A simple and accurate circuit simulation model for high-voltage SiC power MOSFETs. ECS Trans. 2014, 64, 99–110. [Google Scholar] [CrossRef]

- Lidow, A.; Strydom, J.; De Rooij, M.; Reusch, D. GaN Transistors for Efficiency Power Conversion, 2nd ed.; Power Conversion Publications: El Segundo, CA, USA, 2014; ISBN 978-1-118-84476-2. [Google Scholar]

- Wu, H.Y.; Lin, M.C.; Yang, N.Y.; Tsai, C.T.; Wu, C.B.; Lin, Y.S.; Chang, Y.C.; Chen, P.C.; Wong, K.Y.; Kwan, M.H.; et al. GaN cascode performance optimization for high efficient power applications. In Proceedings of the 28th International Symposium on Power Semiconductor Devices and ICs (ISPSD), Prague, Czech Republic, 12–16 June 2016; pp. 255–258. [Google Scholar]

- Jeng, S.L.; Wu, C.C.; Chieng, W.H. Gallium Nitride Electrical Characteristics Extraction and Uniformity Sorting. J. Nanomater. 2015, 2015, 1–15. [Google Scholar] [CrossRef]

- Wong, Y.Y.; Chang, E.Y.; Yang, T.H.; Chang, J.R.; Ku, J.T.; Hudait, M.K.; Chou, W.C.; Chen, M.; Lin, K.L. The roles of threading dislocations on electrical properties of AlGaN/GaN heterostructure grown by MBE. J. Electrochem. Soc. 2010, 157, H746–H749. [Google Scholar] [CrossRef]

- Hsiao, Y.L.; Lu, L.C.; Wu, C.H.; Chang, E.Y.; Kuo, C.I.; Maa, J.S.; Lin, K.L.; Luong, T.T.; Huang, W.C.; Chang, C.H.; et al. Effect of Graded AlxGa1-xN Layers on the Properties of GaN Grown on Patterned Si Substrates. Jpn. J. Appl. Phys. 2012, 51. [Google Scholar] [CrossRef]

- Chen, S.H.; Chou, P.C.; Cheng, S. Evaluation of thermal performance of packaged GaN HEMT cascode power switch by transient thermal testing. Appl. Therm. Eng. 2016, 98, 1003–1012. [Google Scholar] [CrossRef]

- Chou, P.C.; Chen, S.H.; Hsieh, T.E.; Cheng, S.; del Alamo, J.A.; Chang, E.Y. Evaluation and Reliability Assessment of GaN-on-Si MIS-HEMT for Power Switching Applications. Energies 2017, 10, 233. [Google Scholar] [CrossRef]

- King, J.B.; Brazil, T.J. A GaN HEMT equivalent circuit model with novel approach to dispersion modelling. In Proceedings of the IEEE Microwave Integrated Circuits Conference (EuMIC), Amsterdam, The Netherlands, 29–30 October 2012; pp. 68–71. [Google Scholar]

- Raffo, A.; Bosi, G.; Vadala, V.; Vannini, G. Behavioral modeling of GaN FETs: A load-line approach. IEEE Trans. Microw. Theory Tech. 2014, 62, 73–82. [Google Scholar] [CrossRef]

- Jardel, O.; De Groote, F.; Reveyrand, T.; Jacquet, J.C.; Charbonniaud, C.; Teyssier, J.P.; Didier, F.; Quere, R. An electrothermal model for AlGaN/GaN power HEMTs including trapping effects to improve large-signal simulation results on high VSWR. IEEE Trans. Microw. Theory Tech. 2007, 55, 2660–2669. [Google Scholar] [CrossRef]

- Chou, P.C.; Cheng, S. Performance characterization of gallium nitride HEMT cascode switch for power conditioning applications. Mater. Sci. Eng. B Adv. 2015, 198, 43–50. [Google Scholar] [CrossRef]

- Agilent Technologies. Agilent B1505A Power Device Analyzer/Curve Tracer, Step by Step Measurement Handbook for Power MOSFET. Available online: www.agilent.com (accessed on 4 August 2011).

- Ishibashi, T.; Okamoto, M.; Hiraki, E.; Tanaka, T.; Hashizume, T.; Kikuta, D.; Kachi, T. Experimental Validation of Normally-On GaN HEMT and Its Gate Drive Circuit. IEEE Trans. Ind. Appl. 2015, 51, 2415–2422. [Google Scholar] [CrossRef]

- Transphorm. TPH3006PS Datasheet. Available online: http://www.transphormusa.com/sites/default/files/public/TPH3006PS.pdf (accessed on 30 December 2014).

- Description of the ON Semiconductor MOSFET Model. Application Note AND9033, Semiconductor Components Industries, LLC, 2011. November 2011—Rev. 1. Available online: https://www.onsemi.cn/PowerSolutions/document/AND9033-D.PDF (accessed on 1 November 2011).

- Russell, H.T., Jr. The SPICE Diode Model. In Rectifier Applications Handbook; Roehr, W.D., Ed.; November 2001; Ch. 3; pp. 47–71. Available online: http://www.introni.it/pdf/Motorola%20-%20Rectifier%20Applications%20Handbook.pdf (accessed on 2 November 2001).

- Hsieh, T.E.; Lin, Y.C.; Liao, J.T.; Lan, W.C.; Chin, P.C.; Chang, E.Y. Effect of high voltage stress on the DC performance of the Al2O3/AlN GaN metal-insulator-semiconductor high-electron mobility transistor for power applications. Appl. Phys. Express 2015, 8, 104102. [Google Scholar] [CrossRef]

- Arribas, A.P.; Shang, F.; Krishnamurthy, M.; Shenai, K. Simple and accurate circuit simulation model for SiC power MOSFETs. IEEE Trans. Electron Devices 2015, 62, 449–457. [Google Scholar] [CrossRef]

- Umegami, H.; Hattori, F.; Nozaki, Y.; Yamamoto, M.; Machida, O. A novel high-efficiency gate drive circuit for normally off-type GaN FET. IEEE Trans. Ind. Appl. 2014, 50, 593–599. [Google Scholar] [CrossRef]

- Wang, J.; Chung, H.S.H. A novel RCD level shifter for elimination of spurious turn-on in the bridge-leg configuration. IEEE Trans. Power Electron. 2015, 30, 976–984. [Google Scholar] [CrossRef]

- Broadmeadow, M.A. Characterisation of the Cascode Gate Drive of Power MOSFETs in Clamped Inductive Switching Applications. Ph.D. Thesis, Department of Electrical and Electronic Engineering, Queensland University, Brisbane, Australia, 2015. [Google Scholar]

- ON Semiconductor. MOSFET Gate-Charge Origin and Its Applications, AND9083/D Datasheet, February 2016—Rev. 2. Available online: onsemi.com (accessed on 2 February 2016).

- Yiin, A.J.; Schrimpf, R.D.; Galloway, K.F. Gate-Charge Measurements for Irradiated N-Channel DMOS Power Transistors. IEEE Trans. Nucl. Sci. 1991, 38, 1352–1358. [Google Scholar] [CrossRef]

- Chen, Z. Characterization and Modeling of High-Switching-Speed Behavior of SiC Active Devices. Master’s Thesis, Department of Electrical and Electronic Engineering, Virginia Tech, Blacksburg, VA, USA, 2009. [Google Scholar]

- T & M Research, 0.1 Ω (SSDN-414-10), SDN Series Current Viewing Resistors. Available online: www.tandmresearch.com (accessed on 13 March 2015).

- Wu, C.C.; Jeng, S.L. Switching performance of GaN FETs in terms of turn-off resistance characteristics an experimental study. In Proceedings of the 2016 4th International Conference on Electrical & Electronics Engineering and Computer Science (ICEEECS 2016), Jinan, China, 15–16 October 2016; Volume 50, pp. 546–551. [Google Scholar]

- Texas Instruments. Single 9-A High-Speed Low-Side MOSFET Driver. Available online: www.ti.com/product/UCC27322 (accessed on 12 October 2015).

| Parameter | Model | Area | β | VTH | λ | RS | RD | |

|---|---|---|---|---|---|---|---|---|

| MIS-HEMT | JFET | 1 | 0.4/0.39 * | −20 | 0/−0.001 * | 0.05 | 0.13/0.15 * | |

| Parameter | Model | W(μ) | L(μ) | KP | VTH | λ | RS | RD |

| LV MOSFET | Lev.1 MOS | 100 | 100 | 27.8 | 1.7 | 0 | 0.007 | 0.013 |

| SiC SBD | LV MOSFET | MIS-HEMT | |||||||

|---|---|---|---|---|---|---|---|---|---|

| Par. | CJ0 (pF) | VJ (V) | M | CJ0 (pF) | PB (V) | M | CJ0 (pF) | VJ (V) | M |

| CD | 698.53 | 0.52 | 0.45 | - | - | ||||

| Cgs | - | Cgs0 (pF) × W (μ) = 4350 | 44.25 | 25.90 | −0.03 | ||||

| Cgd | - | 368.55 | 95.95 | 8.92 | 15.42 | 15.69 | 0.24 | ||

| Cds | - | 422.14 | 180.75 | 12.04 | 45.17 | 39.97 | 0.06 | ||

| Fabricated | Commercial | ||

|---|---|---|---|

| Turn-on | Current rise time (tCR) (ns) | 255 | 140 |

| Voltage fall time (tVF) (ns) | 307 | 240 | |

| Turn-off | Voltage rise time (tVR) (ns) | 470 | 140 |

| Current fall time (tCF) (ns) | 280 | 70 | |

| RDS(ON) (mΩ) | Static on-resistance Ron,stat | 330 | 150 |

| Dynamic on-resistance Ron,dyn | 2110 | 150 | |

| Ron,dyn/Ron,stat ratio | 6.4 | 1 | |

| Parameter | Fabricated Cascode | Commercial Cascode | |||

|---|---|---|---|---|---|

| QGS (nC) | QGS1 | 12.5 | 8 | 3 | 2.5 |

| QGS2 | 4.5 | 0.5 | |||

| QGD (nC) | 5 | 2 | |||

| QG (nC) | 35 @ 6 V | 8 @ 6 V | |||

| RDS(ON) (mΩ) | 330 | 150 | |||

| FOM | 3135 | 375 | |||

| QGD,0–20 V | 3.52 | 1.60 | |||

| QGD,0–100 V | 3.66 | 2.08 | |||

| QGD,0–20 V/GD,0–100 V | 96.2% | 76.9% | |||

© 2017 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wu, C.-C.; Jeng, S.-L. Simulation Model Development for Packaged Cascode Gallium Nitride Field-Effect Transistors. Crystals 2017, 7, 250. https://doi.org/10.3390/cryst7080250

Wu C-C, Jeng S-L. Simulation Model Development for Packaged Cascode Gallium Nitride Field-Effect Transistors. Crystals. 2017; 7(8):250. https://doi.org/10.3390/cryst7080250

Chicago/Turabian StyleWu, Chih-Chiang, and Shyr-Long Jeng. 2017. "Simulation Model Development for Packaged Cascode Gallium Nitride Field-Effect Transistors" Crystals 7, no. 8: 250. https://doi.org/10.3390/cryst7080250