Modeling, Analysis, and Realization of Permanent Magnet Synchronous Motor Current Vector Control by MATLAB/Simulink and FPGA

Abstract

:1. Introduction

2. The Electrical Model of Permanent Magnet Synchronous Motor

3. Analysis and Design for PMSM Drive System Based on MATLAB/Simulink

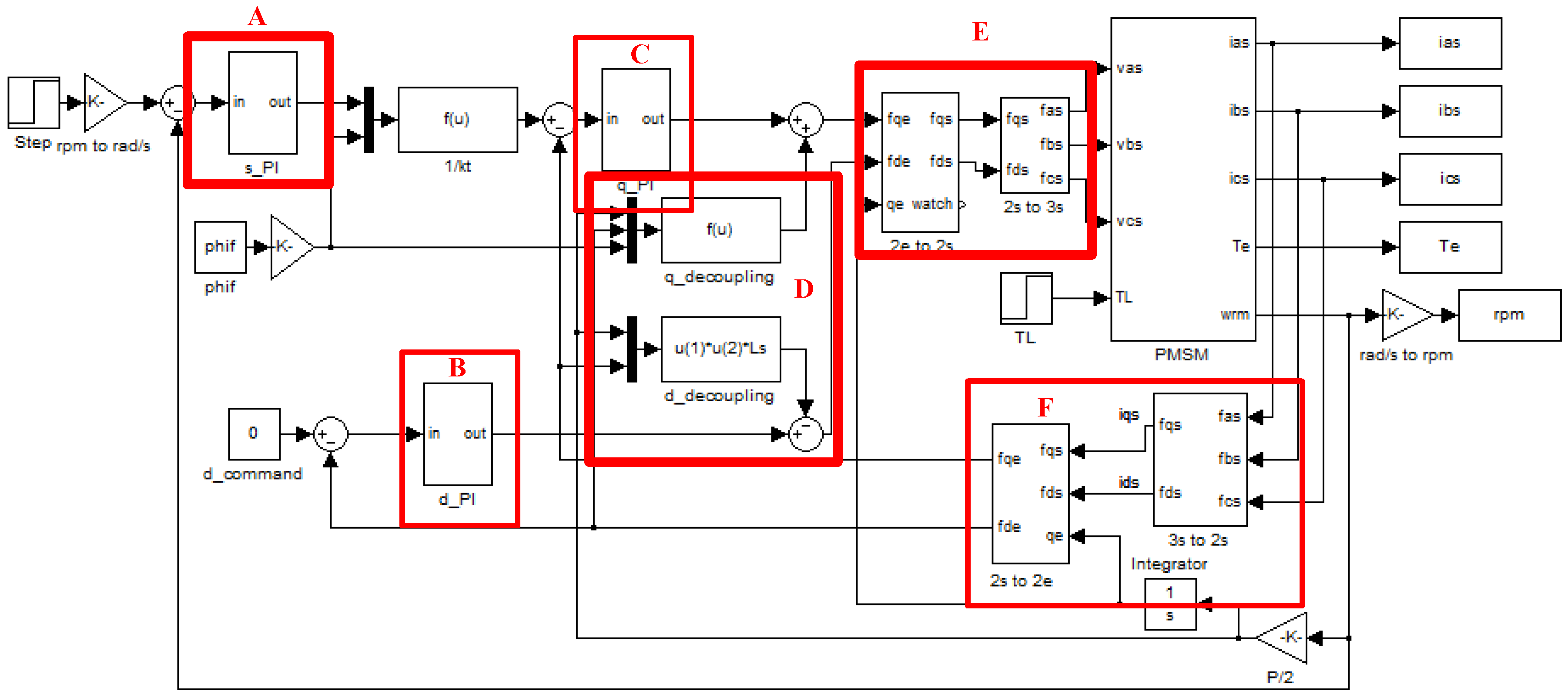

3.1. The Block Diagram of PMSM Drive System

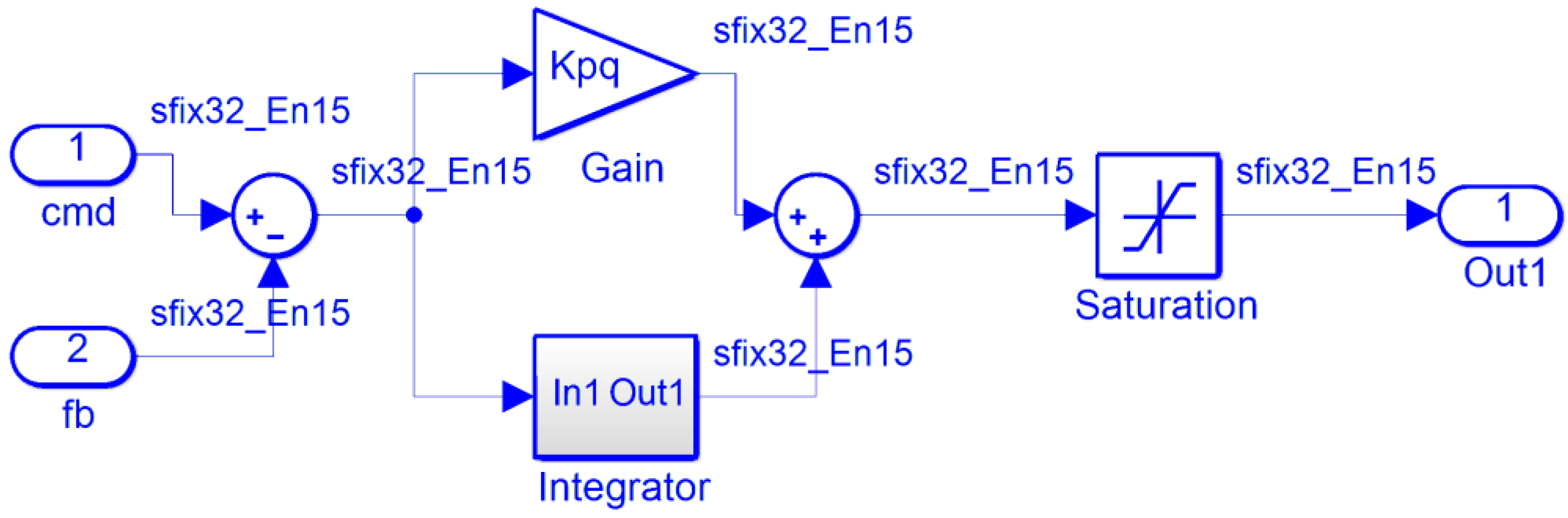

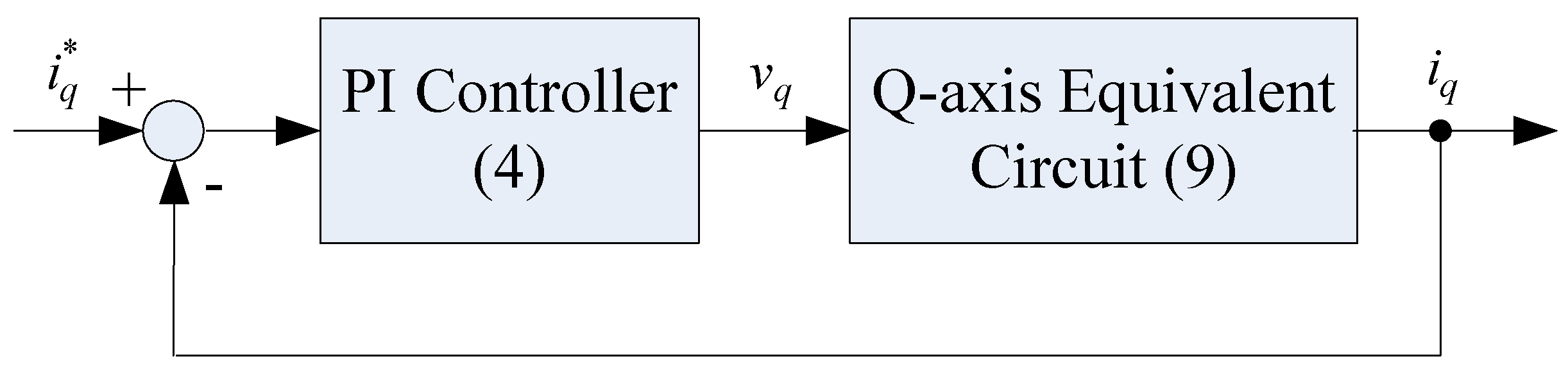

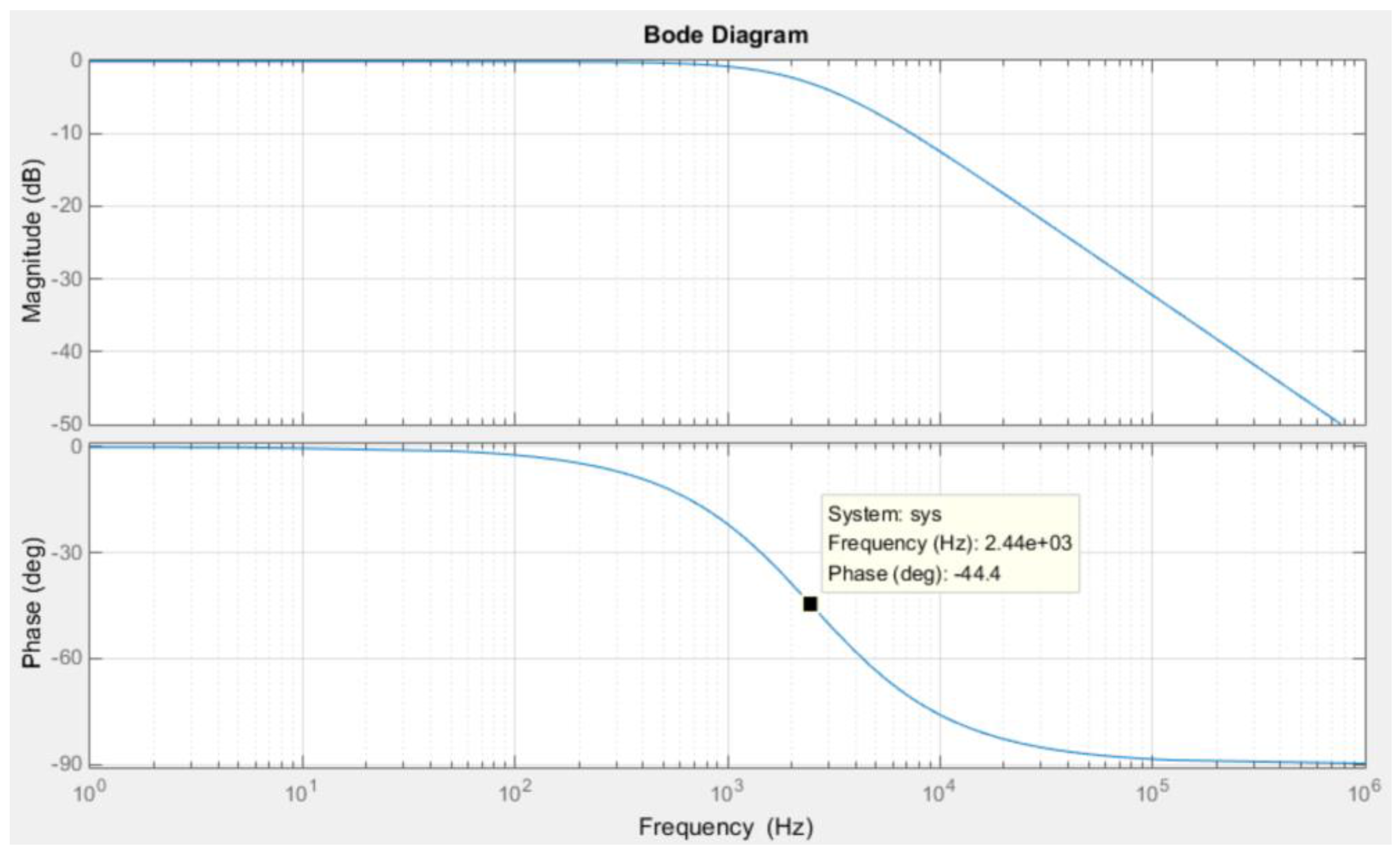

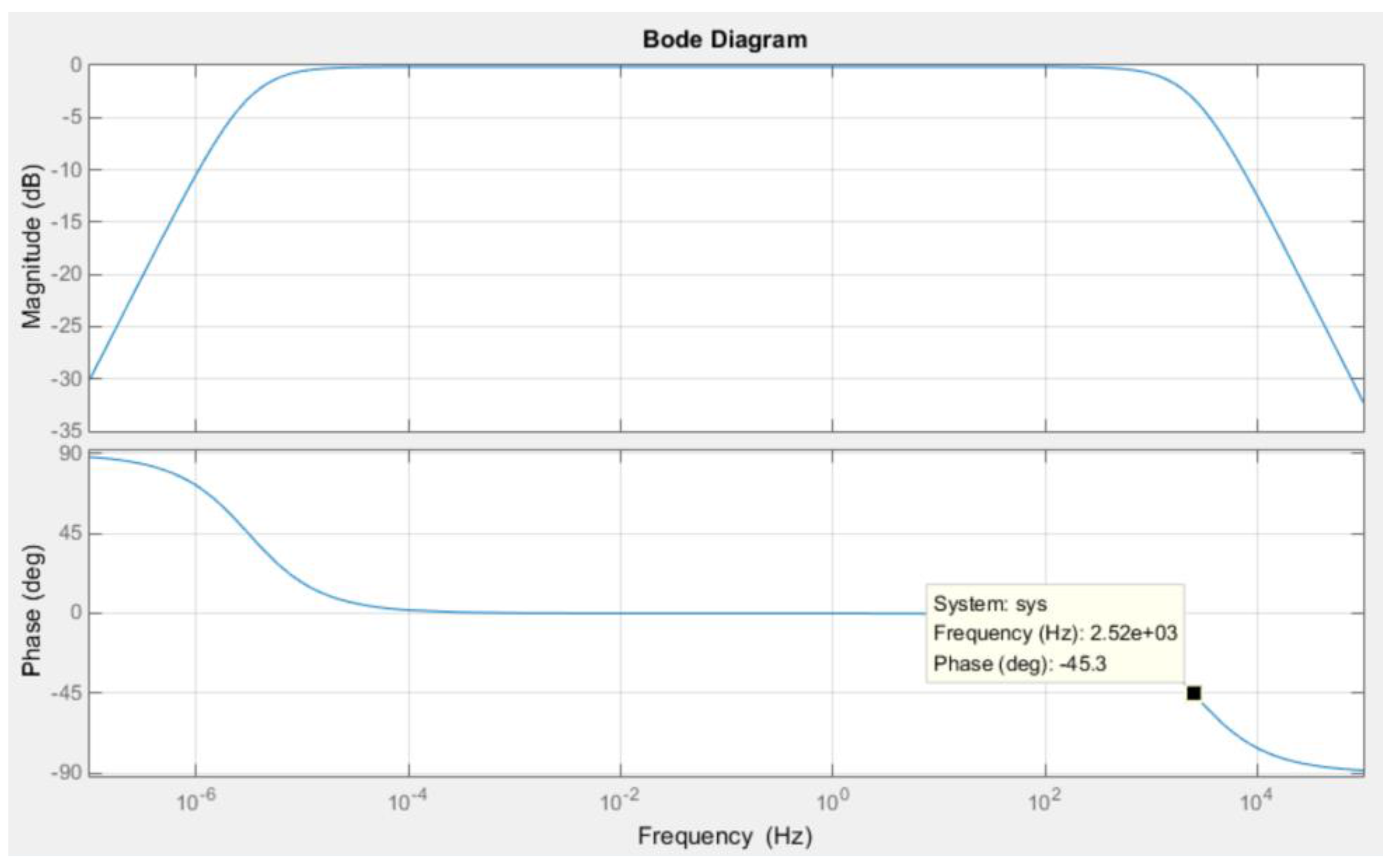

3.2. The Design of Hardware PI Controller

3.3. The Clarke, Park, Inverse Park, and Inverse Clarke Transformations

3.4. The SVPWM Model

4. Simulation, Experiment, and Discussion

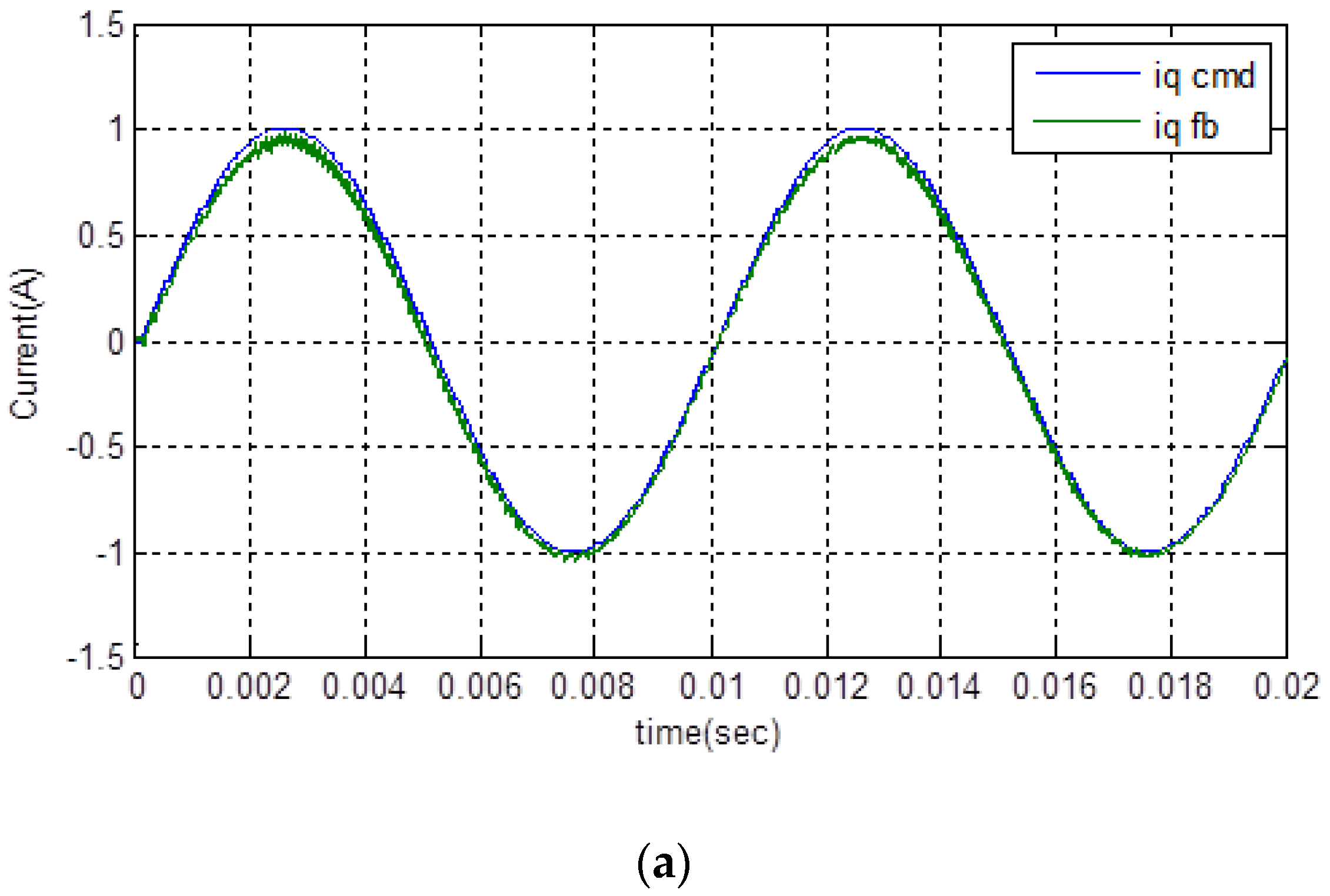

4.1. The Simulation Results

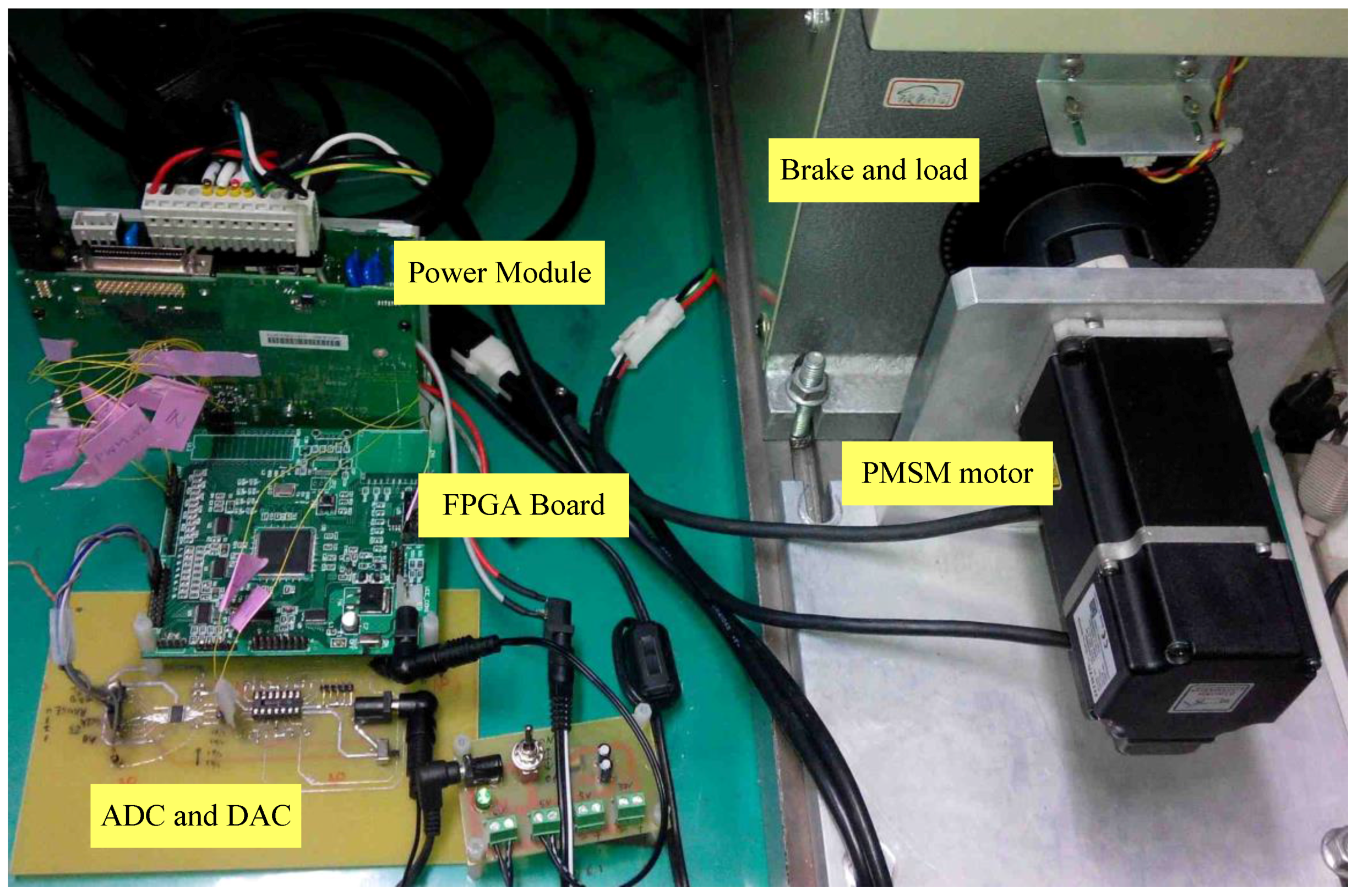

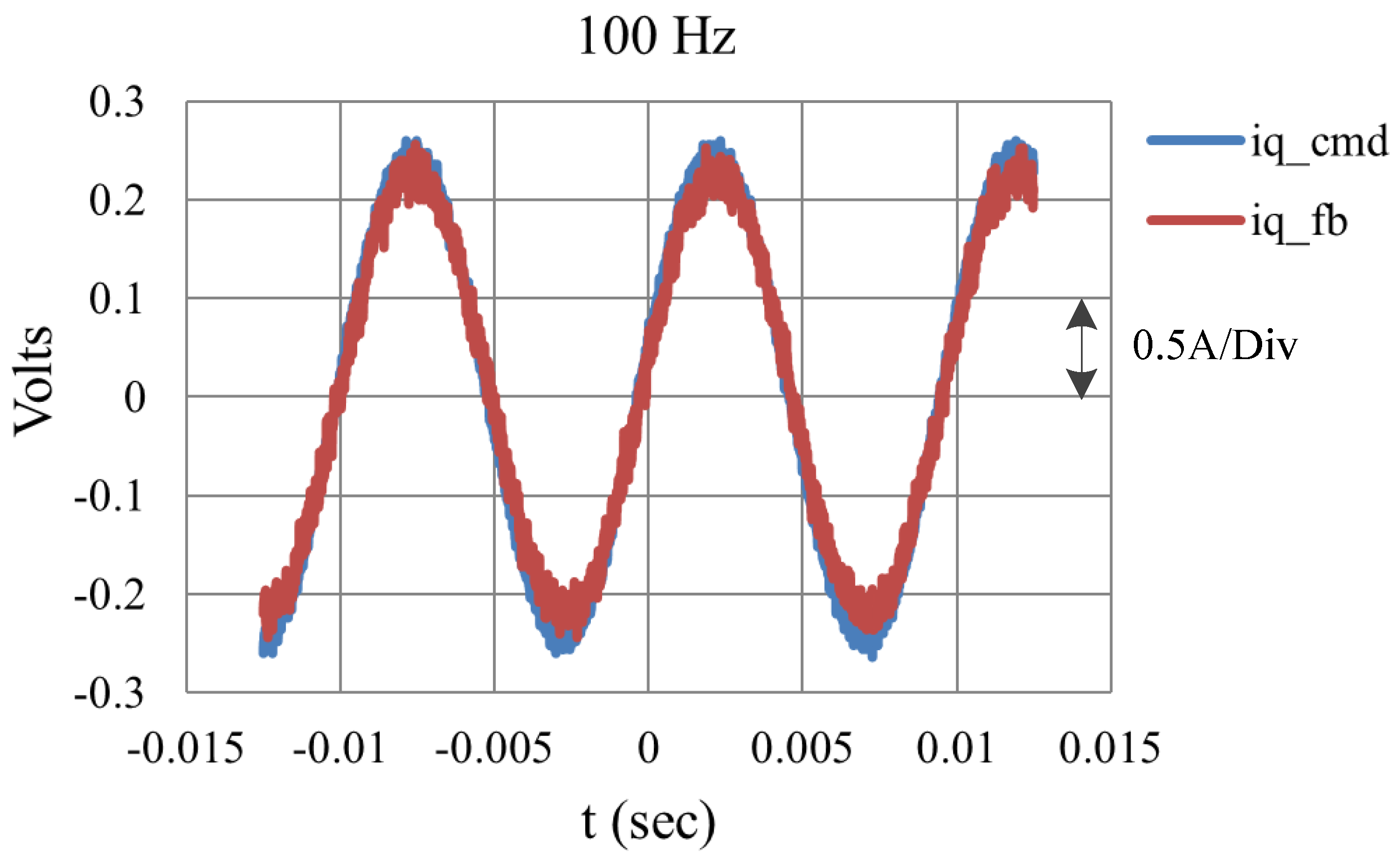

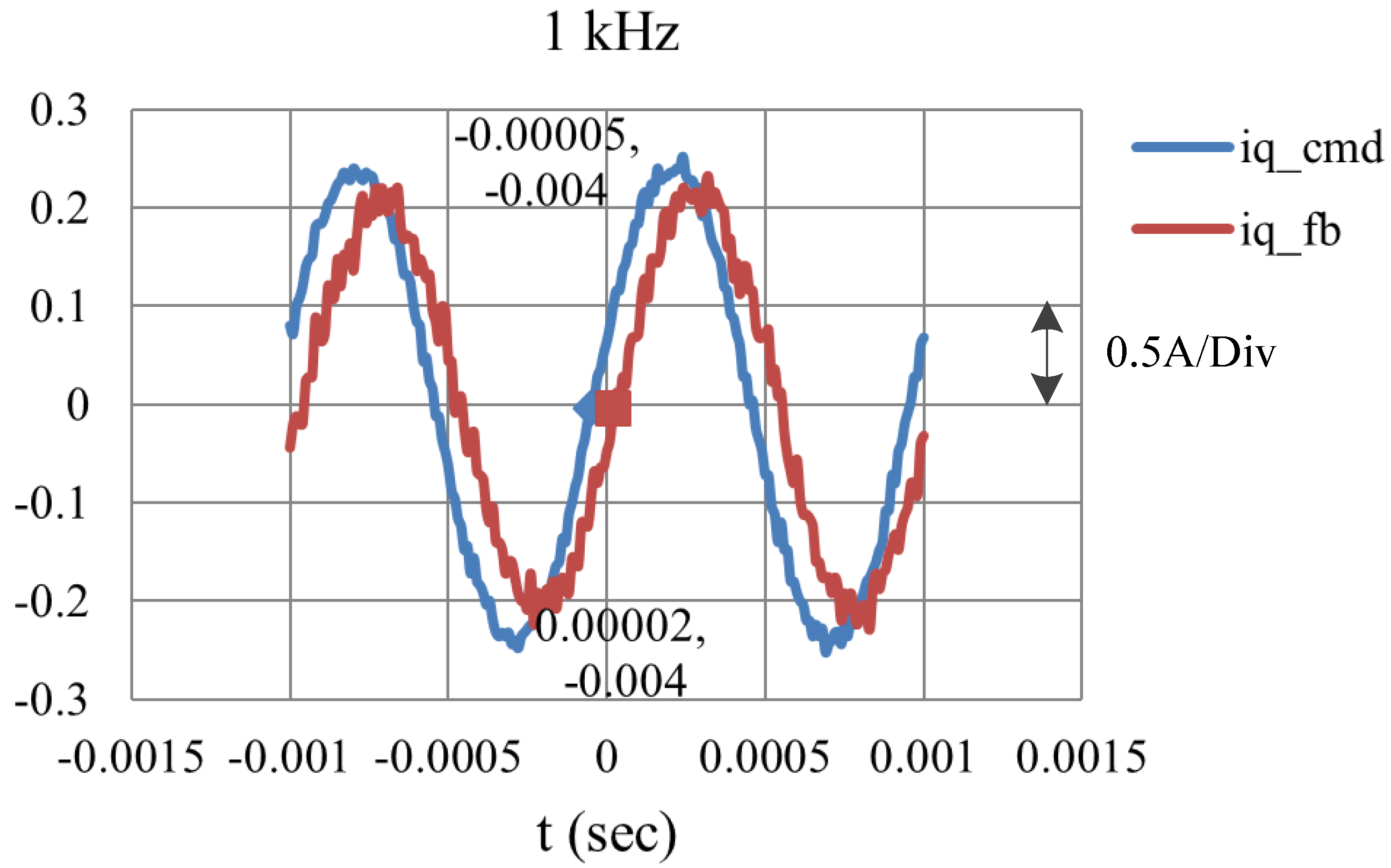

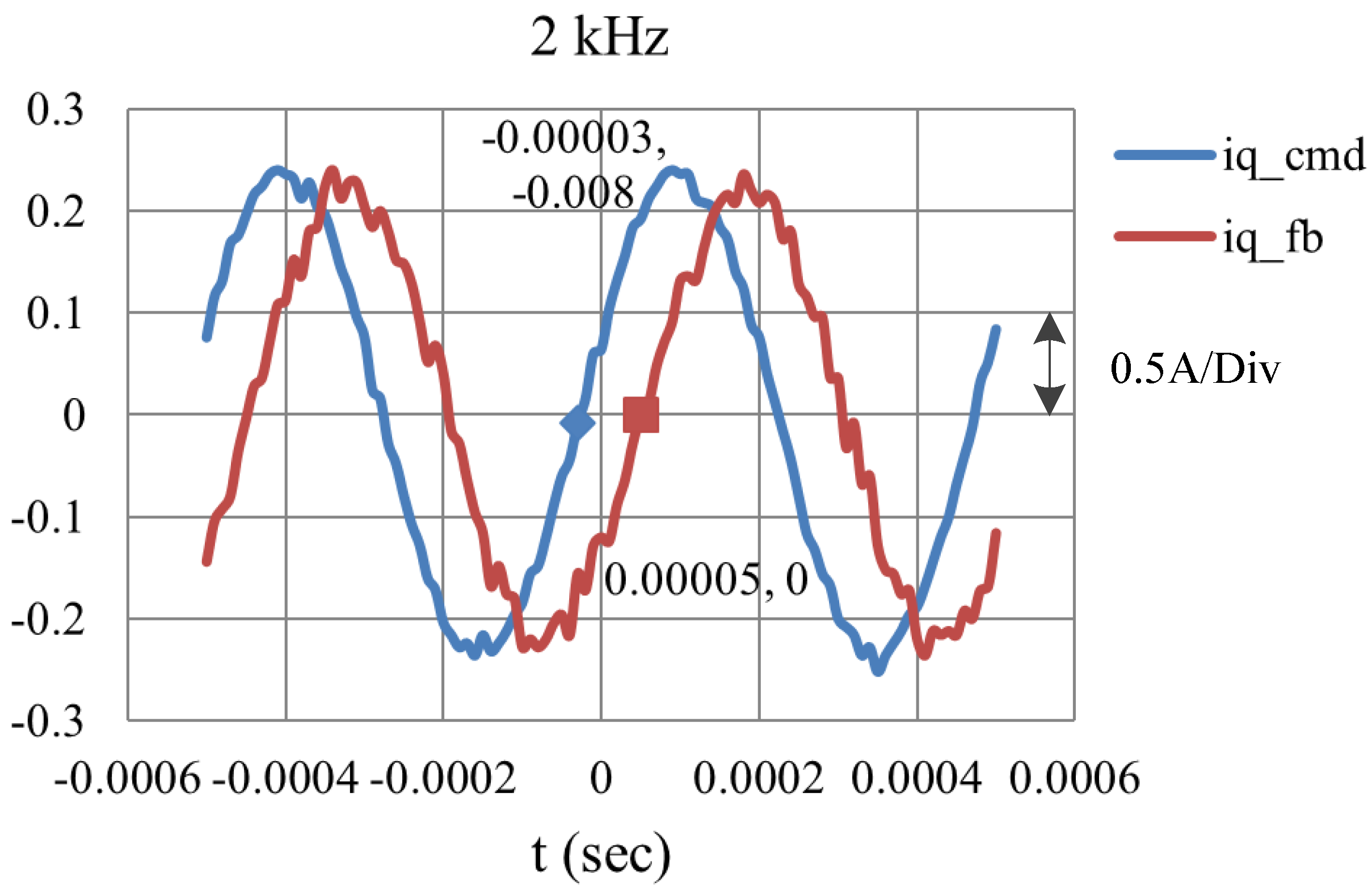

4.2. The Experimental Setup and Results

5. Conclusions

Author Contributions

Conflicts of Interest

References

- Siwakoti, Y.P.; Town, G.E. Design of FPGA-Controlled Power Electronics and Drives Using MATLAB Simulink. In Proceedings of the IEEE/ECCE, Melbourne, VIC, Australia, 3–6 June 2013; pp. 571–577. [Google Scholar] [CrossRef]

- Stumpf, A.; Elton, D.; Devlin, J.; Lovatt, H. Benefits of an FPGA based SRM controller. In Proceedings of the IEEE 9th Conference on Industrial Electronics and Applications (ICIEA), Hangzhou, China, 9–11 June 2014; pp. 12–17. [Google Scholar]

- Rohit, B.C.; Patil, M.D.; Shah, D.; Kadam, A. FPGA Implementation of SVPWM Control Technique for Three Phase Induction Motor Drive Using Fixed Point Realization. In Proceedings of the 2014 International Conference on Circuits, Systems, Communication and Information Technology Applications, Mumbai, Maharashtra, India, 4–5 April 2014; pp. 93–98. [Google Scholar]

- Kung, Y.-S.; Tsai, M.-H. FPGA-Based Speed Control IC for PMSM Drive with Adaptive Fuzzy Control. IEEE Trans. Power Electron. 2007, 22, 2476–2486. [Google Scholar] [CrossRef]

- Kung, Y.-S.; Huang, P.-G.; Chen, C.-W. Development of a SOPC for PMSM Drives. In Proceedings of the 47th IEEE International Midwest Symposium on Circuits and Systems, Hiroshima, Japan, 25–28 July 2004; pp. 329–332. [Google Scholar]

- Quynh, N.V.; Kung, Y.-S. FPGA-Realization of Fuzzy Speed Controller for PMSM Drives without Position Sensor. In Proceedings of the ICCAIS, Nha Trang, Vietnam, 25–28 November 2013; pp. 278–282. [Google Scholar] [CrossRef]

- Zhang, G.Z.; Zhao, F.; Wang, Y.X.; Wen, X.H.; Cong, W. Analysis and Optimization of Current Regulator Time Delay in Permanent Magnet Synchronous Motor Drive System. In Proceedings of the 2013 International Conference on Electrical Machines and Systems, Busan, Korea, 26–29 October 2013; pp. 2286–2290. [Google Scholar]

- Zhang, C.J.; Wu, X.J.; Zuo, X.Y. FPGA Soft-Core Based Step Motor Driving. In Proceedings of the 2010 International Conference on Electrical and Control Engineering, Wuhan, China, 25–27 June 2010; pp. 1035–1038. [Google Scholar]

- Horvat, R.; Jezernik, K.; Curkovic, M. An Event-Driven Approach to the Current Control of a BLDC Motor Using FPGA. IEEE Trans. Ind. Electron. 2014, 61, 3719–3726. [Google Scholar] [CrossRef]

- Kocur, M.; Kozak, S.; Dvorscak, B. Design and Implementation of FPGA-Digital Based PID Controller. In Proceedings of the 15th International Carpathian Control Conference, Velke Karlovice, Czech Republic, 28–30 May 2014; pp. 233–236. [Google Scholar]

- Quang, N.K.; Kung, Y.-S.; Ha, Q.P. FPGA-Based Control Architecture Integration for Multiple-Axis Tracking Motion Systems. In Proceedings of the IEEE/SICE, Kyoto, Japan, 20–22 December 2011; pp. 591–596. [Google Scholar] [CrossRef]

- Data sheet of FRLS4020506A. Available online: https://www.hiwin.de/en/Produktfinder_Detail_2/Motors_Drives_and_Accessories/Servo_motors/Without_motor_brakeand_feather_key/20373 (accessed on 23 October 2017).

| Pole | 10 |

|---|---|

| 3.5 | |

| 13 | |

| 0.270 | |

| 0 | |

| 0.0707 | |

| 1.27 |

© 2017 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lai, C.-K.; Tsao, Y.-T.; Tsai, C.-C. Modeling, Analysis, and Realization of Permanent Magnet Synchronous Motor Current Vector Control by MATLAB/Simulink and FPGA. Machines 2017, 5, 26. https://doi.org/10.3390/machines5040026

Lai C-K, Tsao Y-T, Tsai C-C. Modeling, Analysis, and Realization of Permanent Magnet Synchronous Motor Current Vector Control by MATLAB/Simulink and FPGA. Machines. 2017; 5(4):26. https://doi.org/10.3390/machines5040026

Chicago/Turabian StyleLai, Chiu-Keng, Yao-Ting Tsao, and Chia-Che Tsai. 2017. "Modeling, Analysis, and Realization of Permanent Magnet Synchronous Motor Current Vector Control by MATLAB/Simulink and FPGA" Machines 5, no. 4: 26. https://doi.org/10.3390/machines5040026