Article

# Optimization of Fluorine Plasma Treatment for Interface Improvement on $HfO_2/In_{0.53}Ga_{0.47}As\ MOSFETs$

Yen-Ting Chen \*, Yanzhen Wang, Fei Xue, Fei Zhou and Jack C. Lee

Microelectronics Research Center, Department of Electrical and Computer Engineering, The University of Texas at Austin, TX 78758, USA; E-Mails: yanzhen@physics.utexas.edu (Y.W.); xuefei.ee@gmail.com (F.X.); essenonvidare@gmail.com (F.Z.); jacklee@mail.utexas.edu (J.C.L.)

\* Author to whom correspondence should be addressed; E-Mail: ytchen@mail.utexas.edu; Tel.: +1-512-471-1627; Fax: +1-512-471-5625.

Received: 30 January 2012; in revised form: 20 February 2012 / Accepted: 10 March 2012 /

Published: 19 March 2012

**Abstract:** This paper reports significant improvements in the electrical performance of  $In_{0.53}Ga_{0.47}As$  metal-oxide-semiconductor field-effect transistors (MOSFET) by a post-gate  $CF_4/O_2$  plasma treatment. The optimum condition of  $CF_4/O_2$  plasma treatment has been systematically studied and found to be 30 W for 3–5 min. Approximately 5× reduction in interface trap density from  $2.8 \times 10^{12}$  to  $4.9 \times 10^{11}$  cm<sup>-2</sup>eV<sup>-1</sup> has been demonstrated with fluorine (F) incorporation. Subthreshold swing has been improved from 127 to 109 mV/dec. Effective channel mobility has been enhanced from 826 to 1,144 cm<sup>2</sup>/Vs.

**Keywords:** InGaAs; HfO<sub>2</sub>; fluorine plasma treatment; high-k dielectrics

## 1. Introduction

In<sub>0.53</sub>Ga<sub>0.47</sub>As based-III-V compounds have attracted a great deal of attention for their advantages in high electron mobility over their Si-based counterparts. However, poor interface quality between In<sub>0.53</sub>Ga<sub>0.47</sub>As and high dielectric constant (high-k) gate dielectrics has imposed an enormous challenge for implementing inversion-type enhancement mode metal-oxide-semiconductor field-effect transistors (MOSFETs). Proper surface pre-treatment and insertion of interface passivation layer [1–3] have generally employed to achieve improved interface quality. Those approaches usually performed prior to high-k deposition, however, interface state traps created during the high-k deposition need to be passivated by a post-oxide treatment.

It can be expected that fluorine (F) will be an effective passivation agent for In<sub>0.53</sub>Ga<sub>0.47</sub>As because F has high binding energy with In (5.25 eV), Ga (5.99 eV), and As (4.26 eV), respectively [4]. F incorporation has been demonstrated on Si, Ge, and In<sub>0.53</sub>Ga<sub>0.47</sub>As substrates. It has been found that F can passivate high-k bulk traps and interface defects at high-k/substrates (Si, Ge and In<sub>0.53</sub>Ga<sub>0.47</sub>As) interface [5–9]. Although previous reports showed that the insertion of a thin interface passivation layer could improve interface quality [10], those layers usually have relative lower k value [11]. This may hinder equivalent oxide thickness (EOT) scaling and as a result, hardly meet the requirement for the sub 22 nm nodes.

In this paper, we systematically studied the effects of  $CF_4/O_2$  plasma power wattage and treatment time on  $HfO_2/In_{0.53}Ga_{0.47}As$  gate stack. The condition of  $CF_4/O_2$  plasma has been optimized, which significantly improves the effective channel mobility ( $\mu_{eff}$ ), transconductance ( $G_m$ ), drive current ( $I_d$ ), and subthreshold swing (SS). With F incorporation, we have successfully developed excellent interface quality of  $HfO_2$  directly on  $In_{0.53}Ga_{0.47}As$  without using interface passivation layer. Fluorinated samples exhibit low interface trap density ( $D_{it}$ ) of  $4.9 \times 10^{11}$  cm<sup>-2</sup>eV<sup>-1</sup>, which is the lowest value compared to prior reported  $HfO_2/In_{0.53}Ga_{0.47}As$  gate stacks.

# 2. Experimental Section

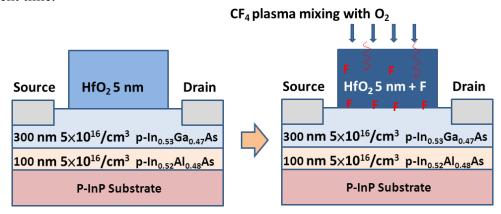

Figure 1 shows the device structure and the illustration of F incorporation. The wafers used in our study were molecular beam epitaxy grown by a vender. P-type (Zn-doped,  $3 \times 10^{18}$ /cm<sup>3</sup>) InP wafers were the starting substrates. P-type (Be-doped,  $5 \times 10^{16}$ /cm<sup>3</sup>) In<sub>0.52</sub>Al<sub>0.48</sub>As of 100 nm thick was grown as a buffer layer, followed by a 300 nm p-type  $In_{0.53}Ga_{0.47}As$  layer (Be-doped,  $5 \times 10^{16}/cm^3$ ), which was used as the channel layer. The native oxides were removed with 1% diluted HF solution, followed by 20% (NH<sub>4</sub>)<sub>2</sub>S solution for sulfur passivation. To protect gate stack from the source and drain (S/D) activation annealing, the gate-last process was adopted: A 10-nm-thick atomic-layer-deposited (ALD) Al<sub>2</sub>O<sub>3</sub> was deposited at a substrate temperature of 200 °C as an encapsulation layer. S/D regions were selectively implanted with a Si dose of  $2 \times 10^{14}$ /cm<sup>2</sup> at 35 keV. The S/D activation annealing was performed in nitrogen ambient at 700 °C/10 s. The encapsulation layer was then removed using buffered oxide etch solution. A 5 nm-thick ALD HfO<sub>2</sub> film was deposited after the same surface preparation (HF and (NH<sub>4</sub>)<sub>2</sub>S). Some samples were treated ex situ with CF<sub>4</sub> plasma with varied RF wattages and treatment times. A mixed flow of CF<sub>4</sub> and O<sub>2</sub> gas (ratio ~10:1) was introduced into the chamber with pressure of 100 mTorr. The purpose of O<sub>2</sub> flow was to avoid carbon contamination. Control samples without CF<sub>4</sub>/O<sub>2</sub> plasma treatment were also fabricated as references. Post-deposition annealing was then performed for all the samples at 500 °C for 60 s in a nitrogen ambient. Subsequently, a 200 nm TaN was sputtered and patterned as gate electrode. AuGe/Ni/Au alloy was deposited by E-beam evaporation and a liftoff process to form S/D Ohmic contacts; backside contact was made by E-beam evaporation of Cr/Au, followed by annealing at 400 °C for 30 s in nitrogen ambient.

**Figure 1.** The device cross-sectional structure of  $HfO_2/In_{0.53}Ga_{0.47}As$  gate stack. Samples were treated in a mixed flow of  $CF_4$  and  $O_2$  gas (ratio ~10:1) with varied RF power and treatment time.

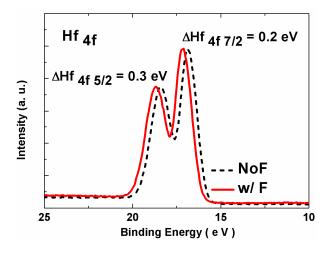

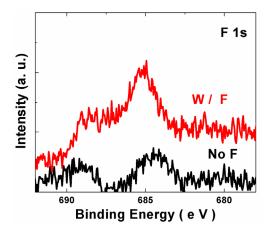

Figures 2 and 3 show the X-ray photoelectron spectroscopy (XPS) spectra of Hf 4f and F 1s for the  $HfO_2/In_{0.53}Ga_{0.47}As$  gate stack with and without  $CF_4/O_2$  plasma treatment. All the scanned binding energy was calibrated by the C 1s signal at 284.5 eV.

**Figure 2.** X-ray photoelectron spectroscopy (XPS) analysis of the Hf 4f electronic spectra for the samples with and without fluorine (F) incorporation.

**Figure 3.** XPS analysis of the F 1s electronic spectra for the control sample and fluorinated sample.

Compared to the control sample, the fluorinated sample has an increased binding energy by 0.2 eV and 0.3 eV for the Hf  $4f_{7/2}$  and Hf  $4f_{5/2}$  signal, respectively. This suggests that parts of the oxygen vacancies were terminated by the incorporated F atoms to form stronger Hf-F bonds with higher binding energy. In Figure 3, the peak signal located at ~685 eV corresponds to the F bonds in the bulk HfO<sub>2</sub>, indicating that F was incorporated into the HfO<sub>2</sub> after CF<sub>4</sub>/O<sub>2</sub> plasma treatment.

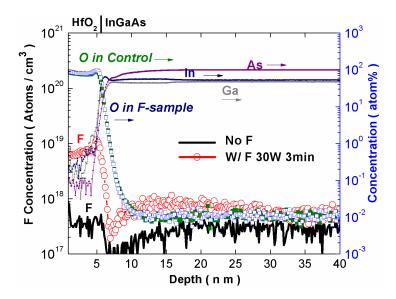

In order to search the F distribution in the HfO<sub>2</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As gate stack, the secondary ion mass spectrometry (SIMS) technique was examined, as shown in Figure 4. A considerable amount of F was incorporated into the HfO<sub>2</sub> gate stacks with CF<sub>4</sub>/O<sub>2</sub> plasma treatment while the oxygen concentration remained similar. Due to sudden structural transition at the HfO<sub>2</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As interface, the density of defective bonds at the interface is much higher than that in the HfO<sub>2</sub> bulk. F tends to pile up at the HfO<sub>2</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As interface passivating interface traps, resulting in a better interface quality (discussed later in this paper).

**Figure 4.** Secondary ion mass spectrometry (SIMS) profile of elements in the  $HfO_2/In_{0.53}Ga_{0.47}As$  gate stack with and without  $CF_4/O_2$  plasma treatment. The  $CF_4/O_2$  plasma condition is 30 W for 3 min.

The composition and stoichiometry of  $HfO_2$  were determined by XPS analysis (data not shown). For the control sample,  $HfO_2$  was in good stoichiometry (Hf:O = 1:2) and it became oxygen-rich ( $HfO_{2.25}$ ) after  $CF_4/O_2$  plasma treatment. One possibility of improvements could be due to the oxygen vacancies passivation during the plasma treatment. The effect of  $O_2$  plasma treatment is under investigation.

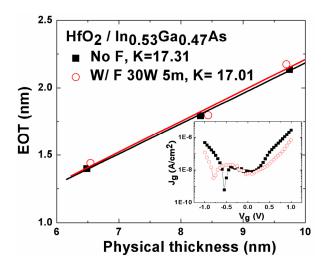

One concern of doping F into gate oxide is that dielectric constant of the gate oxide would decrease with heavy F incorporation. From XPS, the F concentration in our fluorinated HfO<sub>2</sub> is estimated to be 2.7 at.%, which is lower than that used in the low-k technology [12]. Therefore, the dielectric constant of HfO<sub>2</sub> remains similar (~17) after F incorporation, as shown in Figure 5. The inset of Figure 5 compares the gate leakage current of samples with and without F incorporation. The gate leakage current is slightly reduced with F incorporation.

**Figure 5.** Equivalent oxide thickness (EOT) *versus* physical thickness for the samples with and without F incorporation. Inset: the gate leakage current comparison of samples with and without F incorporation.

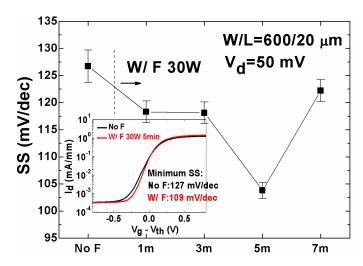

One objective of this work is to investigate the optimum condition of CF<sub>4</sub>/O<sub>2</sub> plasma. The RF power and the plasma treatment time are two critical factors that affect the electrical characteristics significantly. Insufficient plasma treatment might not improve the gate dielectric quality, whereas excessive plasma treatment possibly causes plasma damage and corrodes the improvement. To study the effects of RF power on HfO<sub>2</sub> gate dielectrics, some samples were treated in CF<sub>4</sub>/O<sub>2</sub> plasma for 3 min at different RF power in the range from 20 to 40 W. It was found that the samples treated by the power of 30 W improved most in terms of G<sub>m</sub>, I<sub>d</sub> and SS. With the fixed RF power of 30 W, we continued to study the effect of CF<sub>4</sub>/O<sub>2</sub> plasma treatment time. Some samples were treated in CF<sub>4</sub>/O<sub>2</sub> plasma at different treatment times ranging from 1 to 7 min with a fixed RF power of 30 W. It was found that 5 min plasma treatment further improved SS.

## 3. Results and Discussion

## 3.1. Optimization of CF<sub>4</sub>/O<sub>2</sub> Plasma

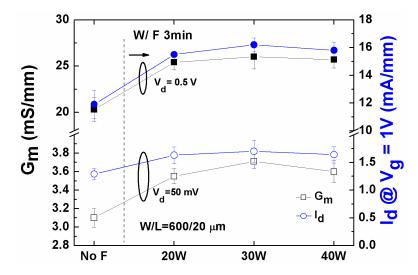

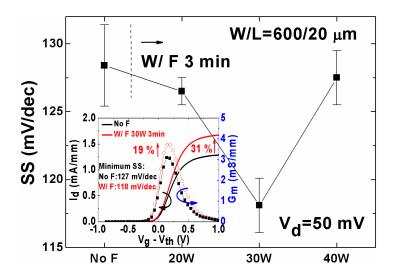

The maximum  $G_m$  and  $I_d$  as a function of different RF power (CF<sub>4</sub>/O<sub>2</sub> plasma treatment time: 3 min) are shown in Figure 6 (W/L = 600/20  $\mu$ m, at  $V_d$  = 50 mV and 0.5 V). The maximum  $G_m$  and  $I_d$  of the control sample are 3.1 mS/mm and 1.3 mA/mm ( $V_d$  = 50 mV), and 20.3 mS/mm and 12 mA/mm ( $V_d$  = 0.5 V), respectively. With F plasma treatment of 30W, the maximum  $G_m$  and  $I_d$  reach 3.7 mS/mm and 1.7 mA/mm ( $V_d$  = 50 mV), and 26 mS/mm and 16.2 mA/mm ( $V_d$  = 0.5 V), respectively. However, the maximum  $G_m$  and  $I_d$  roll back with power larger than 30 W indicative of possible plasma damage. SS data with different RF power are shown in Figure 7.  $I_{0.53}Ga_{0.47}As$  MOSFETs have similar EOT (~1.4 nm, data not shown) with different RF power treatment. With F incorporation, SS has been improved from 127 to 118.1 mV/dec (as shown in the inset of Figure 7), which suggests that the interface quality has been improved. For the RF power of 40W, SS increases to 127.5 mV/dec, indicating that excessive CF<sub>4</sub>/O<sub>2</sub> plasma treatment degrades the interface quality.

**Figure 6.** Maximum  $G_m$  and  $I_d$  as a function of  $CF_4/O_2$  plasma RF power  $(W/L = 600 \ \mu m/20 \ \mu m$  at  $V_d = 50 \ mV$  and  $0.5 \ V)$ .  $CF_4/O_2$  plasma treatment time: 3 min.

**Figure 7.** Subthreshold swing (SS) as a function of  $CF_4/O_2$  plasma RF power.  $CF_4/O_2$  plasma treatment time: 3 min. Inset:  $I_d$ - $V_g$  comparison of the control sample and the sample with  $CF_4/O_2$  plasma treatment for 30 W/3 min.

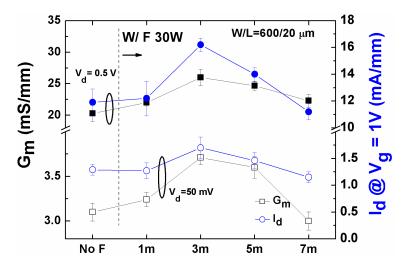

Figure 8 compares the maximum  $G_m$  and  $I_d$  as a function of plasma treatment times ranging from 1 to 7 min with a fixed RF power of 30W (W/L = 600  $\mu$ m/20  $\mu$ m at  $V_d$  = 50 mV and 0.5 V). 3 min plasma treatment reaches the peak values of the maximum  $G_m$  and  $I_d$ , whereas 5 min plasma treatment achieves the lowest SS value (Figure 9). The inset of Figure 8 compares the  $I_d$ - $V_g$  curves (in log-linear scale) of the control sample and the sample with F treatment 30 W/5 min. A steeper SS slope is clearly observed.

**Figure 8.** Maximum  $G_m$  and  $I_d$  as a function of  $CF_4/O_2$  plasma treatment time  $(W/L = 600 \ \mu m/20 \ \mu m$  at  $V_d = 50 \ mV$  and 0.5 V). RF power: 30 W.

**Figure 9.** SS as a function of  $CF_4/O_2$  plasma treatment time. RF power: 30 W. Inset:  $I_d$ - $V_g$  comparison of the control sample and the sample with  $CF_4$  plasma treatment for 30 W/5 min.

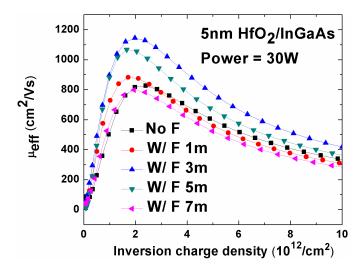

Effective channel mobility ( $\mu_{eff}$ ) of In<sub>0.53</sub>Ga<sub>0.47</sub>As MOSFETs with different plasma treatment times are plotted in Figure 10. The peak  $\mu_{eff}$  of 30 W/3 min reaches 1,144 cm<sup>2</sup>/Vs, which is 38% improvement compared to the control samples (826 cm<sup>2</sup>/Vs). The improvements in the I<sub>d</sub>, G<sub>m</sub>, SS and  $\mu_{eff}$  are believed to be due to the improved interface quality by an appropriate amount of CF<sub>4</sub>/O<sub>2</sub> plasma post-HfO<sub>2</sub> treatment.

**Figure 10.** Effective channel mobility *versus* inversion charge density as a function of  $CF_4/O_2$  plasma treatment time. RF power: 30 W.

We noticed that the plasma damage occurred if excessive plasma (either plasma wattage or treatment time) was applied. The plasma damage could come from disordering, surface roughening, and fluorine contamination [13]. The disordering layer contains dangling bonds and broken bonds, which would scatter the electrons underneath (in the channel) and lower the electron mobility. Severe disordering would lead to surface roughness, which results in more dangling bonds and broken bonds. If the F concentration is too high (>5 at.%, [12]), the dielectric constant of HfO<sub>2</sub> decreases, resulting in lowering drive current.

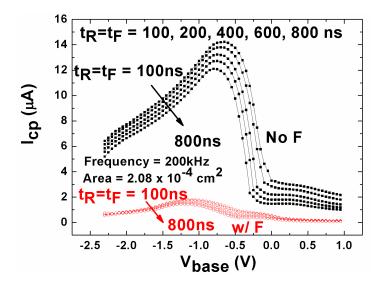

## 3.2. Electrical Characterization of the Interface Trap Density

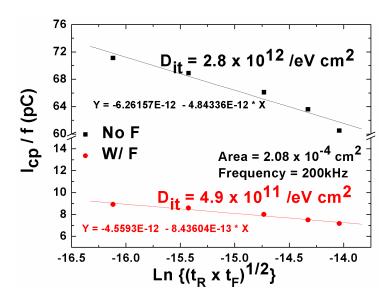

Charge pumping measurements were conducted to accurately evaluate the interface quality of the control and fluorinated MOSFETs. The charge pumping characterization was performed by sweeping the base level voltage ( $V_{base}$ , -2.3 V to 1 V in a step of 50 mV) of the trapezoidal gate pulse (with a constant-amplitude, 1 V) at 200 KHz. The S/D terminals were grounded. The region of the bandgap probed was from electron emission energy level to hole emission energy level, which was around the midgap. The charge pumping current ( $I_{cp}$ ) is plotted as a function of  $V_{base}$  for equal trapezoidal pulse rise time ( $t_R$ ) and fall time ( $t_F$ ), as shown in Figure 11.  $t_R$  and  $t_F$  are varied from 100 to 800 ns. Lower  $I_{cp}$  for the fluorinated sample is indicative of reduced  $D_{it}$ . The mean  $D_{it}$  value can be extracted according to the following equation [14,15],

$$\frac{I_{cp}}{f} = 2qD_{it}AkT \left\{ \ln \sqrt{t_R t_F} + \ln \left( \frac{\left| V_{fb} - V_t \right|}{\left| \Delta V_g \right|} V_{th} n_i \sqrt{\sigma_n \sigma_p} \right) \right\}$$

where q is the electronic charge, A is the transistor gate area  $(2.08 \times 10^{-4} \text{ cm}^2 \text{ in our devices})$ , k is the Boltzmann constant,  $V_{fb}$  is the flat band voltage,  $V_t$  is the threshold voltage,  $\Delta V_g$  is the gate pulse amplitude,  $V_{th}$  is the thermal velocity of the carriers,  $n_i$  is the surface concentration of minority carriers, and  $\sigma_n$  and  $\sigma_p$  are the capture cross sections of electrons and holes, respectively. The mean  $D_{it}$  values were extracted from the slope of  $I_{cp}/f$  versus  $\ln[(t_R \times t_F)^{1/2}]$ , as shown in Figure 12. It has been found that the mean  $D_{it}$  value was reduced  $\sim 5 \times$  from  $2.8 \times 10^{12}$  to  $4.9 \times 10^{11}$  cm<sup>-2</sup>eV<sup>-1</sup> after F plasma

treatment. F atoms possibly passivate dangling bonds and oxygen vacancies in the  $HfO_2/In_{0.53}Ga_{0.47}As$  interface and thereby reduce  $D_{it}$  value.

**Figure 11.** Charge pumping measurement with rise/fall time dependence. Samples with F incorporation show much smaller  $I_{cp}$ .  $V_{base}$ : -2.3 V to 1 V in a step of 50 mV and the pulse amplitude is 1 V.

**Figure 12.**  $Q_{cp}$  (= $I_{cp}/f$ ) vs.  $ln[(t_R \times t_F)^{1/2}]$ . The mean  $D_{it}$  value is extracted by linear fitting according to References [14,15]. Samples with F incorporation show less  $D_{it}$  value of  $4.9 \times 10^{11}/eVcm^2$ .

Table 1 compares the device performance and interfacial properties of In<sub>0.53</sub>Ga<sub>0.47</sub>As MOSFETs reported in this paper and other high-k/In<sub>0.53</sub>Ga<sub>0.47</sub>As gate stacks in recent publications. The D<sub>it</sub> value reported in this paper is the lowest value compared to prior reported HfO<sub>2</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As gate stacks.

| Table 1. Comparison of   | of the electrical | and interfacial | properties | of this | work w | ith some |

|--------------------------|-------------------|-----------------|------------|---------|--------|----------|

| recently reported paper. |                   |                 |            |         |        |          |

| High k                            | Passivation method                         | Channel<br>material                      | $L_{G}$ | EOT or<br>thickness of<br>high-k        | D <sub>it</sub> (cm <sup>-2</sup> eV <sup>-1</sup> ) | SS<br>(mV/dec) | Ref. |

|-----------------------------------|--------------------------------------------|------------------------------------------|---------|-----------------------------------------|------------------------------------------------------|----------------|------|

| Al <sub>2</sub> O <sub>3</sub> *  | -                                          | In <sub>0.53</sub> Ga <sub>0.47</sub> As | -       | 4.2 nm                                  | 5 × 10 <sup>11</sup>                                 | -              | [16] |

| $Al_2O_3$                         | -                                          | $In_{0.53}Ga_{0.47}As$                   | -       | 10 nm of Al <sub>2</sub> O <sub>3</sub> | $2.5 \times 10^{11}$                                 | -              | [17] |

| $Al_2O_3$                         | -                                          | $In_{0.53}Ga_{0.47}As$                   | 1.5 μm  | 8 nm of Al <sub>2</sub> O <sub>3</sub>  | $1 \times 10^{12}$                                   | >200           | [18] |

| $Al_2O_3$                         | -                                          | $In_{0.53}Ga_{0.47}As$                   | 0.5 μm  | 30 nm of Al <sub>2</sub> O <sub>3</sub> | $1.4 \times 10^{12}$                                 | 240            | [19] |

| HfO <sub>2</sub> *                | -                                          | $In_{0.53}Ga_{0.47}As$                   | -       | 2.1 nm                                  | $1 \times 10^{12}$                                   | -              | [16] |

| HfO <sub>2</sub> *                | -                                          | $In_{0.53}Ga_{0.47}As$                   | -       | $7.8 \text{ nm of HfO}_2$               | $2 \times 10^{12}$                                   | -              | [20] |

| HfO <sub>2</sub> *                | Al-doped                                   | $In_{0.53}Ga_{0.47}As$                   | -       | 8–9 nm of HfO <sub>2</sub>              | $6 \times 10^{12}$                                   | -              | [21] |

| HfO <sub>2</sub> *                | $PH_3$                                     | $In_{0.53}Ga_{0.47}As$                   | 4 μm    | 1.7 nm                                  | $8.6 \times 10^{11}$                                 | 103            | [22] |

| HfAlO                             | SiH <sub>4</sub> +NH <sub>3</sub>          | $In_{0.53}Ga_{0.47}As$                   | 2–10 μm | 3.8 nm                                  | $6.5 \times 10^{11}$                                 | 155-210        | [2]  |

| $ZrO_2$                           | LaAlO <sub>3</sub>                         | $In_{0.53}Ga_{0.47}As$                   | 5 μm    | 1.63 nm                                 | $7.5 \times 10^{11}$                                 | 116            | [23] |

| $HfO_2$ $CF_4/O_2$ post treatment | - In <sub>0.53</sub> Ga <sub>0.47</sub> As | 5–20 μm -                                | 1.4 nm  | $4.9 \times 10^{11}$                    | 109                                                  | This           |      |

|                                   |                                            |                                          |         |                                         |                                                      | work           |      |

| HfO <sub>2</sub> Control          |                                            |                                          | 1.35 nm | $2.8 \times 10^{12}$                    | 127                                                  | This           |      |

|                                   |                                            |                                          |         |                                         |                                                      | work           |      |

<sup>\*</sup> Capacitor structure.

## 4. Conclusions

The effects of post-oxide  $CF_4/O_2$  treatment on  $HfO_2/In_{0.53}Ga_{0.47}As$  gate stack have been systematically investigated. The condition for the  $CF_4/O_2$  plasma is optimized to be 30 W for 3–5 min. The gate stack interface quality has been notably improved by F incorporation. The mean  $D_{it}$  value has been reduced ~5× from  $2.8 \times 10^{12}$  to  $4.9 \times 10^{11}$  cm<sup>-2</sup>eV<sup>-1</sup>. As a result, enhanced electrical performances have been presented: steeper SS from 127 to 109 mV/dec, enhanced  $\mu_{eff}$  from 826 to 1,144 cm<sup>2</sup>/Vs, and improved  $G_m$  and  $I_d$  from 3.1 to 3.7 mS/mm and from 1.3 to 1.7 mA/mm, respectively (at  $V_d = 50$  mV, 20  $\mu$ m channel length). These results suggest that the post-HfO<sub>2</sub> F treatment could be a key technique to implement high performance III-V MOSFETs for the sub 22 nm nodes.

# References

- 1. Shahrjerdi, D.; Tutuc, E.; Banerjee, S.K. Impact of surface chemical treatment on capacitance-voltage characteristics of GaAs metal-oxide-semiconductor capacitors with Al<sub>2</sub>O<sub>3</sub> gate dielectric. *Appl. Phys. Lett.* **2007**, *91*, 063501.

- 2. Chin, H.-C.; Liu, X.; Gong, X.; Yeo, Y.-C. Silane and ammonia surface passivation technology for high-mobility In<sub>0.53</sub>Ga<sub>0.47</sub>As MOSFETs. *Trans. Electron. Devices* **2010**, *57*, 973–979.

- 3. Chen, Y.-T.; Zhao, H.; Yum, J.H.; Wang, Y.; Lee, J.C. Metal-oxide-semiconductor field-effect-transistors on indium phosphide using HfO<sub>2</sub> and silicon passivation layer with equivalent oxide thickness of 18 Å. *Appl. Phys. Lett.* **2009**, *94*, 213505.

- 4. CRC. Handbook of Physics and Chemistry, 84th, ed.; CRC: Boca Raton, FL, USA, 2003.

5. Wu, W.-C.; Lai, C.-S.; Lee, S.-C.; Ma, M.-W.; Chao, T.-S.; Wang, J.-C.; Hsu, C.-W.; Chou, P.-C.; Chen, J.-H.; Kao, K.-H.; *et al.* Fluorinated HfO<sub>2</sub> Gate Dielectrics Engineering for CMOS by Pre- and Post-CF<sub>4</sub> Plasma Passivation. In *Proceedings of IEEE International Electron Devices Meeting*, San Francisco, CA, USA, 15–17 December 2008; pp. 1–4.

- 6. Seo, K.; Sreenivasan, R.; McIntyre, P.C.; Saraswat, K.C. Improvement in high-k (HfO<sub>2</sub>/SiO<sub>2</sub>) reliability by incorporation of fluorine. *IEEE Electron. Device Lett.* **2006**, *27*, 821–823.

- 7. Xie, R.; He, W.; Yu, M.; Zhu, C. Effects of fluorine incorporation and forming gas annealing on high-k gated germanium metal-oxide-semiconductor with GeO<sub>2</sub> surface passivation. *Appl. Phys. Lett.* **2008**, *93*, 073504.

- 8. Chin, H.-C.; Gong, X.; Wang, L.; Yeo, Y.-C. Fluorine incorporation in HfAlO gate dielectric for defect passivation and effect on electrical characteristics of In<sub>0.53</sub>Ga<sub>0.47</sub>As n-MOSFETs. *Electrochem. Solid State Lett.* **2010**, *13*, H440–H442.

- 9. Chen, Y.-T.; Zhao, H.; Yum, J.H.; Wang, Y.; Xue, F.; Zhou, F.; Lee, J.C. Improved electrical characteristics of TaN/Al<sub>2</sub>O<sub>3</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As metal-oxide-semiconductor field-effect transistors by fluorine incorporation. *Appl. Phys. Lett.* **2009**, *95*, 013501.

- Zhao, H.; Chen, Y.; Yum, J.H.; Wang, Y.; Lee, J.C. HfO<sub>2</sub>-based In<sub>0.53</sub>Ga<sub>0.47</sub>As MOSFETs (EOT ≈ 10Å) Using Various Interfacial Dielectric Layers. In *Proceedings of IEEE 67th Device Research Conference*, University Park, PA, USA, 22–24 June 2009; pp. 89–90.

- 11. Zhao, H.; Yum, J.H.; Chen, Y.-T.; Lee, J.C. In<sub>0.53</sub>Ga<sub>0.47</sub>As n-metal-oxide-semiconductor field effect transistors with atomic layer deposited Al<sub>2</sub>O<sub>3</sub>, HfO<sub>2</sub>, and LaAlO<sub>3</sub> gate dielectrics. *J. Vac. Sci. Technol. B* **2009**, *27*, 2024–2027.

- 12. Lee, S.; Park, J.-W. Effect of fluorine on dielectric properties of SiOF films. *J. Appl. Phys.* **1996**, 80, 5260–5263.

- 13. Tatsumi, T.; Fukuda, S.; Kadomura, S. Etch rate acceleration of SiO<sub>2</sub> during wet treatment after gate etching. *Jpn. J. Appl. Phys.* **1993**, *32*, 6114–6118.

- 14. Groeseneken, G.; Maes, H.E.; Beltran, N.; Dekeersmaecker, R.F. A reliable approach to charge-pumping measurements in MOS transistors. *IEEE Trans. Electron. Devices* **1984**, *31*, 42–53.

- 15. Xie, R.; Phung, T.H.; He, W.; Sun, Z.; Yu, M.; Cheng, Z.; Zhu, C. High Mobility High-k/Ge pMOSFETs with 1 nm EOT—New Concept on Interface Engineering and Interface Characterization. In *Proceedings of 2008 IEEE International Electron Devices Meeting (IEDM)*, San Francisco, CA, USA, 15–17 December 2008; pp. 393–396.

- 16. Zhao, H.; Huang, J.; Chen, Y.-T.; Yum, J.H.; Wang, Y.; Xue, F.; Zhou, F.; Lee, J.C. Effects of gate-first and gate-last process on interface quality of In<sub>0.53</sub>Ga<sub>0.47</sub>As metal-oxide-semiconductor capacitors using atomic-layer-deposited Al<sub>2</sub>O<sub>3</sub> and HfO<sub>2</sub> oxides. *Appl. Phys. Lett.* **2009**, *95*, 253501.

- 17. Chiu, H.C.; Tung, L.T.; Chang, Y.H.; Lee, Y.J.; Chang, C.C.; Kwo, J.; Hong, M. Achieving a low interfacial density of states in atomic layer deposited Al<sub>2</sub>O<sub>3</sub> on In<sub>0.53</sub>Ga<sub>0.47</sub>As. *Appl. Phys. Lett.* **2008**, *93*, 202903.

18. Lin, D.; Brammertz, G.; Sioncke, S.; Fleischmann, C.; Delabie, A.; Martens, K.; Bender, H.; Conard, T.; Tseng, W.H.; Lin, J.C.; *et al.* Enabling the high-performance InGaAs/Ge CMOS: A common gate stack solution. In *Proceedings of 2009 IEEE International Electron Devices Meeting (IEDM)*, Baltimore, MD, USA, 7–9 December 2009; pp. 1–4.

- 19. Xuan, Y.; Wu, Y.; Shen, T.; Yang, T.; Ye, P. High Performance Submicron Inversion-Type Enhancement-Mode InGaAs MOSFETs with ALD Al<sub>2</sub>O<sub>3</sub>, HfO<sub>2</sub> and HfAlO as Gate Dielectrics. In *Proceedings of 2007 IEEE International Electron Devices Meeting (IEDM)*, Washington, DC, USA, 10–12 December 2007; pp. 637–640.

- 20. Chang, Y.C.; Huang, M.L.; Lee, K.Y.; Lee, Y.J.; Lin, T.D.; Hong, M.; Kwo, J.; Lay, T.S.; Liao, C.C.; Cheng, K.Y. Atomic-layer-deposited HfO<sub>2</sub> on In<sub>0.53</sub>Ga<sub>0.47</sub>As: Passivation and energy-band parameters. *Appl. Phys. Lett.* **2008**, *92*, 072901.

- 21. Hwang, Y.; Chobpattana, V.; Zhang, J.Y.; LeBeau, J.M.; Engel-Herbert, R.; Stemmer, S. Al-doped HfO<sub>2</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As metal-oxide-semiconductor capacitors. *Appl. Phys. Lett.* **2011**, *98*, 142901.

- 22. Lin, J.; Lee, S.; Oh, H.-J.; Yang, W.; Lo, G.Q.; Kwong, D.L.; Chi, D.Z. Plasma PH<sub>3</sub>-Passivated High Mobility Inversion InGaAs MOSFET Fabricated with Self-Aligned Gate-First Process and HfO<sub>2</sub>/TaN Gates Stack. In *Proceedings of 2008 IEEE International Electron Devices Meeting (IEDM)*, San Francisco, CA, USA, 15–17 December 2008; pp. 401–404.

- 23. Huang, J.; Goel, N.; Zhao, H.; Kang, C.Y.; Min, K.S.; Bersuker, G.; Oktyabrsky, S.; Gaspe, C.K.; Santos, M.B.; Majhi, P.; *et al.* InGaAs MOSFET Performance and Reliability Improvement by Simultaneous Reduction of Oxide and Interface Charge in ALD (La)AlOx/ZrO<sub>2</sub> Gate Stack. In *Proceedings of 2009 IEEE International Electron Devices Meeting (IEDM)*, Baltimore, MD, USA, 7–9 December 2009; pp. 335–338.

- © 2012 by the authors; licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution license (http://creativecommons.org/licenses/by/3.0/).