Models and Techniques for Temperature Robust Systems on a Reconfigurable Platform

Abstract

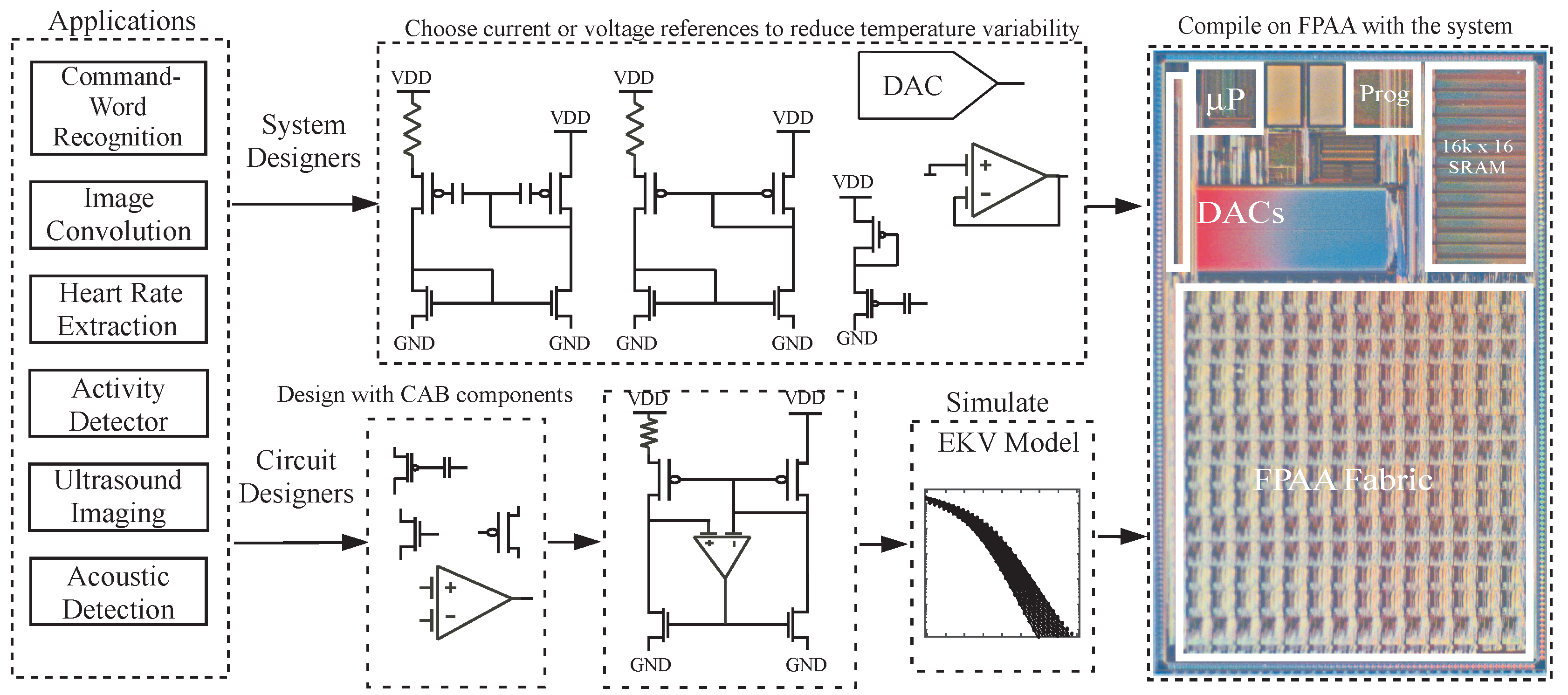

:1. Analog Processing and Temperature Dependence

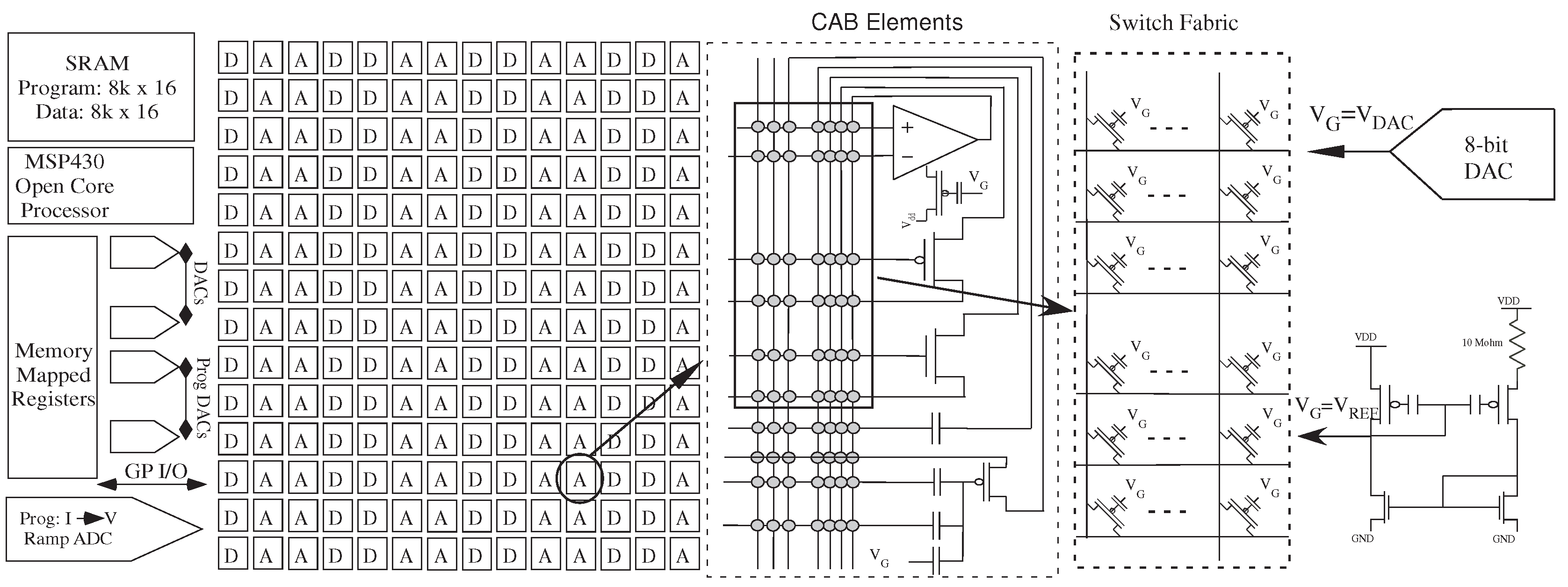

2. Field-Programmable Analog Array

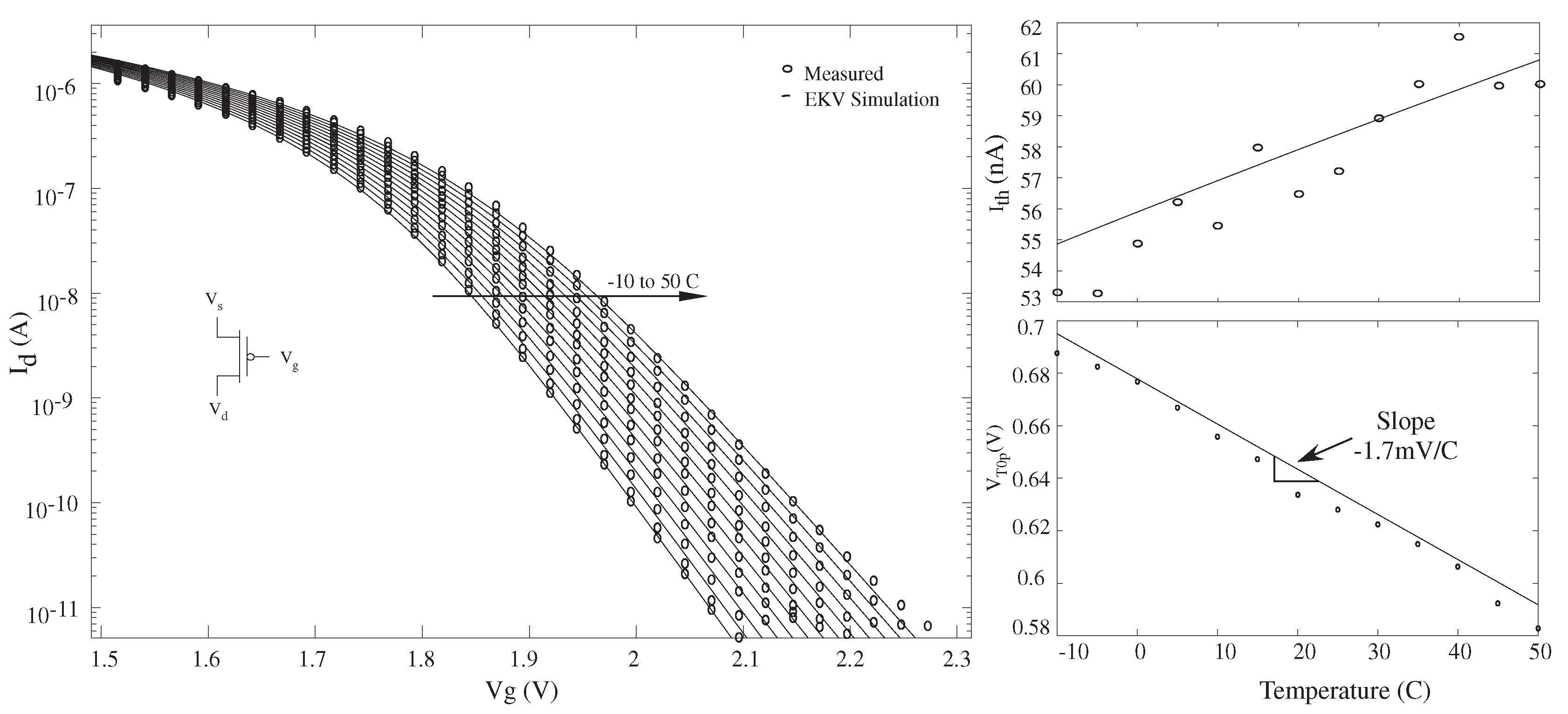

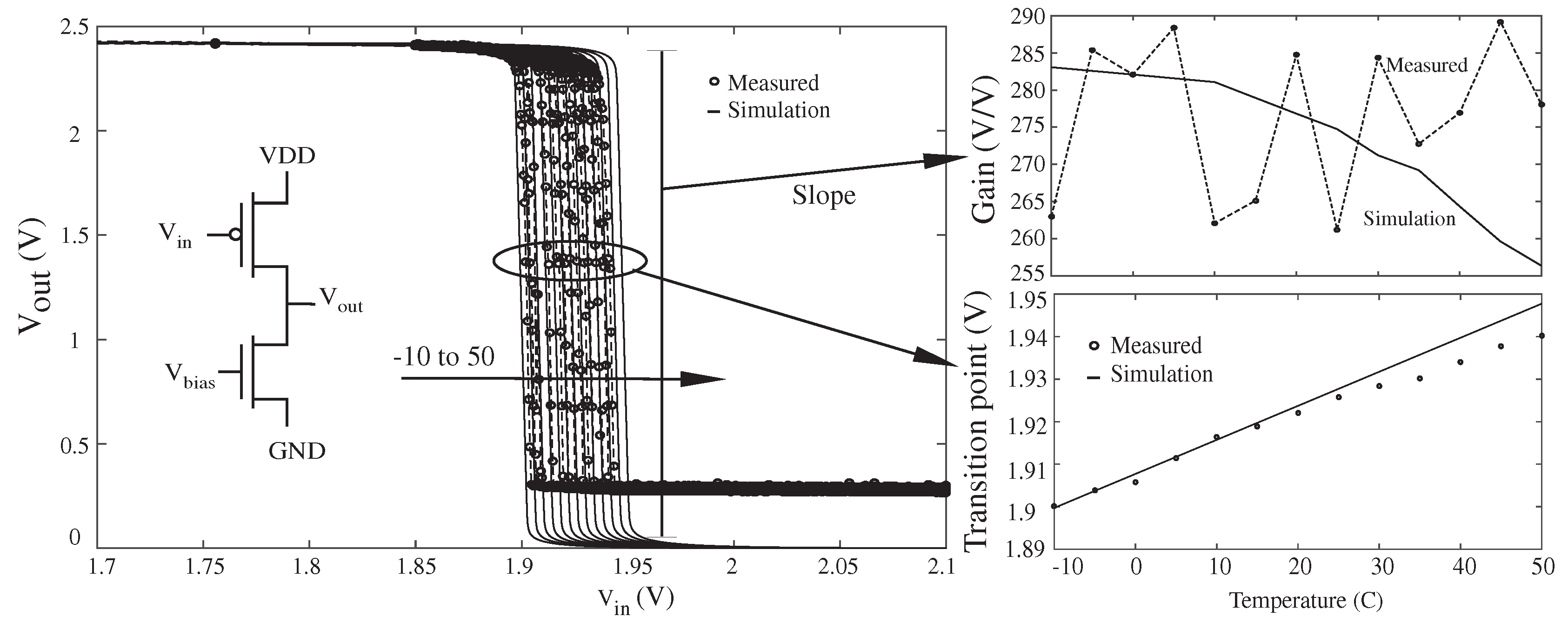

3. Modeling Temperature Dependence

4. Temperature Dependence of Simple Single Ended Circuits

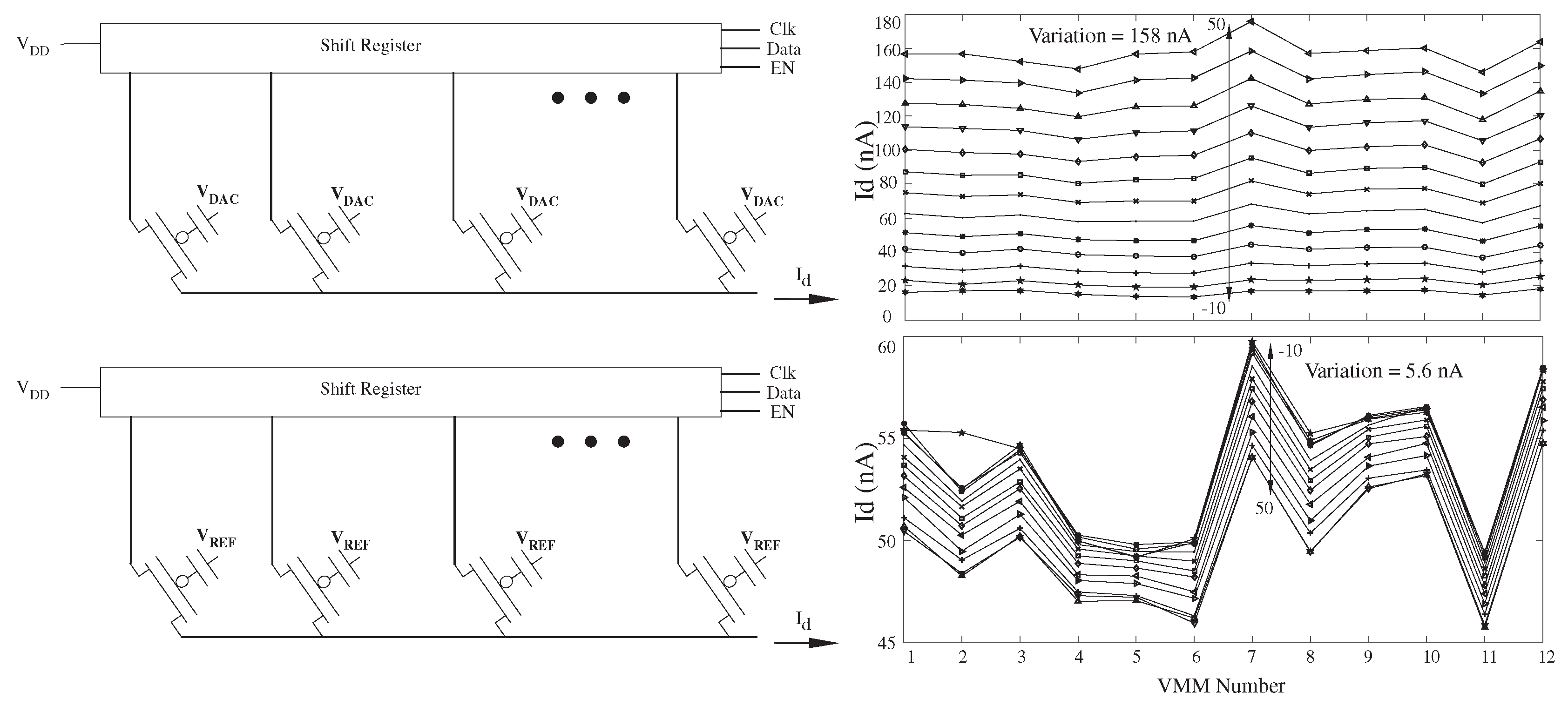

5. Reducing Temperature Dependence in Programmable Circuits and System

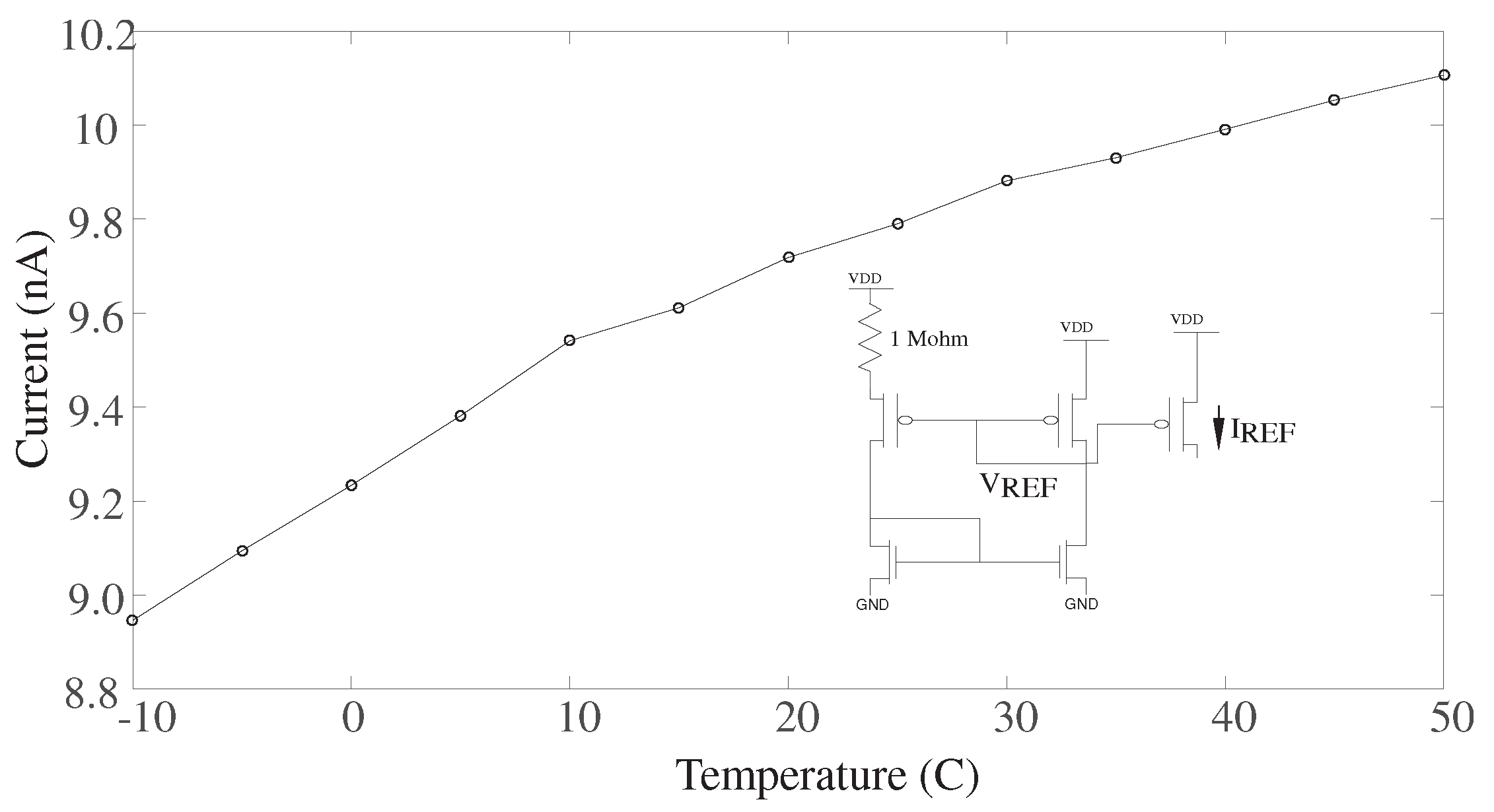

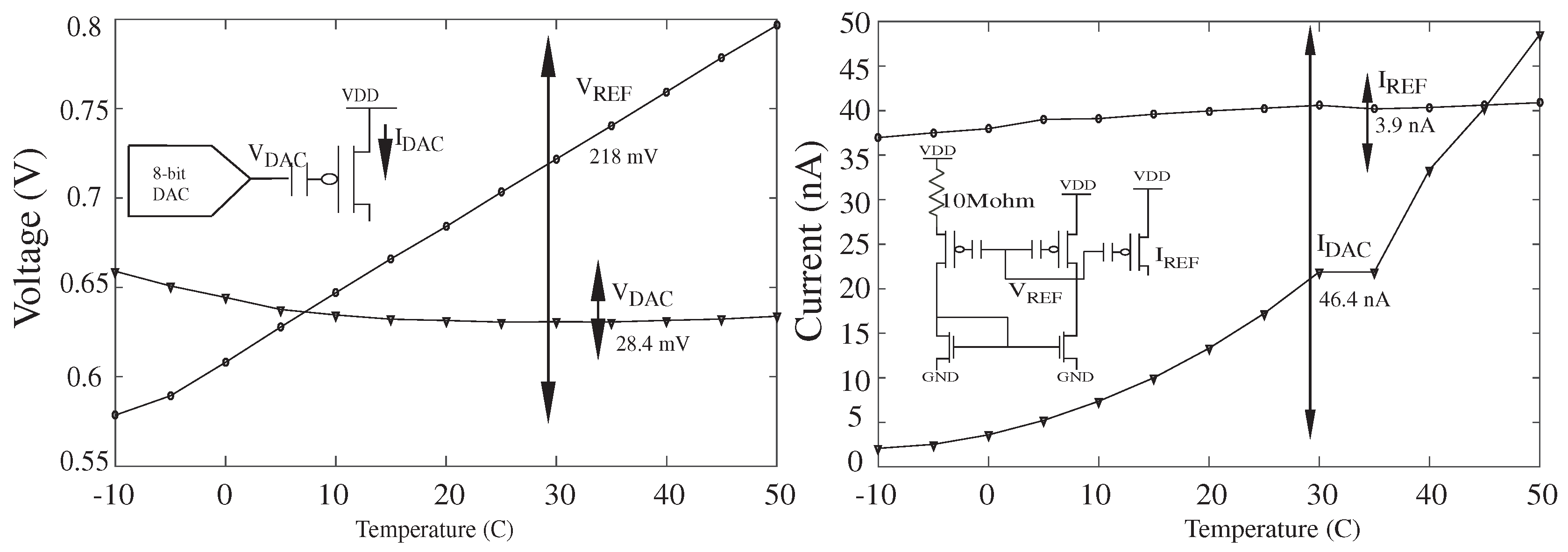

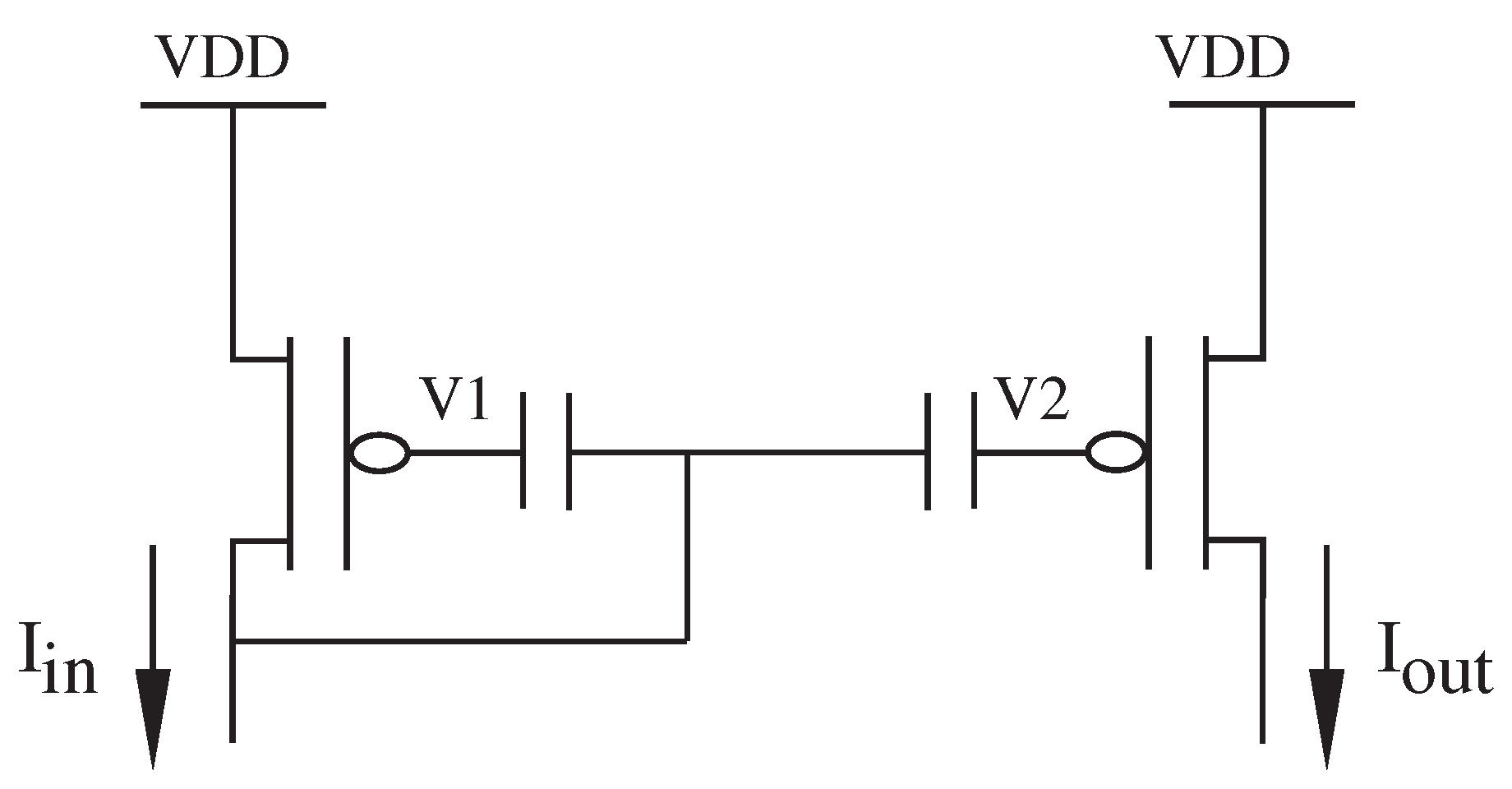

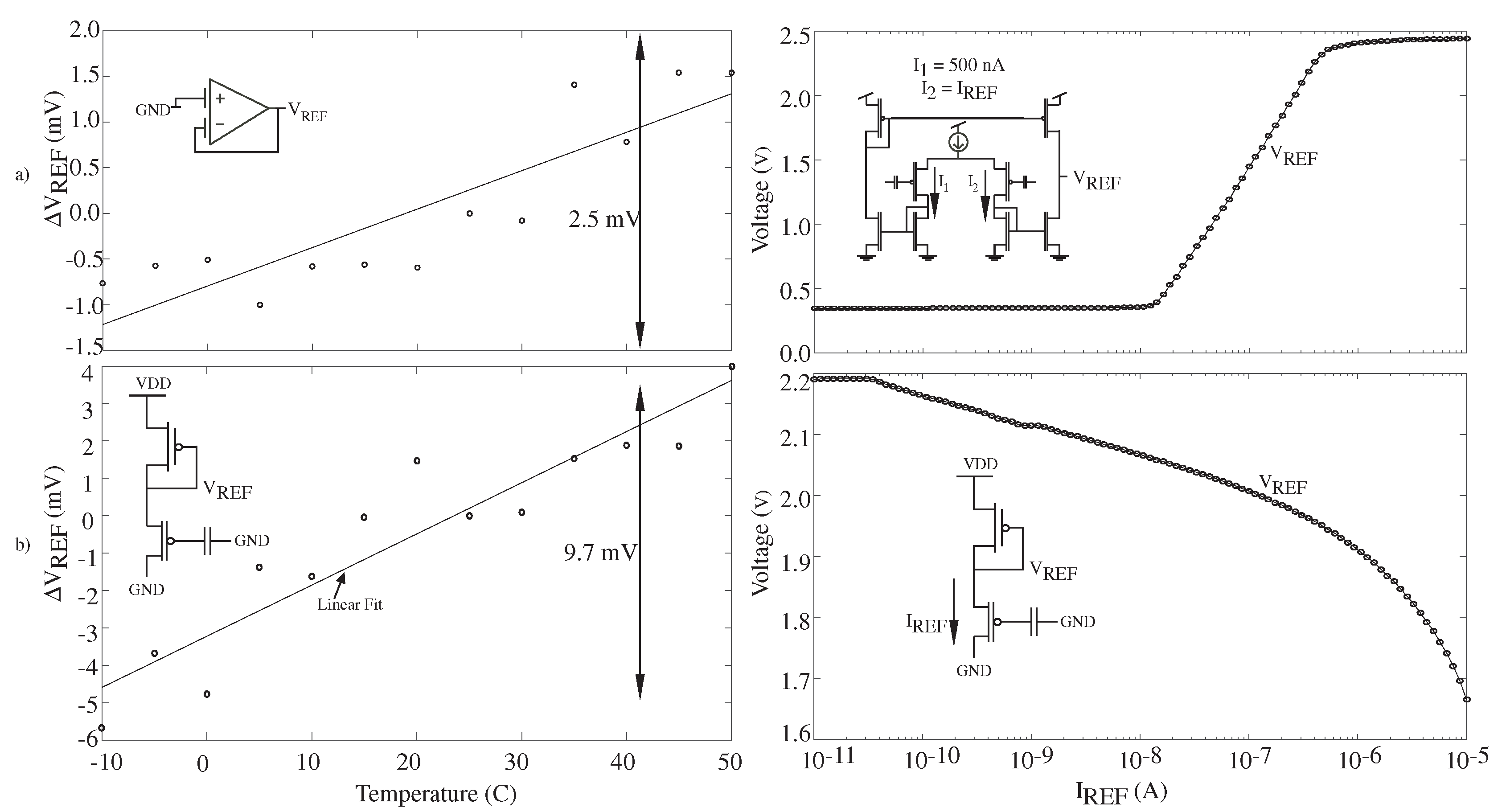

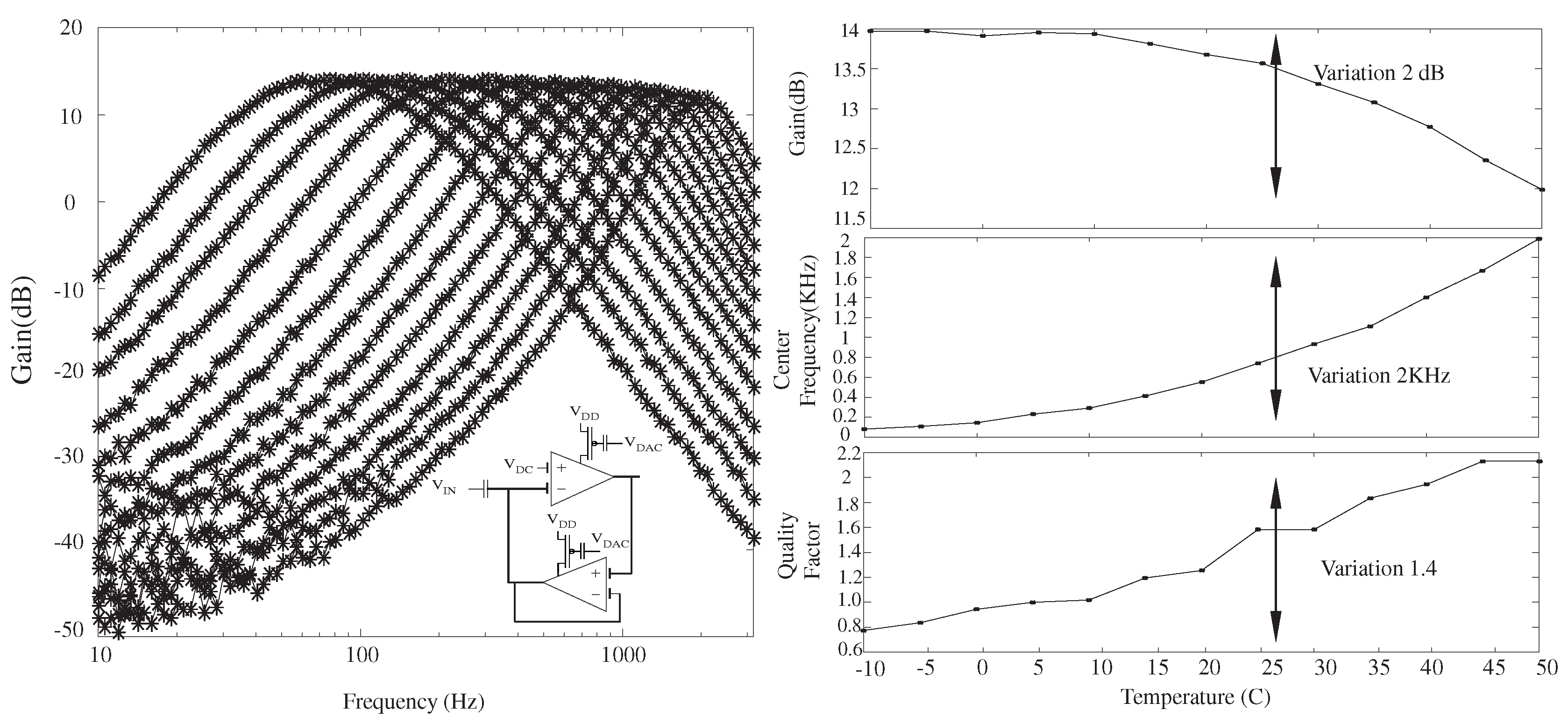

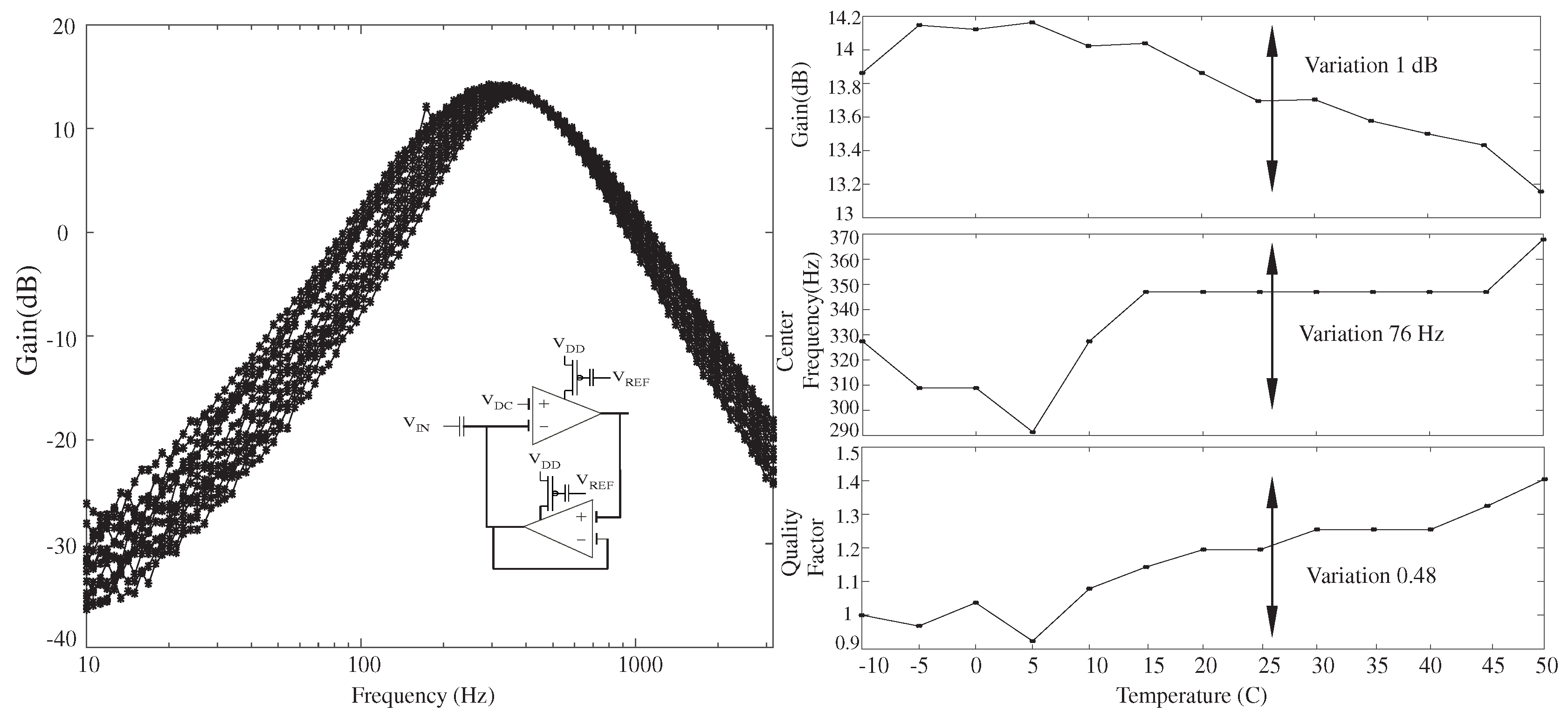

5.1. FG-Based Reference Circuit in Subthreshold Region

5.2. FG-Based Voltage Reference without Resistors

6. Vector Matrix Multiplication (VMM)

7. Variation of Band-Pass Filter

8. Summary and Discussion

Author Contributions

Conflicts of Interest

References

- Hersek, S.; Toreyin, H.; Inan, O.T. A Robust System for Longitudinal Knee Joint Edema and Blood Flow Assessment Based on Vector Bioimpedance Measurements. IEEE Trans. Biomed. Circuits Syst. 2016, 10, 545–555. [Google Scholar]

- Toreyin, H.; Shah, S.; Hersek, S.; Inan, O.T.; Hasler, J. Proof-of-Concept Energy-Efficient and Real-Time Hemodynamic Feature Extraction from Bioimpedance Signals using a Mixed-Signal Field Programmable Analog Array. In Proceedings of the International Conference on Biomedical and Health Informatics (BHI), Orlando, FL, USA, 16–19 Feburary 2017. [Google Scholar]

- Shah, S.; Toreyin, H.; Inan, O.T.; Hasler, J. Reconfigurable Analog Classifier For Knee-Joint Rehabilitation. IEEE Eng. Med. Biol. Soci. 2016. [Google Scholar] [CrossRef]

- Sahil, S.; Jennifer, H. Low Power Speech Detector On A FPAA. Presented at ISCAS 2017, Baltimore, MD, USA, 28–31 May 2017. [Google Scholar]

- George, S.; Kim, S.; Shah, S.; Hasler, J.; Collins, M.; Adil, F.; Wunderlich, R.; Nease, S.; Ramakrishnan, S. A Programmable and Configurable Mixed-Mode FPAA SoC. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2016, 24, 2253–2261. [Google Scholar] [CrossRef]

- Teague, C.; Hersek, S.; Toreyin, H.; Millard-Stafford, M.L.; Jones, M.L.; Kogler, G.F.; Sawka, M.N.; Inan, O.T. Novel approaches to measure acoustic emissions as biomarkers for joint health assessment. In Proceedings of the 2015 IEEE 12th International Conference on Wearable and Implantable Body Sensor Networks (BSN), Cambridge, MA, USA, 9–12 June 2015; pp. 1–6. [Google Scholar]

- Etemadi, M.; Inan, O.T.; Heller, J.A.; Hersek, S.; Klein, L.; Roy, S. A Wearable Patch to Enable Long-Term Monitoring of Environmental, Activity and Hemodynamics Variables. IEEE Trans. Biomed. Circuits Syst. 2016, 10, 280–288. [Google Scholar] [CrossRef] [PubMed]

- Shah, S.; Smith, J.; Stowell, J.; Christen, J.B. Biosensing platform on a flexible substrate. Sens. Actuators B Chem. 2015, 210, 197–203. [Google Scholar] [CrossRef]

- Ahuja, B.K.; Vu, H.; Laber, C.A.; Owen, W.H. A very high precision 500-nA CMOS floating-gate analog voltage reference. IEEE J. Solid-State Circuits 2005, 40, 2364–2372. [Google Scholar] [CrossRef]

- Kim, S.; Shah, S.; Wunderlich, R.; George, S.; Hasler, J. CAD Synthesis Tools for Large-Scale Floating-Gate FPAA System. Trans. Comput. Aided Des. 2017. under review. [Google Scholar]

- Natarajan, A.; Hasler, J. Modeling, simulation and implementation of circuit elements in an open-source tool set on the FPAA. Anal. Integr. Circuits Signal Process. 2017, 91, 119–130. [Google Scholar] [CrossRef]

- Shah, S.; Teague, C.N.; Inan, O.T.; Hasler, J. A Proof-of-Concept Classifier for Acoustic Signals from the Knee Joint on a FPAA. In Proceedings of the 2016 IEEE SENSORS, Orlando, FL, USA, 30 Octorber–3 November 2016. [Google Scholar]

- Gurun, G.; Tekes, C.; Zahorian, J.; Xu, T.; Satir, S.; Karaman, M.; Hasler, J.; Degertekin, F.L. Single-chip CMUT-on-CMOS front-end system for real-time volumetric IVUS and ICE imaging. IEEE Trans. Ultrason. Ferroelectr. Freq. Control 2014, 61, 239–250. [Google Scholar] [CrossRef] [PubMed]

- Kim, S.; Hasler, J.; George, S. Integrated Floating-Gate Programming Environment for System-Level ICs. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2016, 24, 2242–2252. [Google Scholar] [CrossRef]

- Enz, C.C.; Krummenacher, F.; Vittoz, E.A. An analytical MOS transistor model valid in all regions of operation and dedicated to low-voltage and low-current applications. Anal. Integr. Circuits Signal Process. 1995, 8, 83–114. [Google Scholar] [CrossRef]

- Pierret, R. Semiconductor Device Fundamentals; Addison-Wesley: Boston, MA, USA, 1996. [Google Scholar]

- Hasler, J.; Kim, S.; Adil, F. Scaling Floating-Gate Devices Predicting Behavior for Programmable and Configurable Circuits and Systems. J. Low Power Electron. Appl. 2016, 6, 13. [Google Scholar] [CrossRef]

- Minch, B. EKV MOS Transistor Model Summary. Available online: http://madvlsi.olin.edu/circuits/handouts.html (accessed on 2 Feburary 2017).

- Degnan, B.P. Temperature Robust Programmable Subthreshold Circuits Through A Balanced Force Approach. Ph.D. Thesis, Georgia Institute of Technology, Atlanta, GA, USA, 2013. [Google Scholar]

- Kim, S.; Shah, S.; Hasler, J. Calibration of Floating-Gate SoC FPAA System. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2017, 25, 2649–2657. [Google Scholar] [CrossRef]

- Vittoz, E.; Fellrath, J. CMOS analog integrated circuits based on weak inversion operations. IEEE J. Solid-State Circuits 1977, 12, 224–231. [Google Scholar] [CrossRef]

- Srinivasan, V.; Serrano, G.; Twigg, C.M.; Hasler, P. A Floating-Gate-Based Programmable CMOS Reference. IEEE Trans. Circuits Syst. I Regul. Pap. 2008, 55, 3448–3456. [Google Scholar] [CrossRef]

- Georgiou, J.; Toumazou, C. A resistorless low current reference circuit for implantable devices. In Proceedings of the 2002 IEEE International Symposium on Circuits and Systems (Cat. No. 02CH37353), Phoenix-Scottsdale, AZ, USA, 26–29 May 2002; Volume 3, pp. III-193–III-196. [Google Scholar]

- Seok, M.; Kim, G.; Blaauw, D.; Sylvester, D. A Portable 2-Transistor Picowatt Temperature-Compensated Voltage Reference Operating at 0.5 V. IEEE J. Solid-State Circuits 2012, 47, 2534–2545. [Google Scholar] [CrossRef]

- Ramakrishnan, S.; Hasler, J. Vector-Matrix Multiply and Winner-Take-All as an Analog Classifier. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2014, 22, 353–361. [Google Scholar] [CrossRef]

- Ramakrishnan, S.; Basu, A.; Chiu, L.K.; Hasler, J.; Anderson, D.; Brink, S. Speech Processing on a Reconfigurable Analog Platform. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2014, 22, 430–433. [Google Scholar] [CrossRef]

- Lazzaro, J.; Ryckebusch, S.; Mahowald, M.; Mead, C.A. Winner-Take-All Networks of O(N) Complexity. In Advances in Neural Information Processing Systems 1; Touretzky, D., Ed.; Morgan-Kaufmann: Burlington, MA, USA, 1989; pp. 703–711. [Google Scholar]

- Graham, D.W.; Hasler, P.E.; Chawla, R.; Smith, P.D. A Low-Power Programmable Bandpass Filter Section for Higher Order Filter Applications. IEEE Trans. Circuits Syst. I Regul. Pap. 2007, 54, 1165–1176. [Google Scholar] [CrossRef]

- Guo, N.; Huang, Y.; Mai, T.; Patil, S.; Cao, C.; Seok, M.; Sethumadhavan, S.; Tsividis, Y. Energy-Efficient Hybrid Analog/Digital Approximate Computation in Continuous Time. IEEE J. Solid-State Circuits 2016, 51, 1514–1524. [Google Scholar] [CrossRef]

- Dorigo, D.D.; Manoli, Y. An OTA-C signal processing FPAA with 305 MHz GBW and integrated frequency-independent filter tuning. In Proceedings of the 2016 IEEE Asian Solid-State Circuits Conference (A-SSCC), Toyama, Japan, 7–9 November 2016; pp. 61–64. [Google Scholar]

- Becker, J.; Anders, J.; Ortmanns, M. A continuous-time field programmable analog array with 1 GHz GBW. In Proceedings of the 2016 IEEE International Conference on Electronics, Circuits and Systems (ICECS), Monte Carlo, Monaco, 11–14 December 2016; pp. 209–212. [Google Scholar]

- Dilello, A.; Andryzcik, S.; Kelly, B.M.; Rumberg, B.; Graham, D.W. Temperature Compensation of Floating-Gate Transistors in Field-Programmable Analog Arrays. In Proceedings of the IEEE Internation Symposium on Circuits and System, Baltimore, MD, USA, 28 May 2017. [Google Scholar]

- Peng, S.Y.; Liu, L.H.; Chang, P.K.; Wang, T.Y.; Li, H.Y. A Power-Efficient Reconfigurable Output-Capacitor-Less Low-Drop-Out Regulator for Low-Power Analog Sensing Front-End. IEEE Trans. Circuits Syst. I Regul. Pap. 2017, 64, 1318–1327. [Google Scholar]

| Device Parameter | Measured | Simulated | ||||||

|---|---|---|---|---|---|---|---|---|

| Threshold Voltage | Threshold Voltage | |||||||

| pFET | −0.28% | −1.7 mV/C | 0.2% | 2000 ppm/C | −0.27% | −1.7 mV/C | 0.17% | 1700 ppm/C |

| nFET | −0.26% | −1.1 mV/C | 0.24% | 2400 ppm/C | −0.22% | −0.95 mV/C | 0.17% | 1700 ppm/C |

© 2017 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Shah, S.; Toreyin, H.; Hasler, J.; Natarajan, A. Models and Techniques for Temperature Robust Systems on a Reconfigurable Platform. J. Low Power Electron. Appl. 2017, 7, 21. https://doi.org/10.3390/jlpea7030021

Shah S, Toreyin H, Hasler J, Natarajan A. Models and Techniques for Temperature Robust Systems on a Reconfigurable Platform. Journal of Low Power Electronics and Applications. 2017; 7(3):21. https://doi.org/10.3390/jlpea7030021

Chicago/Turabian StyleShah, Sahil, Hakan Toreyin, Jennifer Hasler, and Aishwarya Natarajan. 2017. "Models and Techniques for Temperature Robust Systems on a Reconfigurable Platform" Journal of Low Power Electronics and Applications 7, no. 3: 21. https://doi.org/10.3390/jlpea7030021