Review

# Scalable Fabrication of 2D Semiconducting Crystals for Future Electronics

Jiantong Li and Mikael Östling \*

KTH Royal Institute of Technology, School of Information and Communication Technology, Electrum 229, SE-16440 Kista, Sweden; E-Mail: jiantong@kth.se

\* Author to whom correspondence should be addressed; E-Mail: ostling@kth.se; Tel.: +46-8-790-4301; Fax: +46-8-790-4300.

Academic Editor: Frank Schwierz

Received: 8 October 2015 / Accepted: 16 November 2015 / Published: 3 December 2015

**Abstract:** Two-dimensional (2D) layered materials are anticipated to be promising for future electronics. However, their electronic applications are severely restricted by the availability of such materials with high quality and at a large scale. In this review, we introduce systematically versatile scalable synthesis techniques in the literature for high-crystallinity large-area 2D semiconducting materials, especially transition metal dichalcogenides, and 2D material-based advanced structures, such as 2D alloys, 2D heterostructures and 2D material devices engineered at the wafer scale. Systematic comparison among different techniques is conducted with respect to device performance. The present status and the perspective for future electronics are discussed.

**Keywords:** 2D materials; transition metal dichalcogenides; field effect transistors; scalable synthesis; vapor phase deposition; 2D semiconducting alloys; 2D heterostructures; selective growth; multi-level stacked devices

## 1. Introduction

Two-dimensional (2D) layered materials, such as graphene, boron nitride (BN) and transition metal dichalcogenides (TMDCs), have attracted tremendous interest in extensive research fields [1–3], due to their general excellent electronic, optical and mechanical properties. It is widely accepted that 2D materials will play an important role in the applications of next-generation nanoelectronics [4–6],

optoelectronics [7,8], emerging (flexible, organic, printed and stretchable) electronics [9], energy conversion and storage [10], sensing [11] and medicine and biology [12]. As for the application in the upcoming high-end nanoelectronics, 2D materials possess unique electronic performance as compared with their bulk form (conventional three-dimensional (3D) materials) [13] and easy manipulation for complex structures as compared with the one-dimensional materials [14]. Recently, 2D semiconducting crystals, such as TMDCs and black phosphorous [15], have received increasing attention in electronic applications. At present, the majority of 2D semiconducting crystals lie in the family of TMDCs with the formula MX2, where M is a transition metal element from Group IV (e.g., Ti, Zr or Hf), Group V (e.g., V, Nb or Ta) or Group VI (e.g., Mo or W), and X is a chalcogen (S, Se or Te) [2]. With a simple mechanical cleavage technique, monolayer (sub-nm thick) MoS2 has been fabricated and used to demonstrate high-performance field-effect transistors (FETs) with room-temperature mobility ~200 cm² V<sup>-1</sup> s<sup>-1</sup> and a current on/off ratio ~10<sup>8</sup> [14], verifying the promise of 2D materials for nanoelectronics. However, in order to realize the transfer from lab-scale fabrication to industrial-scale manufacturing for future electronics, scalable synthesis techniques of 2D semiconducting crystals are indispensable.

A variety of scalable synthesis techniques for 2D TMDCs have been developed in the recent literature. In this review, we systematically introduce those techniques that produce highly-crystalline large-area 2D crystals and that have great potential for manufacturing in future nanoelectronics. There are also some other scalable synthesis techniques for nanosheets of 2D materials, such as solvent exfoliation [16] and inkjet printing [17,18]. Despite their promising applications in other fields, e.g., printed electronics and energy storage, they may not be suitable for high-end nanoelectronics and are not included in this review. Section 2 introduces scalable synthesis techniques for large-area (typically wafer-scale) monolayer or few-layer TMDCs. Section 3 introduces the advanced engineering of 2D TMDCs, including 2D TMDC alloys, 2D heterostructures and wafer-scale fabrication of 2D TMDC devices. In Section 4, we benchmark the performance of TMDC FETs based on different scalable synthesis techniques against those based on mechanical cleavage, and offer an outlook for the research tendency in the near future.

## 2. Scalable Synthesis Techniques for TMDCs

Here, we briefly introduce the recently-developed synthesis techniques for wafer-scale TMDCs, including vapor phase deposition, thermal decomposition, magnetron sputtering and molecular beam epitaxial.

## 2.1. Vapor Phase Deposition

Currently, the predominant and most promising scalable synthesis technique for large-area atomically-thin TMDCs is vapor phase deposition (VPD). In general, VPD relies on the chemical reaction or physical transport (often with inert gas as the carrier) of vaporized precursors to deposit TMDCs onto the substrate surface. In terms of the initial precursor state, VPD can be classified into solid-precursor VPD and gas-precursor VPD.

#### 2.1.1. Solid-Precursor VPD

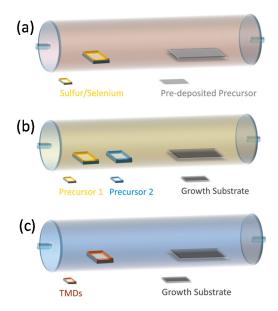

So far, most of the VPD techniques are based on solid-state precursors. Usually, transition metal, metal oxides or chlorides, such as MoO<sub>3</sub>, MoCl<sub>5</sub> and WO<sub>3</sub>, act as the metal precursors, while S/Se powders as the chalcogen precursors [19]. Solid-precursor VPD has been widely employed to synthesize not only pure 2D TMDC crystals, but also TMDC alloys and heterostructures, to be discussed in Section 3. As illustrated in Figure 1, three classes of solid-precursor VPD techniques have been demonstrated in the literature [20]: (1) simple chalcogenization of predefined metal (or metal oxide) film (Figure 1a), where metal or metal oxide thin films are first deposited onto the substrates, then chalcogen powers are heated to be vapors and transported to the substrates and, finally, the metal/metal oxide films are annealed at the atmosphere of chalcogen vapors to produce TMDCs; (2) chemical vapor deposition (CVD) based on the reaction between metal precursors and chalcogen precursors (Figure 1b), where both solid metal precursors and chalcogen powders are heated separately into the vapor phase, and are transported to and react on the substrate surface to form 2D TMDC crystals; and (3) vapor-solid growth based on vapor phase transport and recrystallization of TMDCs (Figure 1c), where TMDC powders serve as the precursors which are vaporized and transported to the cool substrate region and recrystallize to 2D crystals.

**Figure 1.** Schematic of three types of solid-precursor vapor phase deposition techniques for scalable synthesis of large-area transition metal dichalcogenides (TMDCs). (a) Vapor phase chalcogenization of pre-deposited precursor (metal, metal oxide, *etc.*) film; (b) chemical vapor deposition; (c) physical vapor deposition. Adapted with permission from [20]. Copyright 2015, The Royal Society of Chemistry.

The principle and methodology of the solid-precursor VPD techniques have been elaborated in a recent relevant review by Shi *et al.* [20]. In general, TMDCs synthesized through chalcogenization of predefined metal/metal oxide film (Class (1)) give rise to low carrier mobility (<0.1 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>) [20,21]. In contrast, the chemical reaction-based synthesis (Class (2)) is more favorable because of the technique's simplicity, preference for monolayer growth and typically high mobility over

10 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> [20,22]. For all of the techniques, a critical challenge is the limited spatial uniformity. In most cases, spatially inhomogeneous mixtures of monolayer, multi-layer and no-growth regions are obtained [23]. In this section, we focus on the introduction of recent innovative strategies that lead to higher uniformity and/or better controllability.

Pre-treated substrates: Most studies on VPD synthesis use SiO<sub>2</sub> as the growth substrates. However, because of the amorphous nature of the SiO<sub>2</sub> substrate and its relatively high surface roughness, the obtained TMDCs usually suffer from high-density grain boundaries and random orientation among domains. This inevitably generates severe non-uniformity and hinders the scalable growth of large-area high-quality 2D TMDCs. One effective solution is to use an atomically-smooth crystalline substrate [22] to control the crystallographic orientation of TMDC domains during growth and to attain a uniform layer with reduced grain boundary density.

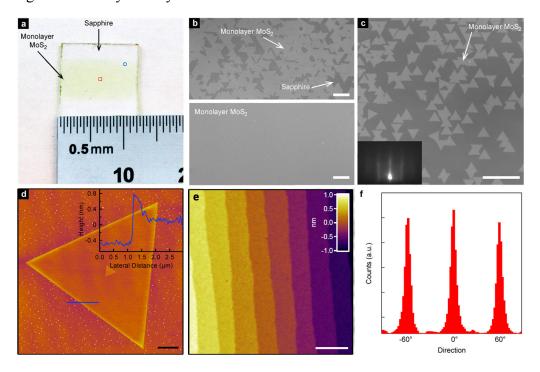

**Figure 2.** Monolayer MoS<sub>2</sub> growth on sapphire with controlled lattice orientation. (a) Photograph of centimeter-scale MoS<sub>2</sub> film on sapphire; (b) optical microscope images of the sample in (a) at the edge region (top, the circle region in (a), scale bar: 20 μm) and the center region (bottom, the square region in (a), scale bar: 10 μm); (c) optical microscope images of the grown monolayer MoS<sub>2</sub> grains, scale bar: 50 μm; the inset is a reflection a high-energy electron diffraction (RHEED) pattern showing a long-range structure order; (d) atomic force microscope (AFM) image of a monolayer MoS<sub>2</sub> grain (inset: thickness profile along the blue line; scale bar: 2 μm); (e) AFM image of annealed sapphire as the growth substrates, where atomically-smooth terraces occurs on the surface (scale bar: 100 nm); (f) the orientation histogram based on the area shown in (c) confirms good control over lattice orientation. Adapted with permission from [24]. Copyright 2015, American Chemical Society.

Sapphire is a suitable substrate for CVD growth of TMDCs [24,25]. In particular, Dumcenco *et al.* [24] have recently achieved good control over lattice orientation (Figure 2) during CVD growth (based on the reaction between vaporized MoO<sub>3</sub> and sulfur) and obtained high-quality monolayer MoS<sub>2</sub> with

centimeter-scale uniformity (Figure 2a,b). The key to the lattice orientation is the introduction of terraces on the sapphire surface (Figure 2e) via annealing in air at an elevated temperature of 1000 °C prior to the growth process. The CVD growth produces well-defined equilateral triangular single-crystal domains (Figure 2d) that merge into a continuous monolayer film with a typical coverage area of 6 mm  $\times$  1 cm in the center of the sapphire substrate (Figure 2b). In addition, over 90% of domains (Figure 2c,f) are well aligned with the relative edge orientation at multiples of 60°. A striking merit of the technique is that the relatively weak van der Waals interaction between sapphire and MoS<sub>2</sub>, on the one hand, effectively induces lattice alignment, while on the other hand, allows easy transfer of the grown MoS<sub>2</sub> from the sapphire substrate to silicon wafers, which facilitates the fabrication of high-performance FETs. As a result, a high mobility of about 43 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> has been attained for devices based on single grains of the grown MoS<sub>2</sub>. Even for devices based on the large-area MoS<sub>2</sub> films, which contain grain boundaries, the mobility still retains about 25 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>. In particular, there is no evident mobility degradation when the channel length increasing from 4  $\mu$ m to ~80  $\mu$ m.

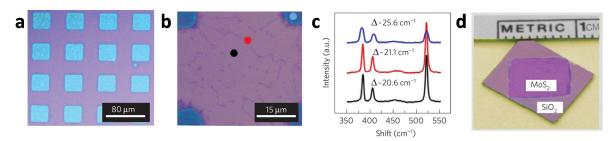

In addition to sapphire substrates, Najmaei *et al.* [21] developed a CVD process to grow centimeter-scale MoS<sub>2</sub> film directly on patterned SiO<sub>2</sub>/Si wafers. Based on the observation that MoS<sub>2</sub> triangular domains and films are commonly nucleated and formed in the vicinity of substrates' edges, scratches, dust particles or rough surfaces, they used conventional lithography to strategically create step edges by patterning SiO<sub>2</sub>/Si substrates with a uniform distribution of square SiO<sub>2</sub> pillars, as shown in Figure 3a. The pillars facilitate a high density of domain nucleation, and the continued growth allows the formation of large-area continuous film. The MoS<sub>2</sub> films, grown on both the pillar surface and the valley space in between (Figure 3b,c), are predominantly single layered (multiple layers typically accumulate at the preferred nucleation sites). The synthesized MoS<sub>2</sub> films can be readily transferred to other substrates (Figure 3d) or directly applied to fabricate devices. FETs based on these MoS<sub>2</sub> films can exhibit average mobility of about  $4.8 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  and a maximum on/off current ratio approaching  $6 \times 10^6$ .

**Figure 3.** Controlled nucleation for CVD growth of large-area MoS<sub>2</sub> growth films on patterned SiO<sub>2</sub>/Si substrates. (a) Optical image of a large-area continuous MoS<sub>2</sub> film on substrates with patterned square SiO<sub>2</sub> pillars; (b) the close-up view indicating monolayer and bilayer MoS<sub>2</sub> films in between pillars and a thicker MoS<sub>2</sub> film on top of pillars; (c) Raman spectra acquired at different regions in (b) confirming the thickness of the sample; (d) centimeter-scale MoS<sub>2</sub> film transferred to a new substrate. Adapted with permission from [21]. Copyright 2013, Nature Publishing Group.

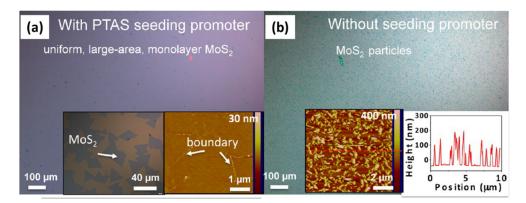

Seeding promoters: In order to improve the uniformity of CVD-grown TMDC films directly on SiO<sub>2</sub>/Si substrates, a simple and effective strategy is to use seeding promoters (Figure 4) [22,26]. In 2012, Lee *et al.* [26] obtained uniform, large-area monolayer MoS<sub>2</sub> by spinning aqueous solutions of

graphene-like molecules, such as reduced graphene oxides (rGO), perylene-3,4,9,10-tetra-carboxylic acid tetra-potassium salt (PTAS) and perylene-3,4,9,10-tetracarboxylic dianhydride (PTCDA), as the seeding promoters onto the SiO<sub>2</sub>/Si substrates prior to growth. Later on, Ling *et al.* [22] identified more aromatic molecules, such as copper phthalocyanine (CuPc) and bathocuproine (BCP), as effective promoters. In particular, in contrast to the previous seeding promoters deposited via aqueous solution [26], the newly-identified seeding promoters can be deposited by thermal evaporation to various substrates, including hydrophobic substrates, to allow direct growth of a variety of hybrid structures (e.g., MoS<sub>2</sub>/Au, MoS<sub>2</sub>/BN and MoS<sub>2</sub>/graphene). Besides, PTAS has also been used as seeding promoters for scalable synthesis of WS<sub>2</sub> [27]. However, possibly because of the presence of grain boundaries, back-gate FETs based on such TMDCs only attain a carrier mobility up to 1.2 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> for MoS<sub>2</sub> and 0.01 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> for WS<sub>2</sub>, in spite of a high on/off ratio above 10<sup>5</sup> [27].

**Figure 4.** The effects of seeding promoter on the CVD growth of MoS<sub>2</sub> films. (a) Optical image of MoS<sub>2</sub> film grown on SiO<sub>2</sub>/Si substrate with perylene-3,4,9,10-tetra-carboxylic acid tetra-potassium salt (PTAS) seeding promoter; (b) optical image of MoS<sub>2</sub> film grown on bare SiO<sub>2</sub>/Si substrate without seeding promoter. The insets show a close-up view through optical or AFM images. Adapted with permission from [22], Copyright 2014, American Chemical Society.

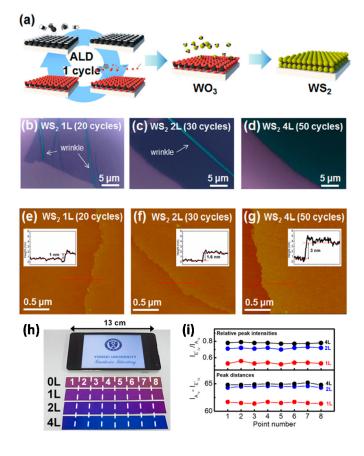

Atomic layer-deposited precursors: In order to obtain layer-controlled wafer-scale WS<sub>2</sub> atomic layers on SiO<sub>2</sub>/Si substrates, Song *et al.* [28] introduced an innovative synthesis technique through sulfurizing the WO<sub>3</sub> film prepared by atomic layer deposition (ALD). The precursor WO<sub>3</sub> film is first deposited on SiO<sub>2</sub>/Si substrates by the ALD process and then sulfurized through the VDP technique (Figure 5a). Benefiting from the excellent controllability of the ALD process, the synthesis of WS<sub>2</sub> films exhibits systematic layer controllability, good reproducibility, wafer-level thickness uniformity and high conformity. In particular, the number of final WS<sub>2</sub> layers can be well controlled by controlling the number of the ALD cycles during WO<sub>3</sub> deposition. With 20, 30 and 50 ALD cycles, mono-, bi- and tetra-layer WS<sub>2</sub> are obtained, respectively (Figure 5b–g). Wafer-scale (2 cm × 13 cm) thickness uniformity has been demonstrated for all of the mono-, bi- and tetra-layer WS<sub>2</sub> films (Figure 5h,i). Top-gate FETs based on the WS<sub>2</sub> films exhibit high mobility of about 3.9 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> with an on/off current ratio around 10<sup>3</sup>.

**Figure 5.** Atomic layer deposition (ALD)-based layer-controlled CVD growth of WS<sub>2</sub> films with precursors. (a) Schematic of the synthesis procedure; (b–d) optical microscope images and (e–g) AFM images and height profile (insets) of the mono-, bi- and tetra-layer WS<sub>2</sub> films transferred onto SiO<sub>2</sub> substrates, respectively; (h) wafer-sale (about 13 cm, comparable to the size of a cellular phone display screen) mono-, bi- and tetra-layer WS<sub>2</sub> films on SiO<sub>2</sub> substrates; (i) Raman peak intensity ratio (top) and peak distance (bottom) of the  $E_{2g}^1$  and  $A_{1g}$  bands for the WS<sub>2</sub> films at eight different measurement positions in (h) indicating the wafer-scale uniformity. Adapted with permission from [28]. Copyright 2013, American Chemical Society.

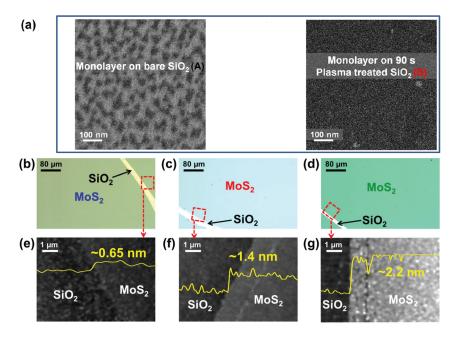

Oxygen plasma treatment: Besides the layer-controlled synthesis by ALD-deposited precursors, Jeon *et al.* [29] have recently developed another facile layer-controlled CVD growth technique for wafer-scale MoS<sub>2</sub> film on silicon substrates. Prior to the growth, the SiO<sub>2</sub>/Si substrates are treated with oxygen plasma. With the low pressure CVD process, uniform MoS<sub>2</sub> film can be obtained in a large area (Figure 6a). In contrast, on untreated SiO<sub>2</sub>/Si substrates, only small-scale (<100 nm) triangular MoS<sub>2</sub> nanoparticles are synthesized. Besides, by changing the duration of the oxygen plasma treatments, different MoS<sub>2</sub> layers can be adjusted in a controllable manner. With treatment durations of 90 s, 120 s and 300 s, mono-, bi- and tri-layer MoS<sub>2</sub> films have been obtained, respectively (Figure 6b–g). All back-gate FETs based on these MoS<sub>2</sub> show a high on/off current ratio between 10<sup>5</sup> and 10<sup>6</sup>. The carrier mobility increases with the layer number, which is 3.6 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, 8.2 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and 15.6 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> for the mono-, bi- and tri-layer MoS<sub>2</sub> transistors, respectively. However, one may notice that the residual oxygen caused by the plasma treatment may impact the quality of the grown MoS<sub>2</sub> [30].

Further cleaning of the plasma-treated SiO<sub>2</sub>/Si wafers (e.g., through purging with Ar at high temperature [29]) might be necessary to obtain high crystallinity.

**Figure 6.** Layer-controlled CVD growth of MoS<sub>2</sub> film on plasma-treated SiO<sub>2</sub> substrates. (a) Scan electron microscope (SEM) images of the grown MoS<sub>2</sub> film on bare (left) and plasma-treated (right) SiO<sub>2</sub> substrates; (b–d) optical microscope images and (e–g) AFM images for the uniform mono-, bi- and tri-layer MoS<sub>2</sub> films, respectively. Adapted with permission from [29]. Copyright 2015, The Royal Society of Chemistry.

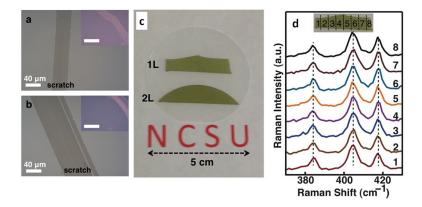

Self-limiting CVD: Yu et al. [31] developed a simple self-limiting CVD process to grow centimeter-scale MoS<sub>2</sub> films with precisely-controlled layer number ranging from 1–4. Highly uniform MoS<sub>2</sub> films (Figure 7) are synthesized on various substrates, including silicon oxide, sapphire and graphite. The MoS<sub>2</sub> films are grown at a high temperature (>800 °C) with MoCl<sub>5</sub> and sulfur as the precursors. At high temperature, precursors react to produce MoS<sub>2</sub> species, which then precipitate onto the substrates to form MoS<sub>2</sub> films. The layer number of the MoS<sub>2</sub> films is precisely controlled by the amount of MoCl<sub>5</sub> used in the source or the total pressure during the growth process. The greater the amount of MoCl<sub>5</sub> or the higher the total pressure used, the larger the layer number of MoS<sub>2</sub> films obtained. The obtained large-area, highly-uniform MoS<sub>2</sub> thin films suggest that the growth is a self-limiting process, i.e., the growth automatically stops once the formation of each individual layer finishes. The self-limiting mechanism may lie in a thermodynamic balance between the partial pressure of gaseous MoS<sub>2</sub> species  $(P_1)$  and the vapor pressure of MoS<sub>2</sub> thin films on the substrate  $(P_2)$ .  $P_2$  could increase with the layer number. The initial force of  $P_1 > P_2$  drives the formation of monolayer MoS<sub>2</sub>. When the growth of the monolayer finishes,  $P_2$  increases, and the driving force  $P_1 > P_2$  may vanish, so that the growth ceases. To grow more layers, higher  $P_1$  should be introduced. Therefore, the layer number can be well controlled by the precursor amount and environmental pressure. However, for thicker MoS<sub>2</sub> films, precise control becomes more difficult. Back-gate FETs based on monolayer MoS<sub>2</sub> films exhibit carrier mobility ranging from 0.003-0.03 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>.

**Figure 7.** Controlled synthesis of monolayer and bilayer MoS<sub>2</sub> films by self-limiting CVD. Optical microscope images of highly uniform (**a**) monolayer and (**b**) bilayer MoS<sub>2</sub> films (scale bars in insets: 80 μm); (**c**) photograph of as-grown large-area monolayer and bilayer MoS<sub>2</sub> films; (**d**) Raman spectra acquired at different locations indicating the homogeneity. Adapted with permission from [31]. Copyright 2013, Nature Publishing Group.

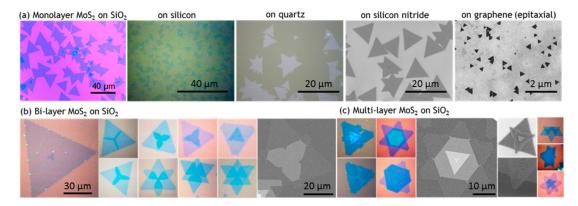

Immediate-state precursor: Usually, CVD synthesis for MoS<sub>2</sub> is based on MoO<sub>3</sub> as the initial metal precursor. During growth, however, the conversion from MoO<sub>3</sub> to MoS<sub>2</sub> involves one intermediate step. MoO<sub>3</sub> is first partially reduced by the sulfur to a volatile state MoO<sub>3-x</sub>, and then, MoO<sub>3-x</sub> is further reduced to MoS<sub>2</sub>. The incomplete reaction (partial reduction) may produce an uncontrollable intermediate phase, which provides extra binding sites to chemisorb oxygen. The absorbed oxygen can generate defects/vacancies in the final MoS<sub>2</sub> flakes and significantly degrade their electrical performance. To diminish the impacts arising from the intermediate chemistry, Bilgin *et al.* [30] developed a CVD process with MoO<sub>2</sub> powders as the metal precursor and directly sulfurized MoO<sub>2</sub> in the vapor phase. With this technique, monolayer, as well as few-layer MoS<sub>2</sub> with an edge-size (Figure 8) ranging from 10–50 µm have been grown in various substrates, including amorphous SiO<sub>2</sub>, crystalline Si wafer, transparent quartz and silicon nitride, as well as conductive graphene. Through transferring the as-grown monolayer MoS<sub>2</sub> onto SiO<sub>2</sub>/Si substrates and building up back-gate device structures, the obtained FETs exhibit excellent performance of high mobility of about 35 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, and a large on/off current ratio about 10<sup>8</sup>.

#### 2.1.2. Gas-Precursor VPD

In addition to the solid-precursor VPD, conventionally with sulfur (or selenium) powder as the precursor, recent studies have also employed gas state precursors to improve the controllability during the course of VPD growth.

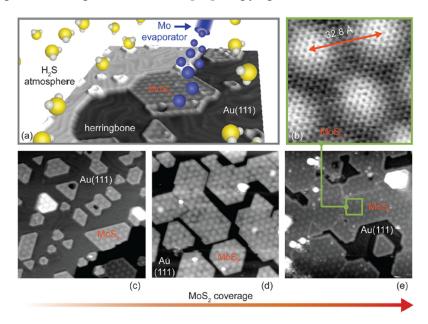

Cycle-based epitaxy on gold: Large-area epitaxial monolayer MoS<sub>2</sub> films have been recently grown on a Au(111) surface [32] under ultrahigh vacuum with H<sub>2</sub>S gas and e-beam evaporated Mo as the precursors (Figure 9a). The synthesis is based on growth cycles, each of which consists of two sequent steps, Mo evaporation and sulfurization by H<sub>2</sub>S gases. Upon the finishing of one growth cycle, the H<sub>2</sub>S gases are pumped out, and the chamber is prepared for a second growth cycle. The first growth cycle is to nucleate MoS<sub>2</sub> nano-islands (Figure 9c), and the following cycles gradually increase the island size (Figure 9d,e). The growth cycles are repeated until a continuous film forms with coverage approaching

unity. Without such a cycle-based synthetic process, it is challenging to obtain high-coverage uniform MoS<sub>2</sub>, since a single long Mo deposition in a H<sub>2</sub>S atmosphere only produces low quality sub-monolayer films.

**Figure 8.** Optical (colored) and SEM (grey) images of (a) monolayer, (b) bilayer and (c) multi-layer MoS<sub>2</sub> films on various substrates grown by CVD with MoO<sub>2</sub> as the metal precursor. Reprinted with permission from [30]. Copyright 2015, American Chemical Society.

**Figure 9.** (a) Schematic of cycle-based epitaxy of MoS<sub>2</sub> on gold; (b) high resolution scan tunneling microscope (STM) image of the moiré lattice of MoS<sub>2</sub>; (c–e) STM images acquired at different growth times. Reprinted with permission from [32]. Copyright 2015, American Chemical Society.

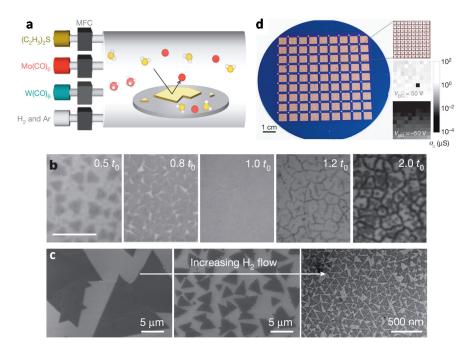

All-gas precursor CVD: Kang *et al.* [23] have developed a metal-organic chemical vapor deposition (MOCVD) technique to grow monolayer MoS<sub>2</sub> and WS<sub>2</sub> films with safer-scale homogeneity. Remarkably, only gas-phase precursors (Figure 10a) are used in the technique, including Mo(CO)<sub>6</sub> or W(CO)<sub>6</sub> as the metal precursors, (C<sub>2</sub>H<sub>5</sub>)S as the sulfide precursors and H<sub>2</sub> to remove carbonaceous species generated during the MOCVD growth. All of the gases are diluted in the carrier gas, argon, so that their concentration can be precisely controlled throughout the growth period by regulating the corresponding partial pressure. In this way, the MoS<sub>2</sub> film is grown layer by layer, which is ideal for uniform layer control over a large scale. Figure 10b reveals the controllable growth process at different

times: initial nucleation on the SiO<sub>2</sub> surface ( $t = 0.5t_0$ ), monolayer growth (0.8 $t_0$ ), maximum monolayer coverage ( $t_0$ ), secondary nucleation mainly at grain boundaries (1.2 $t_0$ ) and bilayer growth (2 $t_0$ ). In addition, the average grain size and inter-grain connection can be well controlled by the concentrations of H<sub>2</sub>, (C<sub>2</sub>H<sub>5</sub>)<sub>2</sub>S and residual water (Figure 10c). The wafer-scale growth of a high-quality monolayer MoS<sub>2</sub> film allows mass production of 8100 FETs (Figure 10d) on a four-inch SiO<sub>2</sub>/Si wafer with a yield as high as 99% and excellent electrical performance of the on/off current ratio of ~10<sup>6</sup> and mobility of ~29 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>. Similar devices based on a CVD-grown WS<sub>2</sub> monolayer also exhibit a high on/off current ratio of ~10<sup>6</sup> and mobility of ~18 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>.

**Figure 10.** All-gas precursor metal-organic chemical vapor deposition (MOCVD) growth of continuous large-area MoS<sub>2</sub> film and device fabrication. (a) Diagram of the MOCVD setup; (b) optical images of the grown MoS<sub>2</sub> films at different growth times, where  $t_0$  is the optimal growth time for full monolayer coverage (scale bar: 10 µm); (c) the effects on the H<sub>2</sub> flow rate on the grown MoS<sub>2</sub> grains; (d) mass production of 8100 MoS<sub>2</sub> FETs on a four-inch SiO<sub>2</sub>/Si wafer. Adapted with permission from [23]. Copyright 2015, Nature Publishing Group.

#### 2.2. Thermal Decomposition

In addition to the VPD techniques, other techniques have also been developed for scalable synthesis of 2D TMDC materials.

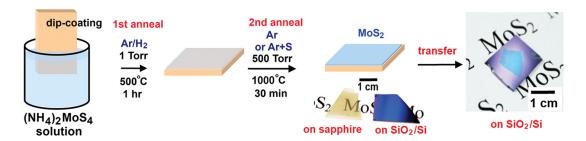

In 2011, Liu *et al.* [33] developed a thermal decomposition technique to produce large-area MoS<sub>2</sub> thin layers on insulating substrates (Figure 11). First, a thin and uniform film of the precursor, ammonium thiomolybdates, (NH<sub>4</sub>)<sub>2</sub>MoS<sub>4</sub>, is coated onto insulating substrates (sapphire or SiO<sub>2</sub>/Si wafer) through dip coating. Then, the precursor is annealed and converts to MoS<sub>2</sub>. The annealing process comprises a first low-pressure (1 Torr) annealing at 500 °C in the presence of H<sub>2</sub> for the decomposition of (NH<sub>4</sub>)<sub>2</sub>MoS<sub>4</sub> to MoS<sub>2</sub> and a second high-pressure (500 Torr) annealing at 1000 °C in an atmosphere

of Ar (or a mixture of Ar and sulfur) to improve crystallinity and/or increase the grain domain size. Typically, uniform and continuous bi- or tri-layer  $MoS_2$  films are obtained throughout the substrates (Figure 11). Bottom-gate FETs based on the synthesized  $MoS_2$  annealed under the atmosphere of Ar and S exhibit a current ratio up to  $1.6 \times 10^5$  and a mobility up to  $4.7 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ .

**Figure 11.** Schematic of the thermal decomposition process for the growth of MoS<sub>2</sub> films on insulating substrates. Adapted with permission from [33]. Copyright 2012, American Chemical Society.

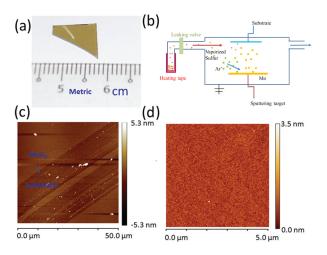

## 2.3. Magnetron Sputtering

Tao *et al.* [34] recently developed a one-step magnetron sputtering technique to synthesize wafer-scale MoS<sub>2</sub> atomic layers on various substrates. As illustrated in Figure 12b, the growth is based on the reaction between vaporized S and sputtered Mo. Sulfur is first vaporized and then transported to the chamber, where the metal target is sputtered in an Ar atmosphere by a low power. The sputtered Mo is more reactive than Mo or MoO<sub>3</sub> in CVD processes and can easily react with the vaporized S. After the reaction, the product is deposited onto the hot substrate to form MoS<sub>2</sub> layers. Because of the low sputtering power, the growth rate is very low. Therefore, mono- or few-layer MoS<sub>2</sub> can be obtained in a controllable manner by adjusting the sputtering power or deposition time. Since magnetron sputtering is compatible with large-scale production, highly-homogeneous MoS<sub>2</sub> flakes with dimensions up to centimeter scale (Figure 12a) are obtained with a controllable layer number of 1, 2, 3 and more. The back-gate FETs based on the grown MoS<sub>2</sub> exhibit a p-type behavior with an on/off current ratio of about 10<sup>3</sup> and an average mobility of about 7 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>.

#### 2.4. Molecular Beam Epitaxy

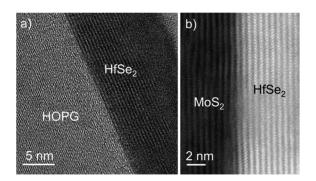

Recently, Yue *et al.* [35] developed a molecular beam epitaxy (MBE) to grow one 2D TMDC (HfSe<sub>2</sub>) on another 2D material (highly-ordered pyrolytic graphite (HOPG) or MoS<sub>2</sub>). Although MBE was introduced for hetero-epitaxial growth of TMDC (e.g., NbSe<sub>2</sub>) three decades ago, few studies have demonstrated the MBE growth of 2D HfSe<sub>2</sub> on another 2D material to fabricate an all-2D heterostructure. Hf-based TMDCs have a small band gap, a large work function and reasonable mobility and, hence, are promising for a variety of applications in nanoelectronics and optoelectronics. In Yue's processing, the HfSe<sub>2</sub> films are grown on mechanically-exfoliated HOPG and MoS<sub>2</sub> through a VG-Semicon V80H molecular beam epitaxy system, where the growth chamber is equipped with a vertical e-beam evaporator to allow the growth of high melting-point metals (Hf, Ti, Mo, W, *etc.*) in addition to effusion cell evaporation of the chalcogen. Prior to growth, the substrates are cleaned by

heating for 2 h in the growth chamber, and the Hf and S sources are cleaned by outgassing. During the growth, the Se and Hf shutters were opened and closed simultaneously, and the Se:Hf flux was maintained at a ratio of 5:1. As shown in Figure 13, the interface is atomically sharp, and there are no detectable misfit dislocations or strains between the MBE-grown HfSe<sub>2</sub> and the HOPG or MoS<sub>2</sub> underneath, in spite of the large lattice mismatch (41% and 17%, respectively). The grains are typically larger than 100 nm  $\times$  100 nm, and the layer number depends on the growth time. The grown HfSe<sub>2</sub> is slightly n-type with a band gap of about 1.1 eV.

**Figure 12.** Large-area uniform MoS<sub>2</sub> film grown on sapphire by magnetron sputtering. (a) Photograph of a centimeter-scale film; (b) schematic of the magnetron sputtering growth process; (c) AFM image of as-grown MoS<sub>2</sub> film showing a clear film edge; (d) a close-up view of the AFM image showing good uniformity. Adapted with permission from [34]. Copyright 2015, The Royal Society of Chemistry.

**Figure 13.** Transmission electron microscope (TEM) images of epitaxial HfSe<sub>2</sub> on (a) highly-ordered pyrolytic graphite (HOPG) and (b) MoS<sub>2</sub> with a sharp interface and layered crystallinity. Reprinted with permission from [35]. Copyright 2015, American Chemical Society.

# 3. Advanced Engineering for Materials, Heterostructures and Devices

As the scalable synthesis of 2D TMDC becomes mature, more and more techniques have been developed to allow advanced engineering in TMDC-based electronics at different levels, from synthesis

of the TDMC alloys (material level), to fabrication of various 2D heterostructures, to controllable and batch production of electronic devices at the wafer scale.

## 3.1. TMDC Alloys

Both theoretical calculation and experiments have demonstrated that the band gap of 2D TMDC alloys can be modulated in a wide spectrum range by changing the composition [36]. This is a desired property for many applications in electronic and optoelectronics and has stimulated great efforts in controllable fabrication of various 2D TMDC alloys. So far, two types of alloys have been synthesized through scalable VDP techniques. One is a mixture of chalcogens, e.g.,  $MoS_{2(1-x)}Se_{2x}$  alloys, and the other is a mixture of metals, e.g.,  $Mo_{1-x}W_xS_2$  alloys.

## 3.1.1. $MoS_{2(1-x)}Se_{2x}$ Alloys

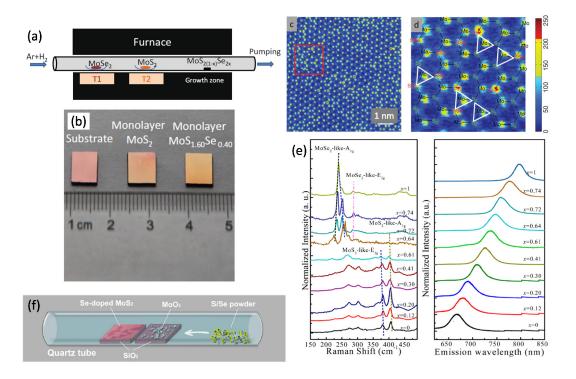

Two CVD processes have been developed for scalable synthesis of  $MoS_{2(1-x)}Se_{2x}$  alloys. One [37,38] uses MoSe<sub>2</sub> and MoS<sub>2</sub> powders as the precursors, which are placed separately, as illustrated in Figure 14a. The precursors are directly vaporized at a high temperature (940–975 °C), while the SiO<sub>2</sub>/Si substrate is put in a relatively low temperature (600-700 °C) region. In order to optimize the supersaturation for the nucleation process, a moderately high temperature gradient of about 50 °C/cm in the substrate (deposition) region is applied [37,38]. Too low of a temperature gradient (<30 °C/cm) may suffer from insufficient supersaturation and nucleation for the alloy growth [37], whereas too high of a temperature gradient (>80 °C/cm) may cause surplus nucleation, which greatly reduces the domain size of the monolayer alloy [38] or even changes the morphology to a fiber-like structure [37]. By finely adjusting the evaporation temperature, the temperature gradient and the H<sub>2</sub> flow rate in the carrier gas, high-quality centimeter-scale  $MoS_{2(1-x)}Se_{2x}$  monolayer alloy can grow on the substrate (Figure 14b). By fixing the evaporation temperature of MoS<sub>2</sub> at 940 °C and increasing the evaporation temperature of MoSe<sub>2</sub> from 940–975 °C, the composition in the MoS<sub>2(1-x)</sub>Se<sub>2x</sub> alloy can be finely controlled with x ranging from 0–0.4. However, at an even higher evaporation temperature (>975 °C), MoSe<sub>2</sub> tends to decompose, and it becomes hard to further increase x in the alloy. Nevertheless, if extra Se vapor is introduced into the upstream of the furnace, more Se-rich alloy with 0.4 < x < 1 can be obtained [38]. Atomic-resolution high-angle annular dark filed (HAADF) scanning transmission electron microscopy (STEM) imaging (Figure 14c,d) shows the distribution of S and Se atoms in the monolayer alloys. Raman and photoluminescence spectra (Figure 14e) also indicate the shift of characteristic peaks induced by composition change.

The other process [36,39] uses mixed S and Se fine powders as the chalcogen source and MoO<sub>3</sub> as the metal source (Figure 14f). By changing the ratio of the S and Se powders in the source, the fraction in the alloy can be well controlled with x ranging from 0–0.75. FETs based on the synthesized MoS<sub>2(1-x)</sub>Se<sub>2x</sub> alloy exhibit a high on/off current ratio of about 10<sup>6</sup> and a mobility up to 15.3 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> [39].

**Figure 14.** Two CVD processes for the synthesis of MoS<sub>2(1-x)</sub>Se<sub>2x</sub> alloys. (a) Schematic of CVD with separate MoSe<sub>2</sub> and MoS<sub>2</sub> precursors; (b) photograph of bare SiO<sub>2</sub>/Si substrate and centimeter-scale MoS<sub>2</sub> and MoS<sub>1.60</sub>Se<sub>0.4</sub> monolayer films on substrates; (**c**,**d**) high-angle annular dark filed (HAADF)-STEM image of MoS<sub>1.60</sub>Se<sub>0.4</sub> monolayer film in false color; (e) Raman (left) and photo-luminescence (right) spectra of MoS<sub>2(1-x)</sub>Se<sub>2x</sub> alloys with *x* ranging from 0 to 1; (f) schematic of CVD with separate mixtures of S and Se powders as precursors. (a–d) Adapted with permission from [37]. Copyright 2014, WILEY-VCH Verlag GmbH. (e) Adapted with permission from [38]. Copyright 2015, American Chemical Society. (f) Adapted with permission from [39]. Copyright 2014, American Chemical Society.

# 3.1.2. $Mo_{1-x}W_xS_2$ Alloys

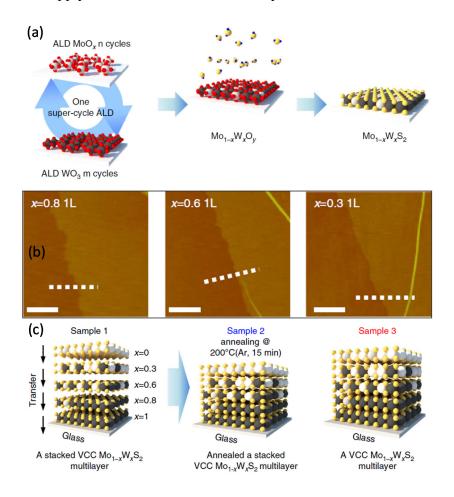

Song *et al.* [40] recently reported a synthesis method of  $Mo_{1-x}W_xS_2$  alloys by sulfurization of super-cycle ALD  $Mo_{1-x}W_xO_y$  alloy thin films. First, 10 cycles of WO<sub>3</sub> were pre-deposited through ALD to address the nucleation delay issues of ALD-grown WO<sub>3</sub>. Then, one super-cycle ALD process (Figure 15a) comprising *n* cycles of ALD  $MoO_x$  and *m* cycles of ALD-grown WO<sub>3</sub> is performed to grow  $Mo_{1-x}W_xO_y$  alloy thin films, followed by sulfurization to obtain 2D  $Mo_{1-x}W_xS_2$  alloys. By adjusting the n/m ratio, the fraction of W in the final alloys, *x*, can be well controlled. Typically, one super-cycle gives rise to uniform monolayer  $Mo_{1-x}W_xS_2$  alloys with a thickness of ~1 nm (Figure 15b), and two and three super-cycles produce bi- or tri-layer 2D alloys, respectively. In other words, the alloy composition and layer number can be well controlled during the ALD-based synthesis process. Consequently, the band gaps of the alloys can also be precisely controlled. Furthermore, vertically-composition-controlled (VCC)  $Mo_{1-x}W_xS_2$  multilayer alloys (Figure 15c) have also been synthesized by using a sequential super-cycle ALD process, which consists of five continuous super-cycles with different n/m ratios for each super-cycle. The VCC  $Mo_{1-x}W_xS_2$  multilayer alloys exhibit a broadband light absorption property

and are very promising for efficient photodetector applications. In particular, the ALD-based super-cycle process is anticipated to apply also to other 2D TMDC alloys than  $Mo_{1-x}W_xS_2$ .

**Figure 15.** ALD-based synthesis of  $Mo_{1-x}W_xO_y$  alloy. (a) Schematic of the synthesis procedure with the super-cycle of the ALD processes; (b) AFM images of the alloys with different x (scale bars: 500 nm); (c) schematics of three vertically-composition-controlled (VCC)  $Mo_{1-x}W_xO_y$  multilayers. Adapted with permission from [40]. Copyright 2015, Nature Publishing Group.

Meanwhile, Zhang *et al.* [36] also developed a CVD process to synthesize 2D  $Mo_{1-x}W_xS_2$  alloys. They used a mixture of WO<sub>3</sub> and MoO<sub>3</sub> powders as the metal precursor and sulfur powder as the chalcogen precursor. The band gaps of the grown  $Mo_{1-x}W_xS_2$  alloys are tuned through adjusting the Mo/W ratio in the precursors.

#### 3.2. 2D Heterostructures

One of the greatest interests in recent research is to reassemble isolated 2D materials into heterostructures in a layer-by-layer form and in a controllable sequence, just like building with atomic-scale Lego blocks [13]. The assembled 2D heterostructures, sometimes called van der Waals heterostructures, often reveal unusual properties and new phenomena and are anticipated to play an important role in future electronics and optoelectronics [8]. The van der Waals heterostructures can be readily fabricated by stacking different 2D materials through mechanical transfer techniques. However, the techniques suffer from

uncontrolled stacking orientation, contaminated interfaces and significant challenges for massive production. As a matter of fact, researchers have also begun to develop scalable synthesis techniques for various 2D heterostructures, including semiconductor/conductor (TMDC/graphene), semiconductor/insulator (TMDC/BN) and semiconductor/semiconductor (TMDC/ TMDC) 2D structures. Actually some techniques introduced above are already able to synthesize 2D TMDC heterostructures, such as the MBE-grown HfSe<sub>2</sub>/HPOG and HfSe<sub>2</sub>/MoS<sub>2</sub> heterostructures (Section 2.4, Figure 13, [35]) and the ALD-based CVD-grown VCC  $Mo_{1-x}W_xO_y$  multilayers (Section 3.1.2, Figure 15c, [40]). Below, we briefly introduce other techniques for the 2D TMDC heterostructures.

## 3.2.1. TMDC/Graphene Heterostructures

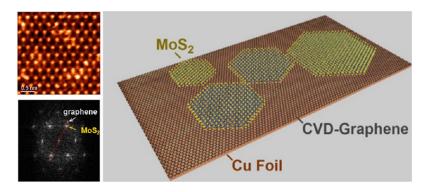

In 2011, Shi *et al.* [41] introduced a method to synthesize MoS<sub>2</sub>/graphene heterostructures (Figure 16). First, monolayer graphene is synthesized on copper foil through a CVD process. Then, the graphene/copper substrate is placed in a quartz tube chamber, and the (NH<sub>4</sub>)<sub>2</sub>MoS<sub>4</sub>/DMF dispersion is carried by Ar gas to deposit onto the graphene surface as the MoS<sub>2</sub> precursor. Finally, after DMF evaporates, the samples are annealed at 400 °C in Ar/H<sub>2</sub> atmosphere to decompose (NH<sub>4</sub>)<sub>2</sub>MoS<sub>4</sub> and obtain the MoS<sub>2</sub>/graphene heterostructures.

**Figure 16.** TEM analysis (left) and schematic (right) of the MoS<sub>2</sub>/graphene heterostructure. Reprinted with permission from [41]. Copyright 2012, American Chemical Society.

Miwa et al. [42] recently demonstrated direct van der Waals epitaxy of MoS<sub>2</sub>/graphene heterostructures on silicon carbide (SiC) substrates. The graphene/SiC substrate is first fabricated through direct current annealing of SiC under a mild flux of silicon atoms. Then, MoS<sub>2</sub> is synthesized in a similar way to the cycle-based MoS<sub>2</sub> growth on gold (Figure 9, [32]). The buffer layers coexisting with graphene on the substrates facilitate the MoS<sub>2</sub> growth. Due to the weak van der Waals interaction between graphene and MoS<sub>2</sub>, the electronic structure of free-standing monolayer MoS<sub>2</sub> is retained in the heterostructure as confirmed by angle-resolved photoemission spectroscopy measurements.

## 3.2.2. TMDC/BN Heterostructures

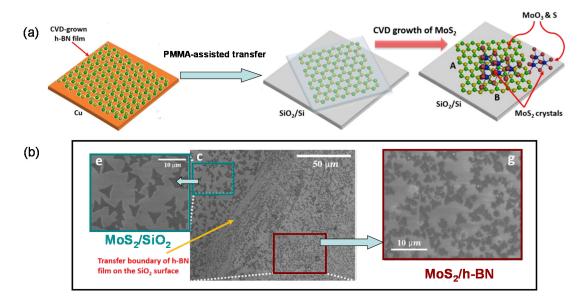

Wang *et al.* [43] recently reported an all-CVD process to fabricate high-quality monolayer MoS<sub>2</sub>/BN heterostructures with centimeter-scale MoS<sub>2</sub> domains. As illustrated in Figure 17a, first, few-layer hexagonal boron nitride (h-BN) is grown on copper substrates by CVD with an ammonia borane precursor. To suppress decomposition during MoS<sub>2</sub> growth, few-layer h-BN films (2–4 layers) are

preferred to monolayer h-BN. Then, the h-BN film is transferred to SiO<sub>2</sub>/Si wafer. Finally, MoS<sub>2</sub> is grown on top of h-BN films by CVD with MoO<sub>3</sub> and S powders as the precursors. Possibly because of the relatively strong interaction between MoS<sub>2</sub> and h-BN, the directly-grown MoS<sub>2</sub> on h-BN films exhibits smaller lattice strain, a lower doping level, cleaner and sharper interfaces and better interlayer contact, as compared with those directly grown on SiO<sub>2</sub>/Si wafer (Figure 17b).

**Figure 17.** (a) Schematic of one fabrication process of the MoS<sub>2</sub>/hexagonal boron nitride (h-BN) heterostructure; (b) SEM images of MoS<sub>2</sub> grown on the edge of the transferred h-BN indicating the difference in morphology of MoS<sub>2</sub> grown on SiO<sub>2</sub> and h-BN. Adapted with permission from [43]. Copyright 2015, American Chemical Society.

## 3.2.3. TMDC/TMDC Heterostructures

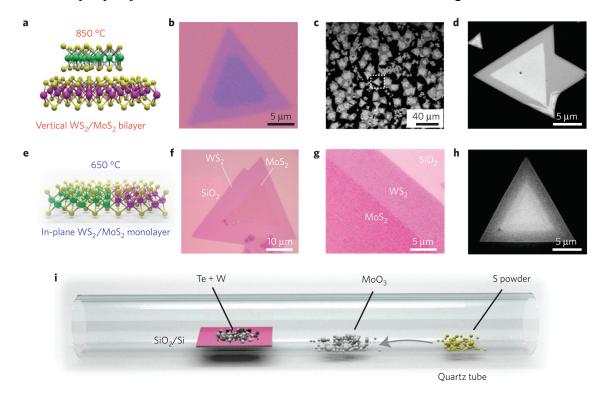

Gong et al. [44] report a scalable single-step VPD process to synthesize highly-crystalline MoS<sub>2</sub>/WS<sub>2</sub> heterostructures with both a vertically-stacked bilayer structure (Figure 18a-d) and an in-plane inter-connected structure (Figure 18e-h). As shown in Figure 18i, in front of the SiO<sub>2</sub>/Si substrate, MoO<sub>3</sub> powder is placed as the metal precursor for the growth of MoS<sub>2</sub>. On top of the substrate, a mixture of tungsten (W) and tellurium (Te) powders is placed for the growth of WS2. Here, the Te powder serves as the catalyst to accelerate the melting of W powder. Argon is used as the carrier gas to transport the S vapor from the upstream. Since MoS<sub>2</sub> and WS<sub>2</sub> have different nucleation and growth rates, this leads to sequential growth of the materials and, thereby, forms heterostructures, rather than growing the  $Mo_{1-x}W_xS_2$  alloy. The structure of the final product is determined by the reaction temperature. High-temperature (~850 °C) growth produces mostly vertically-stacked bilayers, where WS<sub>2</sub> is grown epitaxially on top of monolayer MoS<sub>2</sub>, while low-temperature (~650 °C) growth generates mostly in-plane lateral heterojunctions where MoS<sub>2</sub> and WS<sub>2</sub> locate within a single hexagonal monolayer lattice with seamless and atomically-sharp interfaces. Because of the clean interface, the vertically-stacked bilayers can retain the performance of individual monolayers and meanwhile generate an additional direct band gap via interlayer coupling. Remarkably, back-gate FETs based on the vertical MoS<sub>2</sub>/WS<sub>2</sub> stacks exhibit an on/off current ratio over 10<sup>6</sup> at a high mobility ranging from 15–34 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>. The

in-plane MoS<sub>2</sub>/WS<sub>2</sub> heterojunctions greatly enhance the localized photoluminescence and can serve as intrinsic monolayer p—n junctions with no need for external electrical tuning.

**Figure 18.** CVD growth of vertically-stacked and in-plane WS<sub>2</sub>/MoS<sub>2</sub> heterostructures. (a–d) Schematic, optical and SEM images of vertically-stacked heterostructures; (e–h) schematic, optical and SEM images of in-plane heterostructures; (i) schematic of the synthesis process. Reprinted with permission from [44]. Copyright 2014, Nature Publishing Group.

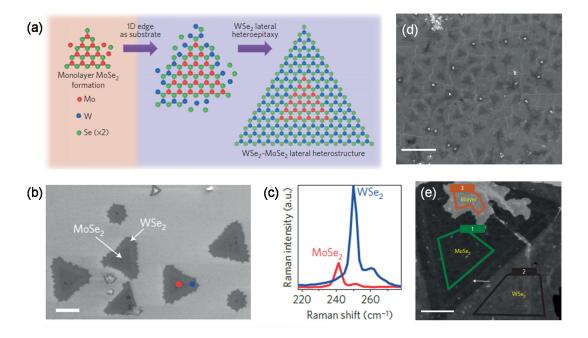

Huang *et al.* [45] also demonstrate a technique based on direct physical vapor deposition (PVD) to synthesize high-quality monolayer MoSe<sub>2</sub>/WSe<sub>2</sub> lateral heterojunctions. The precursor, a mixture of WSe<sub>2</sub> and MoSe<sub>2</sub> powders, is vaporized at high temperature ( $\sim$ 950 °C) and carried by hydrogen gas to the downstream SiO<sub>2</sub>/Si substrate and, finally, crystallizes on the substrate to form the lateral heterojunctions (Figure 19). The growth mechanism may rely on the different evaporation rates of the two materials. In the beginning, MoSe<sub>2</sub> evaporates quickly, and pure monolayer MoSe<sub>2</sub> crystals predominate in the substrate. After some time, the MoSe<sub>2</sub> source has considerable surface depletion of Se, so that its evaporation slows down. Meanwhile, the evaporation of WSe<sub>2</sub> increases, leading to predominant growth of WSe<sub>2</sub> on the substrate. The different evaporation rates prevent the formation of Mo<sub>1-x</sub>W<sub>x</sub>Se<sub>2</sub> alloy. Due to their great similarity, WSe<sub>2</sub> can epitaxially grow on the MoSe<sub>2</sub> crystal edges to form the lateral heterojunctions. The monolayer heterojunctions retain an undistorted honeycomb lattice and exhibit enhanced photoluminescence.

**Figure 19.** PVD growth of in-plane WSe<sub>2</sub>/MoSe<sub>2</sub> heterostructures. (**a**) Schematic of the synthesis mechanism; (**b**) SEM image of the grown in-plane heterostructures (scale bar: 10 μm); (**c**) Raman spectra acquired at different regions in the heterostructure as indicated in (**b**); (**d**) SEM image of a film transfer film to a SiO<sub>2</sub> substrate (scale bar: 5 μm); (**e**) HAADF-STEM image of a triangle (scale bar: 100 nm). Adapted with permission from [45]. Copyright 2014, Nature Publishing Group.

## 3.3. Wafer-Scale Device Engineering

Despite the great progress in scalable and controllable synthesis of 2D TMDCs, with respect to device performance, however, most studies just explore a few devices in selected areas [23]. Large-scale device engineering still remains challenging. Fortunately, the increasing maturity of the VDP techniques has enabled some attempts in advanced engineering of 2D TMDC-based devices at the wafer scale.

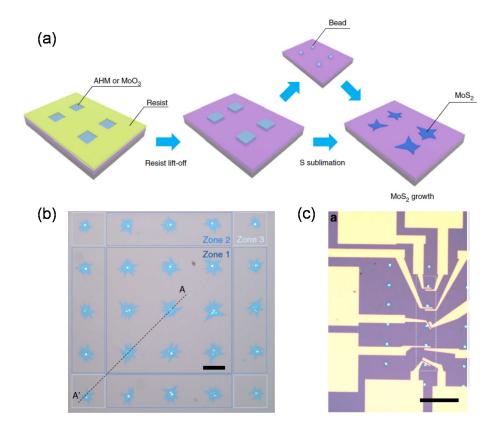

## 3.3.1. Direct Growth of TMDC at Controlled Locations

Han *et al.* [46] use patterned Mo precursors to grow MoS<sub>2</sub> flakes at predefined locations at the resolution of micrometer scale. As illustrated in Figure 20a, first, lithography is employed to define the area for MoS<sub>2</sub> growth with photoresist. Then, the precursor, MoO<sub>3</sub> or ammonium heptamolybdate (AHM), is deposited into the area through thermal evaporation or spin coating. After the photoresist is stripped, a special aggregation step and chemical treatment by promoters, such as PTAS and PTCDA, are conducted to form spherical beads of precursors and to improve the uniformity of the following MoS<sub>2</sub> growth. Finally, the precursor is sulfurized by vaporized S in a nitrogen atmosphere. The grown MoS<sub>2</sub> shows high crystallinity and excellent optical properties. Back-gate FETs exhibit high carrier mobility between 8.2 and 14.4 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> with the on/off current ratio around 10<sup>6</sup>. In particular, the precise control over the location of discrete MoS<sub>2</sub> flakes (Figure 20b) facilitates direct integration and massive device production (Figure 20c) through conventional lithography without the need for an etching step.

**Figure 20.** Selective CVD growth of MoS<sub>2</sub> using patterned precursors. (a) Schematic of growth process; (b) an array of CVD-grown MoS<sub>2</sub> monolayer flakes (scale bar: 50 μm); (c) batch production of FETs based on MoS<sub>2</sub> array (scale bar: 100 μm). Adapted with permission from [46]. Copyright 2015, Nature Publishing Group.

## 3.3.2. Multi-Level Stacking of TMDC Devices

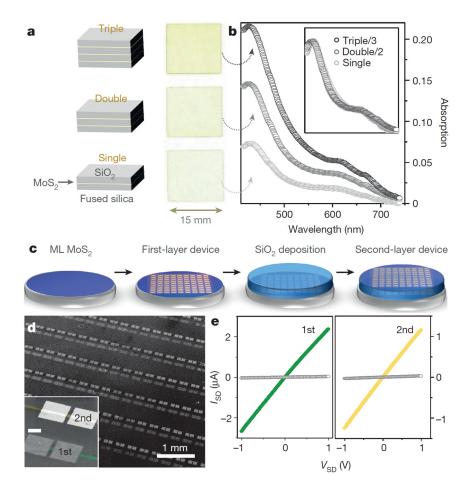

As introduced in Section 2.1.2, the all-gas precursor MOCVD process developed by Kang *et al.* [23] enables wafer-scale growth of high-quality monolayer MoS<sub>2</sub> film directly on SiO<sub>2</sub> substrates. This opens opportunities to fabricate multi-level stacked monolayer MoS<sub>2</sub> films (Figure 21a,b) and devices (Figure 21c–e). As illustrated in Figure 21c, the multi-level stacked structure can be fabricated in the following sequence: growing the first MoS<sub>2</sub> monolayer on the SiO<sub>2</sub>/Si wafer, fabricating first-level FETs, depositing SiO<sub>2</sub> (~500 nm thick) by plasma-enhanced CVD, growing the second MoS<sub>2</sub> monolayer, fabricating second-level FETs, and so on. Figure 21d indicates an array of two vertical levels of MoS<sub>2</sub> FETs, both of which can be well modulated through the global back gate (Figure 21e). Note that as compared to the first-level device, which has an on-state sheet conductance of about 2.5  $\mu$ S and a mobility of about 11.5 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, the second-level device only exhibits a little performance degradation with an on-state sheet conductance of about 1.5  $\mu$ S and a mobility of about 8.8 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>. This suggests that the technique can be employed for 3D device architecture based on TMDCs, which may provide a new solution to the most attractive, yet challenging field in recent electronics research, monolithic 3D integration [47].

**Figure 21.** Multi-level stacking of MoS<sub>2</sub>/SiO<sub>2</sub> structures. (a) Schematics (left) and optical images of 1–3 level stacking; (b) optical absorption of three levels of stacking; (c) schematic of the fabrication of multi-level stacking of MoS<sub>2</sub>-based devices; (d) SEM image of MoS<sub>2</sub> FET arrays on the first (bottom) and second (top) layers (inset: close-up view; scale bar: 50 um); (e) current-voltage curves for a pair of devices on the first (left) and second (right) layers. The first-layer device is biased by the back gate of 50 V (green) and –50 V (grey), while the second-layer devices are at 100 V (yellow) and –100 V (grey). Reprinted with permission from [23]. Copyright 2015, Nature Publishing Group.

#### 4. Discussions and Outlook

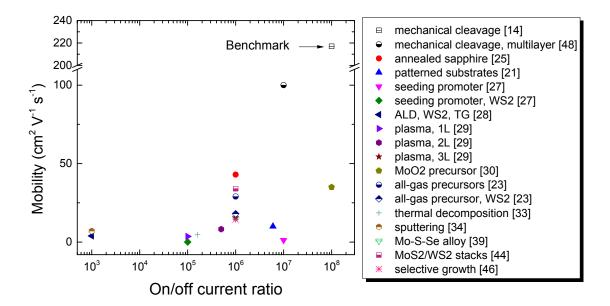

As introduced above, versatile scalable synthesis techniques for 2D semiconducting TMDCs have been developed in the literature, many of which have already led to commendable device performance (mobility  $>10~\rm cm^2~V^{-1}~s^{-1}$  with on/off current ratio  $>10^6$ ) approaching the state-of-the-art performance acquired by the high-quality mechanically-exfoliated MoS<sub>2</sub> flakes (Figure 22) [14,48]. More importantly, the techniques tend to be mature and have been effective for advanced engineering of 2D TMDC alloys, various 2D heterostructures, wafer-scale device fabrication and vertical stacking of 2D transistors. These suggest that 2D TMDC-based devices have great potential for up-scaled manufacturing of high-end nanoelectronics in the near future. In particular, the unique properties of 2D TMDCs will enable innovative applications in emerging electronics and provide ideal solutions to the challenging research fields nowadays, such as monolithic 3D integration.

**Figure 22.** Plots of mobility against the on/off current ratio for FETs based on TMDCs synthesized by some techniques introduced above and the state-of-the-art performance acquired by the mechanically-exfoliated MoS<sub>2</sub> [14]. Unless specified in the legend, all devices are back-gate FETs with MoS<sub>2</sub> channels. "TG" in the legend means "top gate".

However, referring to Figure 22, one may see that despite the versatile scalable synthesis techniques demonstrated, none of them outperform the mechanically-exfoliated MoS<sub>2</sub> flakes with respect to device mobility and on/off current ratio. There is still great space for further advances in the fields of the scalable synthesis of 2D semiconducting materials. We foresee that the issues concerning material crystallinity, interface contamination, spatial uniformity, controlled layer number and integration with device engineering will remain critical for a relatively long time. Here, we envision several tendencies in the upcoming research: (1) The device performance boost may have to rely on effective integration among different synthetic techniques. Seemingly, one single technique can hardly make a breakthrough in addressing all of the issues. In contrast, a comprehensive technology integrating substrate treatment, seeding promoters, gas-phase precursors and growth cycle control will likely lead to higher crystallinity, better layer number controllability, higher uniformity at the wafer scale and, hence, substantially improved device performance. (2) Material synthesis will be integrated with device fabrication to enable advanced engineering at multiple levels. A good example has been demonstrated in [46], where the precursors are patterned before material growth to facilitate the following device fabrication. (3) More efforts will be transferred from synthesizing high-quality simple materials to fabricating complex materials and building advanced structures, such as the 2D alloys and van der Waals heterostructures, aiming to offer more flexibility to construct advanced device architectures. (4) The established synthesis techniques may extend to newly-discovered 2D semiconducting materials within or outside the family of TMDCs to seek a breakthrough through a new perspective.

It is worth mentioning that the final device performance is not merely determined by the material synthesis. The device engineering also plays an important role in the performance boost. For example, as shown in Figure 22, most TMDC-based FETs are of the back-gate device structure with exposed channels, which, although simplifying device fabrication, usually does not give rise to high device

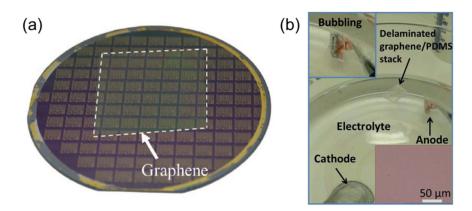

performance. This might be an important reason that they cannot outperform the state-of-the-art FETs based on mechanically-exfoliated MoS<sub>2</sub> where a high-k gate oxide is deposited on top of the channel to generate dielectric screening and to improve the mobility [14]. In most cases, the synthesized TMDCs have to be transferred from the growth substrates to the SiO<sub>2</sub>/Si substrates for device fabrication. Versatile techniques (Figure 23) have been developed for wafer-scale transfer of 2D materials [49–51]. They provide more flexibility for material synthesis and device fabrication. However, a common issue is that the residual contamination induced by the transfer processing may also degrade the device performance [52]. Therefore, in addition to improving material synthesis techniques, properly addressing the issues arising from device engineering is also crucial for 2D material-based electronic devices.

**Figure 23.** Wafer-scale transfer techniques for 2D materials. (a) Transferred graphene onto a 4-inch silicon wafer with poly(bisphenol A) carbonate (PC) as the carrier; (b) delamination of the graphene/polydimethylsiloxane (PDMS) stack using electrolysis (inset: optical microscope image of graphene transferred onto an SiO<sub>2</sub> layer). (a) Reprinted with permission from [49]. Copyright, 2014 IEEE. (b) Reprinted with permission from [50]. Copyright 2014, IEEE.

Finally, there are considerable efforts on computational simulations in order to understand the growth dynamics of 2D materials [53–59]. These theoretical studies provide mechanisms and explanations for experimental observations and useful suggestions for material quality improvement [56,58]. They also indicate optimal conditions for nucleation [57] and edge reconstruction [53] during growth, as well as predict the structure and stability of 2D materials grown on different substrates [54–57,59]. Such guidance is also valuable for experimentalists to improve their growth processes or to explore innovative techniques.

In summary, the review provides a systematic and comprehensive introduction of scalable synthesis techniques of 2D semiconducting materials for high-end applications in future nanoelectronics, most of which have shown promise in scaling up device fabrication. We hope the review is beneficial to the readers, either in establishing existing techniques for further research on 2D materials or in stimulating innovative ideas to enhance and extend the research on scalable synthesis techniques.

## Acknowledgments

We acknowledge the financial support by the Swedish Research Council through the research project iGRAPHENE (No. 2013-5759), the Framework project (No. 2014-6160) and the Marie Skłodowska

Curie International Career Grant (No. 2015-00395, co-funded by Marie Skłodowska-Curie Actions, through the Project INCA 600398), the European Research Council through the Proof of Concept Grant iPUBLIC (No. 641416), the Göran Gustafsson Foundation through the Young Researcher Prize (No. 1415B), the Olle Engkvist Byggmästare Foundation through the Research Project (No. 2014/799) and the Swedish Innovation Agency VINNOVA through the Strategic Innovation Program for Graphene, iEnergy (No. 2015-01337).

#### **Author Contributions**

Jiantong Li and Mikael Östling discussed the topic, surveyed the literature and wrote the manuscript.

#### **Conflicts of Interest**

The authors declare no conflict of interest.

#### References

- 1. Novoselov, K.S.; Fal'ko, V.I.; Colombo, L.; Gellert, P.R.; Schwab, M.G.; Kim, K. A roadmap for graphene. *Nature* **2012**, *490*, 192–200.

- 2. Wang, Q.H.; Kalantar-Zadeh, K.; Kis, A.; Coleman, J.N.; Strano, M.S. Electronics and optoelectronics of two-dimensional transition metal dichalcogenides. *Nat. Nanotechnol.* **2012**, *7*, 699–712.

- 3. Kim, S.J.; Choi, K.; Lee, B.; Kim, Y.; Hong, B.H. Materials for Flexible, Stretchable Electronics: Graphene and 2D Materials. *Annu. Rev. Mater. Res.* **2015**, *45*, 63–84.

- 4. Vaziri, S.; Lupina, G.; Henkel, C.; Smith, A.D.; Östling, M.; Dabrowski, J.; Lippert, G.; Mehr, W.; Lemme, M.C. A Graphene-Based Hot Electron Transistor. *Nano Lett.* **2013**, *13*, 1435–1439.

- 5. Lemme, M.C.; Li, L.-J.; Palacios, T.; Schwierz, F. Two-dimensional materials for electronic applications. *MRS Bull.* **2014**, *39*, 711–718.

- 6. Lemme, M.C.; Echtermeyer, T.J.; Baus, M.; Kurz, H. A Graphene Field-Effect Device. *IEEE Electron Device Lett.* **2007**, *28*, 282–284.

- 7. Lopez-Sanchez, O.; Lembke, D.; Kayci, M.; Radenovic, A.; Kis, A. Ultrasensitive photodetectors based on monolayer MoS<sub>2</sub>. *Nat. Nanotechnol.* **2013**, *8*, 497–501.

- 8. Yim, C.; O'Brien, M.; McEvoy, N.; Riazimehr, S.; Schäfer-Eberwein, H.; Bablich, A.; Pawar, R.; Iannaccone, G.; Downing, C.; Fiori, G.; *et al.* Heterojunction Hybrid Devices from Vapor Phase Grown MoS<sub>2</sub>. *Sci. Rep.* **2014**, *4*, 5458.

- 9. Li, J.; Lemme, M.C.; Östling, M. Inkjet Printing of 2D Layered Materials. *Chemphyschem* **2014**, *15*, 3427–3434.

- 10. Li, J.; Östling, M. Prevention of Graphene Restacking for Performance Boost of Supercapacitors—A Review. *Crystals* **2013**, *3*, 163–190.

- 11. Smith, A.D.; Niklaus, F.; Paussa, A.; Vaziri, S.; Fischer, A.C.; Sterner, M.; Forsberg, F.; Delin, A.; Esseni, D.; Palestri, P.; *et al.* Electromechanical Piezoresistive Sensing in Suspended Graphene Membranes. *Nano Lett.* **2013**, *13*, 3237–3242.

- 12. Shen, H.; Zhang, L.; Liu, M.; Zhang, Z. Biomedical applications of graphene. *Theranostics* **2012**, *2*, 283–294.

- 13. Geim, A.K.; Grigorieva, I.V. Van der Waals heterostructures. *Nature* **2013**, 499, 419–425.

- 14. Radisavljevic, B.; Radenovic, A.; Brivio, J.; Giacometti, V.; Kis, A. Single-layer MoS<sub>2</sub> transistors. *Nat. Nanotechnol.* **2011**, *6*, 147–150.

- 15. Liu, H.; Du, Y.; Deng, Y.; Ye, P.D. Semiconducting black phosphorus: Synthesis, transport properties and electronic applications. *Chem. Soc. Rev.* **2015**, *44*, 2732–2743.

- 16. Nicolosi, V.; Chhowalla, M.; Kanatzidis, M.G.; Strano, M.S.; Coleman, J.N. Liquid Exfoliation of Layered Materials. *Science* **2013**, 340, doi: 10.1126/science.1226419.

- 17. Li, J.; Ye, F.; Vaziri, S.; Muhammed, M.; Lemme, M.C.; Östling, M. Efficient Inkjet Printing of Graphene. *Adv. Mater.* **2013**, *25*, 3985–3992.

- 18. Li, J.; Naiini, M.M.; Vaziri, S.; Lemme, M.C.; Östling, M. Inkjet Printing of MoS<sub>2</sub>. *Adv. Funct. Mater.* **2014**, *24*, 6524–6531.

- 19. Kong, D.; Wang, H.; Cha, J.J.; Pasta, M.; Koski, K.J.; Yao, J.; Cui, Y. Synthesis of MoS<sub>2</sub> and MoSe<sub>2</sub> Films with Vertically Aligned Layers. *Nano Lett.* **2013**, *13*, 1341–1347.

- 20. Shi, Y.; Li, H.; Li, L.J. Recent advances in controlled synthesis of two-dimensional transition metal dichalcogenides via vapor deposition techniques. *Chem. Soc. Rev.* **2015**, *44*, 2744–2756.

- 21. Najmaei, S.; Liu, Z.; Zhou, W.; Zou, X.; Shi, G.; Lei, S.; Yakobson, B.I.; Idrobo, J.-C.; Ajayan, P.M.; Lou, J. Vapour phase growth and grain boundary structure of molybdenum disulphide atomic layers. *Nat. Mater.* **2013**, *12*, 754–759.

- 22. Ling, X.; Lee, Y.-H.; Lin, Y.; Fang, W.; Yu, L.; Dresselhaus, M.S.; Kong, J. Role of the Seeding Promoter in MoS<sub>2</sub> Growth by Chemical Vapor Deposition. *Nano Lett.* **2014**, *14*, 464–472.

- 23. Kang, K.; Xie, S.; Huang, L.; Han, Y.; Huang, P.Y.; Mak, K.F.; Kim, C.-J.; Muller, D.; Park, J. High-mobility three-atom-thick semiconducting films with wafer-scale homogeneity. *Nature* **2015**, *520*, 656–660.

- 24. Dumcenco, D.; Ovchinnikov, D.; Marinov, K.; Lazić, P.; Gibertini, M.; Marzari, N.; Sanchez, O.L.; Kung, Y.; Krasnozhon, D.; Chen, M.; *et al.* Large-Area Epitaxial Monolayer MoS<sub>2</sub>. *ACS Nano* **2015**, *9*, 4611–4620.

- 25. Zhang, Y.; Zhang, Y.; Ji, Q.; Ju, J.; Yuan, H.; Shi, J.; Gao, T.; Ma, D.; Liu, M.; Chen, Y.; *et al.* Controlled Growth of High-Quality Monolayer WS<sub>2</sub> Layers on Sapphire and Imaging Its Grain Boundary. *ACS Nano* **2013**, *7*, 8963–8971.

- 26. Lee, Y.H.; Zhang, X.Q.; Zhang, W.; Chang, M.T.; Lin, C.T.; Chang, K.D.; Yu, Y.C.; Wang, J.T.W.; Chang, C.S.; Li, L.J.; *et al.* Synthesis of large-area MoS<sub>2</sub> atomic layers with chemical vapor deposition. *Adv. Mater.* **2012**, *24*, 2320–2325.

- 27. Lee, Y.; Yu, L.; Wang, H.; Fang, W.; Ling, X.; Shi, Y.; Lin, C.-T.; Huang, J.-K.; Chang, M.-T.; Chang, C.-S.; *et al.* Synthesis and Transfer of Single Layer Transition Metal Disulfides on Diverse Surfaces. *Nano Lett.* **2013**, *13*, 1852–1857.

- 28. Song, J.; Park, J.; Lee, W.; Choi, T.; Jung, H.; Lee, C.W.; Hwang, S.-H.; Myoung, J.M.; Jung, J.-H.; Kim, S.; *et al.* Layer-Controlled, Wafer-Scale, and Conformal Synthesis of Tungsten Disulfide Nanosheets Using Atomic Layer Deposition. *ACS Nano* **2013**, *7*, 11333–11340.

- 29. Jeon, J.; Jang, S.K.; Jeon, S.M.; Yoo, G.; Jang, Y.H.; Park, J.-H.; Lee, S. Layer-controlled CVD growth of large-area two-dimensional MoS<sub>2</sub> films. *Nanoscale* **2015**, *7*, 1688–1695.

30. Bilgin, I.; Liu, F.; Vargas, A.; Winchester, A.; Man, M.K.L.; Upmanyu, M.; Dani, K.M.; Gupta, G.; Talapatra, S.; Mohite, A.D.; *et al.* Chemical Vapor Deposition Synthesized Atomically Thin Molybdenum Disulfide with Optoelectronic-Grade Crystalline Quality. *ACS Nano* **2015**, *9*, 8822–8832.

- 31. Yu, Y.; Li, C.; Liu, Y.; Su, L.; Zhang, Y.; Cao, L. Controlled scalable synthesis of uniform, high-quality monolayer and few-layer MoS<sub>2</sub> films. *Sci. Rep.* **2013**, *3*, 1866.

- 32. Grønborg, S.S.; Ulstrup, S.; Bianchi, M.; Dendzik, M.; Sanders, C.E.; Lauritsen, J.V.; Hofmann, P.; Miwa, J.A. Synthesis of Epitaxial Single-Layer MoS<sub>2</sub> on Au(111). *Langmuir* **2015**, *31*, 9700–9706.

- 33. Liu, K.-K.; Zhang, W.; Lee, Y.-H.; Lin, Y.-C.; Chang, M.-T.; Su, C.-Y.; Chang, C.-S.; Li, H.; Shi, Y.; Zhang, H.; *et al.* Growth of large-area and highly crystalline MoS<sub>2</sub> thin layers on insulating substrates. *Nano Lett.* **2012**, *12*, 1538–1544.

- 34. Tao, J.; Chai, J.; Lu, X.; Wong, L.M.; Wong, T.I.; Pan, J.; Xiong, Q.; Chi, D.; Wang, S. Growth of wafer-scale MoS<sub>2</sub> monolayer by magnetron sputtering. *Nanoscale* **2015**, *7*, 2497–2503.

- 35. Yue, R.; Barton, A.T.; Zhu, H.; Azcatl, A.; Pena, L.F.; Wang, J.; Peng, X.; Lu, N.; Cheng, L.; Addou, R.; *et al.* HfSe<sub>2</sub> Thin Films: 2D Transition Metal Dichalcogenides Grown by Molecular Beam Epitaxy. *ACS Nano* **2015**, *9*, 474–480.

- 36. Zhang, W.; Li, X.; Jiang, T.; Song, J.; Lin, Y.; Zhu, L.; Xu, X. CVD synthesis of Mo<sub>(1-x)</sub>W<sub>x</sub>S<sub>2</sub> and MoS<sub>2(1-x)</sub>Se<sub>2x</sub> alloy monolayers aimed at tuning the bandgap of molybdenum disulfide. *Nanoscale* **2015**, 7, 13554–13560.

- 37. Feng, Q.; Zhu, Y.; Hong, J.; Zhang, M.; Duan, W.; Mao, N.; Wu, J.; Xu, H.; Dong, F.; Lin, F.; *et al.* Growth of large-area 2D MoS<sub>2(1-x)</sub>Se<sub>2x</sub> semiconductor alloys. *Adv. Mater.* **2014**, *26*, 2648–2653.

- 38. Feng, Q.; Mao, N.; Wu, J.; Xu, H.; Wang, C.; Zhang, J.; Xie, L. Growth of MoS<sub>2(1-x)</sub>Se<sub>2x</sub> (x = 0.41–1.00) Monolayer Alloys with Controlled Morphology by Physical Vapor Deposition. *ACS Nano* **2015**, *9*, 7450–7455.

- 39. Gong, Y.; Liu, Z.; Lupini, A.R.; Shi, G.; Lin, J.; Najmaei, S.; Lin, Z.; Elías, A.L.; Berkdemir, A.; You, G.; *et al.* Band Gap Engineering and Layer-by-Layer Mapping of Selenium-doped Molybdenum Disulfide. *Nano Lett.* **2014**, *14*, 442–449.

- 40. Song, J.-G.; Ryu, G.H.; Lee, S.J.; Sim, S.; Lee, C.W.; Choi, T.; Jung, H.; Kim, Y.; Lee, Z.; Myoung, J.-M.; *et al.* Controllable synthesis of molybdenum tungsten disulfide alloy for vertically composition-controlled multilayer. *Nat. Commun.* **2015**, *6*, 7817.

- 41. Shi, Y.; Zhou, W.; Lu, A.-Y.; Fang, W.; Lee, Y.-H.; Hsu, A.L.; Kim, S.M.; Kim, K.K.; Yang, H.Y.; Li, L.-J.; *et al.* Van der Waals Epitaxy of MoS<sub>2</sub> Layers Using Graphene as Growth Templates. *Nano Lett.* **2012**, *12*, 2784–2791.

- 42. Miwa, J.A.; Dendzik, M.; Grønborg, S.S.; Bianchi, M.; Lauritsen, J.V.; Hofmann, P.; Ulstrup, S. Van der Waals Epitaxy of Two-Dimensional MoS<sub>2</sub>-Graphene Heterostructures in Ultrahigh Vacuum. *ACS Nano* **2015**, *9*, 6502–6510.

- 43. Wang, S.; Wang, X.; Warner, J.H. All Chemical Vapor Deposition Growth of MoS<sub>2</sub>:h-BN Vertical van der Waals Heterostructures. *ACS Nano* **2015**, *9*, 5246–5254.

- 44. Gong, Y.; Lin, J.; Wang, X.; Shi, G.; Lei, S.; Lin, Z.; Zou, X.; Ye, G.; Vajtai, R.; Yakobson, B.I.; *et al.* Vertical and in-plane heterostructures from WS<sub>2</sub>/MoS<sub>2</sub> monolayers. *Nat. Mater.* **2014**, *13*, 1135–1142.

45. Huang, C.; Wu, S.; Sanchez, A.M.; Peters, J.J.P.; Beanland, R.; Ross, J.S.; Rivera, P.; Yao, W.; Cobden, D.H.; Xu, X. Lateral heterojunctions within monolayer MoSe<sub>2</sub>-WSe<sub>2</sub> semiconductors. *Nat. Mater.* **2014**, *13*, 1096–1101.

- 46. Han, G.H.; Kybert, N.J.; Naylor, C.H.; Lee, B.S.; Ping, J.; Park, J.H.; Kang, J.; Lee, S.Y.; Lee, Y.H.; Agarwal, R.; *et al.* Seeded growth of highly crystalline molybdenum disulphide monolayers at controlled locations. *Nat. Commun.* **2015**, *6*, 6128.

- 47. Garidis, K.; Jayakumar, G.; Asadollahi, A.; Litta, E.D.; Hellström, P.-E.; Östling, M. Characterization of bonding surface and electrical insulation properties of inter layer dielectrics for 3D monolithic integration. In Proceedings of the IEEE Ultimate Integration on Silicon (EUROSOI-ULIS), Bologna, Italy, 26–28 January 2015; pp. 165–168.

- 48. Kim, S.; Konar, A.; Hwang, W.-S.; Lee, J.H.; Lee, J.; Yang, J.; Jung, C.; Kim, H.; Yoo, J.-B.; Choi, J.-Y.; *et al.* High-mobility and low-power thin-film transistors based on multilayer MoS<sub>2</sub> crystals. *Nat. Commun.* **2012**, *3*, 1011.

- 49. Smith, A.D.; Vaziri, S.; Rodriguez, S.; Östling, M.; Lemme, M.C. Wafer scale graphene transfer for back end of the line device integration. In Proceedings of the ULIS 2014—2014 15th International Conference on Ultimate Integration on Silicon, Stockholm, Sweden, 7–9 April 2014; pp. 29–32.

- 50. Vaziri, S.; Smith, A.D.; Lupina, G.; Lemme, M.C.; Östling, M. PDMS-supported Graphene Transfer Using Intermediary Polymer Layers. In Proceedings of the 2014 44th European Solid State Device Research Conference (ESSDERC), Venice, Italy, 22–26 September 2014; pp. 309–312.

- 51. Kataria, S.; Wagner, S.; Ruhkopf, J.; Gahoi, A.; Pandey, H.; Bornemann, R.; Vaziri, S.; Smith, A.D.; Ostling, M.; Lemme, M.C. Chemical vapor deposited graphene: From synthesis to applications. *Phys. Status Solidi A* **2014**, *211*, 2439–2449.

- 52. Lupina, G.; Kitzmann, J.; Costina, I.; Lukosius, M.; Wenger, C.; Wolff, A.; Pasternak, I.; Krajewska, A.; Strupinski, W.; Vaziri, S.; *et al.* Residual Metallic Contamination of Transferred Chemical Vapor Deposited Graphene. *ACS Nano* **2015**, *9*, 4776–4785.

- 53. Gao, J.; Zhao, J.; Ding, F. Transition metal surface passivation induced graphene edge reconstruction. *J. Am. Chem. Soc.* **2012**, *134*, 6204–6209.

- 54. Gao, J.; Zhang, J.; Liu, H.; Zhang, Q.; Zhao, J. Structures, mobilities, electronic and magnetic properties of point defects in silicene. *Nanoscale* **2013**, *5*, 9785–9792.

- 55. Penev, E.S.; Bhowmick, S.; Sadrzadeh, A.; Yakobson, B.I. Polymorphism of Two-Dimensional Boron. *Nano Lett.* **2012**, *12*, 2441–2445.

- 56. Gao, J.; Zhao, J. Initial geometries, interaction mechanism and high stability of silicene on Ag(111) surface. *Sci. Rep.* **2012**, *2*, 861.

- 57. Gao, J.; Yip, J.; Zhao, J.; Yakobson, B.I.; Ding, F. Graphene nucleation on transition metal surface: Structure transformation and role of the metal step edge. *J. Am. Chem. Soc.* **2011**, *133*, 5009–5015.

- 58. Artyukhov, V.I.; Liu, Y.; Yakobson, B.I. Equilibrium at the edge and atomistic mechanisms of graphene growth. *Proc. Natl. Acad. Sci. USA* **2012**, *109*, 15136–15140.

59. Gao, J.; Ding, F. The structure and stability of magic carbon clusters observed in graphene chemical vapor deposition growth on Ru(0001) and Rh(111) surfaces. *Angew. Chem. Int. Ed. Engl.* **2014**, *53*, 14031–14035.

© 2015 by the authors; licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution license (http://creativecommons.org/licenses/by/4.0/).