Smart E-Beam for Defect Identification & Analysis in the Nanoscale Technology Nodes: Technical Perspectives

Abstract

:1. Introduction

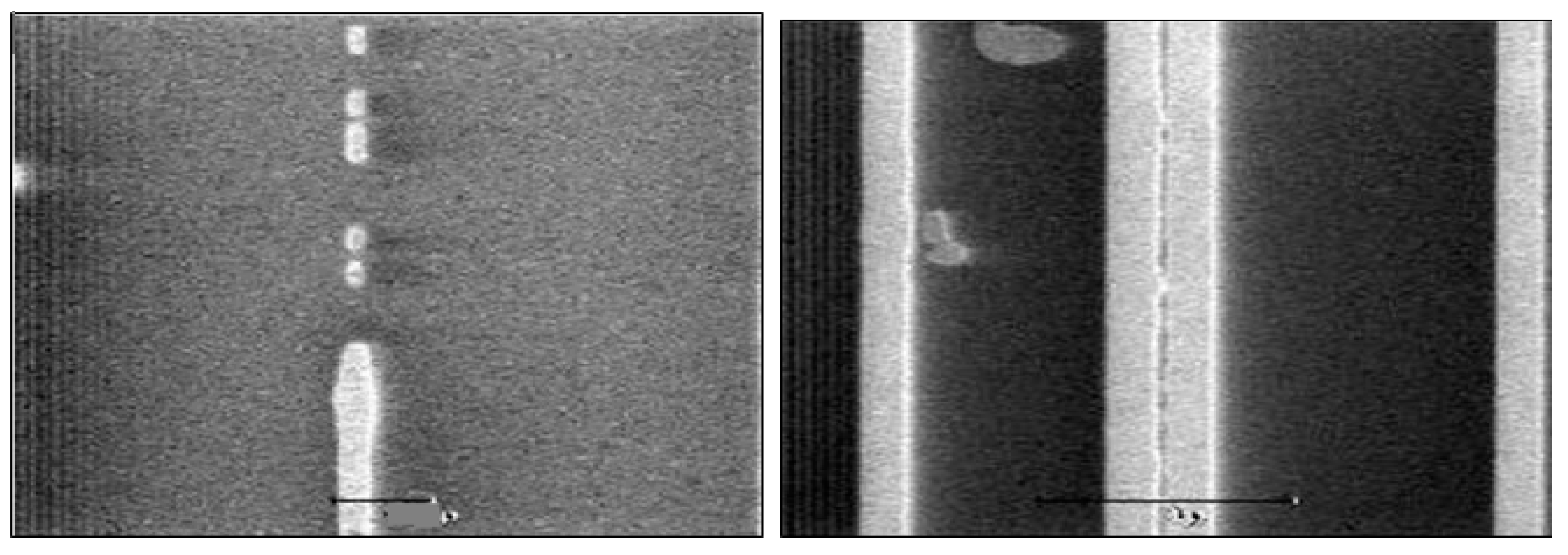

2. Smart E-Beam versus Legacy Optical Wafer Inspection at Nodes below 10 nm

2.1. Patterned Wafer Inspection System

2.2. The Fundamental Use of E-Beam and Optical Inspection

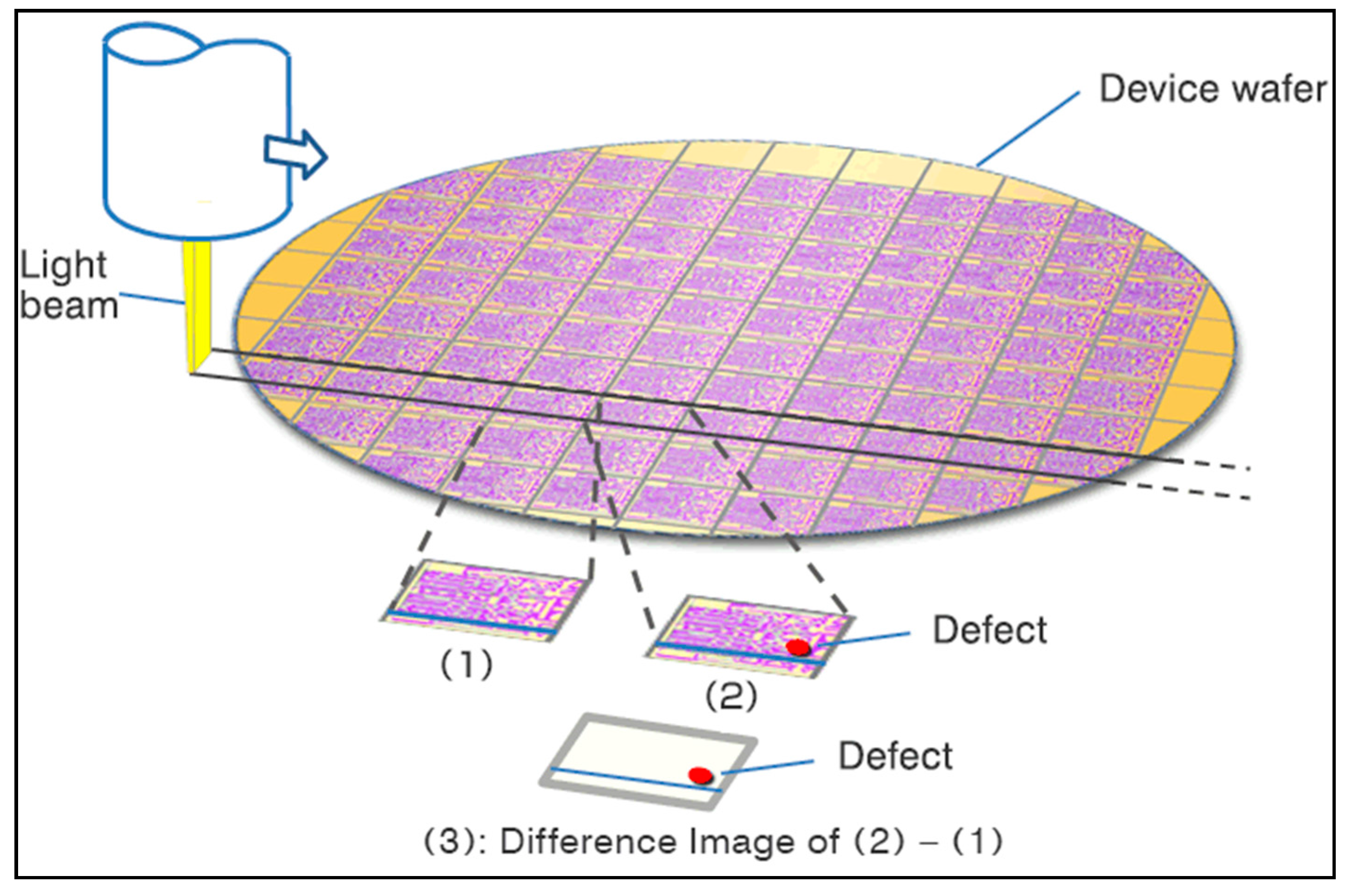

2.2.1. Detecting Defects on a Wafer Using Defect-Specific and Multi-Channel Information

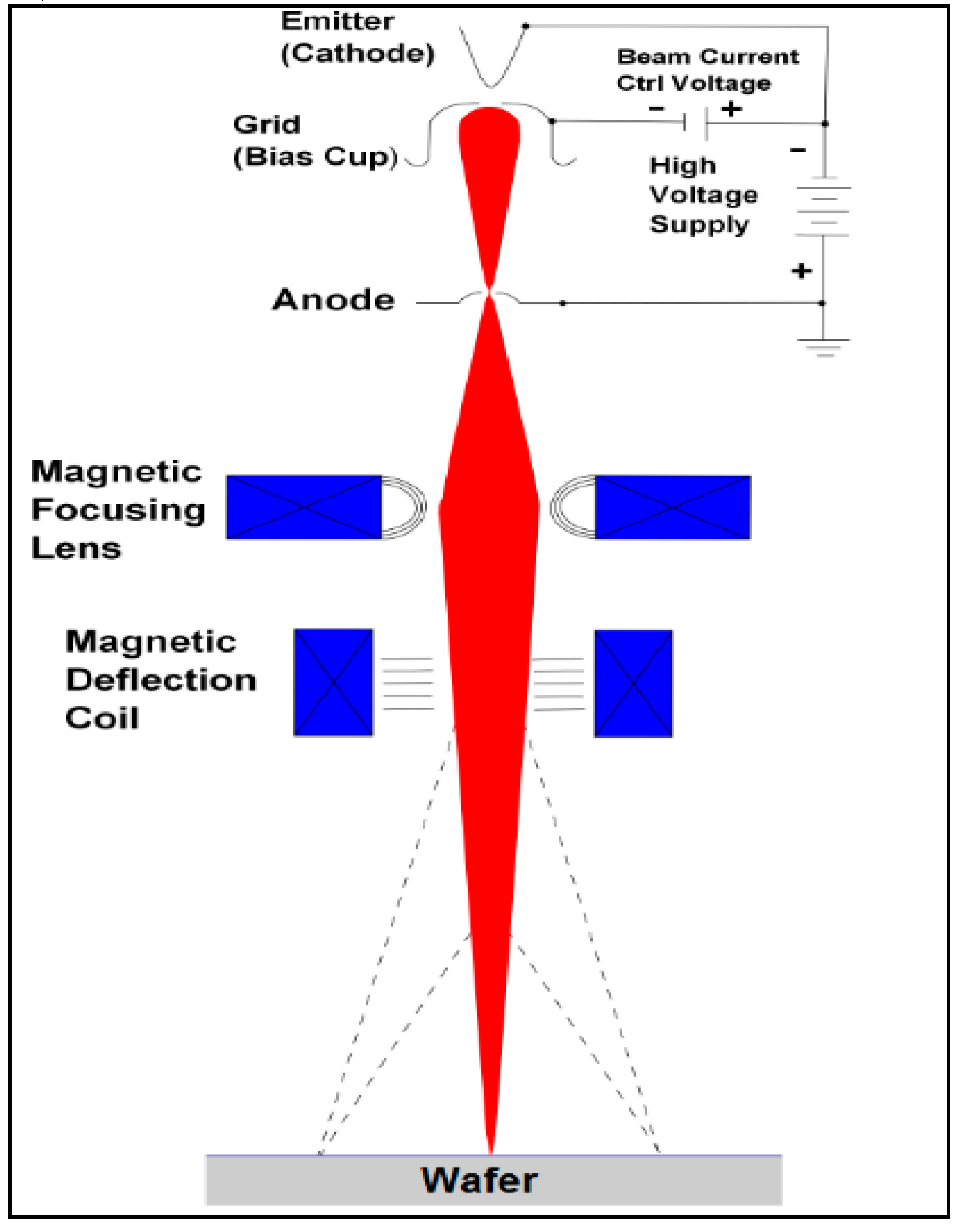

2.2.2. E-Beam

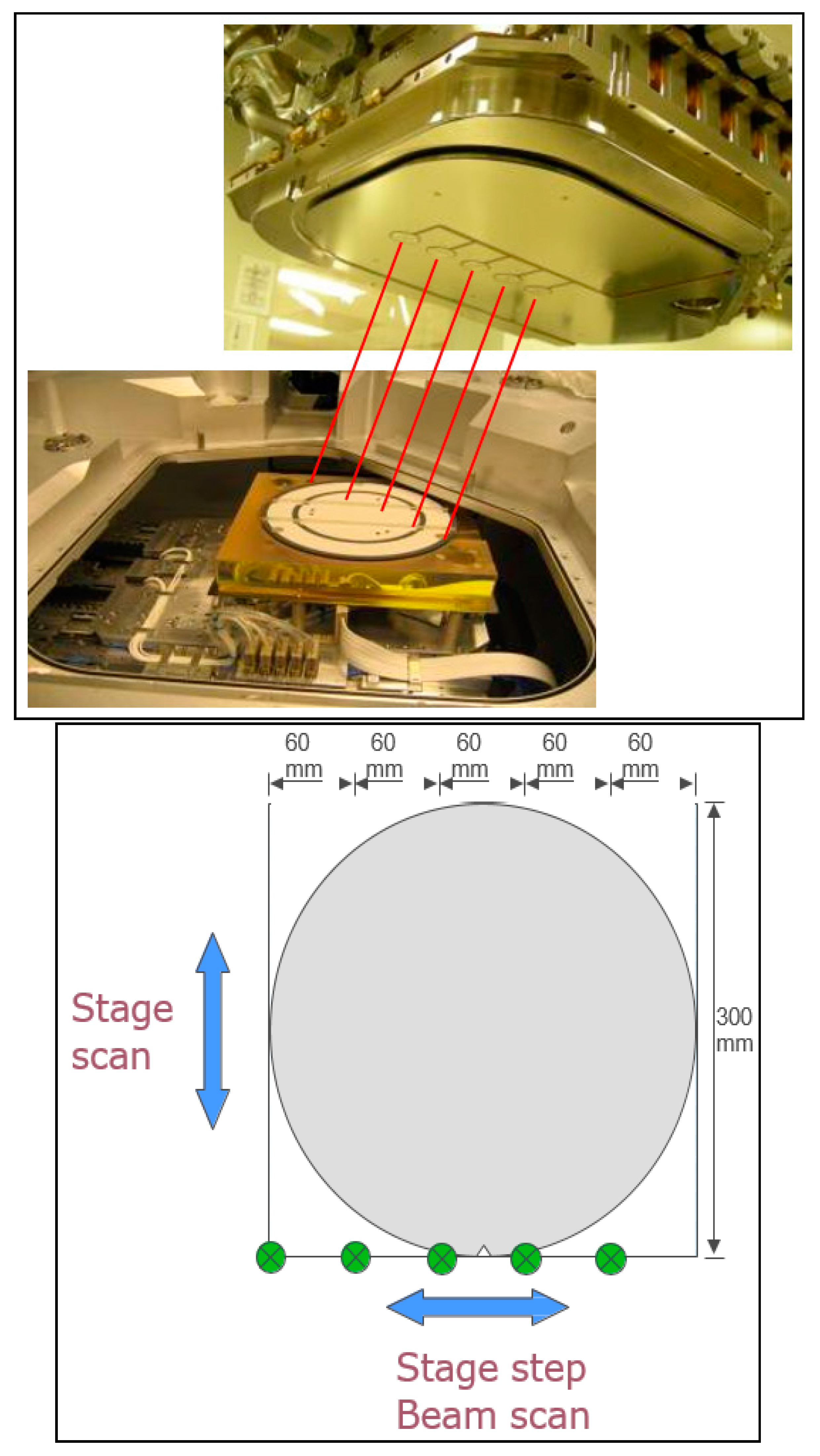

- Step and scan: The wafer is held stationary to capture an image of the wafer at one location. The process is repeated until the whole care area is covered.

- Swathing: The wafer is moving when the image is being captured so that a whole strip of two-dimensional (2-D) image is created also known as a swath. The process is repeated with multiple swaths until the whole care area has been covered.

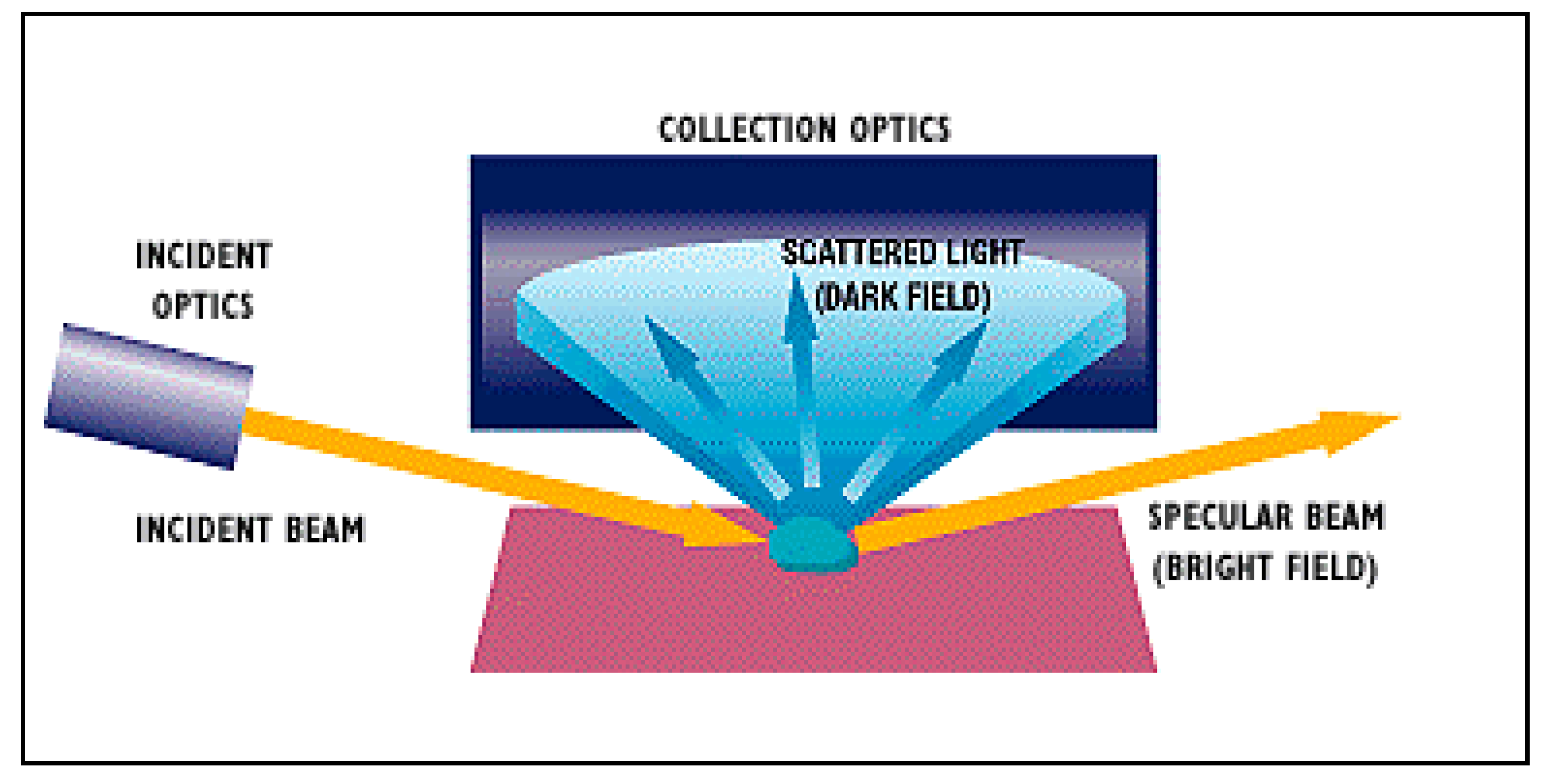

2.2.3. Optical Tools

2.3. Techniques Explored to Make E-Beam Inspection Smarter to Compensate for Its Slower Performance

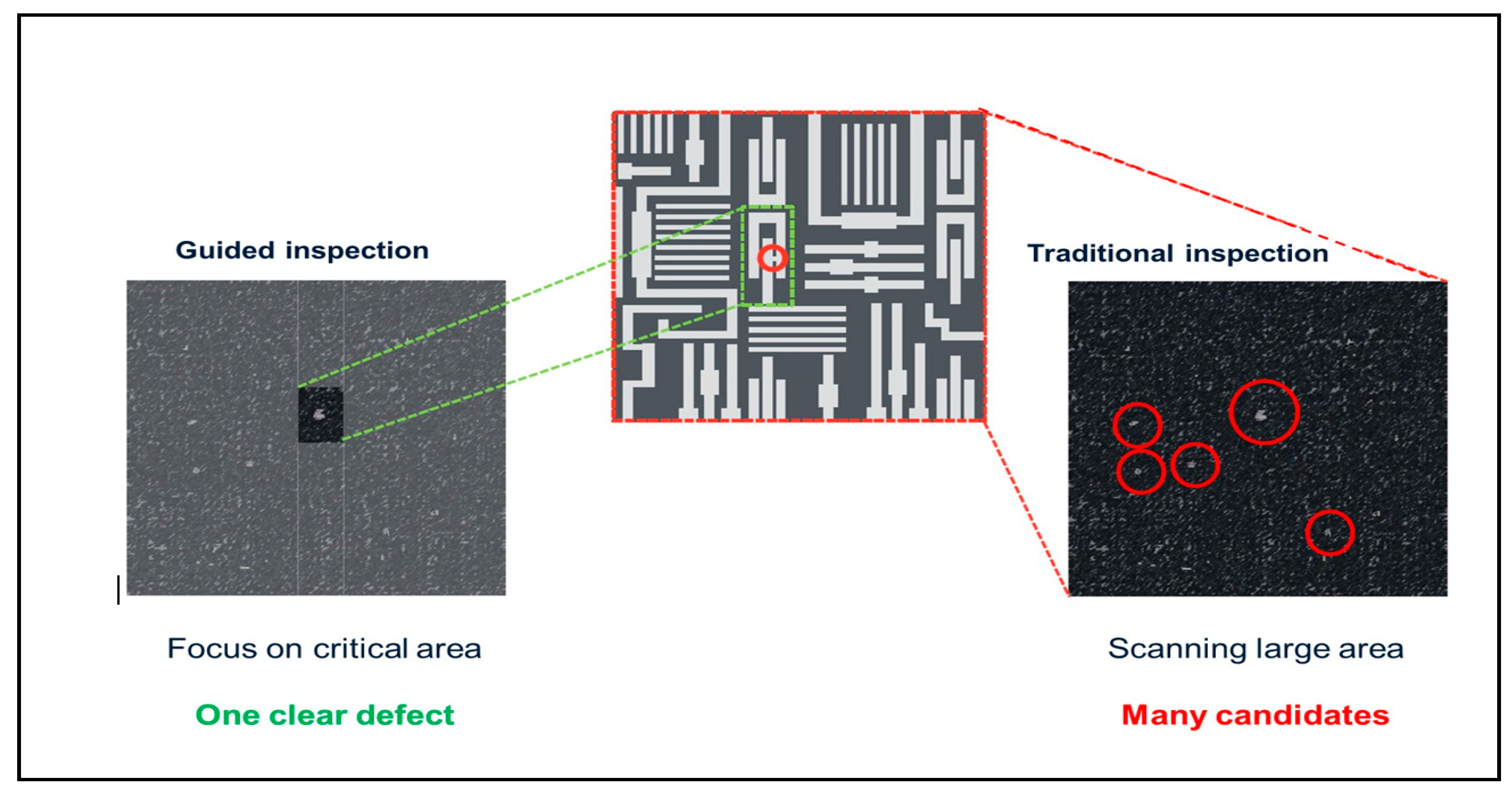

2.3.1. DBI Helps in Faster EBI Recipe Setup

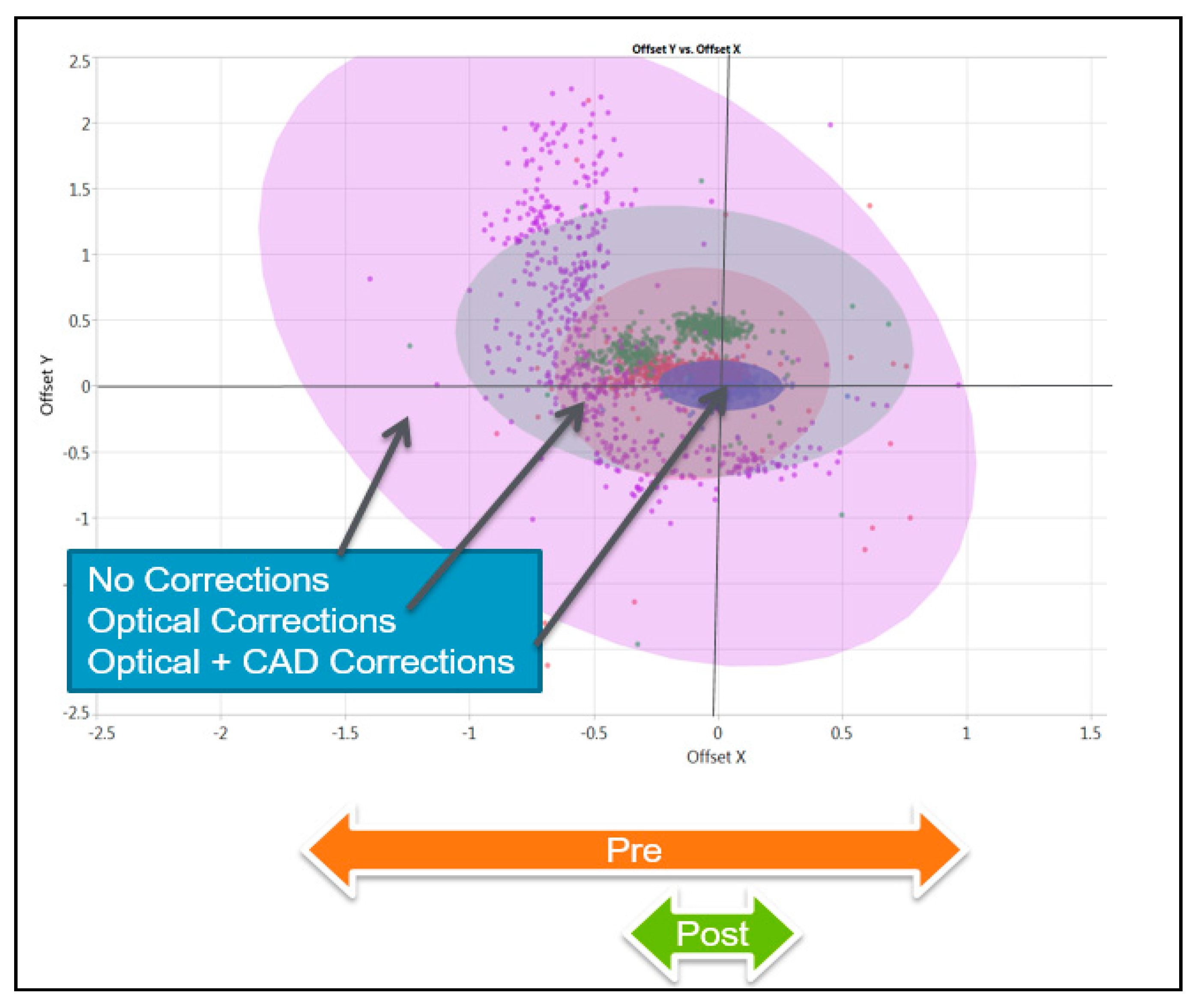

2.3.2. Accuracy Enhancement Using DBI for EBI

2.3.3. Detecting Defects on a Wafer Using Defect-Specific and Multi-Channel Information

2.3.4. EBI for Complete Wafer Inspection

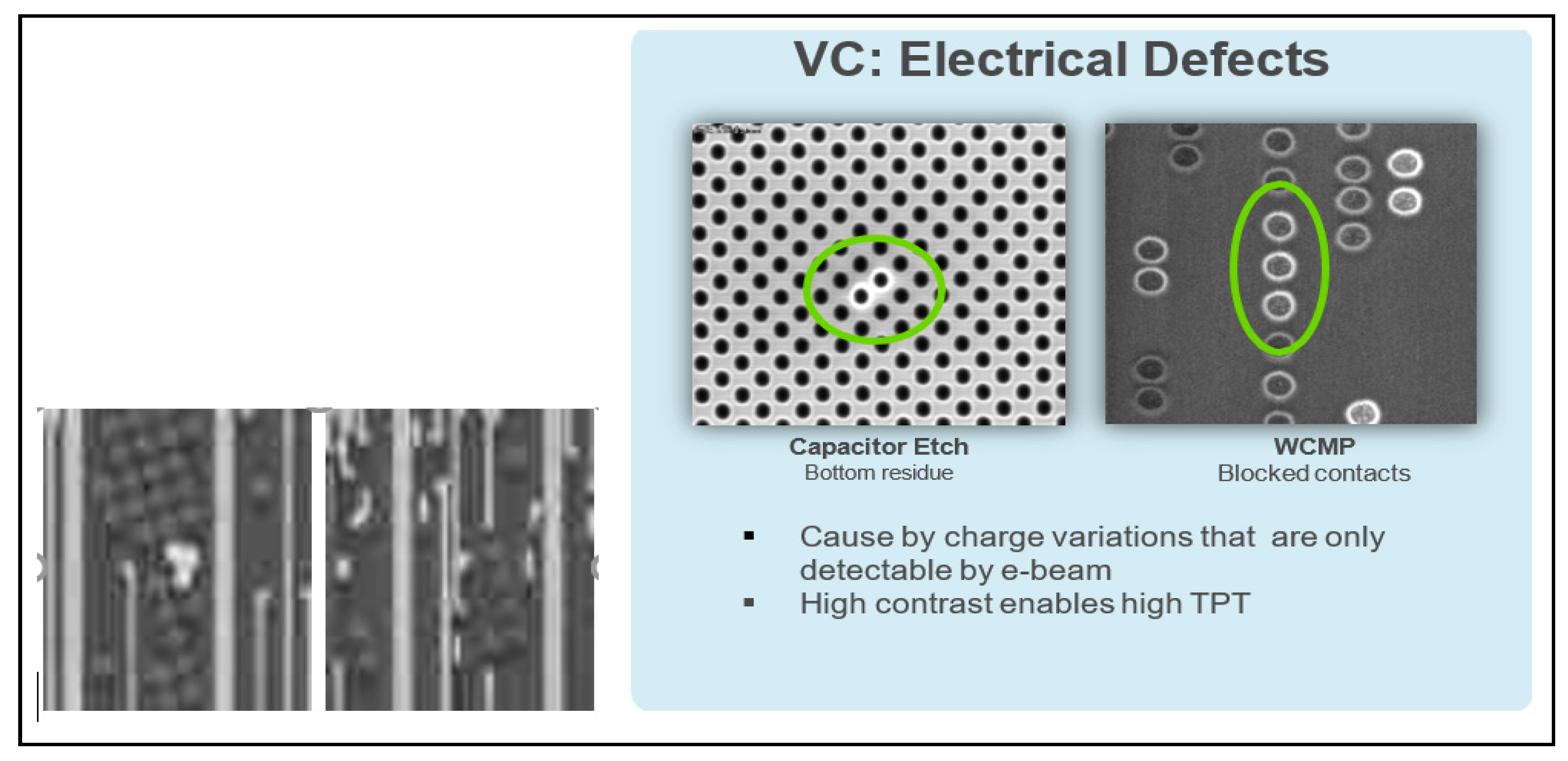

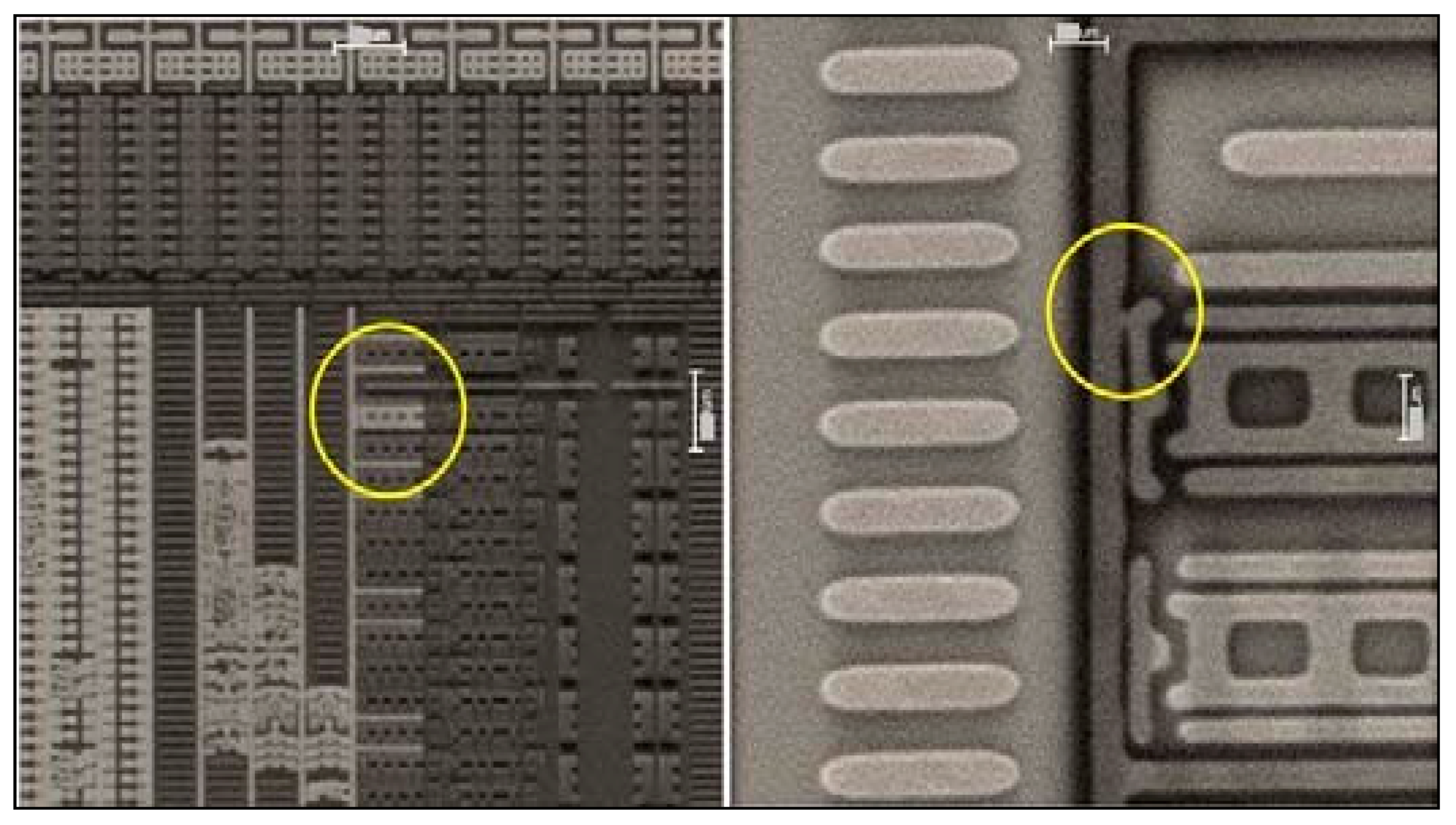

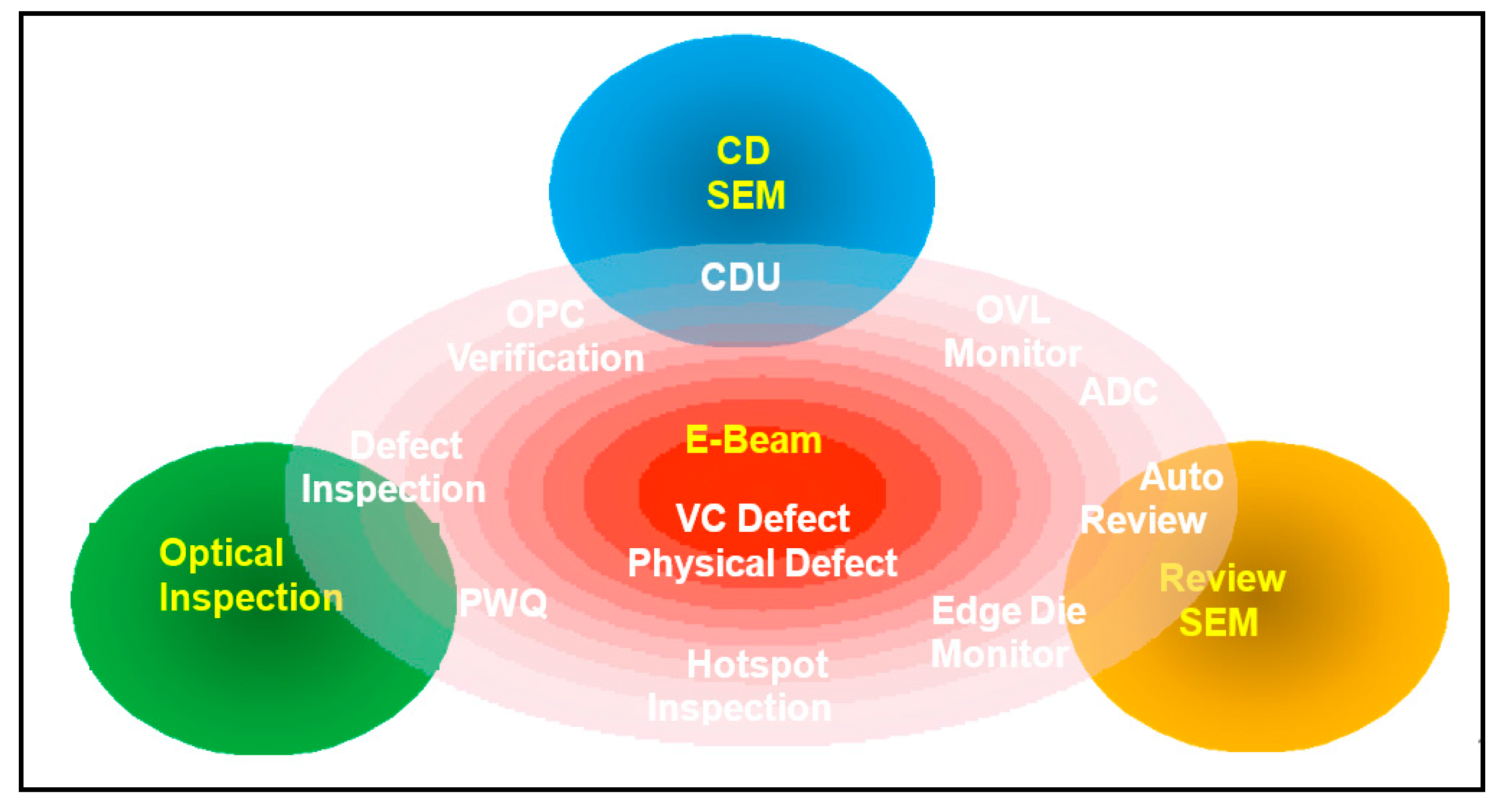

- Voltage contrast inspection: Voltage contrast inspection is used to isolate electrically active defects both buried and at the wafer surface (see Figure 9).

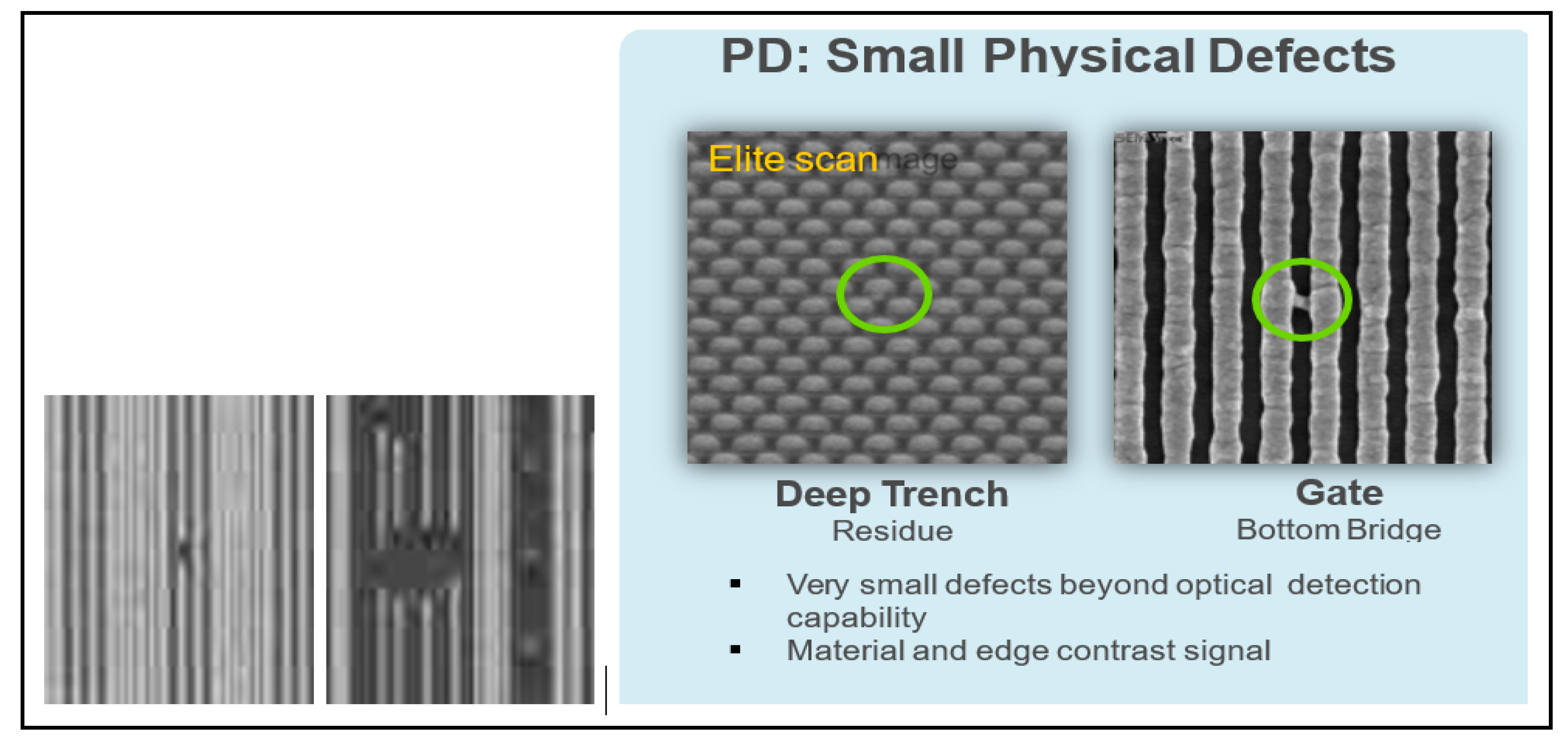

- Physical defect inspection: Physical defect inspection is used to detect defects that may not yet be electrically active but will likely impact yield (see Figure 10).

Metal 1 Dose Modulated Wafer

Voltage Contrast Signal from Prior Level Physical Defects

Accelerate Time to Review Process

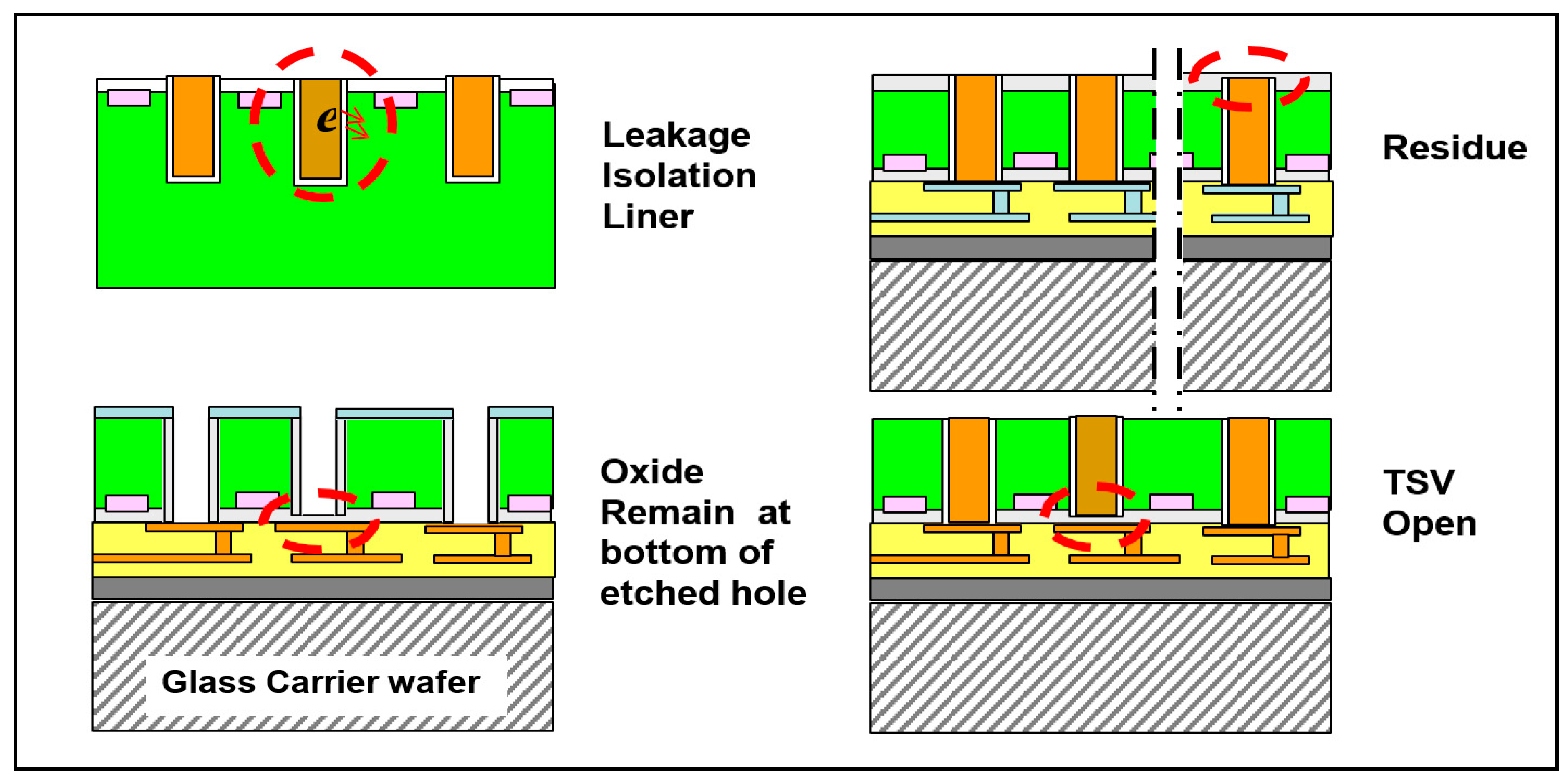

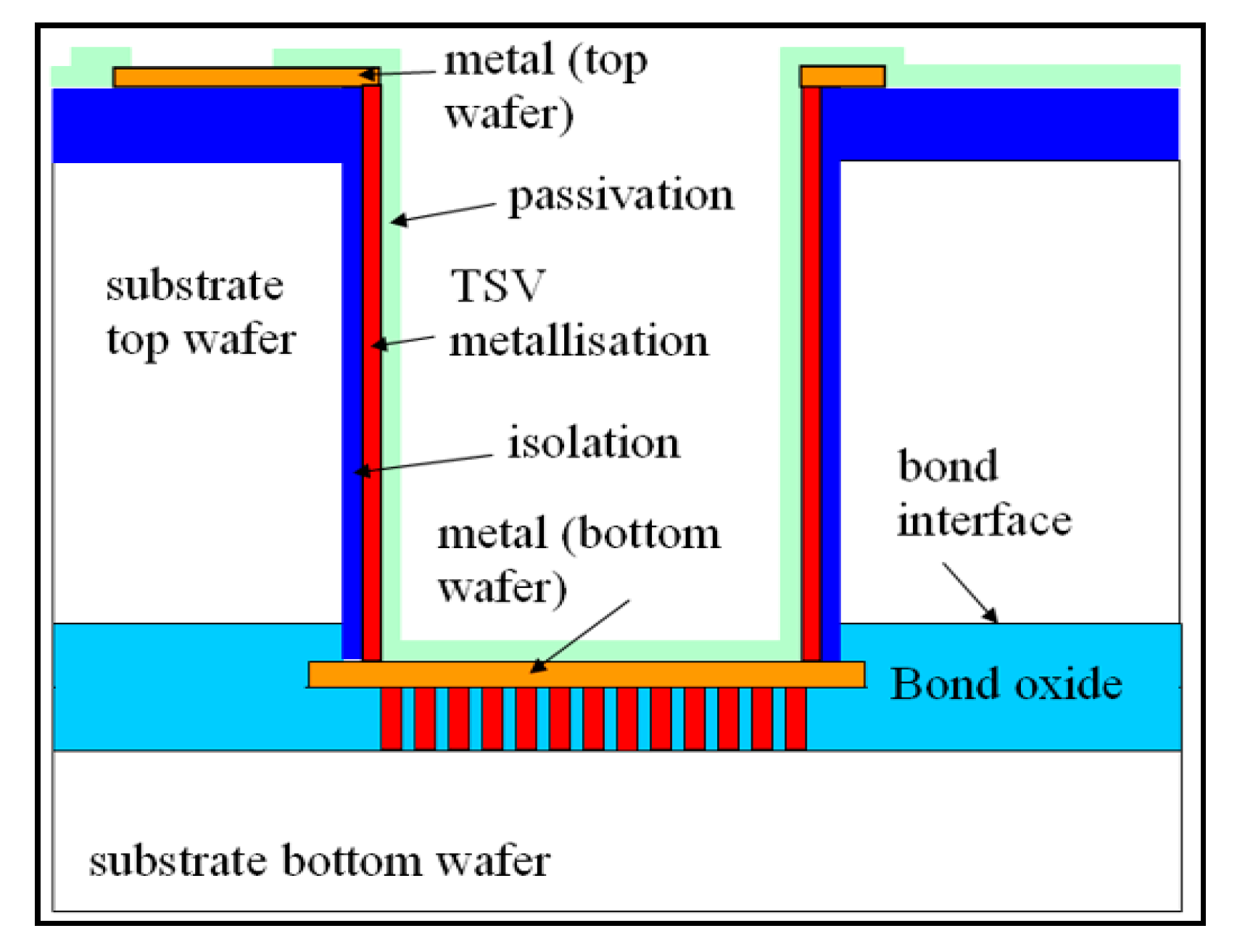

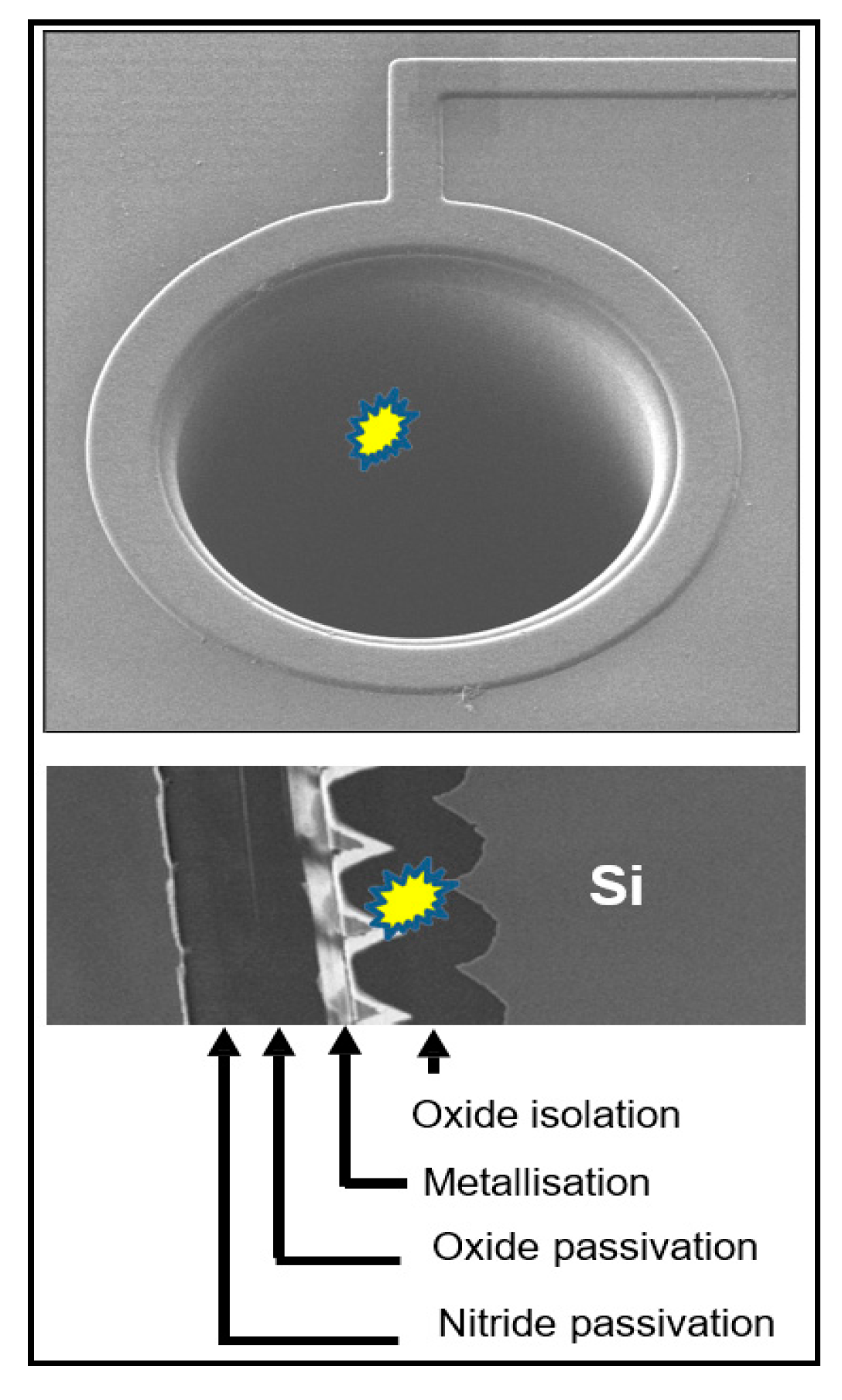

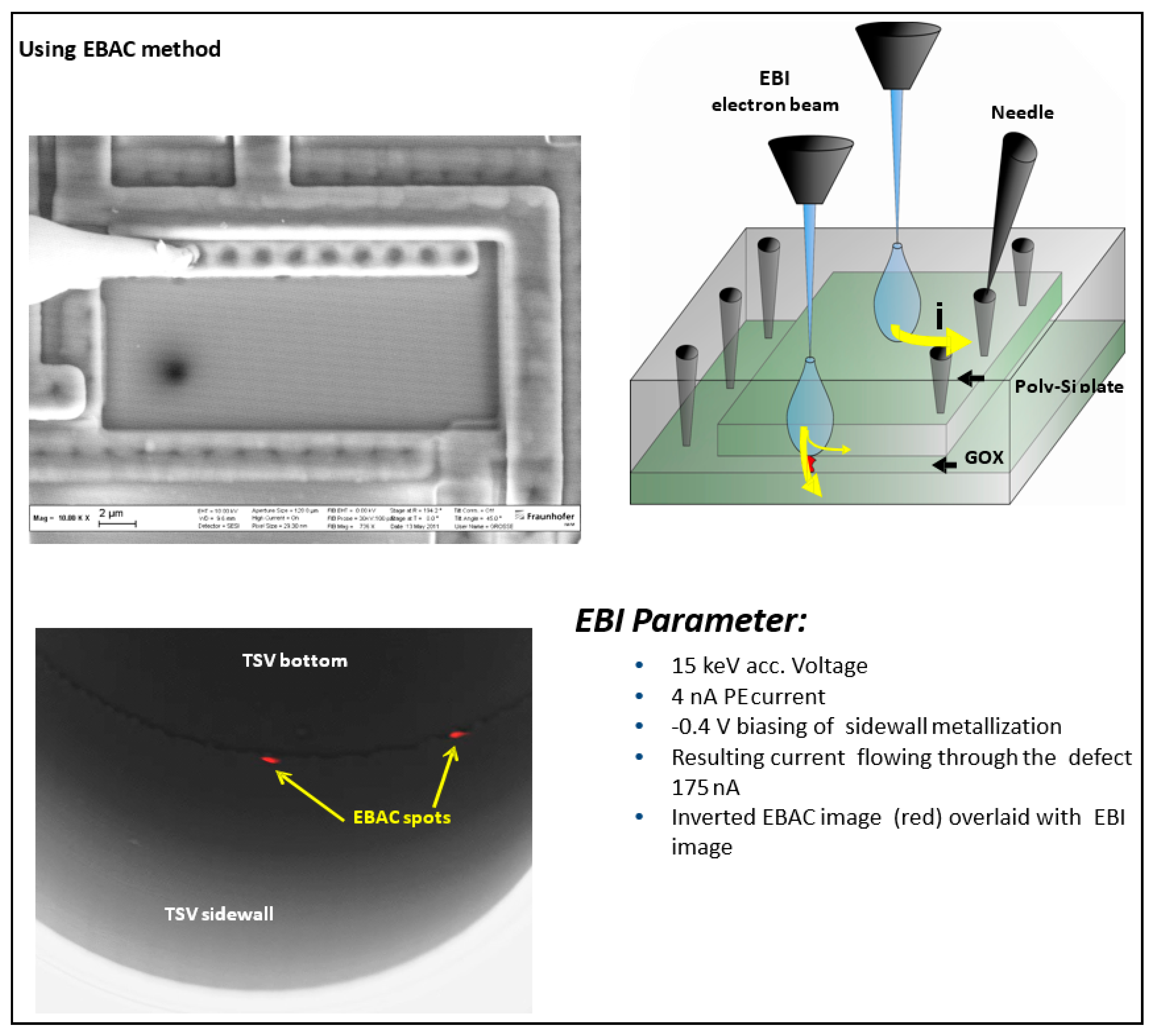

Potential Through-Silicon via (TSV) Application by E-Beam Inspection

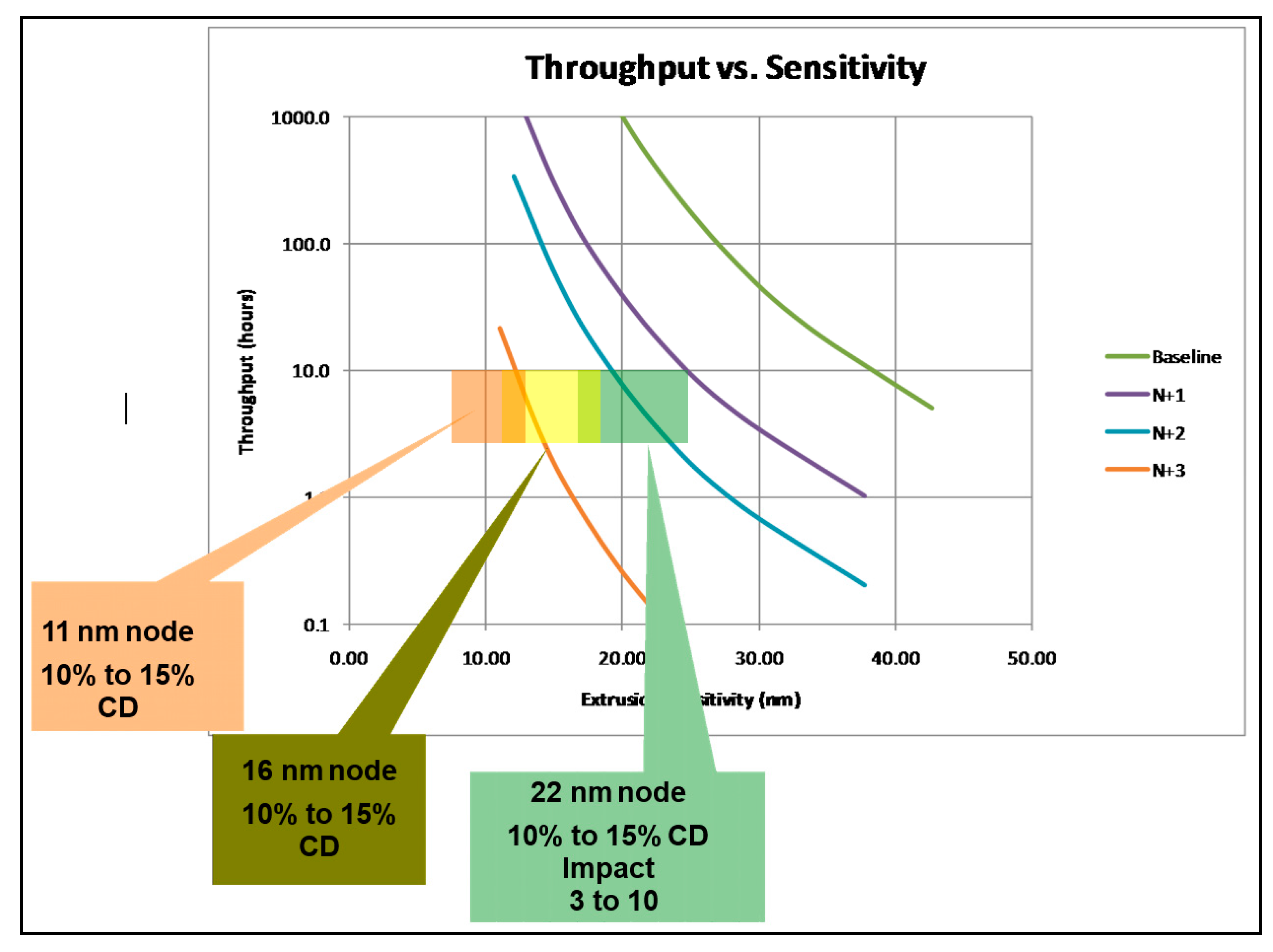

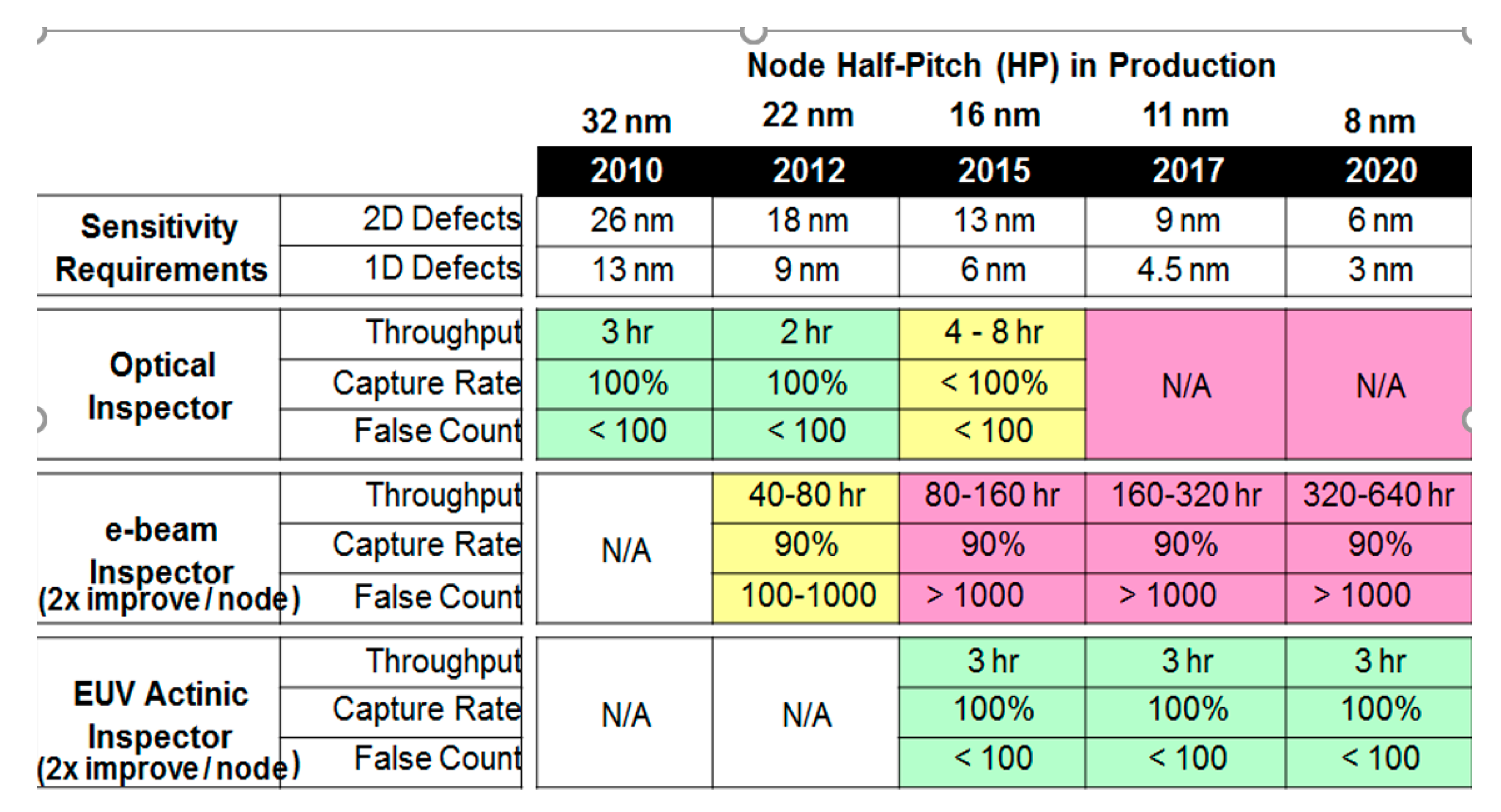

2.4. Understanding on How E-Beam Inspection will Break the Barrier from R&D/Low Volume Production to High Volume Production

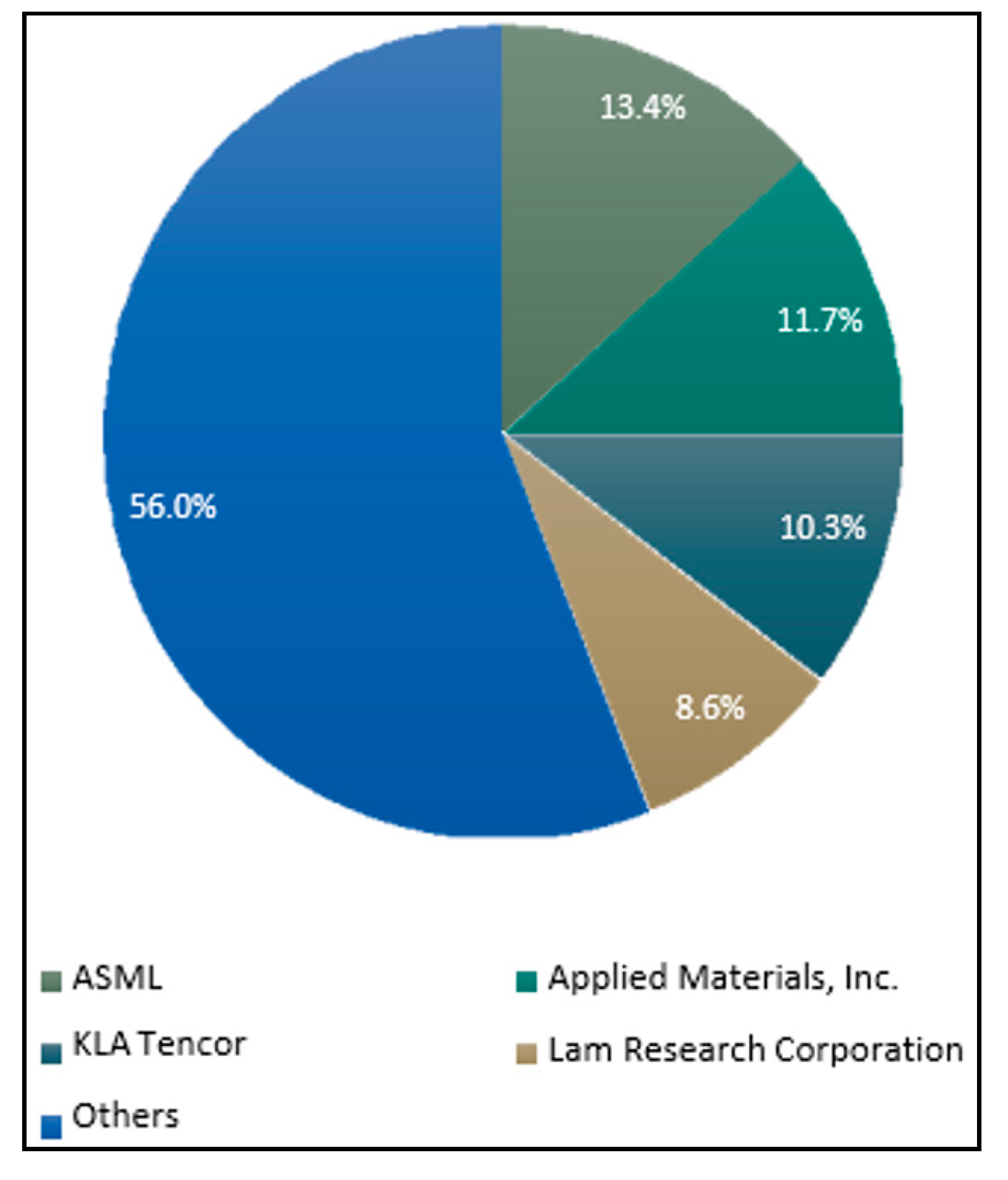

2.5. Study of Leading Commercial Optical and E-Beam Products

- KLA-Tencor eS805TM Electron-Beam Inspection System launch in 2013. However, no known new development has been published on this.

- HERMES–MicroVision Inc. (HMI, Hsinchu, Taiwan) eScan® 320xp and eScan® 500 E-beam inspection system.

- eScan® is capable of generating defectivity baseline for both physical and electrical defects. eScan®’s main applications include: front-end of line at Salicide, high-k metal gate (HKMG) and FinFET; mid-end of line at contacts, and back-end of line at via and copper chemical mechanical polishing (CMP) [33].

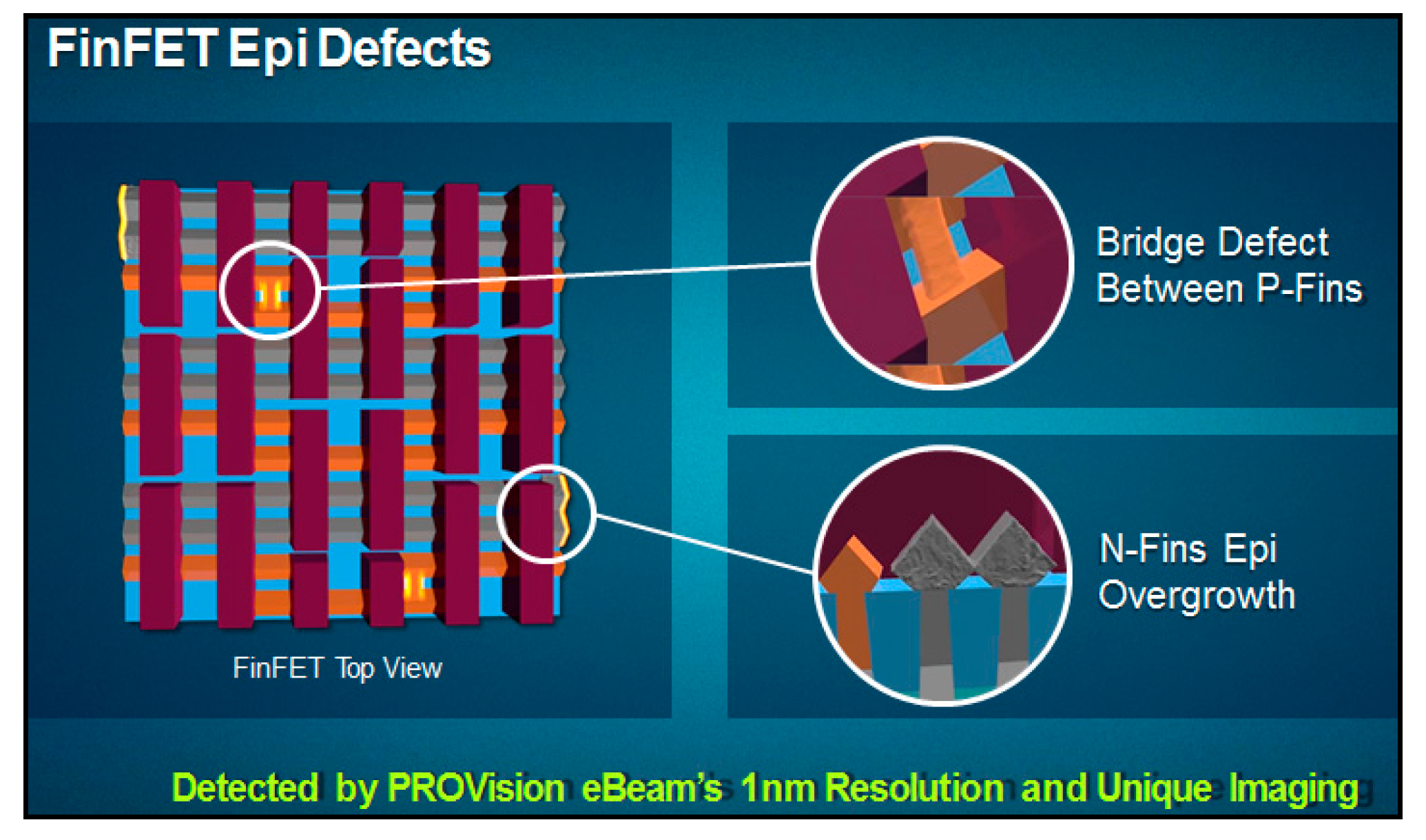

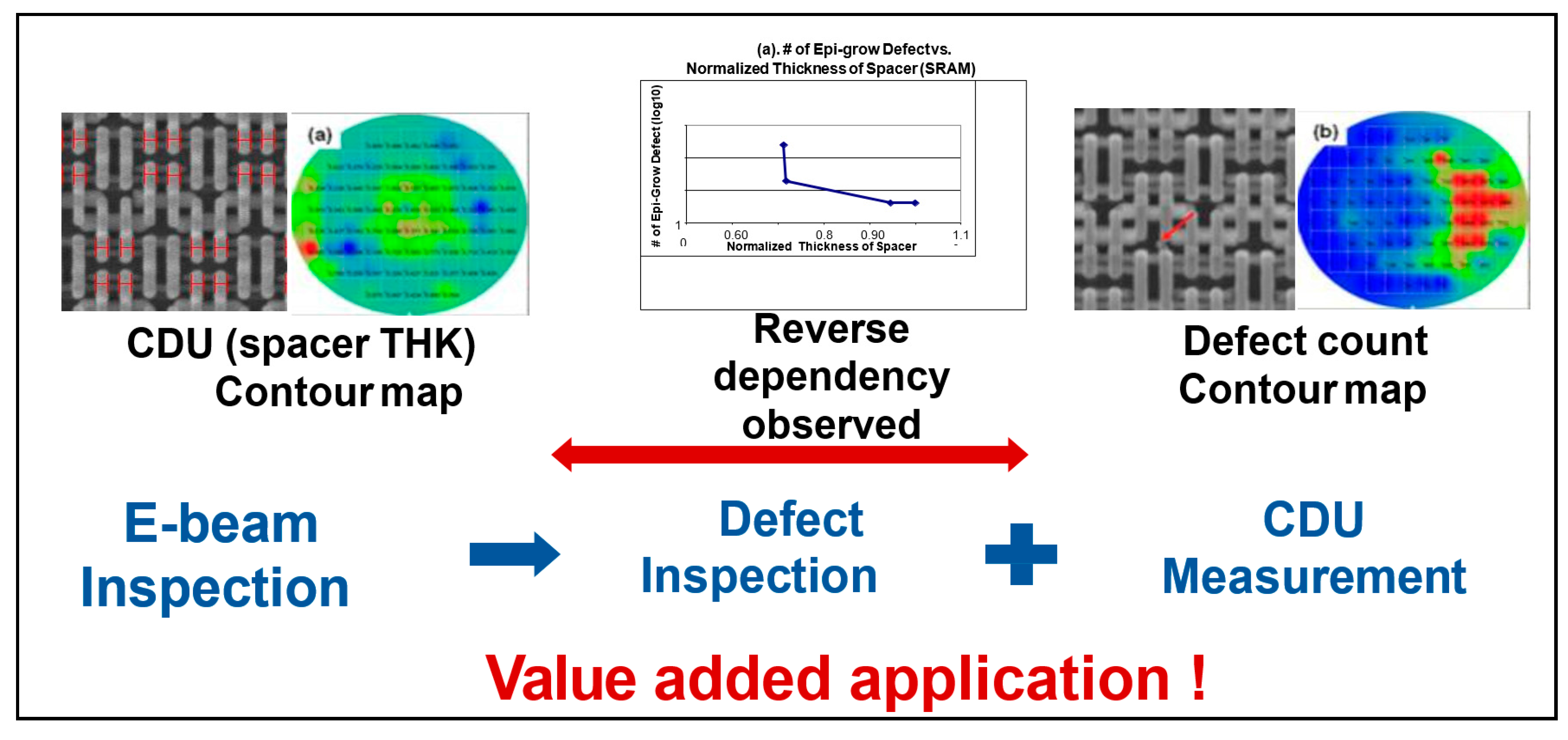

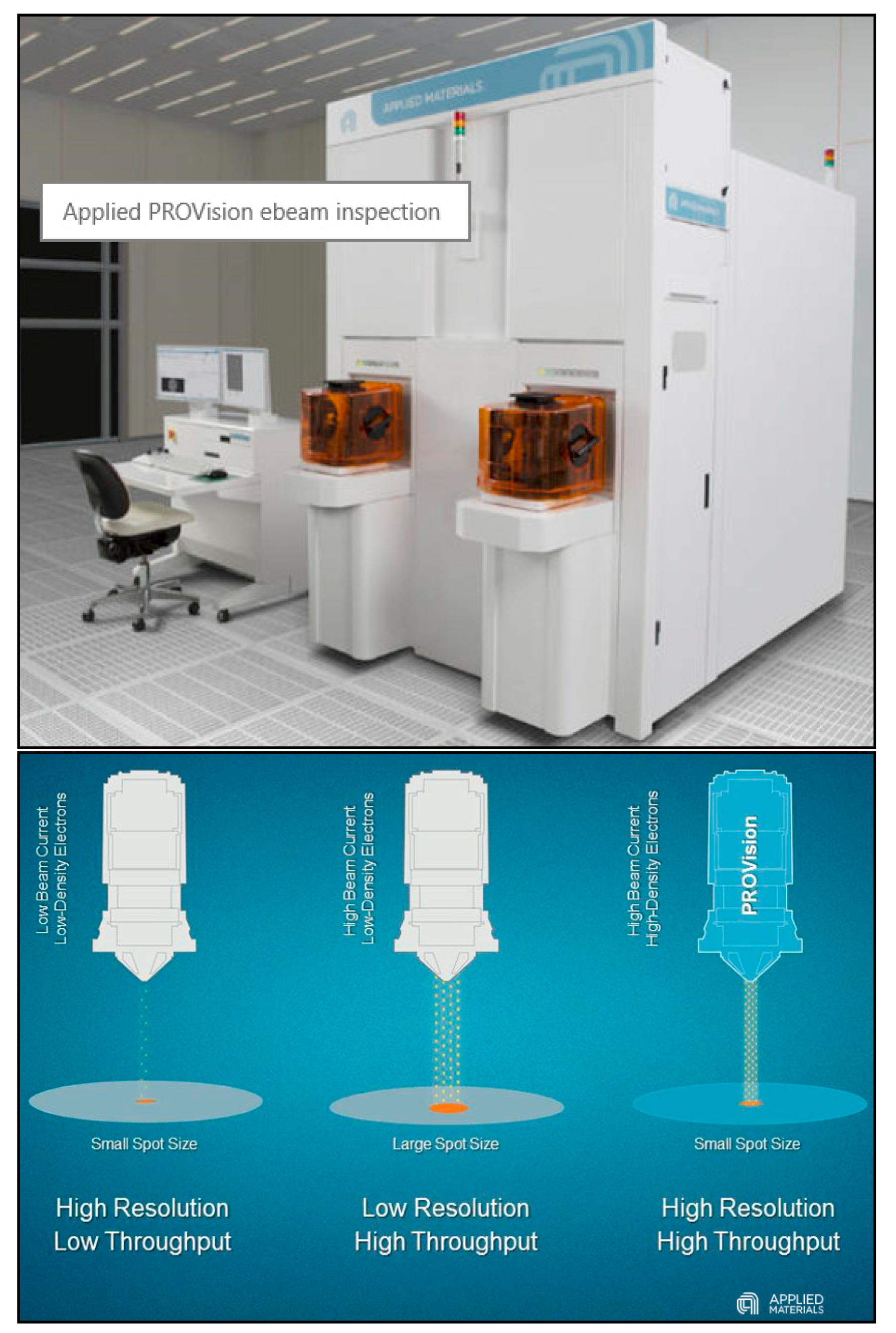

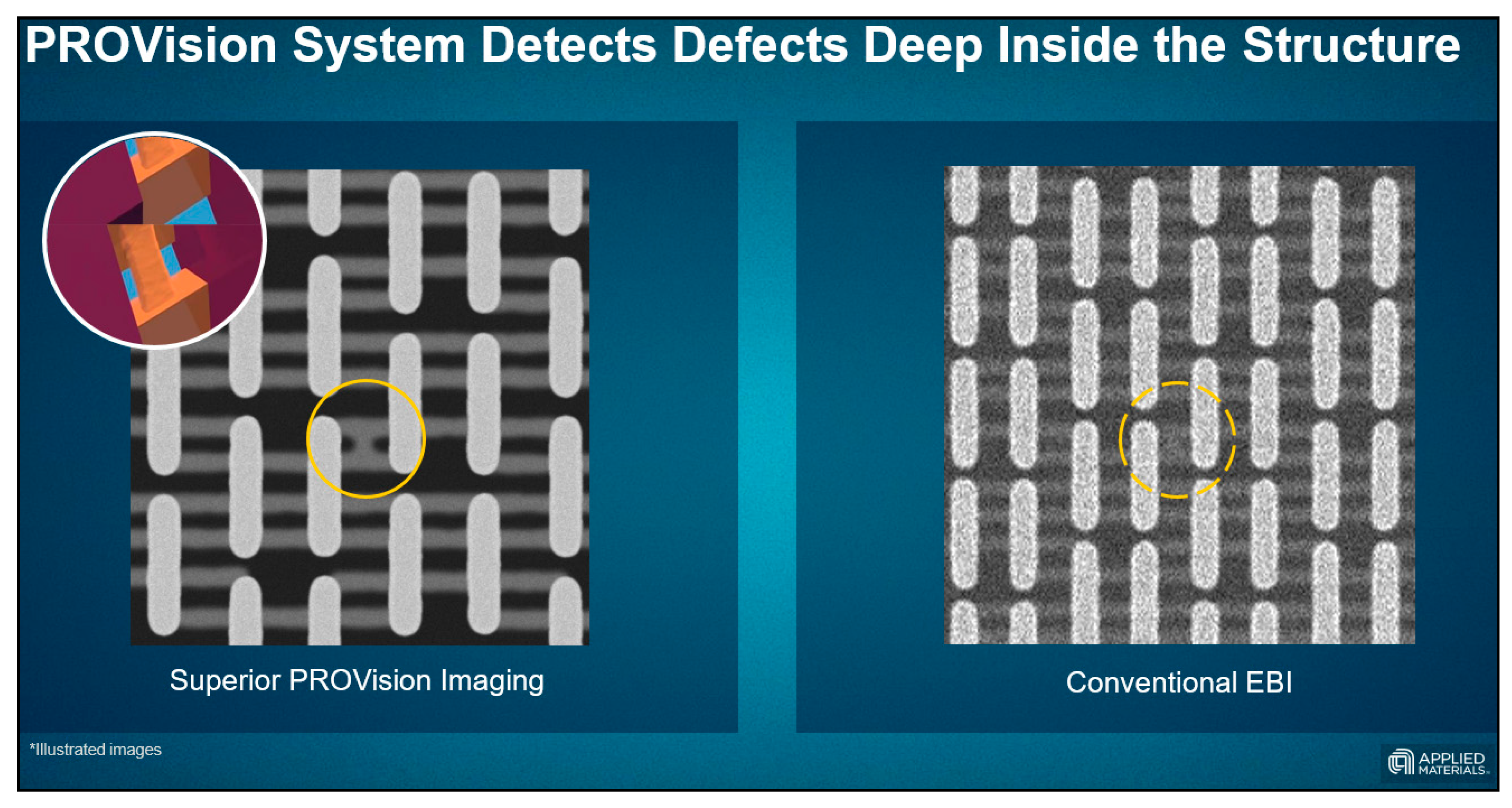

- Applied Materials ProVision Tool.The Applied PROVisionTM system (see Figure 22) is the industry’s most advanced e-beam inspection tool, incorporating innovations based on more than 20 years of leading expertise in e-beam technology for review and metrology [34]. It is the only e-beam hotspot inspection tool offering down to 1 nm resolution, allowing customers to detect the most challenging “killer” defects that other technologies cannot find, and to monitor process marginality to rapidly resolve ramp issues and achieve higher yields. Provision allows capturing defects they could not see before (Figure 23). The system can detect, for example, epi-overgrowth in FinFETs. “While the epi overgrowth is clearly visible on the PROVision, it’s almost impossible to see in conventional EBI. Without the resolution and the special imaging, it is very difficult to catch that.

- KLA Tencor

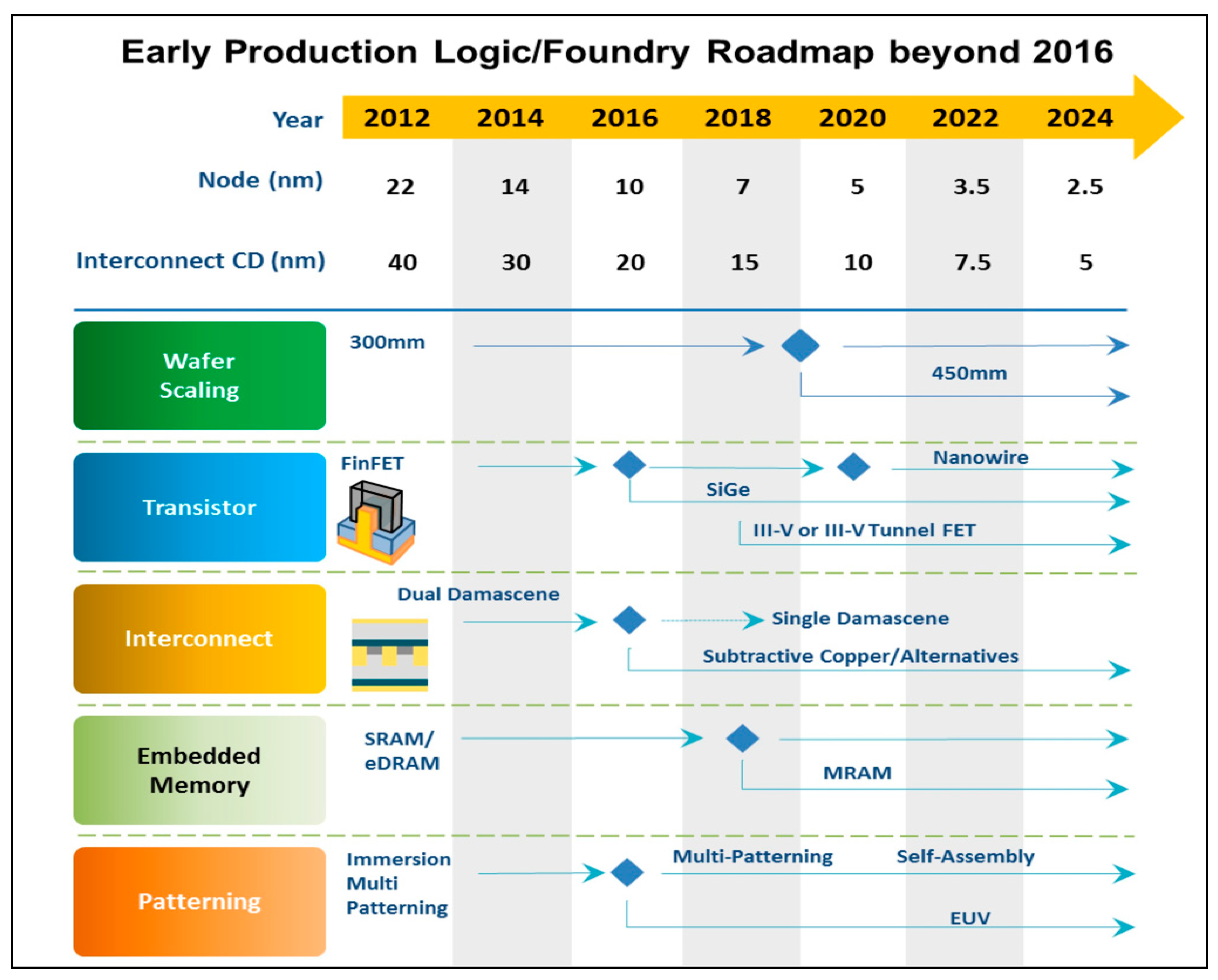

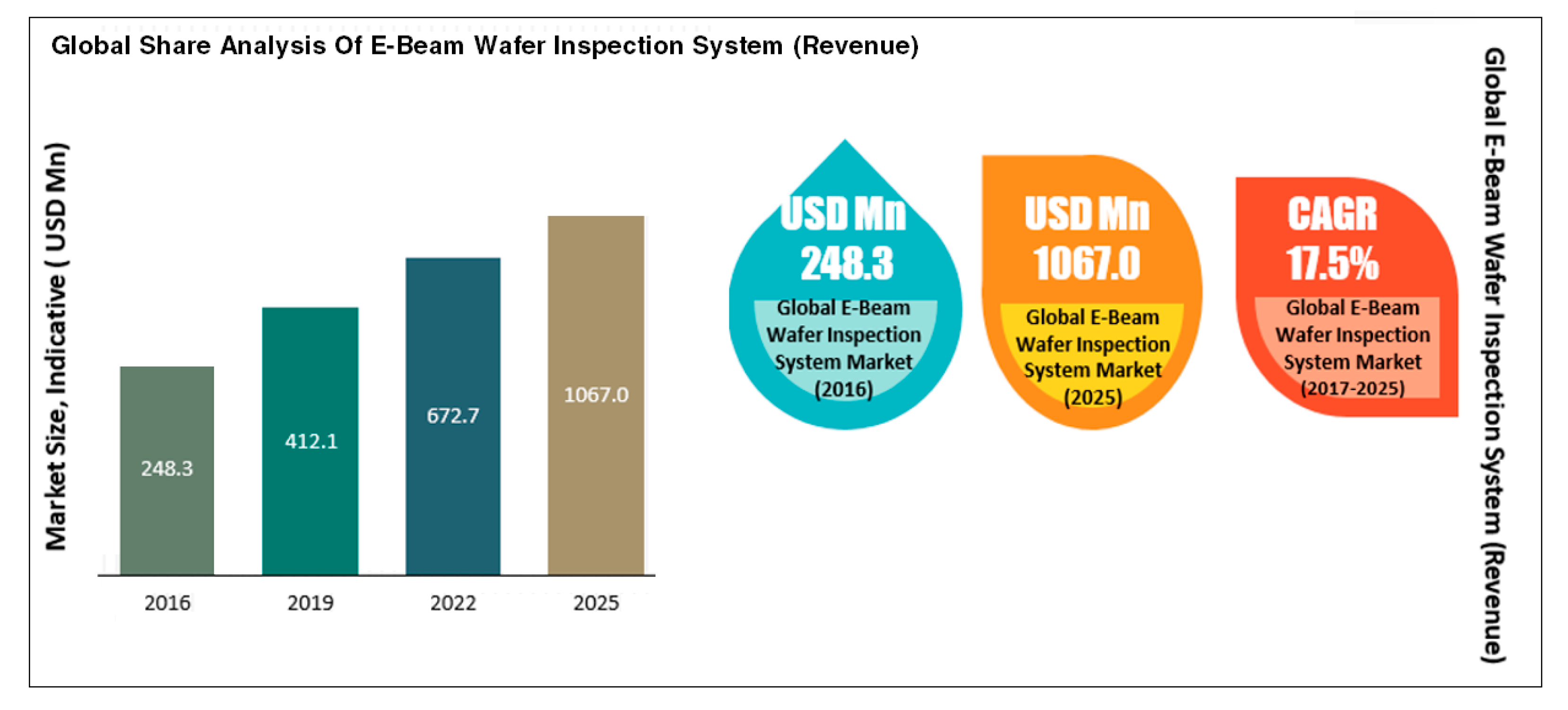

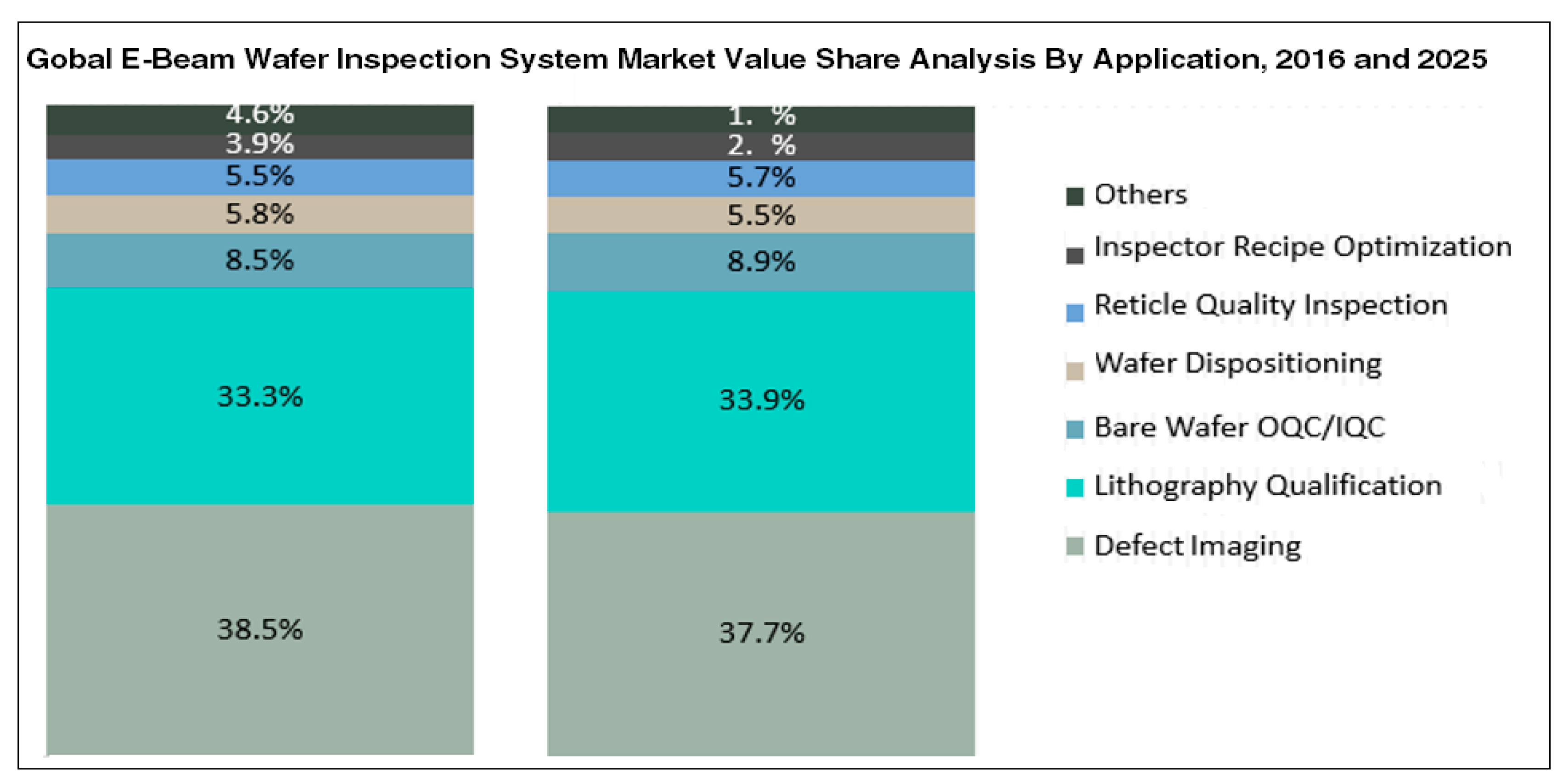

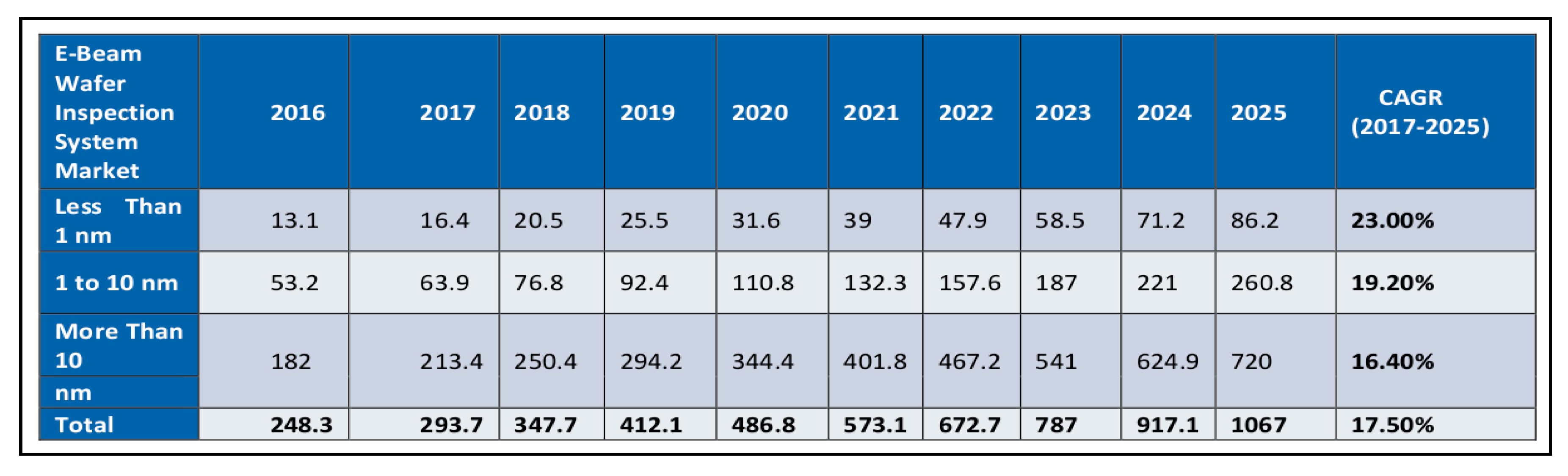

2.6. Roadmap of Semiconductor Inspection Technology Down to 1 nm

2.7. Evolution of Less than 1 nm Node Inspection System

2.7.1. Current State of Technology

2.7.2. Challenges Faced

2.7.3. Upcoming Technologies

2.7.4. Key Points

3. Discussion

4. Conclusions

Acknowledgments

Author Contributions

Conflicts of Interest

Abbreviations and Acronyms

| ACI | After Clean Inspection |

| BBP | Brightfield Broad-band Plasma |

| BEOL | Back End of Line |

| C2C | Cell to Cell |

| CAD | Computer Aided Design |

| CD | Critical Dimension |

| CD SEM | Critical Dimension Scanning Electron Microscopes |

| Cu-CMP | Copper Chemical Mechanical Polishing |

| D2D | Die to Die |

| DBA | Design Based Alignment |

| DBI | Design Based Inspection |

| DOI | Defect of Interest |

| DRAM | Dynamic Random Access Memory |

| EBAC | Electron Beam Absorbed Current |

| EBI | Electron Beam Inspection |

| FOV | Field of View |

| GOX | Gate Oxide |

| HKMG | High-k (k-dielectric) Metal Gate |

| IC | Integrated Chip |

| LIT | Lock-in Thermography |

| PDC | Process Diagnostic Control |

| PEM | Photo Emission Microscopy |

| POI | Pattern of Interest |

| SEM | Scanning Electron Microscopes |

| SOM | Self-Organizing Map |

| SR-DUV | Super Resolution Deep Ultraviolet |

| SE | Secondary electrons |

| TSV | Through-Silicon Via |

| VC | Voltage Contrast |

| WCMP | Tungsten Chemical Mechanical Polishing |

References

- Raplee, J.; Plothowski, A.; Kirka, M.; Dinwiddie, R.; Okello, A.; Dehoff, R.; Rabu, S. Themographic microstructure monitoring in electron beam additive manufacturing. Sci. Rep. 2017, 7, 43554. [Google Scholar] [CrossRef] [PubMed]

- Childres, I.; Foxe, M.; Jovanovic, I.; Chen, Y. Effect of energetic electron irradiation on graphene and graphene field-effect transistors. Proc. SPIE 2011, 8031, 803122-1–803122-8. [Google Scholar] [CrossRef]

- Van Himbergen, H.; Nijikerk, M.; de Jager, P. High throughput defect detection with multiple parallel electron beams. J. Vac. Sci. Technol. B 2007, 25, 2521. [Google Scholar] [CrossRef]

- Cai, N.; Zeng, X.; Wu, K.; Song, H.; Gao, W.; Tian, Q.; Lei, C.; Gao, K.; Wang, L.; Zhao, Y. Automated Klarf-Based Defect Inspection by Electron-Beam Inspection Tool: A Novel Approach to Inline Monitoring and/or Process Change Validation. Proc. SPIE 2016, 9778. [Google Scholar] [CrossRef]

- Propabality of Defect Detection of Posiva’s Electron Beam Weld. Available online: http://www.posiva.fi/files/3527/WR_2013-70.pdf (accessed on 20 September 2017).

- Patterson, O.; Lee, J.; Let, C.; Salvado, D. E-beam inspection for detection of sub-design rule physical defects. In Proceedings of the Annual SEMI Advanced Semiconductor Manufacturing Conference, Saratoga Springs, NY, USA, 15–17 May 2012. [Google Scholar] [CrossRef]

- Lin, P.; Cai, N.; Eah, S.; Patteron, O.; Gao, W. E-beam mechanics and net connectivity for interlayer short detection: DI: Defect inspection and reduction. In Proceedings of the Annual SEMI Advanced Semiconductor Manufacturing Conference, Saratoga Springs, NY, USA, 15–18 May 2017; pp. 256–261. [Google Scholar]

- Hafer, R.; Patterson, O.; Hakn, R.; Xiao, H. Full-wafer voltage contrast inspection for detection of BEOL defects. In Proceedings of the Annual SEMI Advanced Semiconductor Manufacturing Conference, Saratoga Springs, NY, USA, 15–17 May 2017; pp. 461–468. [Google Scholar]

- Liao, H.; Luoh, T.; Yang, L.; Yang, T.; Chen, K.; Lu, C.; Lin, D.; Lv, R.; Hsiang, C.; Hu, C. Tiny physical defects inspection by optimized EBI methodology. In Proceedings of the e-Manufacturing & Design Collaboration Symposium, Hsinchu, Taiwan, 12 September 2014; pp. 1–3. [Google Scholar]

- Zhou, X.; Guo, Y.; Jones, J. E-beam inspection BVC (Bright Voltage Contrast) verification for 14 nm technology: DI: Defect inspection and reduction. In Proceedings of the Annual SEMI Advanced Semiconductor Manufacturing Conference, Saratoga Springs, NY, USA, 15–18 May 2017; pp. 234–239. [Google Scholar]

- Speeding up E-Beam Inspection. Available online: http://semiengineering.com/speeding-up-e-beam-inspection/ (accessed on 20 August 2017).

- Cooray, A. Extragalactic background light measurements and applications. R. Soc. Open Sci. 2016, 3, 150555. [Google Scholar] [CrossRef] [PubMed]

- Prescop, T.; Tran, C.; Monahan, K.; Lam, D.; Liu, E. Multiple column high-throughput e-beam inspection (EBI). Proc. SPIE 2012, 8324. [Google Scholar] [CrossRef]

- Kaestner, M.; Hofer, M.; Rangelow, I. Mix & match electron beam & scanning probe lithography for high throughput sub-10 nm lithography. Proc. SPIE 2013, 8680. [Google Scholar] [CrossRef]

- Bunday, B.; Mukhtar, M.; Quoi, K.; Thiel, B.; Malloy, M. Simulating massively parallel electron beam inspection for sub-20 nm defects. Proc. SPIE 2015, 9424. [Google Scholar] [CrossRef]

- Xiao, H.; Ma, L.; Wang, F.; Zhao, Y.; Jau, J.; Selinidis, K.; Thompson, E.; Sreenivasan, S.; Resnick, D. Inspection of 32 nm imprinted patterns with an advanced E-Beam inspection system. Proc. SPIE 2009, 7488. [Google Scholar] [CrossRef]

- Hayashi, H.; Fukunaga, Y.; Yamasaki, M.; Nagai, T.; Yamazaki, Y. Development of voltage contrast defect inspection technique for line monitoring 300 mm ULSI hp90 logic contact layer. Proc. SPIE 2005, 5752, 997–1008. [Google Scholar]

- Adler, D.; McCord, M.; Vaez-Iravani, M.; Han, L.; Bertsche, K. High-Speed Electron Beam Inspection. U.S. Patent US7315022 B1, 6 January 2008. [Google Scholar]

- Kemen, T.; Malloy, M.; Thiel, B.; Mikula, W.; Denk, W.; Dellemann, G.; Zeidler, D. Further advancing the throughput of a multi-beam SEM. Proc. SPIE 2015, 9424. [Google Scholar] [CrossRef]

- Applied Materials intros High res E-Beam Inspection System. Available online: http://semimd.com/blog/2016/07/11/applied-materials-intros-high-res-e-beam-inspection-system/ (accessed on 22 August 2017).

- E-Beam vs. Optical Inspection. Available online: https://semiengineering.com/e-beam-vs-optical-inspection/ (accessed on 26 August 2017).

- Wafer Defect Inspection System. Available online: http://www.hitachi-hightech.com/global/products/device/semiconductor/inspection.html (accessed on 10 September 2017).

- Frosien, J. Charged Particle Beam Device and Method for Inspecting and/or Imaging a Sample. U.S. Patent 9601303, 21 March 2017. [Google Scholar]

- Mankos, D.; Hess, C.; Ciplickas, D. E-beam Inspection Apparatus and Method of Using the same on Various Integrated Circuit Chips. U.S. Patent 9496119, 15 November 2016. [Google Scholar]

- Luoh, T.; Yang, L.; Yang, H.; Chen, K. Electron Beam Inspection Optimization. U.S. Patent 9116108, 25 August 2015. [Google Scholar]

- Why EUV Is so Difficult. Available online: https://semiengineering.com/why-euv-is-so-difficult/ (accessed on 9 August 2017).

- Wu, K.; Gao, L.; Chen, H.; Shortt, D. Detecting Defects on a Wafer Using Defect-Specific and Multi-Channel Information. U.S. Patent 9552636, 24 January 2017. [Google Scholar]

- Hafer, R.; Patterson, O.; Hahn, R.; Xiao, H. Full-wafer electron beam inspection for detection of BEOL defects. In Proceedings of the 25th SEMI Advanced Semiconductor Manufacturing Conference (ASMC), Saratoga Springs, NY, USA, 19–21 May 2014. [Google Scholar]

- Beyersdorfer, J.; Altman, F.; Schrank, F. Enhanced Failure Analysis on Open TSV Interconnects. In Proceedings of the International Symposium for Testing and Failure Analysis American Society for Metals, Phoenix, AZ, USA, 11–15 November 2012. [Google Scholar]

- Shen, J.; Chen, P.; Su, L.; Shi, T.; Tang, Z.; Liao, G. X-ray inspection of TSV defects with self-organizing map network and Otsu algorithm. Microelectron. Reliab. 2016, 67, 129–134. [Google Scholar] [CrossRef]

- Holcman, I. Joint assessment of novel multi column E-beam inspection system. In In Proceedings of the 2013 EMICON Europa Workshop on Equipment Assessment & Equipment Performance Improvements, Berlin, Germany, 8–10 October 2013. [Google Scholar]

- Eberle, A.; Mikula, S.; Schalek, R.; Lichtman, J.; Knothe, M.; Zeidler, D. High-resolution, high-throughput imaging with a multibeam scanning electron microscope. J. Microsc. 2015, 259, 114–120. [Google Scholar] [CrossRef] [PubMed]

- Hermes Microvision eScan Series. Available online: http://www.hermes-microvision.com/Products/ (accessed on 1 September 2017).

- Applied Materials’ Next-Generation E-Beam Inspection System Provides Industry’s Highest Resolution. Available online: http://www.appliedmaterials.com/company/news/press-releases/2016/07/applied-materials’-next-generation-e-beam-inspection-system-provides-industry’s-highest-resolution (accessed on 15 August 2017).

- Global E-Beam Wafer Inspection System Market 2017–2021. Available online: https://www.researchandmarkets.com/reports/4027530/global-e-beam-wafer-inspection-system-market-2017 (accessed on 24 August 2017).

- Schuegraf, K.; Abraham, M.; Brand, A.; Naik, M.; Thakur, R. Semiconductor logic technology innovation to achieve sub-10 nm manufacturing. IEEE J. Electron Devices Soc. 2013, 1, 66–75. [Google Scholar] [CrossRef]

| Parameters | Optical Inspection | e-Beam Inspection |

|---|---|---|

| Defects Capability | Physical defects | Smaller physical defects and electrical defects |

| Performance | Fast | Slow |

| Scan area | Large area (complete wafer) | High |

| Market share | ~86% | ~14% |

| Majorly used at | Production (in-line) | Research and Development (R&D) |

| Resolution | Medium | High |

| Parameter | Value |

|---|---|

| Typical landing energies of the multi-beam electron microscope | 1–3 keV |

| Typical pixel sizes | 4–10 nm |

| Distance between two electron beams | 12 μm |

| Future Technology | Projection e-Beam | Multiple e-Beam | Multi-Column Multi-Objective Lens | Multi-Column Single Objective Lens |

|---|---|---|---|---|

| Pros | High scan rate | With-in full die application | Easy control symmetry beam | Small volume |

| Cons | Interaction high, low SNR, low resolution | Asymmetrical control, non-uniform | Large volume | Asymmetrical control |

| Resolution | Moderate | Moderate | High | High |

| Throughput | Fastest | Faster | Fast | Faster |

| Scan Time | 16 nm | 11 nm | 8 nm |

|---|---|---|---|

| EBI (Pattern only) | 320 h (2 weeks) | 1280 h (8 weeks) | 5120 h (30 weeks) |

| Actinic (Blank and Pattern) | 3 h | 6 h | 12 h |

© 2017 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Oberai, A.; Yuan, J.-S. Smart E-Beam for Defect Identification & Analysis in the Nanoscale Technology Nodes: Technical Perspectives. Electronics 2017, 6, 87. https://doi.org/10.3390/electronics6040087

Oberai A, Yuan J-S. Smart E-Beam for Defect Identification & Analysis in the Nanoscale Technology Nodes: Technical Perspectives. Electronics. 2017; 6(4):87. https://doi.org/10.3390/electronics6040087

Chicago/Turabian StyleOberai, Ankush, and Jiann-Shiun Yuan. 2017. "Smart E-Beam for Defect Identification & Analysis in the Nanoscale Technology Nodes: Technical Perspectives" Electronics 6, no. 4: 87. https://doi.org/10.3390/electronics6040087