Power Efficient Fully Differential Bulk Driven OTA for Portable Biomedical Application

Abstract

:1. Introduction

2. Materials and Methods

2.1. Linearization Methods

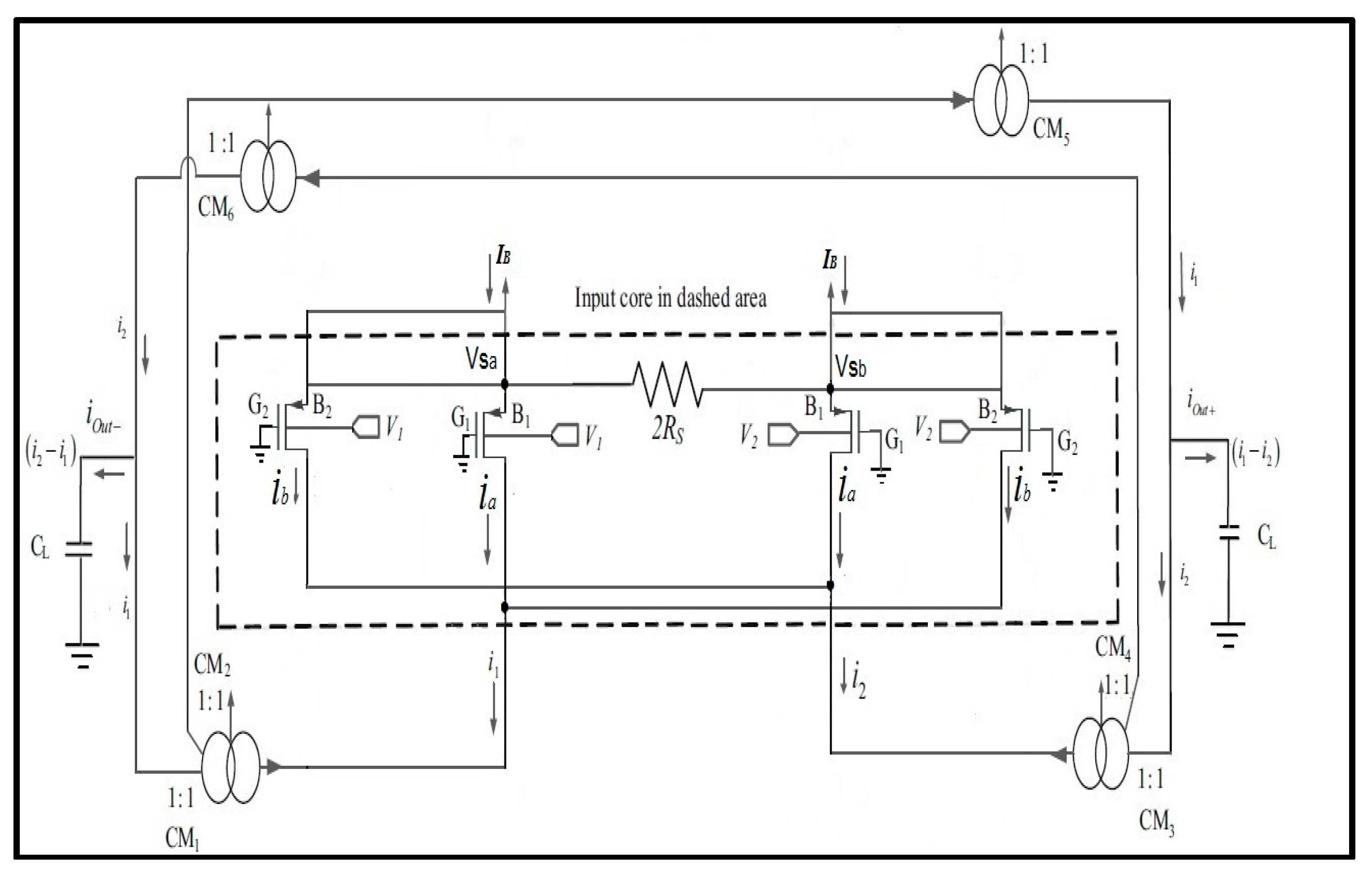

2.1.1. Source Degeneration with Cross Coupled Differential Pair

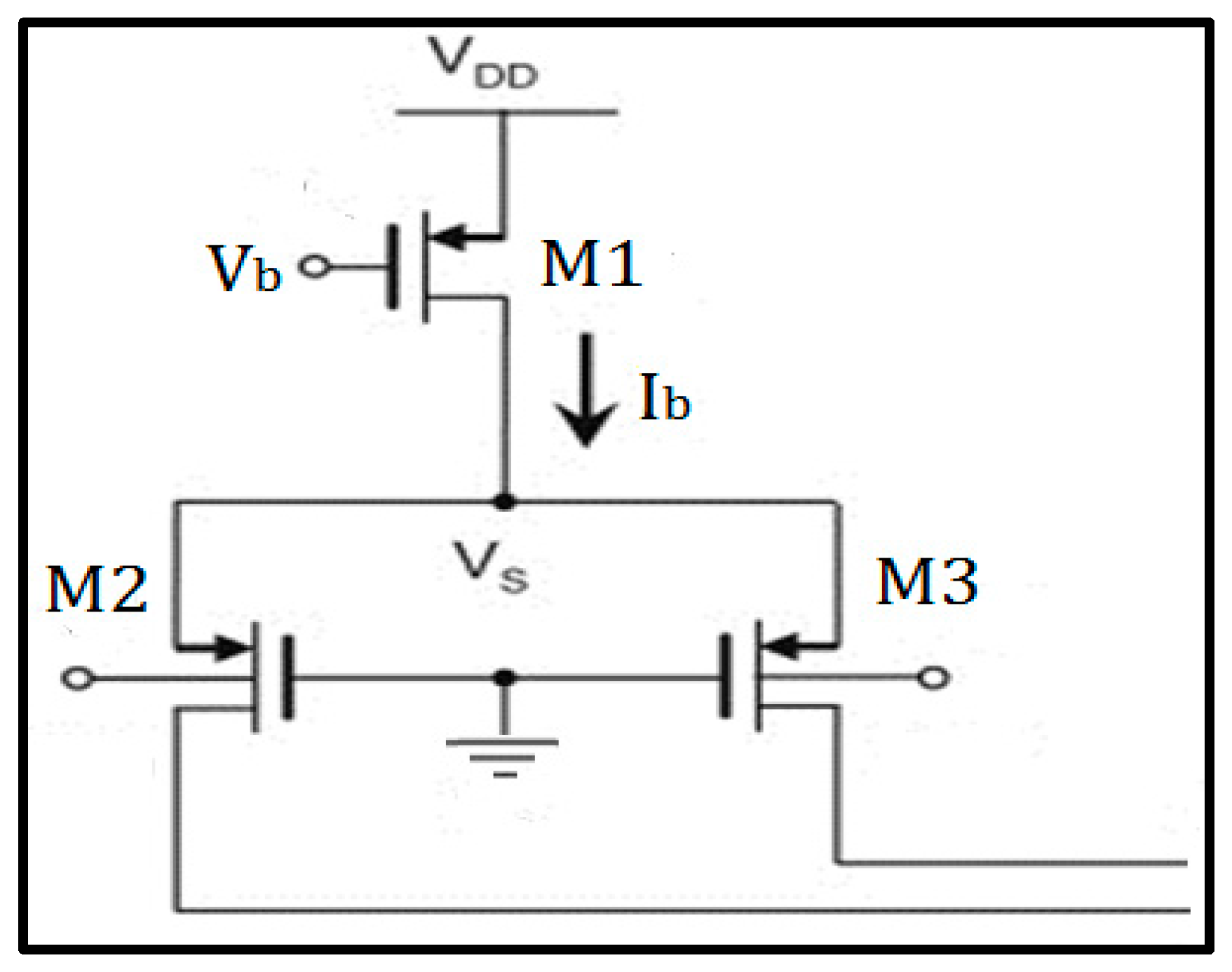

2.1.2. Bulk Driven Transistors

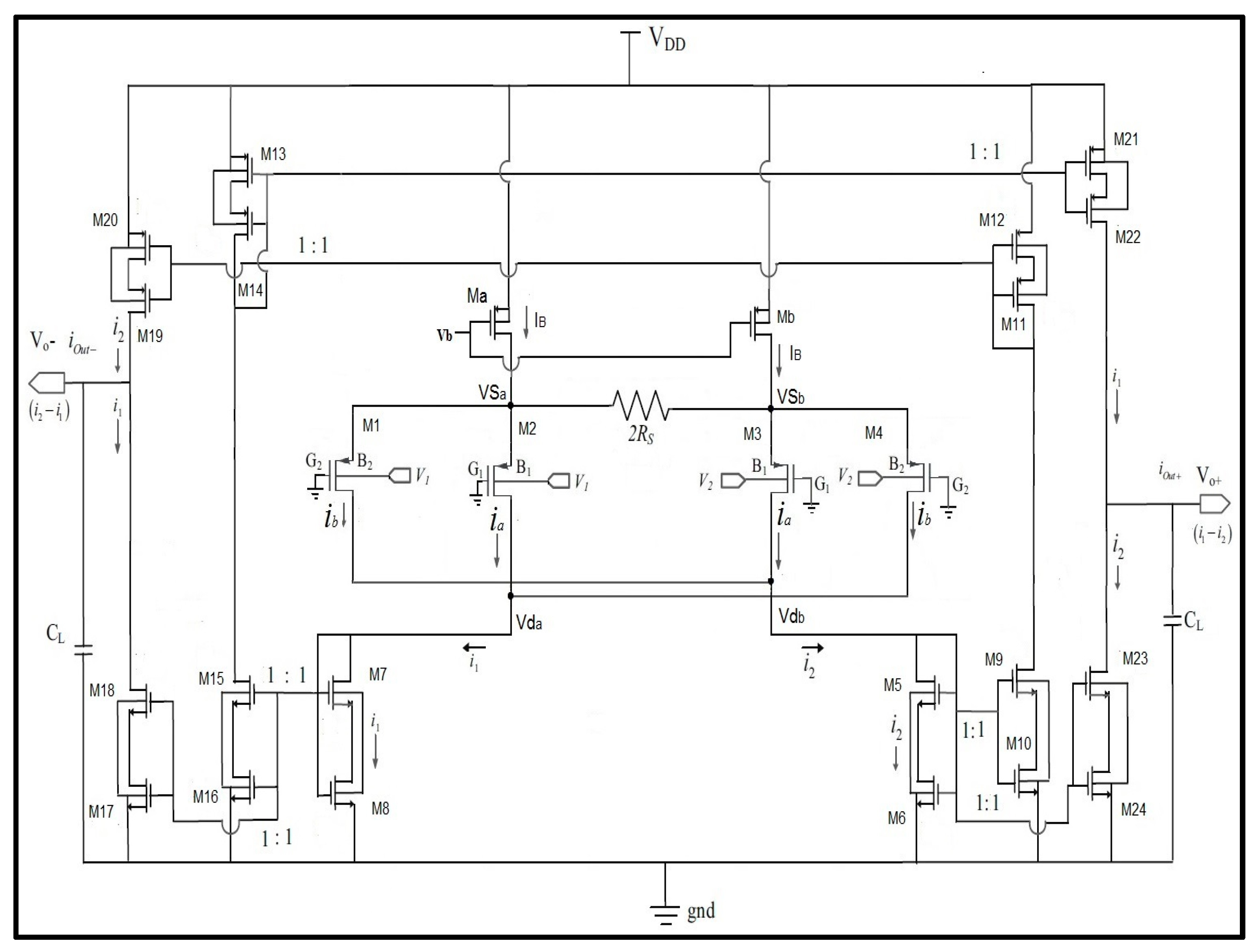

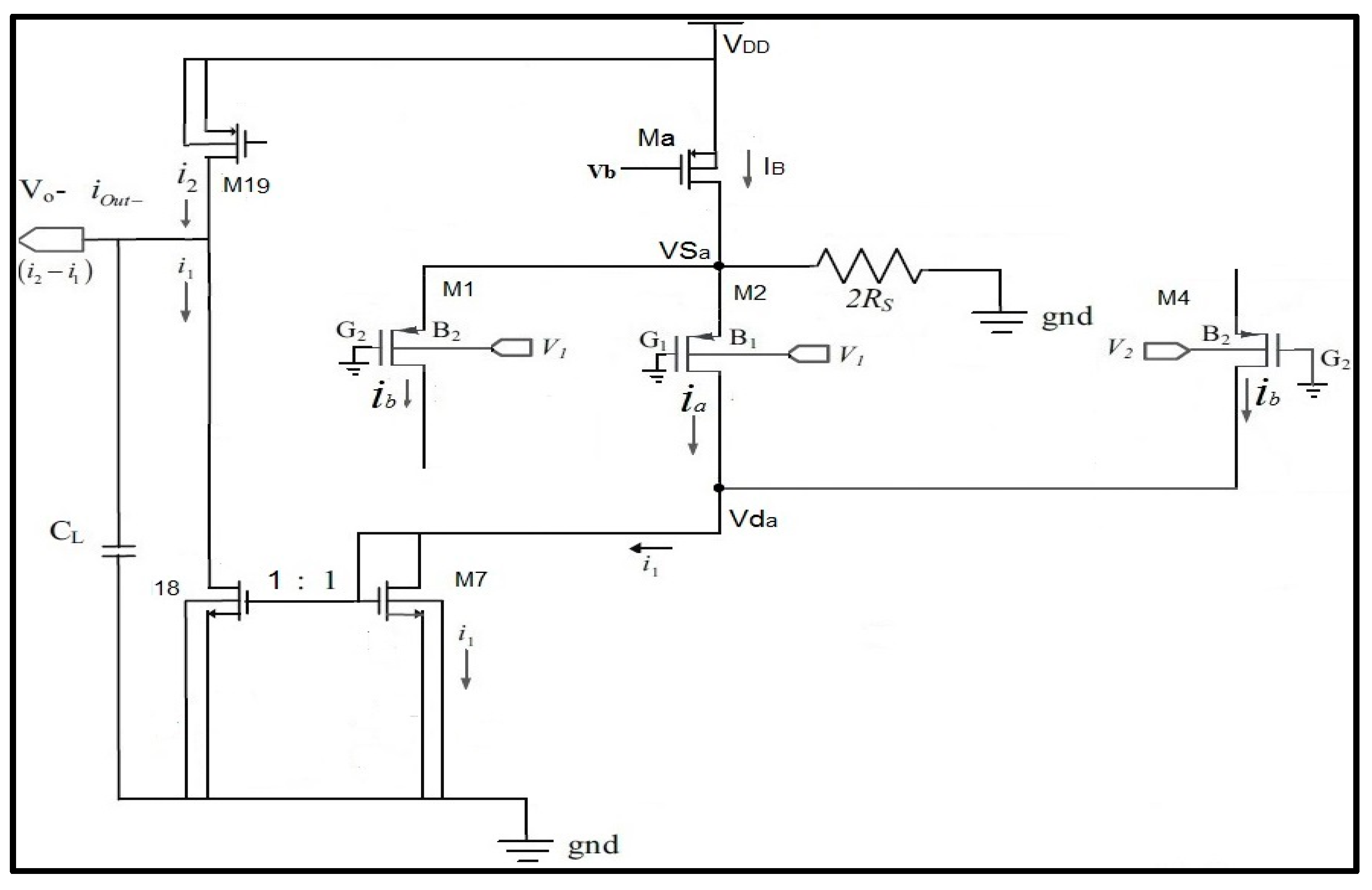

2.2. Proposed OTA

3. Performance Equation

3.1. Subthreshold Equation

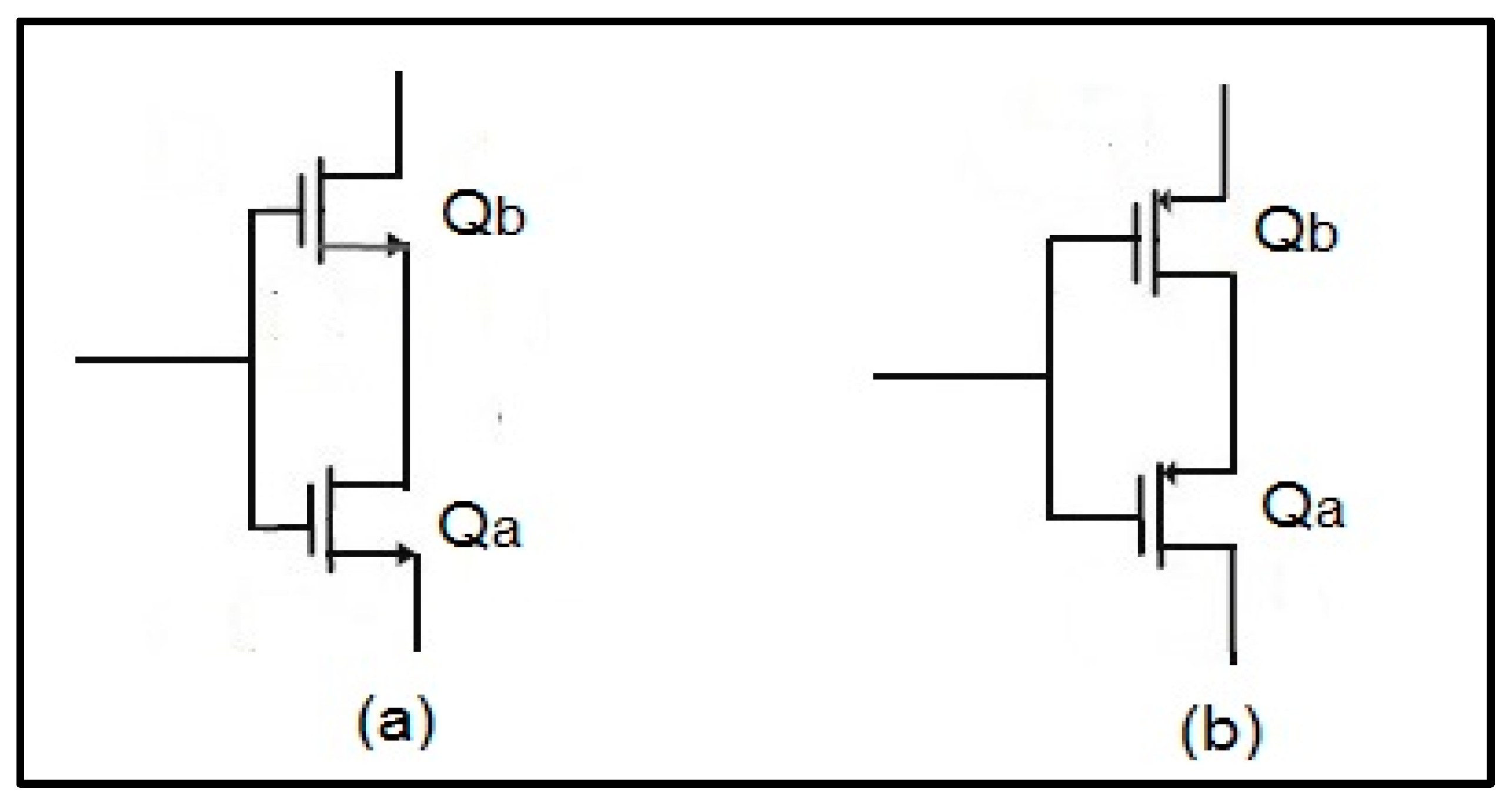

3.2. Composite MOS

3.2.1. Sizing of Composite Transistors

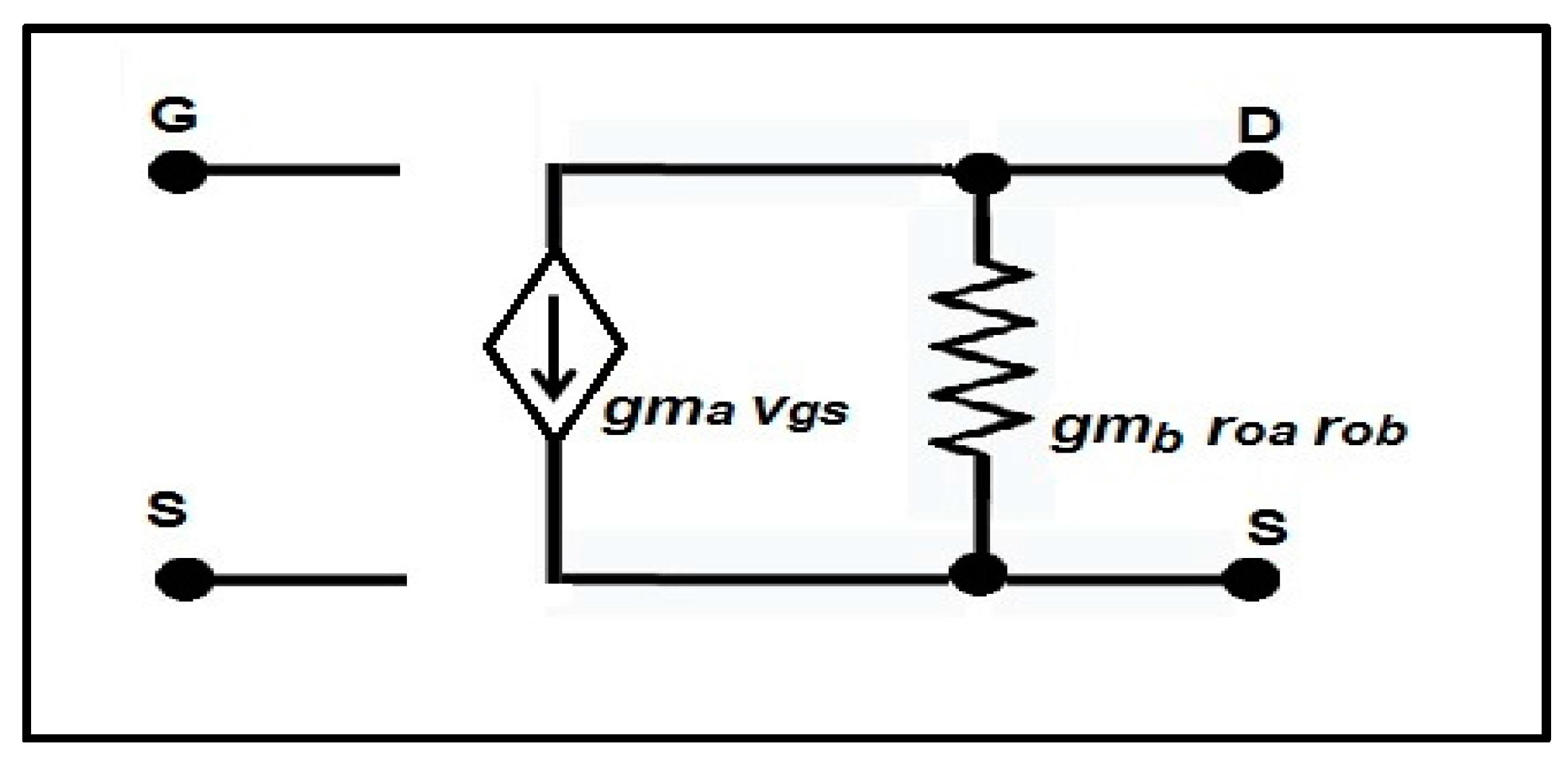

3.2.2. Small Signal Model of Composite Transistors

3.2.3. Noise of Composite MOS

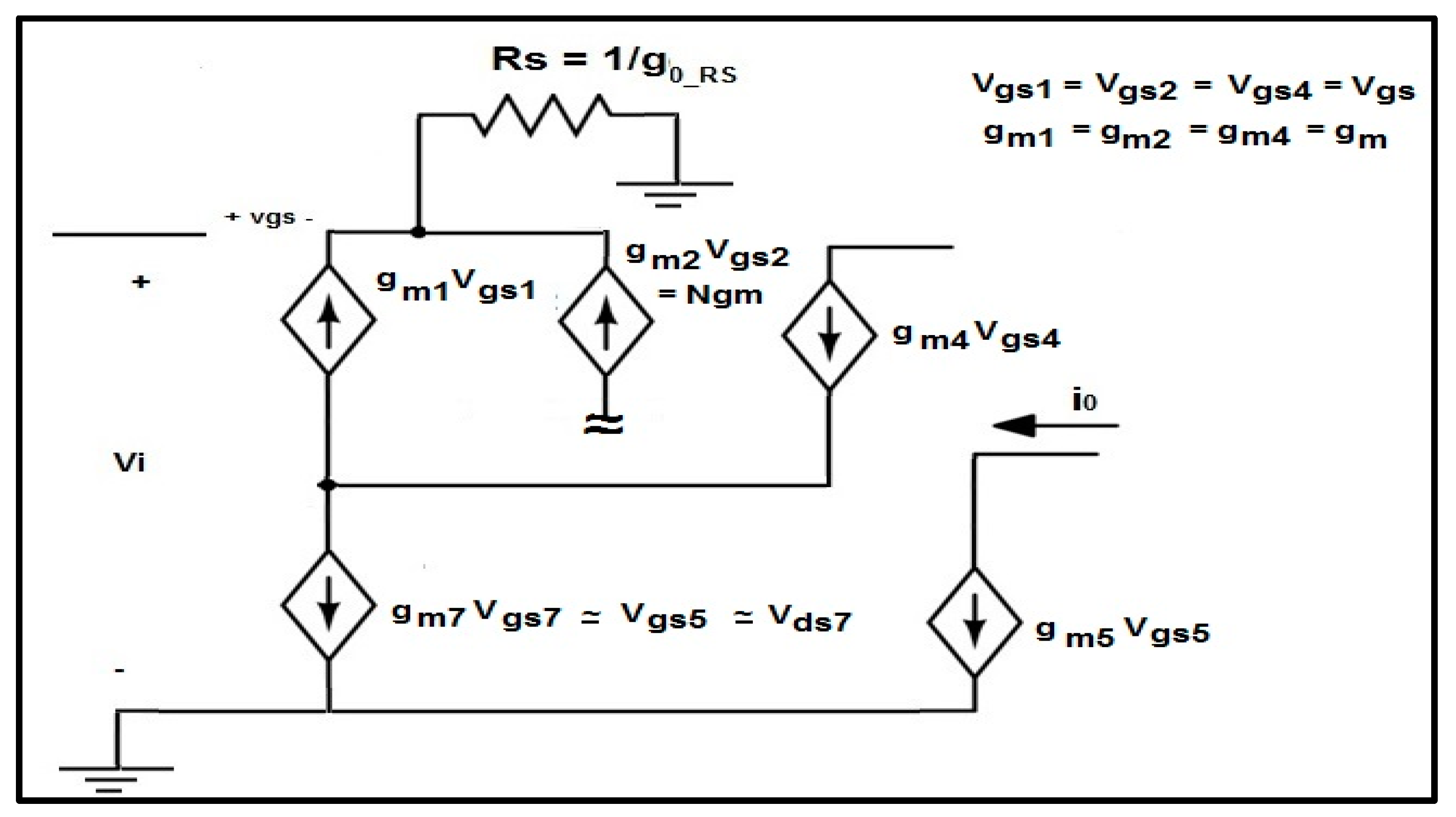

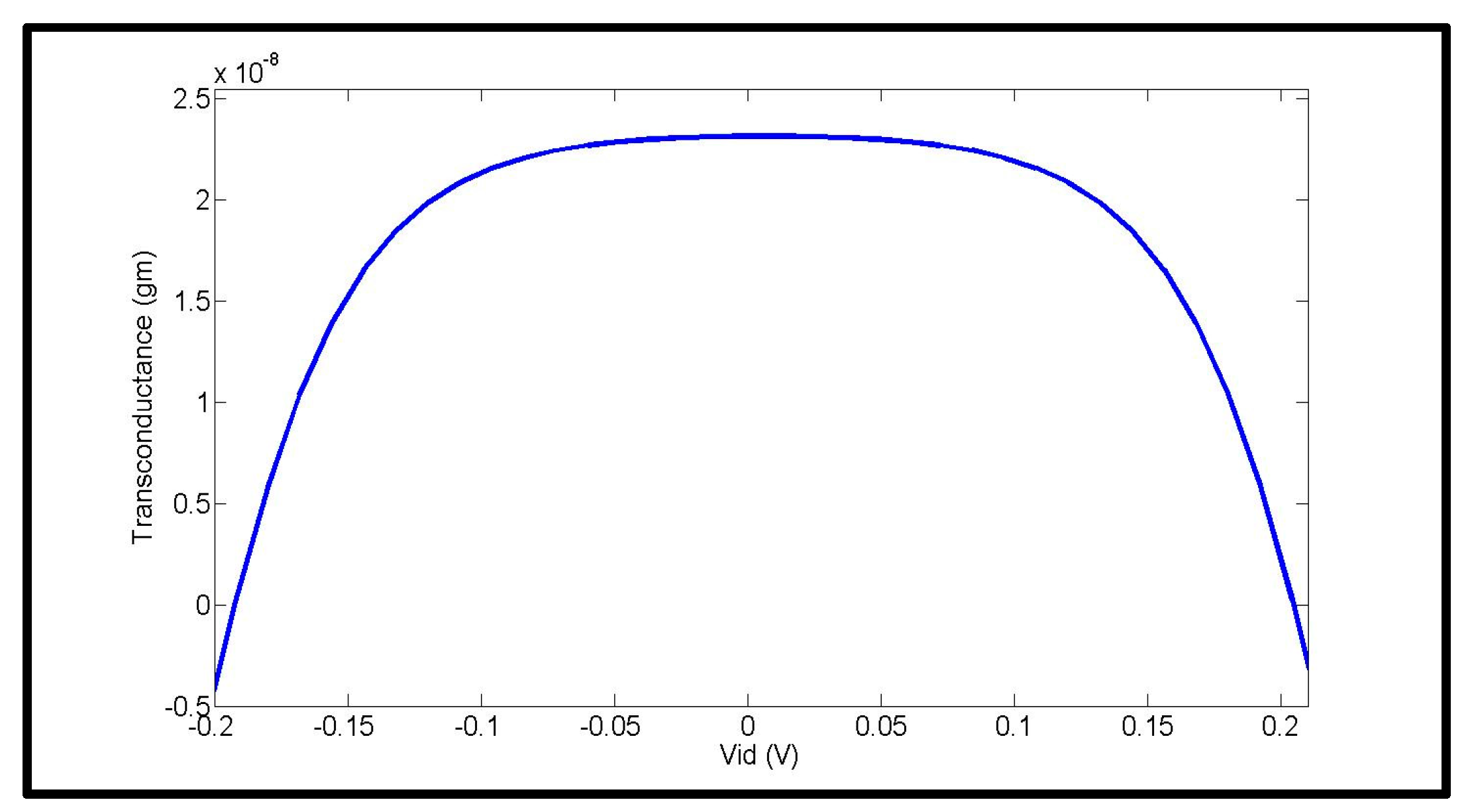

3.3. Transconductance of OTA

4. Simulation Results

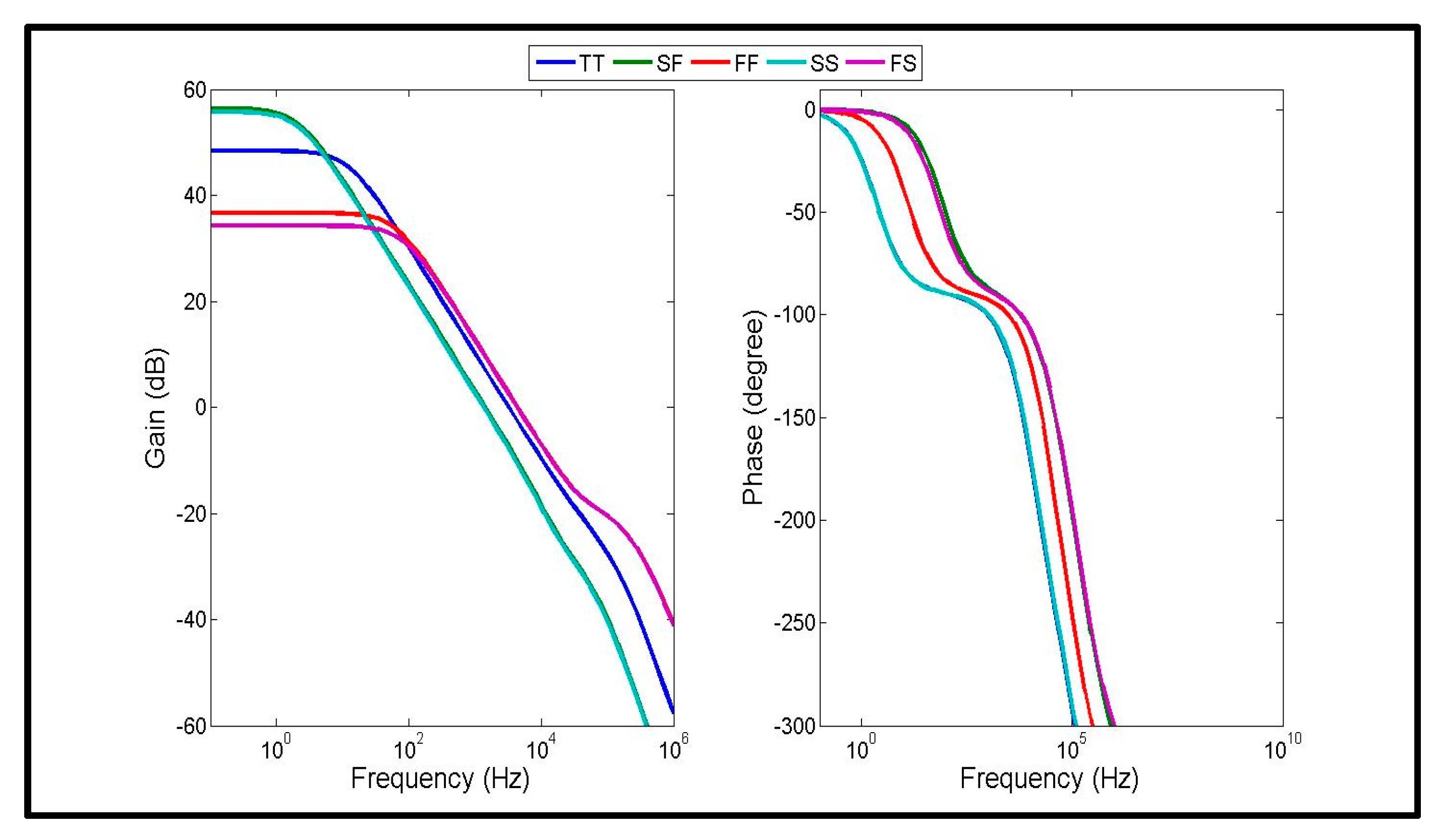

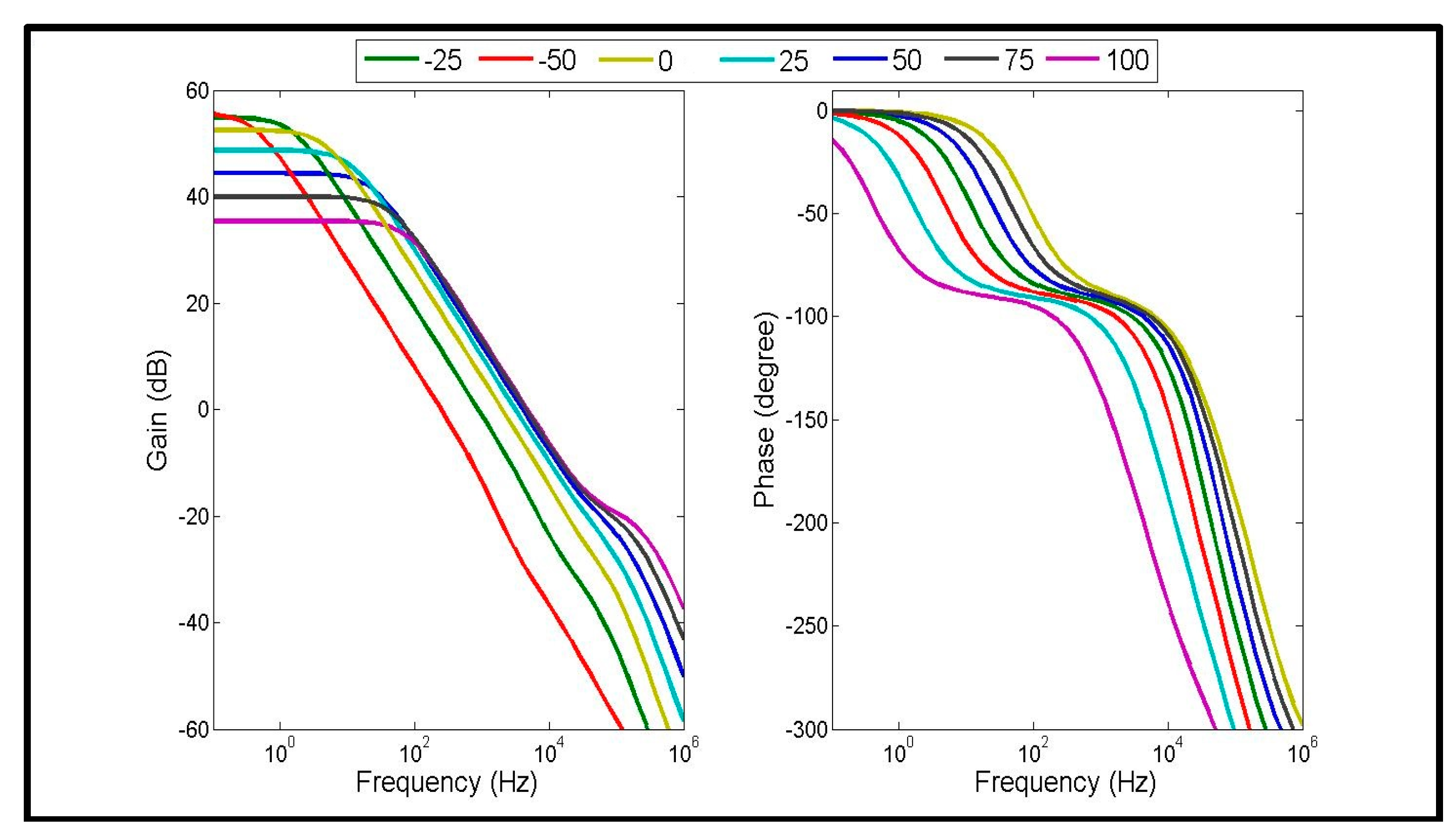

4.1. AC Response

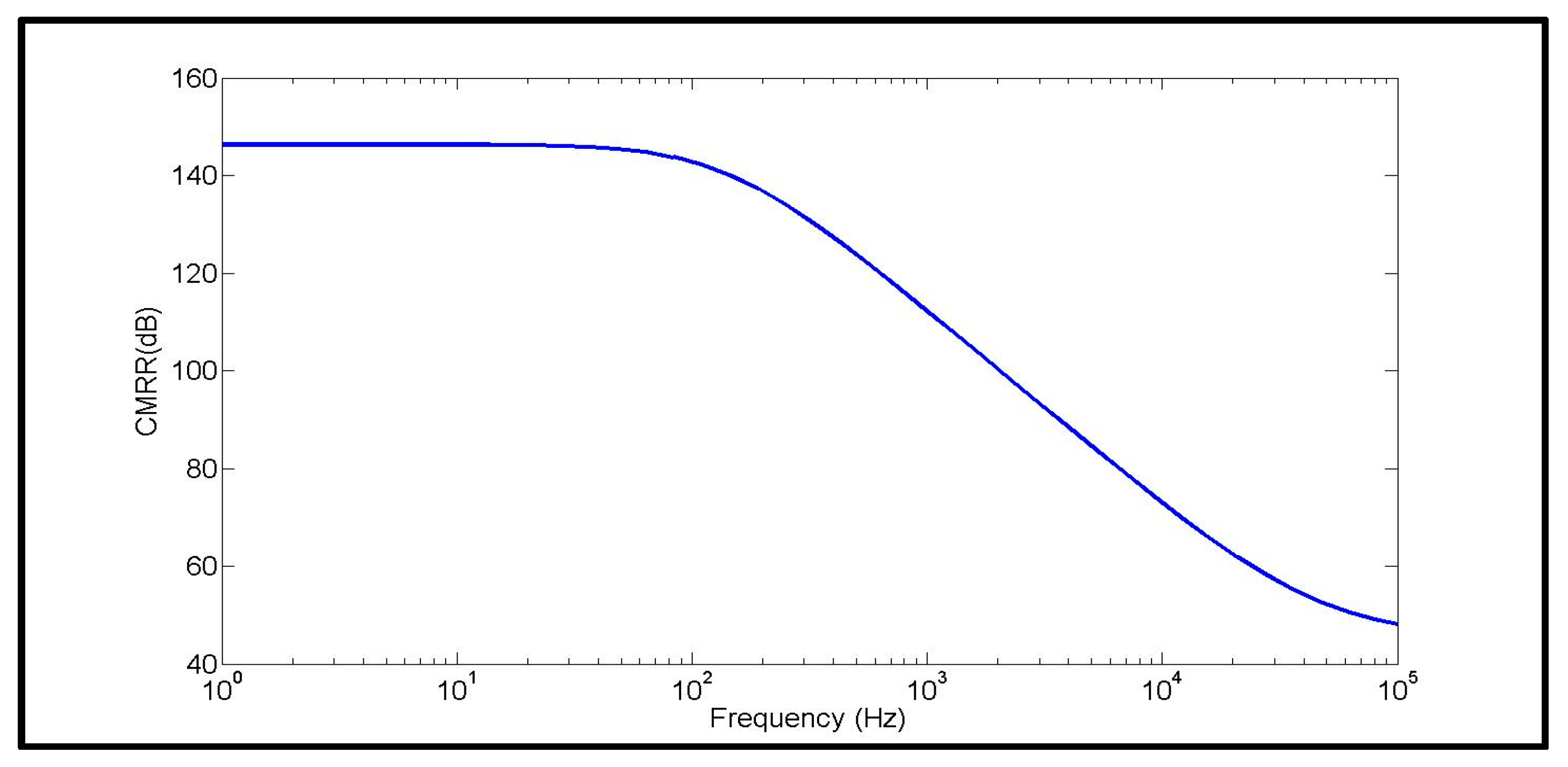

4.2. Common Mode Rejection Ratio (CMRR)

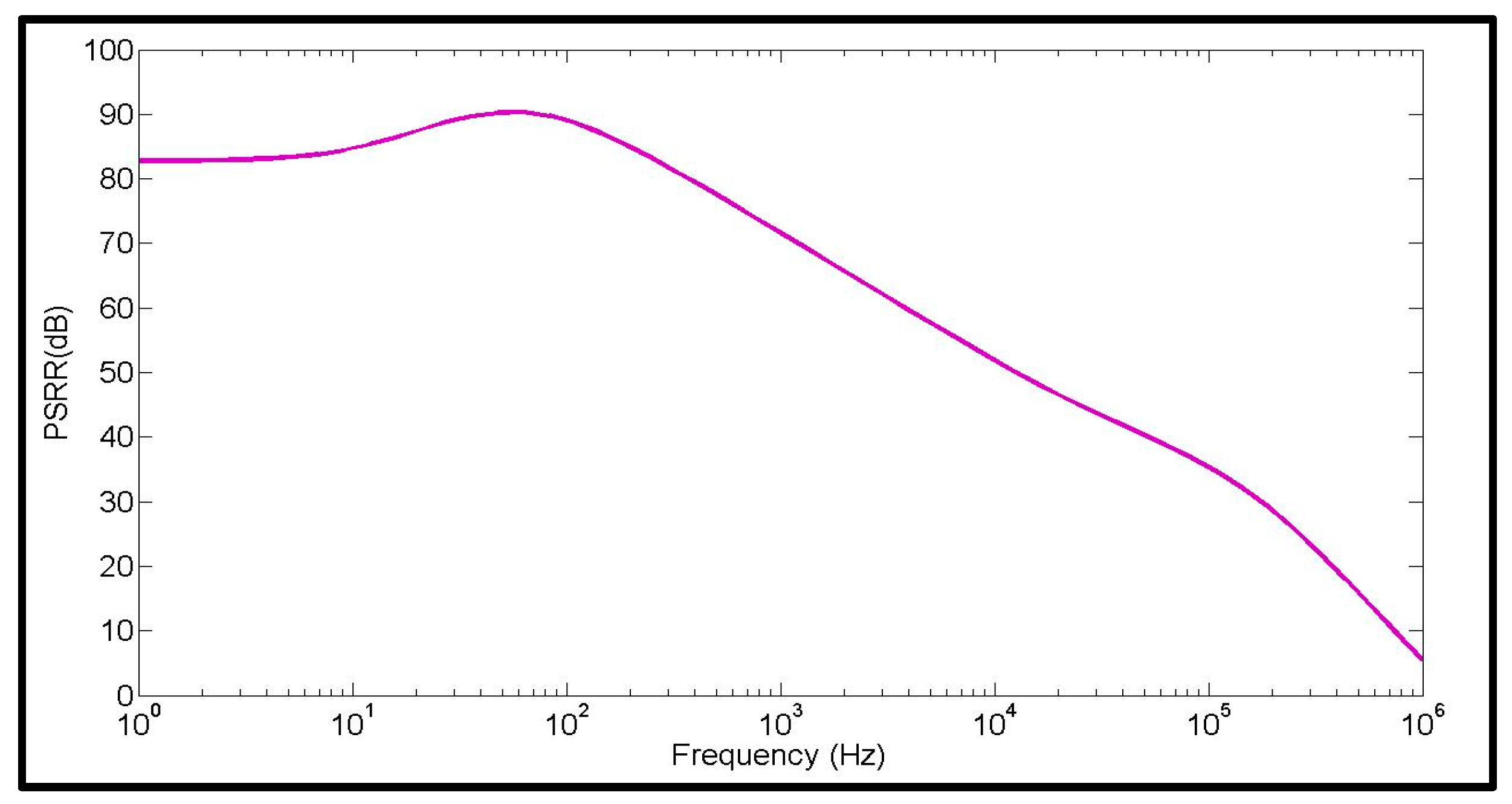

4.3. Power Supply Rejection Ratio (PSRR)

4.4. Slew Rate (SR)

4.5. Transient Response

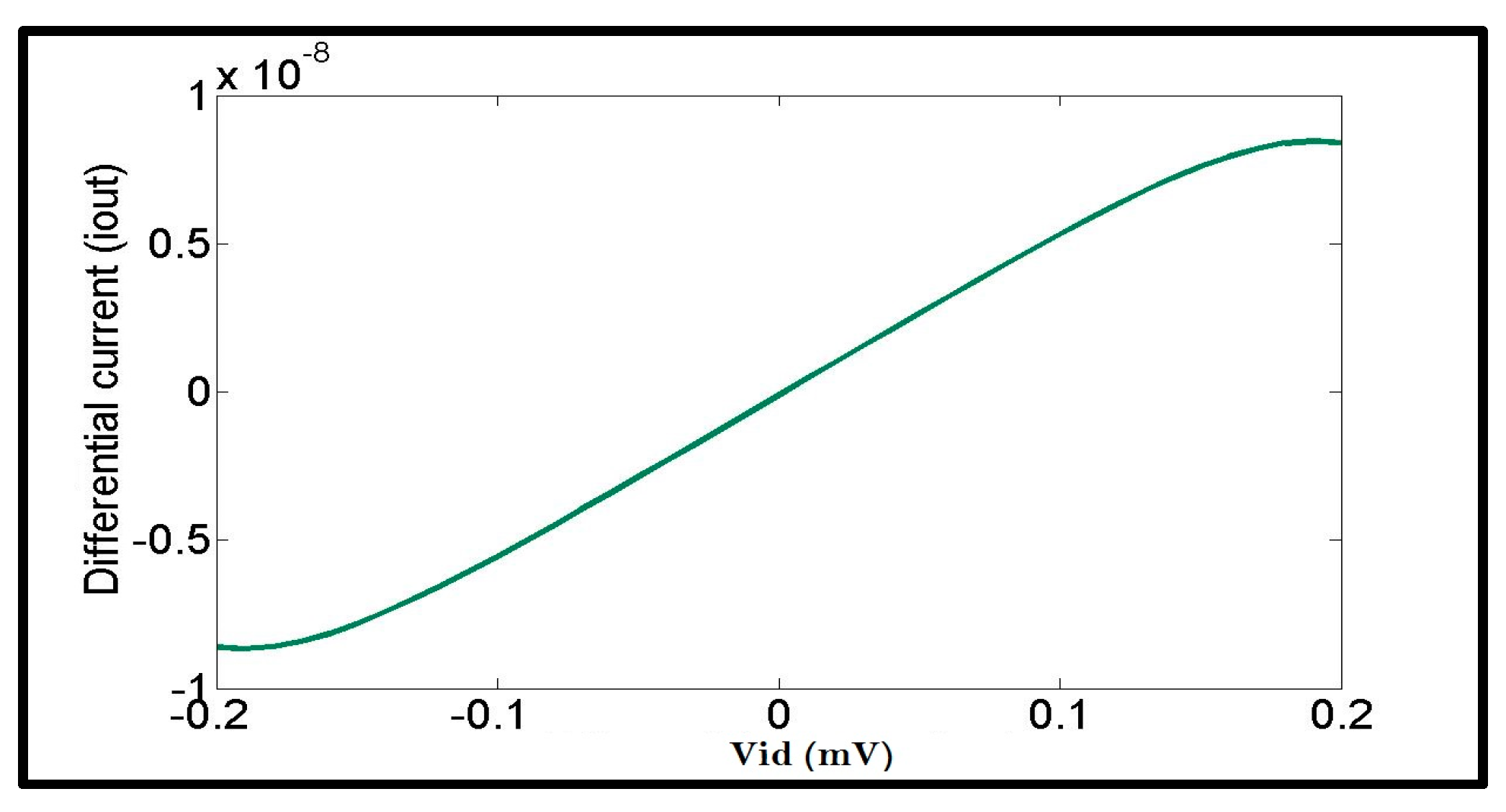

4.6. Transconductance

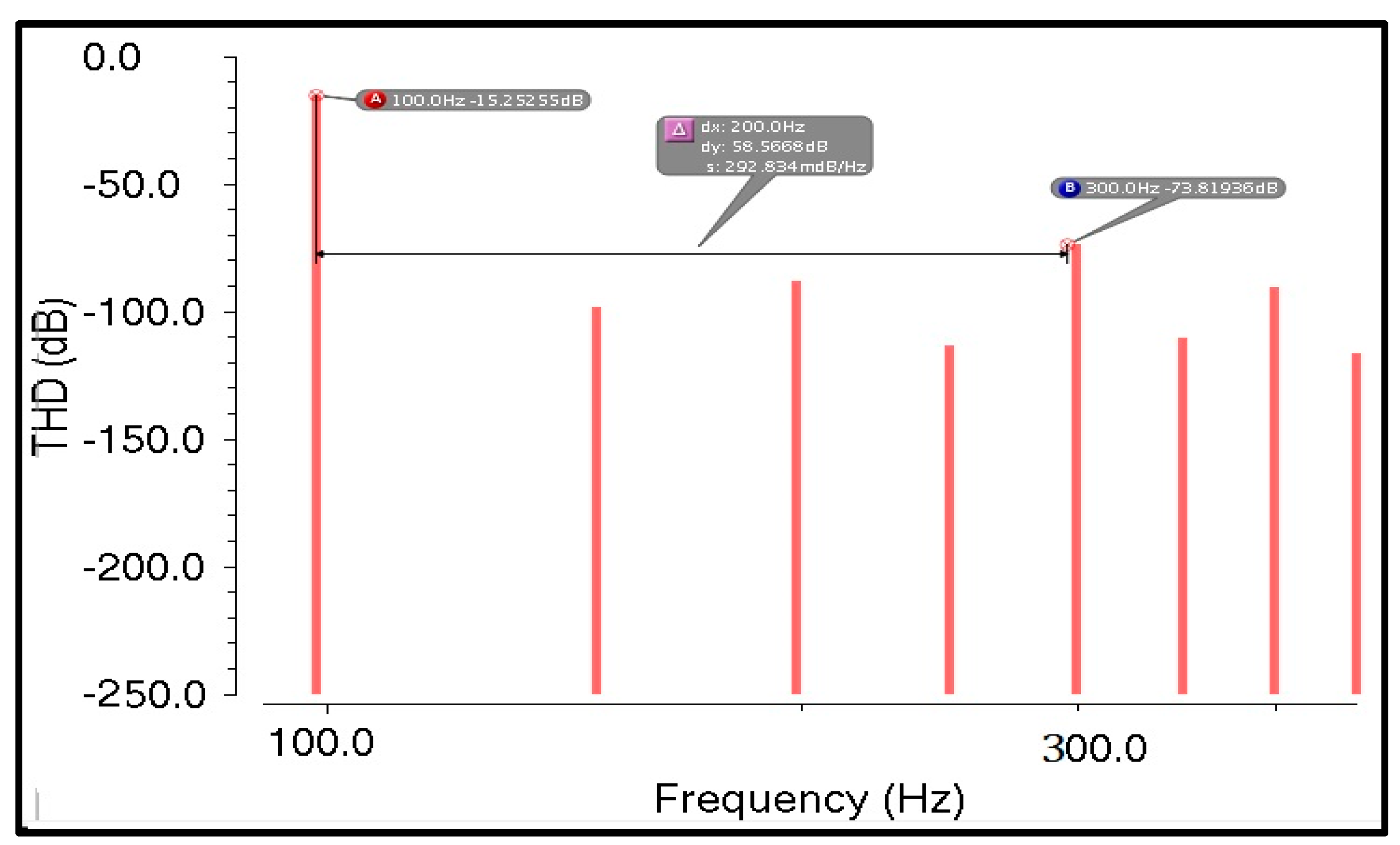

4.7. Total Harmonic Distortion (THD)

4.8. Power Consumption

5. Discussion

6. Conclusions

Author Contributions

Conflicts of Interest

Appendix A

| Acronyms | Definition |

|---|---|

| OTA | Operational transconductance amplifier |

| THD | Total harmonic distortion |

| FOM | Figure of merit |

| BD | Bulk driven |

| GD | Gate driven |

| GBW | Gain bandwidth |

| GM | Gain margin |

| PM | Phase margin |

| SR | Slew rate |

| CMRR | Common mode rejection ratio |

| PSRR | Power supply rejection ratio |

| SNR | Signal to noise ratio |

| LV | Low voltage |

| LP | Low power |

References

- Rakus, M.; Stopjakova, V.; Arbet, D. Design techniques for low voltage analog integrated circuits. J. Electr. Eng. 2017, 68, 245–255. [Google Scholar] [CrossRef]

- Raj, N.; Sharma, K.; Jasuja, A.; Gard, R. A low power OTA for biomedical applications. Cyber J. Multidiscip. J. Sci. Technol./J. Sel. Areas Bioeng. 2010, 1–5. [Google Scholar] [CrossRef]

- Wang, T.-Y.; Liu, L.-H.; Peng, S.Y. A power efficient highly linear reconfigurable bio-potential sensing amplifier using gate balanced Pseudo resistors. IEEE Trans. Circuits Syst. II Express Briefs 2015, 62, 199–203. [Google Scholar] [CrossRef]

- Chakraborty, A. Low power low voltage operation of operational amplifier. Int. J. Res. Eng. Technol. 2015, 4, 297–300. [Google Scholar]

- Yodtean, A.; Thanachayanont, A. Sub 1-V highly linear low power class AB bulk driven tunable CMOS transconductor. Analog Integr. Circuits Signal Process. 2013, 73, 383–397. [Google Scholar] [CrossRef]

- Hogervorst, R.; Huijsing, J. Design of Low-Voltage, Low-Power Operational Amplifier Cells, 3rd ed.; Springer: Dordrecht, The Netherland, 2000; pp. 1–206. ISBN 978-1-4757-2489-9. [Google Scholar]

- Sharan, T.; Bhadauria, V. Fully differential, bulk driven, class AB, sub-threshold OTA with enhanced slew rates and gain. J. Circuits Syst. Comput. 2017, 26, 1750001. [Google Scholar] [CrossRef]

- Sharan, T.; Chetri, P.; Bhadauria, V. Ultra-low-power bulk-driven fully differential subthreshold OTAs with partial positive feedback for Gm-C filters. Analog Integr. Circuits Syst. 2018, 94, 427–447. [Google Scholar] [CrossRef]

- Carrillo, J.M.; Torelli, G.; P-Aloe, R.; Valverde, J.M.; D-Carrillo, J.F. Single-pair bulk driven CMOS input stage: A compact low-voltage analog cell for scaled technologies. Integr. VLSI J. 2010, 43, 251–257. [Google Scholar] [CrossRef]

- Raikos, G.; Vlassis, S. 0.8V bulk driven operational amplifier. Analog Integr. Circuit Signal Process. 2010, 63, 425–432. [Google Scholar] [CrossRef]

- Carvajal, R.G.; R-Angulo, J.; L-Martin, A.J.; Torralba, A.; Galan, J.A.G.; Carlosena, A.; Chavero, F.M. The flipped voltage follower: A useful cell for low voltage low power circuit design. IEEE Trans. Circuits Syst. I 2005, 52, 1276–1291. [Google Scholar] [CrossRef]

- Rodriguez-Villegas, E.; Yufera, Y.; Reuda, A. A 1.25V micropower Gm-C filter based on FGMOS transistor operating in weak inversion. IEEE J. Solid State Circuits 2004, 39, 100–111. [Google Scholar] [CrossRef]

- Lo, T.-Y.; Hung, C.C. A 1-V 50 MHz pseudo differential OTA with compensation of mobility reduction. IEEE Trans. Circuits Syst. II 2007, 54, 1047–1051. [Google Scholar] [CrossRef]

- Szczepanski, S.; Pankiewicz, B.; Koziel, S.; Wojcikowski, M. Multiple output differential OTA with linearized bulk driven active-error feedback loop for continuous time filter applications. Int. J. Circuit Theory Appl. 2015, 43, 1671–1686. [Google Scholar] [CrossRef]

- Cotrim, E.D.C.; Ferreira, L.H.C. An ultra-low-power CMOS symmetrical OTA for low-frequency Gm-C applications. Analog Integr. Circuits Signal Process. 2012, 71, 275–282. [Google Scholar] [CrossRef]

- Khateb, F.; Biolek, D.; Khatib, N.; Vávra, J. Utilizing the Bulk-driven technique in analog circuit design. In Proceedings of the IEEE 13th International Symposium on Design and Diagnostics of Electronic Circuits and Systems (DDECS), Vienna, Austria, 14–16 April 2010. [Google Scholar]

- Ferreira, L.H.C.; Pimenta, T.C.; Moreno, R.L. An ultra–low-voltage ultra-low power MOS miller OTA with rail-to-rail input/output swing. IEEE Trans. Circuits Syst.-II Express Briefs 2007, 54, 843–847. [Google Scholar] [CrossRef]

- Sharan, T.; Bhadauria, V. Sub-threshold, cascode compensated, bulk driven OTAs with enhanced gain and phase margin. Microelectron. J. 2016, 54, 150–165. [Google Scholar] [CrossRef]

- Azhari, S.J.; Rezaei, F. High linear, high CMRR, low power OTA with class AB output stage. Int. J. Comput. Theory Eng. 2010, 2, 473–477. [Google Scholar] [CrossRef]

- Mincey, J.S.; Briseno-Vidrios, C.; Martinez, J.S.; Rodenbeck, C.T. Low-power Gm-C filter employing current re-use differential difference amplifiers. IEEE Trans. Circuits Syst. II Express Briefs 2017, 64, 635–639. [Google Scholar] [CrossRef]

- El Mourabit, A.; Lu, G.; Pittet, P. Wide linear range sub-threshold OTA for low power, low voltage and low frequency applications. IEEE Trans. Circuits Syst. I 2005, 52, 1481–1488. [Google Scholar] [CrossRef]

- Worapishet, A.; Naphaphan, C. Current feedback source degenerated CMOS transconductor with very high linearity. Electron. Lett. 2003, 39, 17–18. [Google Scholar] [CrossRef]

- Kwon, K.; Kim, H.T.; Lee, K. A 50–300 MHz highly linear and low noise CMOS Gm-C filter adopting multiple gated transistors for digital TV tuner ICs. IEEE Trans. Microw. Theory Tech. 2009, 57, 306–313. [Google Scholar] [CrossRef]

- Razaei, F.; Azhari, S.J. Transconductor linearization based on adaptive biasing of source degenerative MOS transistors. Circuits Syst. Signal Process. 2015, 34, 1149–1165. [Google Scholar] [CrossRef]

- Moreno, R.F.L.; Baruqui, F.A.P.; Petraglia, A. Bulk-tuned Gm-C filter using current cancellation. Microelectronics 2015, 46, 777–782. [Google Scholar] [CrossRef]

- Kim, D.; Kim, B.; Nam, S. A transconductor and tunable Gm-C high-pass filter linearization technique using feed forward Gm cancellation. IEEE Trans. Circuits Syst. II Express Brief 2015, 62, 1058–1062. [Google Scholar] [CrossRef]

- Lee, S.-Y.; Cheng, C.-J. Systematic design and modeling of OTA-C filter for portable ECG detection. IEEE Trans. Biomed. Circuits Syst. I 2009, 3, 53–64. [Google Scholar] [CrossRef] [PubMed]

- Abbasalizadeh, S.; Sheikhaei, S.; Forouzandeh, B. A 0.9 V supply OTA in 0.18 um CMOS technology and its application in realizing a tunable low-pass Gm-C filter for wireless sensor networks. Circuits Syst. 2013, 4, 34–43. [Google Scholar] [CrossRef]

- Sarrafinazhad, A.; Kara, I.; Baskaya, F. Design of a digitally tunable 5th order Gm-C filter using linearized OTA in 90 nm CMOS Technology. In Proceedings of the International Symposium on Signals, Circuits and Systems (ISSCS), Iasi, Romania, 9–10 July 2015. [Google Scholar]

- Ferreira, L.H.; Pimento, T.C.; Moreno, R.L. An ultra-low-voltage ultra-power weak inversion composite MOS transistor: Concept and applications. IEICE Trans. Fundamental Commun./Electron. Inf. Syst. 2002, E-85/A/B/C/D, 1–6. [Google Scholar] [CrossRef]

- Jihai, D.; Chuang, L.; Weilin, X.; Baolin, W. OTA-C filter for ECG acquisition systems with highly linear range and less pass band attenuation. J. Semicond. 2015, 36. [Google Scholar] [CrossRef]

- Soares, C.F.T.; de Maoraes, G.S.; Pertaglia, A. Low transconductance OTA with improved linearity suitable for low frequency Gm-C filters. Microelectronics 2014, 45, 1499–1507. [Google Scholar] [CrossRef]

- Sun, C.-Y.; Lee, S.-Y. A fifth order Butterworth OTA-C LPF with multiple output differential input OTA-C filter for ECG applications. IEEE Trans. Circuits Syst. II Express Brief 2017. [Google Scholar] [CrossRef]

- Akbari, M.; Nazari, M.; Sharifi, L.; Hashemipour, O. Improving power efficiency of a two stage operational amplifier for biomedical applications. Analog Integr. Circuits Signal Process. 2015, 84, 173–183. [Google Scholar] [CrossRef]

- Grasso, A.D.; Marano, D.; Palumbo, G.; Pennisi, S. Design methodology of subthreshold three-stage CMOS OTS suitable for ultra-low power low area and high driving capability. IEEE Trans. Circuit Syst. I 2015, 62, 1453–1462. [Google Scholar] [CrossRef]

- Akbari, M.; Hashemipour, O. A 0.6 V, 0.4uW bulk driven operational amplifier with rail to rail input/output swing. Analog Integr. Circuits Signal Process. 2016, 86, 341–351. [Google Scholar] [CrossRef]

| Transistors | W/L (um) |

|---|---|

| Ma, Mb | 1/0.5 |

| M1, M4 | 10/10 |

| M2, M3 | 30/10 |

| M5, M7, M9, M15, M18, M23 | 30/1 |

| M6, M8, M10, M16, M17, M24 | 1.5/1 |

| M12, M13, M20, M21 | 8/1 |

| MM11, M14, M19, M22 | 160/1 |

| Corner Name | Corner | Gain (dB) | GBW (Hz) | PM (degree) | GM (dB) |

|---|---|---|---|---|---|

| Nominal | TT | 48.40 | 3.1 K | 80° | 19.01 |

| C0 | SS | 55.78 | 1.3 K | 76.5° | 20.4 |

| C1 | SF | 56.32 | 1.4 K | 78.6° | 20.5 |

| C2 | FS | 34.24 | 4.2 k | 83.5° | 19.2 |

| C3 | FF | 36.67 | 4.3 K | 83.3° | 19.3 |

| Temperature (°C) | Gain (dB) | GBW (Hz) | PM (degree) | GM (dB) |

|---|---|---|---|---|

| −50 | 55.4 | 234.7 | 78.5° | 25.2 |

| −25 | 54.84 | 866.5 | 77.8° | 22.1 |

| 0 | 52.48 | 1.9 K | 77.5° | 20.1 |

| 25 | 48.72 | 2.9 K | 79.9° | 18.9 |

| 50 | 44.38 | 3.8 K | 81.1° | 18.7 |

| 75 | 40 | 4.4 K | 82.1° | 18.9 |

| 100 | 35.4 | 4.7 K | 83.4° | 18.8 |

| Parameters | This Work [2018] | [2017] Ref [7] | [2015] Ref [34] | [2015] Ref [35] | [2015] Ref [36] |

|---|---|---|---|---|---|

| Technology (nm) | 150 nm | 180 nm | 180 nm | 350 nm | 180 nm |

| Topology | BD (D) | BD (D) | GD (D) | GD (S) | BD (S) |

| Stages | Single | Single | Two | Three | Two |

| VDD | 0.8 V | 0.5 V | 0.6 V | 1 V | 0.6 V |

| Gain (dB) | 48.4 dB | 70.4 dB | 90.1 dB | 120 dB | 82 dB |

| GBW (Hz) | 3.1 KHz | 9.24 KHz | 34.9 KHz | 20 KHz | 19.1 KHz |

| GM (dB) | 19.01 dB | 19.5 dB | 20 dB | - | - |

| PM (degree) | 80° | 54° | 62.2° | 54° | 60° |

| CMRR (dB) | 146.3 dB | 106 dB | 37 dB | 70 dB | 114.7 dB |

| PSRR (dB) | 83 dB | 70 dB | 30.7 dB | 184 dB | |

| SR+/− (V/ms) | 99.56/100 | 967 | 7.5 | 7.38/2.88 | 5.6 |

| Power (W) | 59.04 nW | 64 nW | 300 nW | 195 nW | 400 nW |

| THD (dB) | −58.56 dB | −52.4 dB | −40 dB | Less as SE | −55.9 dB |

| Cap. load (pF) | 1 pF | 2 × 15 pF | 2 × 7.5 pF | 200 pF | 15 pF |

| FOM | 254.13 | 9828.5 | 78.6 | 90.83 | 21.92 |

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Bano, S.; Narejo, G.B.; Ali Shah, S.M.U. Power Efficient Fully Differential Bulk Driven OTA for Portable Biomedical Application. Electronics 2018, 7, 41. https://doi.org/10.3390/electronics7030041

Bano S, Narejo GB, Ali Shah SMU. Power Efficient Fully Differential Bulk Driven OTA for Portable Biomedical Application. Electronics. 2018; 7(3):41. https://doi.org/10.3390/electronics7030041

Chicago/Turabian StyleBano, Saleha, Ghous Bakhsh Narejo, and Syed Muhammad Usman Ali Shah. 2018. "Power Efficient Fully Differential Bulk Driven OTA for Portable Biomedical Application" Electronics 7, no. 3: 41. https://doi.org/10.3390/electronics7030041