Article

# More Discussions on Intrinsic Frequency Detection Capability of Full-Rate Linear Phase Detector in Clock and Data Recovery

Sangjin Byun 🗓

Division of Electronics and Electrical Engineering, Dongguk University, Seoul 04620, Korea; sjbyun@dongguk.edu; Tel.: +82-2-2260-3331

Received: 8 May 2018; Accepted: 7 June 2018; Published: 8 June 2018

**Abstract:** The full-rate linear phase detector (PD) has not only phase detection capability but also single-sided frequency detection capability intrinsically. Previously, this fact has been discovered by researching the phase and frequency characteristics of the combined full-rate linear PD and charge pump (CP) under the condition that the ratio of the received data frequency ( $f_{\rm DATA}$ ) and the recovered clock frequency ( $f_{\rm CLK}$ ) is set as an integer number. In this paper, for completeness of the theory, the phase and frequency characteristics of the combined full-rate linear PD and CP are studied again while the ratio of  $f_{\rm DATA}$  and  $f_{\rm CLK}$  is set as a general rational number. Additionally, theoretical analyses of the lock-in range and the lock time of the referenceless single-loop clock and data recovery (CDR) including the full-rate linear PD are newly developed and verified. The calculated lock times by the analysis results agree well with the measured lock times from the MATLAB Simulink simulations.

**Keywords:** linear phase detector; frequency detection capability; clock and data recovery; CMOS integrated circuits

#### 1. Introduction

To cover the wide range of data rates of the clock and data recovery (CDR) loops and to compensate for the process, voltage, and temperature (PVT) variations of clock frequency from voltage controlled oscillator (VCO), various frequency acquisition techniques have been utilized [1–9] in the serial data interfaces. However, most of these techniques originate from the thought that the phase detectors cannot detect the frequency difference between the received data and the recovered clock in the CDR loops.

Recently, it has been discovered in Reference [10] that the full-rate Hogge linear phase detector (PD) [11] has not only phase detection capability but also intrinsic single-sided frequency detection capability, and such that a referenceless single-loop CDR can be simply implemented by using only the full-rate linear PD without any frequency acquisition techniques. To prove this intrinsic frequency detection capability of the full-rate linear PD, several timing diagrams have been drawn at different clock frequencies specifically when the ratio of the received data frequency ( $f_{\text{DATA}}$ ) and the recovered clock frequency ( $f_{\text{CLK}}$ ) is set as an integer number and the phase and frequency characteristics of the combined full-rate linear PD and charge pump (CP) have been obtained [10]. However, if the ratio of  $f_{\text{DATA}}$  and  $f_{\text{CLK}}$  is not an integer number, we could not help but use interpolation between adjacent integer ratios and confirm the interpolated phase and frequency characteristics by providing many supportive MATLAB Simulink simulations. In Reference [10], we have also developed the frequency-locked loop (FLL) analysis to prove that the locking trajectory of the referenceless single-loop CDR utilizing the frequency detection capability of the full-rate linear PD is uniquely represented by

an exponential decay function with a single time constant. However, we could not derive in [10] the closed-form equations of the lock-in range and the lock time of the CDR loop theoretically.

In this paper, for completeness of the theory, the phase and frequency characteristics of the combined full-rate linear PD and CP are to be studied again while the ratio of  $f_{\rm DATA}$  and  $f_{\rm CLK}$  is not constrained to just an integer but extended to a general rational number. Additionally, theoretical analyses of the lock-in range and the lock time are to be newly developed for the referenceless single-loop CDR implemented by using only the full-rate linear PD without any frequency acquisition aids and verified by comparing the calculated lock times by the analysis results and the measured lock times from the MATLAB Simulink simulations.

Therefore, this paper is organized as follows. In Section 2, the phase and frequency characteristics of the combined full-rate linear PD and CP are presented when the ratio of  $f_{\rm DATA}$  and  $f_{\rm CLK}$  is set as a general rational number. In Section 3, theoretical analyses of the lock-in range and the lock time of the referenceless single-loop CDR including the full-rate linear PD are developed and verified by using the MATLAB Simulink simulations. The conclusion is given in Section 4.

### 2. Phase and Frequency Characteristics of the Combined Full-Rate Linear PD and CP

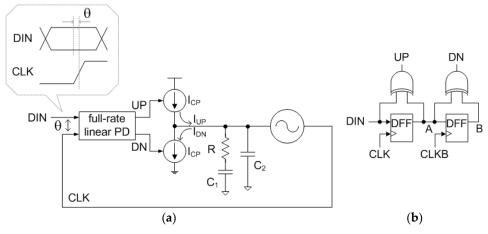

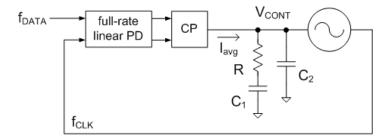

Figure 1 shows the referenceless single-loop CDR architecture including the full-rate linear PD, which is the so-called Hogge PD [11]. If  $\theta$  is defined as the phase difference between the center of the received data (DIN) and the rising edge of the recovered clock (CLK) as shown in Figure 1, we have shown in Reference [10] that the full-rate linear PD outputs the up (UP) and down (DN) pulses of which pulse widths are  $(2n-1)\pi + \theta$  and  $n\pi$ , respectively, per every n bits when  $f_{\text{CLK}} = 1/n \times f_{\text{DATA}}$  and n is an integer number greater than or equal to 1. As the one bit duration of the received data is  $2\pi$ , the CP output current can be represented as

$$I_{\rm UP} - I_{\rm DN} = \alpha \ I_{\rm CP} \frac{(2n-1)\pi + \theta}{2n\pi} - \alpha \ I_{\rm CP} \frac{n\pi}{2n\pi} = \alpha \ I_{\rm CP} \frac{(n-1)\pi + \theta}{2n\pi} \ {\rm for} \ -\pi \ < \ \theta \ < \ \pi$$

(1)

where  $I_{\rm UP}$  is the CP up current,  $I_{\rm DN}$  is the CP down current,  $\alpha$  is the bit transition density, and the current sources of the CP up and down paths are both equal to  $I_{\rm CP}$ . Figure 2a,b show the timing diagrams when n=1 and n=2, respectively, for example. For ease of understanding, the rising and falling edges of the recovered clock are colored in red and green, respectively. In these timing diagrams, we can observe that  $\theta$  is kept constant from bit to bit as time goes on because n is set as an integer number exactly. In Figure 2a,b, the UP pulse is null during  $\pi-\theta$ , which is equivalent to the time difference between the rising edge (in red color) of the recovered clock and the next bit transition of the received data. Thus, the UP pulse width is  $2n\pi-(\pi-\theta)$  per every n bits. However, the DN pulse width is always  $n\pi$  because it is equal to half of the recovered clock period per every n bits.

**Figure 1.** (a) The referenceless single-loop clock and data recovery (CDR) architecture including (b) the full-rate Hogge linear phase detector (PD).

**Figure 2.** The timing diagrams of the full-rate linear PD when  $f_{CLK} = 1/n \times f_{DATA}$  and (a) n = 1, (b) n = 2, (c) n = 3/2 and (d) n = 4/3.

By following the similar way, we can also derive the CP output current when n is set as a general rational number greater than 1. Since n is now a rational number greater than 1, n = p/q, p > q, and p and q are relatively prime integers. Then, we can find regularity in the UP and DN pulses by carefully observing the timing diagrams when n is set as rational numbers. Figure 2c,d show the timing diagrams when n = 3/2 and n = 4/3, respectively, for example. In these timing diagrams, it is interestingly observed that there are exactly q clocks and so q different  $\theta \in \{\theta_1, \theta_2, \ldots, \theta_q\}$  in every p bits and that the UP pulse is null during  $\pi - \theta$  again. Thus, the UP pulse width is  $2\pi \times p - \sum\limits_{i=1}^{q} (\pi - \theta_i)$  per every p bits and the DN pulse width is  $\pi \times p$  per every p bits since the DN pulse is always null for half of the recovered clock period. Consequently, the CP output current can be represented in a simple form as follows.

$$I_{\text{UP}} - I_{\text{DN}} = \alpha \ I_{\text{CP}} \frac{2\pi \times p - \sum\limits_{i=1}^{q} (\pi - \theta_i)}{2\pi \times p} - \alpha \ I_{\text{CP}} \frac{\pi \times p}{2\pi \times p} = \alpha \ I_{\text{CP}} \frac{\pi \times (p - q) + \sum\limits_{i=1}^{q} \theta_i}{2\pi \times p} = \alpha \ I_{\text{CP}} \frac{(n - 1)\pi + \frac{1}{q} \sum\limits_{i=1}^{q} \theta_i}{2n\pi}$$

(2)

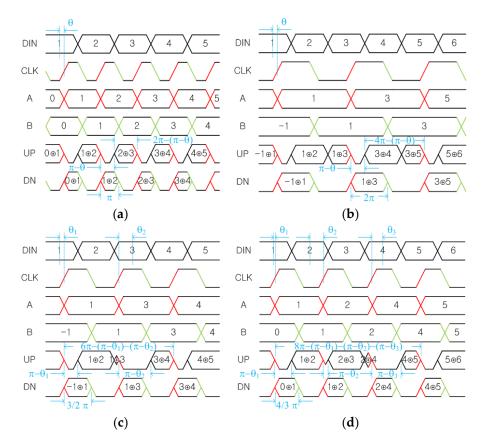

For the calculation of  $\frac{1}{q}\sum_{i=1}^{q}\theta_{i}$  in Equation (2), we have to carefully consider the distribution of the rising edges of the recovered clock signals in Figure 3. Since n=p/q is a rational number greater than 1,  $\theta$  increases linearly within the range of  $(-\pi, +\pi)$  as time goes on. Since  $\theta$  is periodic for every q clocks such that  $\theta_{i+q}=\theta_{i}$ ,  $\theta$  is uniformly distributed over one bit period between  $-\pi$  and  $+\pi$  with the same space of  $2\pi/q$  as shown in Figure 3. Accordingly,  $\frac{1}{q}\sum_{i=1}^{q}\theta_{i}$  has the minimum value of  $-\pi/q$  if the rising

Electronics **2018**, 7, 93 4 of 9

edges of the clock signals are aligned as shown in Figure 3b and the maximum value of  $+\pi/q$  if the rising edges of the clock signals are aligned as shown in Figure 3c. Thus,

$$\frac{1}{q} \sum_{i=1}^{q} \theta_{i} = -\frac{\pi}{q} + \theta - \left(-\pi + \frac{2\pi}{q}j\right) \text{ for } -\pi + \frac{2\pi}{q}j < \theta < -\pi + \frac{2\pi}{q}(j+1)$$

(3)

when  $\theta \in \{\theta_1, \theta_2, \dots, \theta_q\}$  and  $j = 0, 1, \dots, q - 1$ . Consequently, from Equations (2) and (3), the CP output current is represented by

$$I_{\text{UP}} - I_{\text{DN}} = \alpha \ I_{\text{CP}} \frac{(n-1)\pi - \frac{\pi}{q} + \theta - \left(-\pi + \frac{2\pi}{q}j\right)}{2n\pi} \text{ for } -\pi + \frac{2\pi}{q}j < \theta < -\pi + \frac{2\pi}{q}(j+1)$$

(4)

when  $\theta \in \{\theta_1, \theta_2, \dots, \theta_q\}$  and  $j = 0, 1, \dots, q - 1$ . Additionally, it is worth noting that, if n is an integer number, or equivalently q = 1, the derived Equation (4) for a general rational number becomes equal to the previous Equation (1) for an integer number.

**Figure 3.** The rising edges of the clock signals when  $\sum_{i=1}^{q} \theta_i$  is (a) zero, (b) minimum, and (c) maximum.

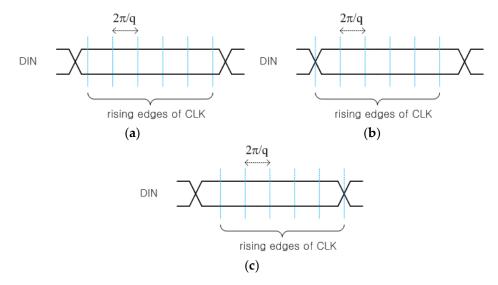

Figure 4a,b show the phase characteristics of the combined full-rate linear PD and CP at several rational numbers of n. The solid lines are the calculated values by the derived Equation (4) and the dot points are the simulated values by MATLAB Simulink. As shown in the figures, the calculated and simulated values agree well with each other. The difference between them is due to the randomness of the received data pattern. Figure 4c shows the figure of the general phase characteristic when n = p/q and  $n \ge 1$ . The general phase characteristic is composed of the same q segments of which the width is  $2\pi/q$  and the height is  $\alpha$   $I_{\rm CP}/p$ . The average value of the general phase characteristic becomes the frequency characteristic of the combined full-rate linear PD and CP.

$$I_{\text{avg}} = \frac{1}{2\pi} \int_{-\pi}^{\pi} I_{\text{UP}} - I_{\text{DN}} d\theta = \frac{\alpha I_{\text{CP}}}{2} \times \left(1 - \frac{f_{\text{CLK}}}{f_{\text{DATA}}}\right) \text{ if } f_{\text{CLK}} < f_{\text{DATA}}$$

(5)

Electronics **2018**, 7, 93 5 of 9

**Figure 4.** The phase characteristic of the combined full-rate linear PD and charge pump (CP) when  $f_{\text{CLK}} = 1/n \times f_{\text{DATA}}$  and (a) n = 3/2, n = 4/3, and n = 5/4; (b) n = 3/2, n = 5/2, and n = 7/2; (c) n = p/q.

## 3. Lock Time of the Referenceless Single-Loop CDR Including the Full-Rate Linear PD

Figure 5 is the FLL model of the referenceless single-loop CDR including only the full-rate linear PD. The locking trajectory of the recovered clock frequency is represented by the exponential decay function with the single time constant ( $\tau$ ) if  $f_{CLK}(0) < f_{DATA}$ .

$$f_{\text{CLK}}(t) = f_{\text{DATA}} - (f_{\text{DATA}} - f_{\text{CLK}}(0)) \times e^{-\frac{t}{\tau}} \text{ where } \tau = RC_1 \times \left(1 + \frac{2 f_{\text{DATA}}}{K_{\text{VCO}} R \alpha I_{\text{CP}}}\right)$$

(6)

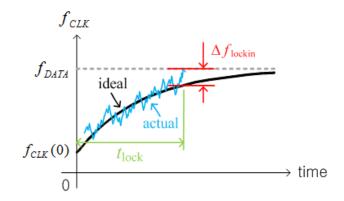

Figure 6 shows both the ideal and actual locking trajectories of  $f_{\rm CLK}(t)$ . The difference between them is due to the high-frequency ripple voltage which is added onto the ideal VCO control voltage ( $V_{\rm CONT}$ ). This ripple voltage is mostly generated by R and  $C_2$  of the loop filter and by the real-time CP output current which is depending on  $\theta$  and the bit transition pattern of the received random data. Since the lock-in range is defined as the frequency range within which a phase-locked loop (PLL) locks fast without cycle slip between the reference frequency and the output frequency, the lock-in range of the referenceless single-loop CDR is equivalent to the peak frequency deviation of  $f_{\rm CLK}(t)$  due to the ripple voltage [12]. Thus,

$$f_{\text{CLK}}(t_{\text{lock}}) + \Delta f_{\text{lockin}} = f_{\text{DATA}}$$

(7)

where  $\Delta f_{\text{lockin}}$  is the lock-in range and  $t_{\text{lock}}$  is the lock time as shown in Figure 6.

Electronics **2018**, 7, 93 6 of 9

Figure 5. The frequency-locked loop model.

**Figure 6.** The locking trajectory of  $f_{CLK}$  and the lock-in range.

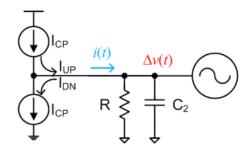

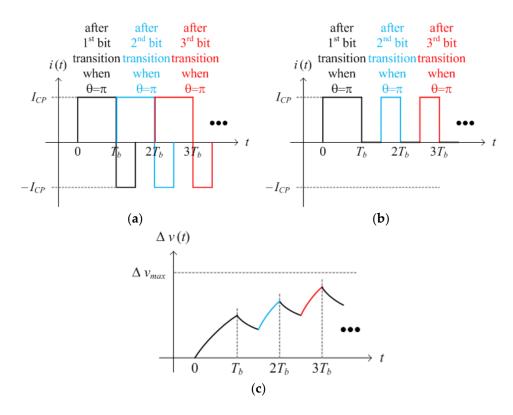

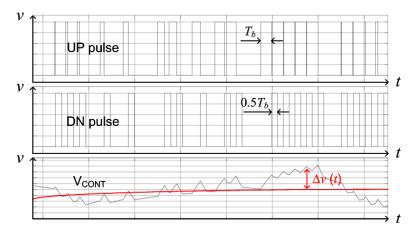

To derive the lock time of the referenceless single-loop CDR, we should obtain the peak frequency deviation of  $f_{\text{CLK}}(t)$ . Figure 7 depicts the R and  $C_2$  of the loop filter and the CP of the referenceless single-loop CDR.  $\Delta v(t)$  is the ripple voltage and i(t) is the real-time CP output current. The value of  $\Delta v(t)$  will be maximum if  $\theta = \pi$  and there comes consecutive bit transitions in the received data. Of course, keeping  $\theta = \pi$  with long consecutive bit transitions is actually not possible and, thus,  $\Delta v(t)$  may be a bit smaller than the maximum value. Figure 8a shows the ideal waveforms of the real-time CP output current after each bit transition assuming that  $\theta = \pi$  and there comes consecutive bit transitions and Figure 8b shows that of the effective real-time CP output current. Since i(t) flows into R and  $C_2$ ,  $\Delta v(t)$  increases asymptotically toward the maximum value ( $\Delta v_{\text{max}}$ ) as shown in Figure 8c and can be derived as

$$\Delta v(mT_b) = \Delta v((m-1)T_b)e^{-\frac{T_b}{RC_2}} + I_{CP}R\left(1 - e^{-\frac{T_b}{2RC_2}}\right)$$

(8)

when  $m \ge 2$ . Figure 9 shows the MATLAB Simulink simulated waveforms of the UP and DN pulses and the  $V_{\text{CONT}}$  while frequency acquisition is being made. Since  $\Delta v_{\text{max}} = \Delta v(mT_b)$  when m is  $\infty$  in Equation (8), the peak frequency deviation, or the lock-in range, is obtained from Equation (8) as

$$\Delta f_{\text{lockin}} = K_{\text{VCO}} \Delta v_{\text{max}} = \frac{I_{\text{CP}} R K_{\text{VCO}}}{1 + e^{-\frac{T_b}{2RC_2}}}$$

(9)

By using Equations (6) and (7), the lock time can be also derived as follows.

$$t_{\text{lock}} = \tau \ln \frac{f_{\text{DATA}} - f_{\text{CLK}}(0)}{\Delta f_{\text{lockin}}}$$

(10)

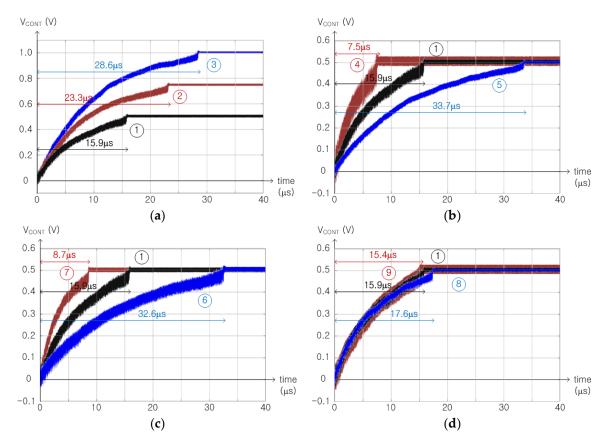

For verification purpose, the MATLAB Simulink simulations were performed. The loop parameters of the referenceless single-loop CDR are set as  $f_{\rm DATA}=2$  GHz,  $f_{\rm CLK}(0)=1$  GHz,  $\alpha=0.5$ ,  $K_{\rm VCO}=2$  GHz/V,  $I_{\rm CP}=100$   $\mu$ A, R=1 k $\Omega$ ,  $C_1=159$  pF and  $C_2=1.59$  pF. The Bernoulli random binary sequence was used as the input data stream. Since  $V_{\rm CONT}$  is linear with  $f_{\rm CLK}$  in this simulation setup, we could measure the locking trajectory of  $V_{\rm CONT}$  instead of  $f_{\rm CLK}$  directly.

**Figure 7.** The calculation of the ripple voltage due to R and  $C_2$ .

**Figure 8.** (a) Each and (b) the effective real-time charge pump current after consecutive bit transitions when  $\theta = \pi$  and (c) the consequent ripple voltage.

Figure 9. The simulated UP/DN pulses and  $V_{\rm CONT}$  voltage.

Figure 10 shows the simulated locking trajectories of  $V_{\rm CONT}$  when  $f_{\rm DATA}$ ,  $I_{\rm CP}$ ,  $C_1$ , and  $C_2$  are varied, respectively. The measured lock times are summarized with the corresponding loop parameters in Table 1. As can be seen in Figure 10 and Table 1, the calculated lock times by Equation (10) agree well with the measured lock times from the MATLAB Simulink simulations.

**Figure 10.** The simulated locking trajectories of  $V_{\text{CONT}}$  when (a)  $f_{\text{DATA}}$ , (b)  $I_{\text{CP}}$ , (c)  $C_1$  and (d)  $C_2$  are varied.

**Table 1.** The loop parameters and lock times.

|     | $f_{\mathrm{DATA}}$ | f <sub>CLK</sub> (0) | α   | K <sub>VCO</sub> | I <sub>CP</sub> | R                     | C <sub>1</sub> | C <sub>2</sub> | τ            | $\Delta f_{ m lockin}$ | calculated $t_{ m lock}$ (A) | measured $t_{\mathrm{lock}}$ (B) | B/A  |

|-----|---------------------|----------------------|-----|------------------|-----------------|-----------------------|----------------|----------------|--------------|------------------------|------------------------------|----------------------------------|------|

| 1   | 2 GHz               | 1 GHz                | 0.5 | 2 GHz/V          | 100 μΑ          | $1  \mathrm{k}\Omega$ | 159 pF         | 1.59 pF        | 6.52 μs      | 108 MHz                | $14.5 \mu s$                 | 15.9 μs                          | 1.10 |

| 2   | 2.5 GHz             | 1 GHz                | 0.5 | 2 GHz/V          | 100 μΑ          | $1 \text{ k}\Omega$   | 159 pF         | 1.59 pF        | 8.11 μs      | 106 MHz                | 21.5 μs                      | 23.3 μs                          | 1.09 |

| 3   | 3 GHz               | 1 GHz                | 0.5 | 2 GHz/V          | 100 μΑ          | $1 \text{ k}\Omega$   | 159 pF         | 1.59 pF        | 9.70 μs      | 105 MHz                | 28.6 μs                      | 28.6 μs                          | 1.00 |

| 4   | 2 GHz               | 1 GHz                | 0.5 | 2 GHz/V          | 200 μΑ          | $1 \text{ k}\Omega$   | 159 pF         | 1.59 pF        | $3.34~\mu s$ | 216 MHz                | 5.1 µs                       | 7.5 µs                           | 1.46 |

| (5) | 2 GHz               | 1 GHz                | 0.5 | 2 GHz/V          | 50 μΑ           | $1 \text{ k}\Omega$   | 159 pF         | 1.59 pF        | 12.88 μs     | 54 MHz                 | 37.6 μs                      | 33.7 µs                          | 0.90 |

| 6   | 2 GHz               | 1 GHz                | 0.5 | 2 GHz/V          | 100 μΑ          | $1 \text{ k}\Omega$   | 318 pF         | 1.59 pF        | 13.04 μs     | 108 MHz                | 29.0 μs                      | 32.6 µs                          | 1.12 |

| 7   | 2 GHz               | 1 GHz                | 0.5 | 2 GHz/V          | 100 μΑ          | $1 \text{ k}\Omega$   | 79.5 pF        | 1.59 pF        | $3.26 \mu s$ | 108 MHz                | 7.3 µs                       | 8.7 µs                           | 1.20 |

| 8   | 2 GHz               | 1 GHz                | 0.5 | 2 GHz/V          | 100 μΑ          | $1 \text{ k}\Omega$   | 159 pF         | 3.18 pF        | 6.52 μs      | 104 MHz                | $14.8 \mu s$                 | 17.6 μs                          | 1.19 |

| 9   | 2 GHz               | 1 GHz                | 0.5 | 2 GHz/V          | 100 μΑ          | $1  \mathrm{k}\Omega$ | 159 pF         | 0.795 pF       | $6.52~\mu s$ | 116 MHz                | $14.1~\mu s$                 | $15.4~\mu s$                     | 1.09 |

Red and blue colors are used to highlight that the values of the variables are changed for simulations and the resulted ratios are almost 1.

#### 4. Conclusions

In this paper, the phase and frequency characteristics of the combined full-rate linear PD and CP have been derived while the ratio of  $f_{\rm DATA}$  to  $f_{\rm CLK}$  is set as a general rational number. Additionally, the closed-form equations of the lock-in range and the lock time of the referenceless single-loop CDR including the full-rate linear PD have been derived theoretically. The calculated lock times by the derived equations agree well with the measured lock times from the MATLAB Simulink simulations.

Electronics **2018**, 7, 93 9 of 9

**Funding:** This research was supported by Basic Science Research Program through the National Research Foundation of Korea (NRF) funded by the Ministry of Education (NRF-2017R1D1A1B03028325).

Conflicts of Interest: The author declares no conflict of interest.

#### References

- 1. Lee, J.-Y.; Yoon, J.-H.; Bae, H.-M. A 10-Gb/s CDR with an adaptive optimum loop-bandwidth calibrator for serial communication links. *IEEE Trans. Circuits Syst. I Reg. Pap.* **2014**, *61*, 2466–2472. [CrossRef]

- 2. Kim, Y.-J.; Chung, S.-H.; Ha, K.-S.; Bae, S.-J.; Kim, L.-S. A 9.6 Gb/s 0.96 mW/Gb/s forwarded clock receiver with high jitter tolerance using mixing cell integrated injection-locked oscillator. *IEEE Trans. Circuits Syst. I Reg. Pap.* 2015, 62, 2495–2503. [CrossRef]

- 3. Saxena, S.; Shu, G.; Nandwana, R.K.; Talegaonkar, M.; Elkholy, A.; Anand, T.; Choi, W.-S.; Hanumolu, P.K. A 2.8 mW/Gb/s, 14 Gb/s serial link transceiver. *IEEE J. Solid-State Circuits* **2017**, *52*, 1399–1411. [CrossRef]

- 4. Jung, I.; Shin, D.; Kim, T.; Kim, C. A 140-Mb/s to 1.82-Gb/s continuous-rate embedded clock receiver for flat-panel displays. *IEEE Trans. Circuits Syst. II Express Briefs* **2009**, *56*, 773–777. [CrossRef]

- 5. Byun, S.; Son, C.H.; Hwang, J.; Min, B.-H.; Park, M.-Y.; Yu, H.-K. 1-5.6Gb/s CMOS clock and data recovery IC with a static phase offset compensated linear phase detector. *IET Circuits Devices Syst.* **2013**, 7, 159–168. [CrossRef]

- 6. Lee, D.; Kim, J.-J. 3.8 mW 10 Gbit/s CDR for intra-panel interface with a modulated training pattern. *Electron. Lett.* **2017**, 53, 1098–1100. [CrossRef]

- 7. Pottbacker, A.; Langmann, U.; Schreiber, H.-U. A Si bipolar phase and frequency detector IC for clock extraction up to 8 Gb/s. *IEEE J. Solid-State Circuits* **1992**, 27, 1747–1751. [CrossRef]

- 8. Dalton, D.; Chai, K.; Evans, E.; Ferriss, M.; Hitchcox, D.; Murray, P.; Selvanayagam, S.; Shepherd, P.; DeVito, L. A 12.5-Mb/s to 2.7-Gb/s continuous-rate CDR with automatic frequency acquisition and data-rate readback. *IEEE J. Solid-State Circuits* **2005**, *40*, 2713–2725. [CrossRef]

- 9. Hwang, S.; Song, J.; Lee, Y.; Kim, C. A 1.62–5.4 Gb/s receiver for DisplayPort version 1.2a with adaptive equalization and referenceless frequency acquisition techniques. *IEEE Trans. Circuits Syst. I Reg. Pap.* **2017**, 64, 2691–2702. [CrossRef]

- 10. Son, C.H.; Byun, S. On frequency detection capability of full-rate linear and binary phase detectors. *IEEE Trans. Circuits Syst. II Express Briefs* **2017**, *64*, 757–761. [CrossRef]

- 11. Hogge, C.R. A self-correcting clock recovery circuit. J. Lightw. Technol. 1985, 3, 1312–1314. [CrossRef]

- 12. Best, R.E. Phase-Locked Loops: Design, Simulation, and Applications; McGraw-Hill: New York, NY, USA, 2007.

© 2018 by the author. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).