Performance Analysis of a 3D Wireless Massively Parallel Computer

Abstract

:1. Introduction

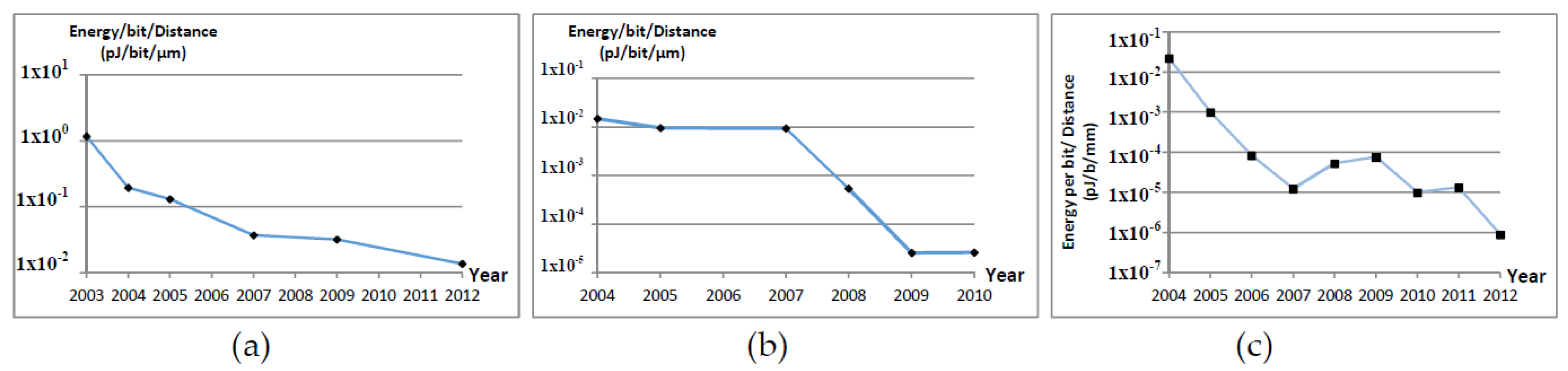

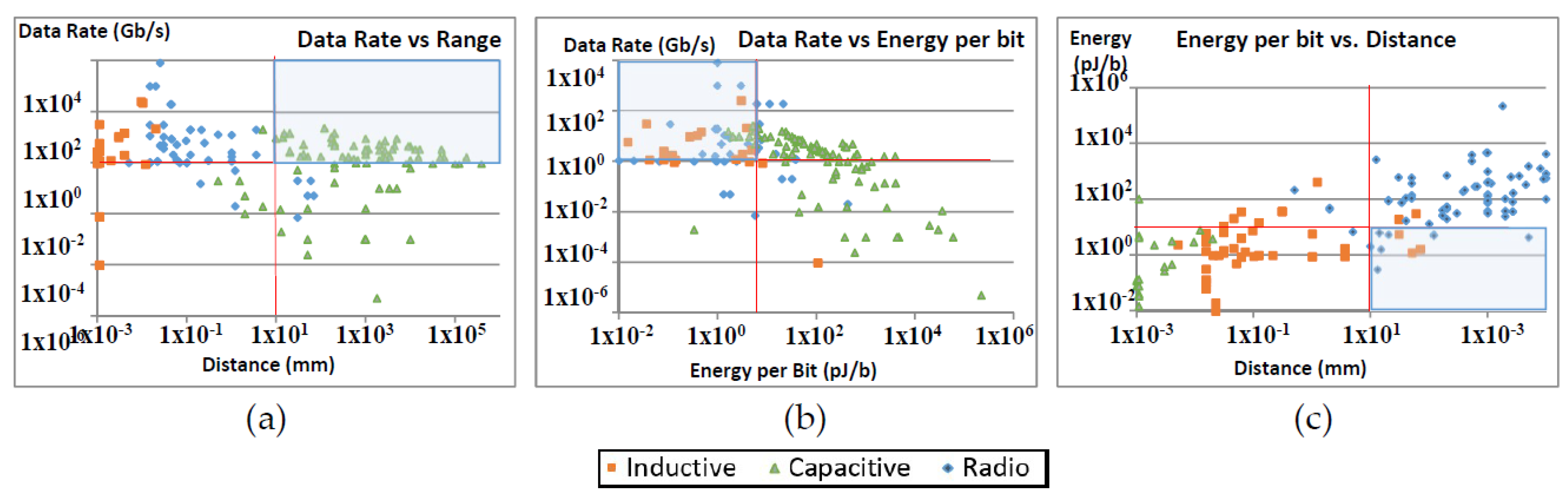

1.1. Wireless Technologies

1.2. Packet-Switching

1.2.1. Store-and-Forward

1.2.2. Cut-Through

1.2.3. Wormhole

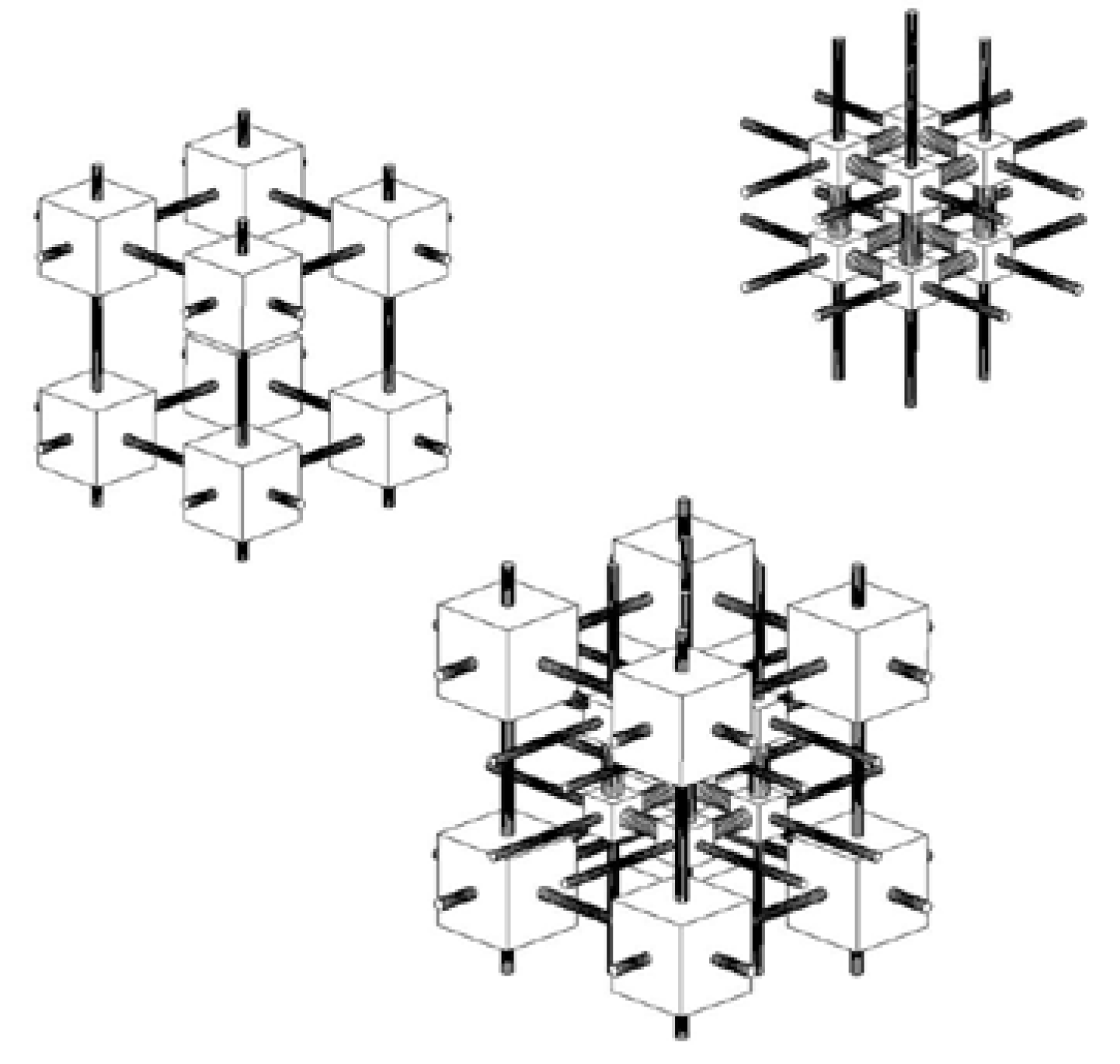

2. Ball Computer Architecture

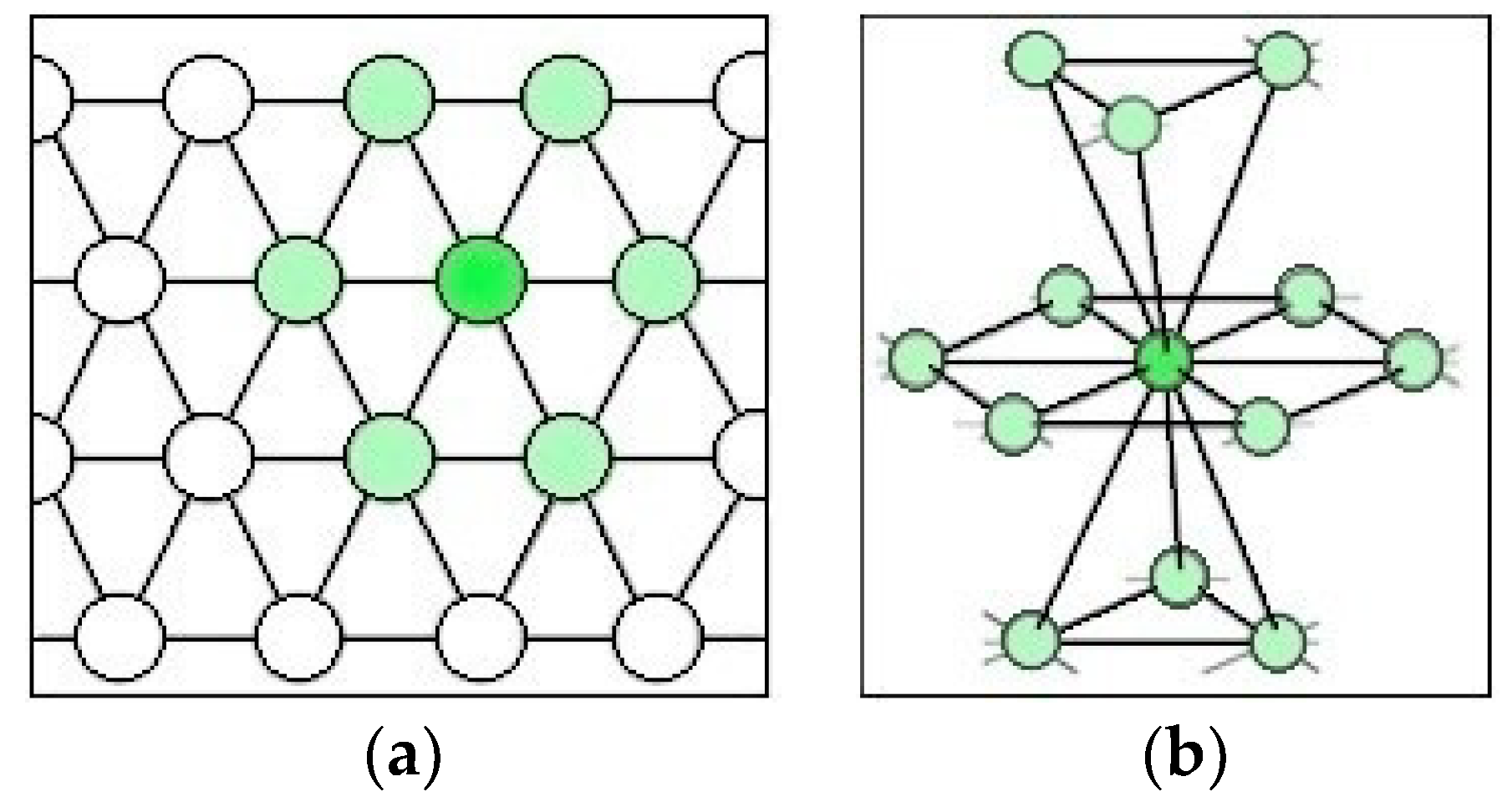

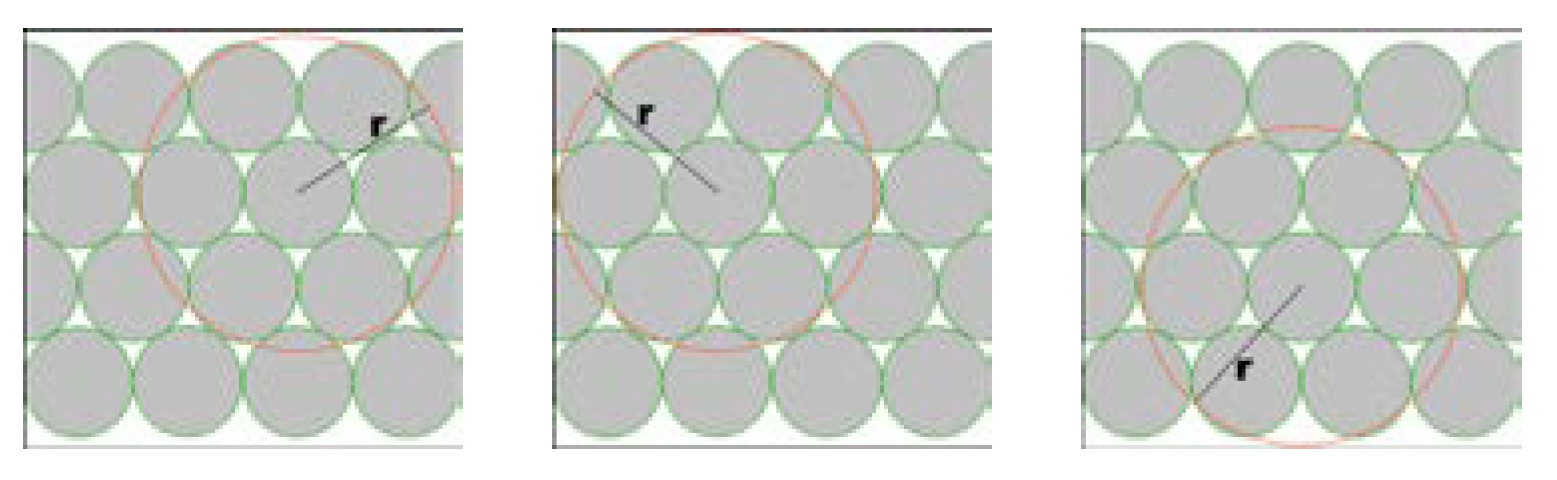

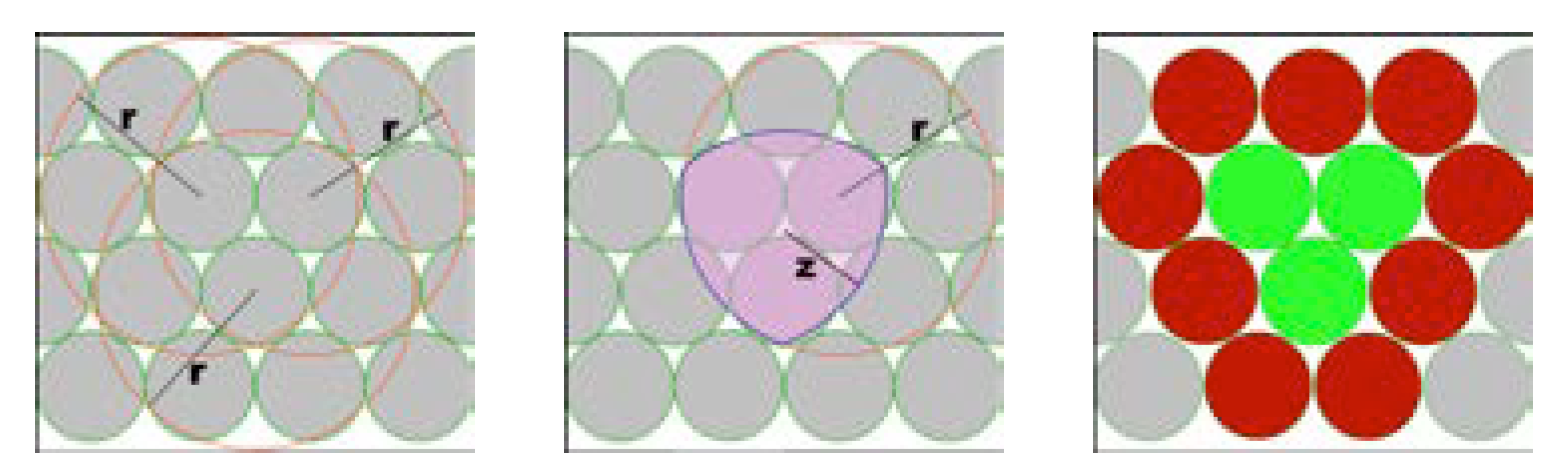

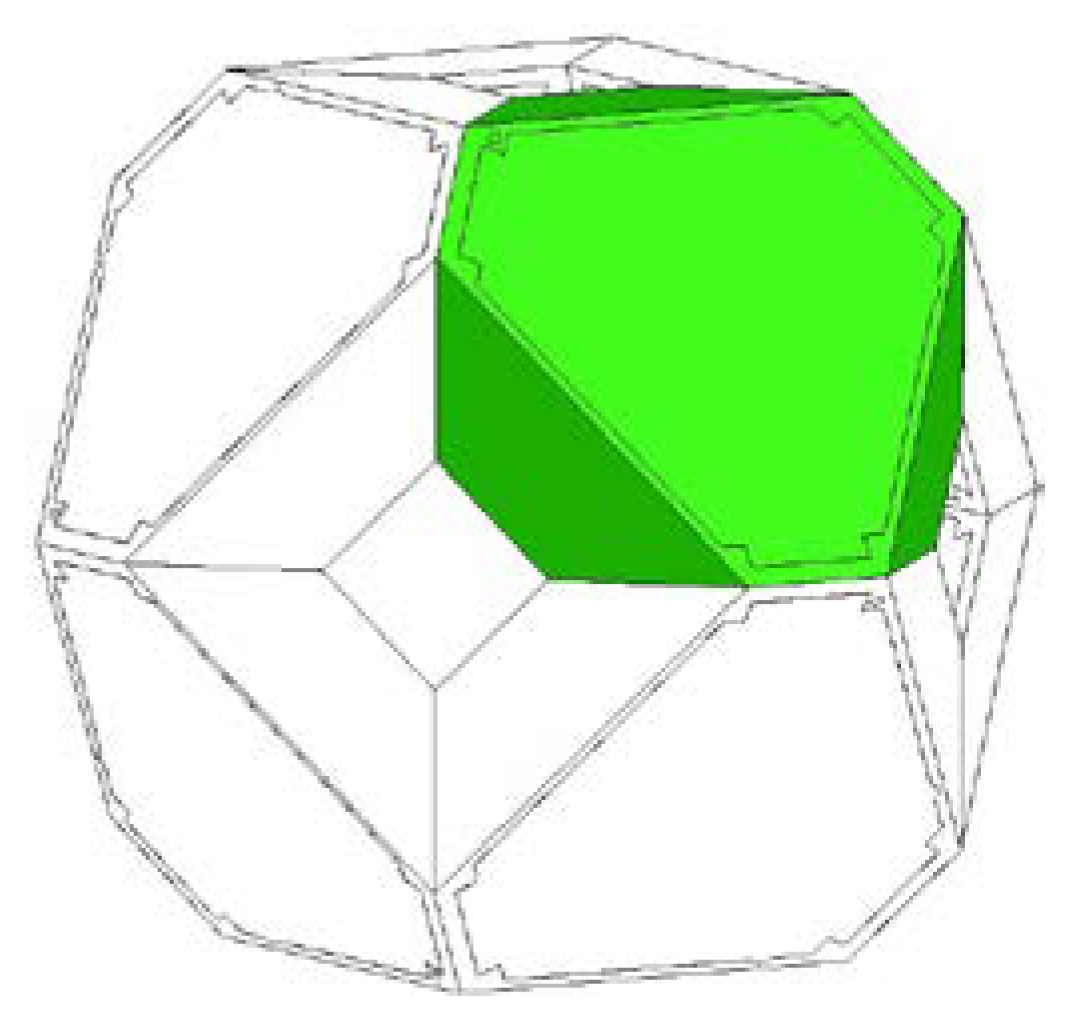

2.1. 3D Hexagonal Topology

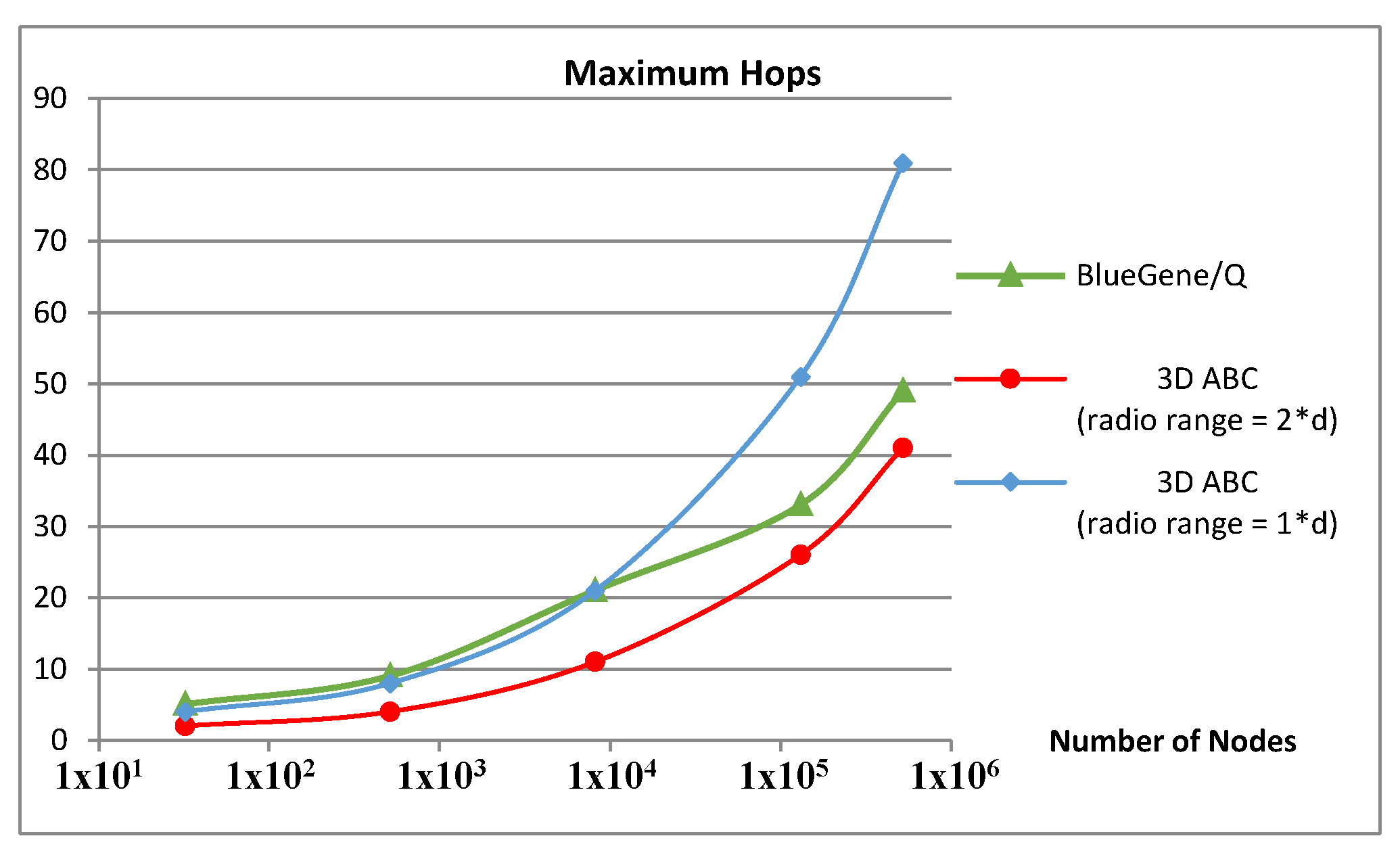

2.2. 4D ABC Topology

3. Simulation Results

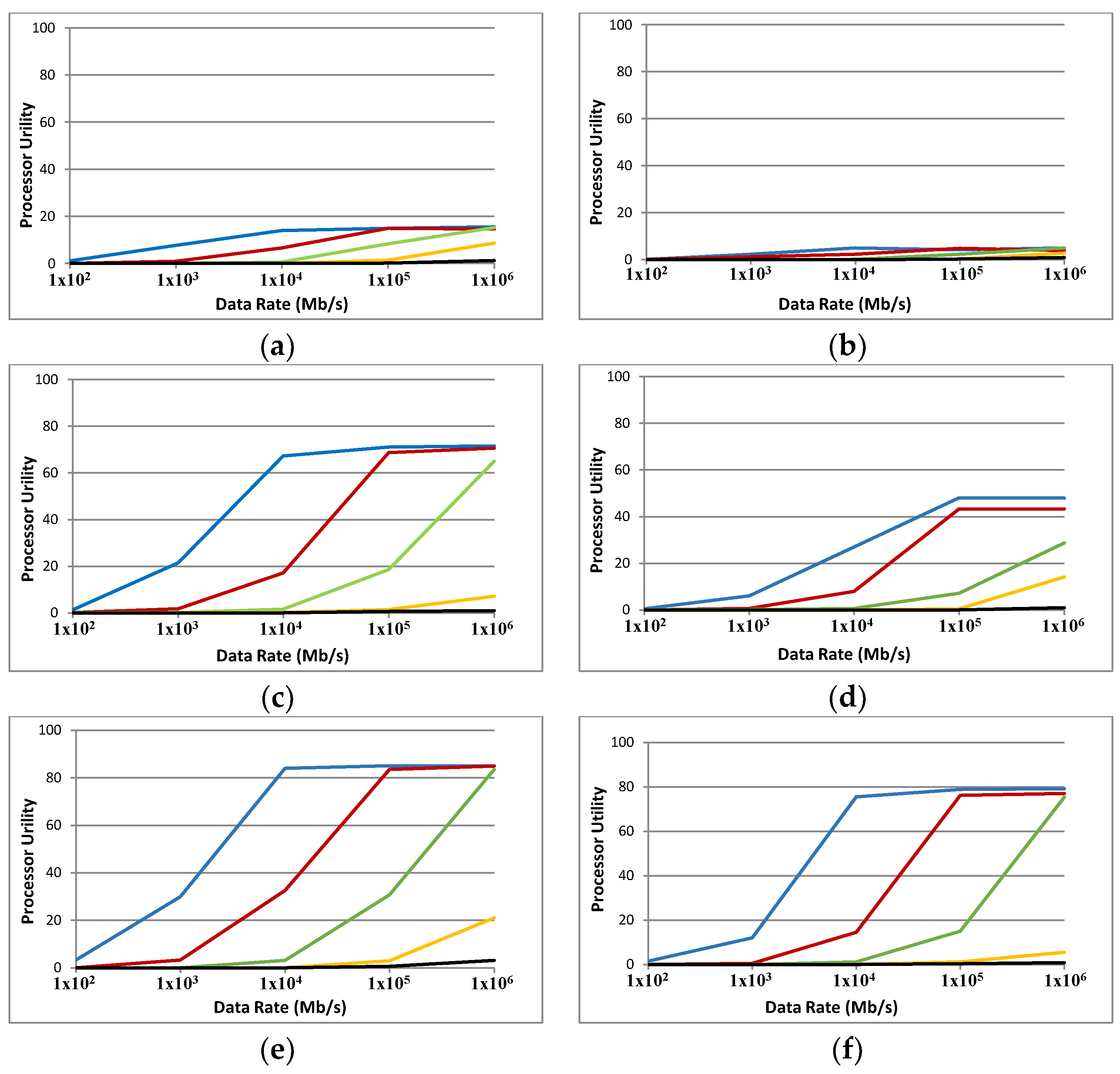

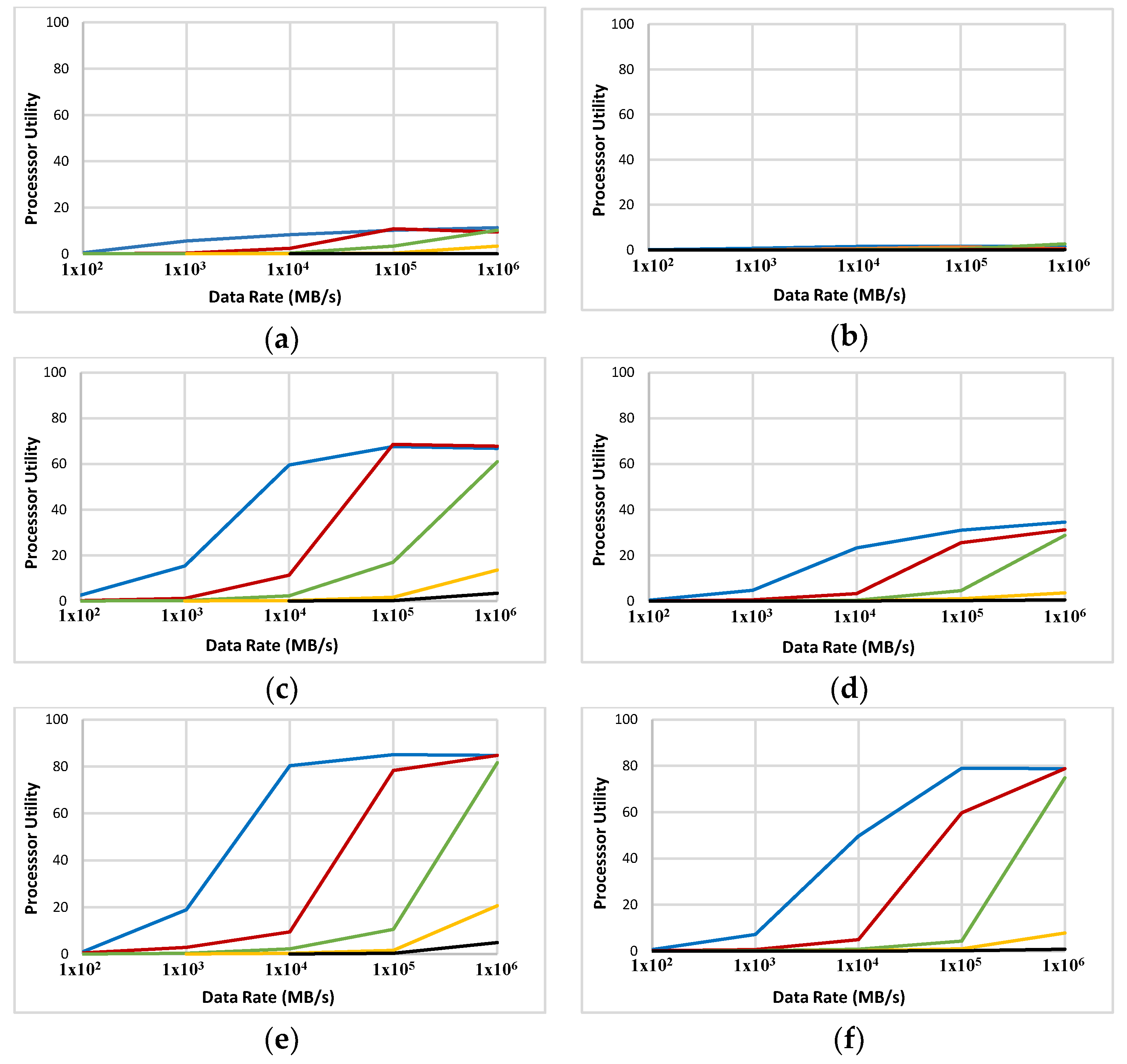

3.1. Processor Utilisation Analysis

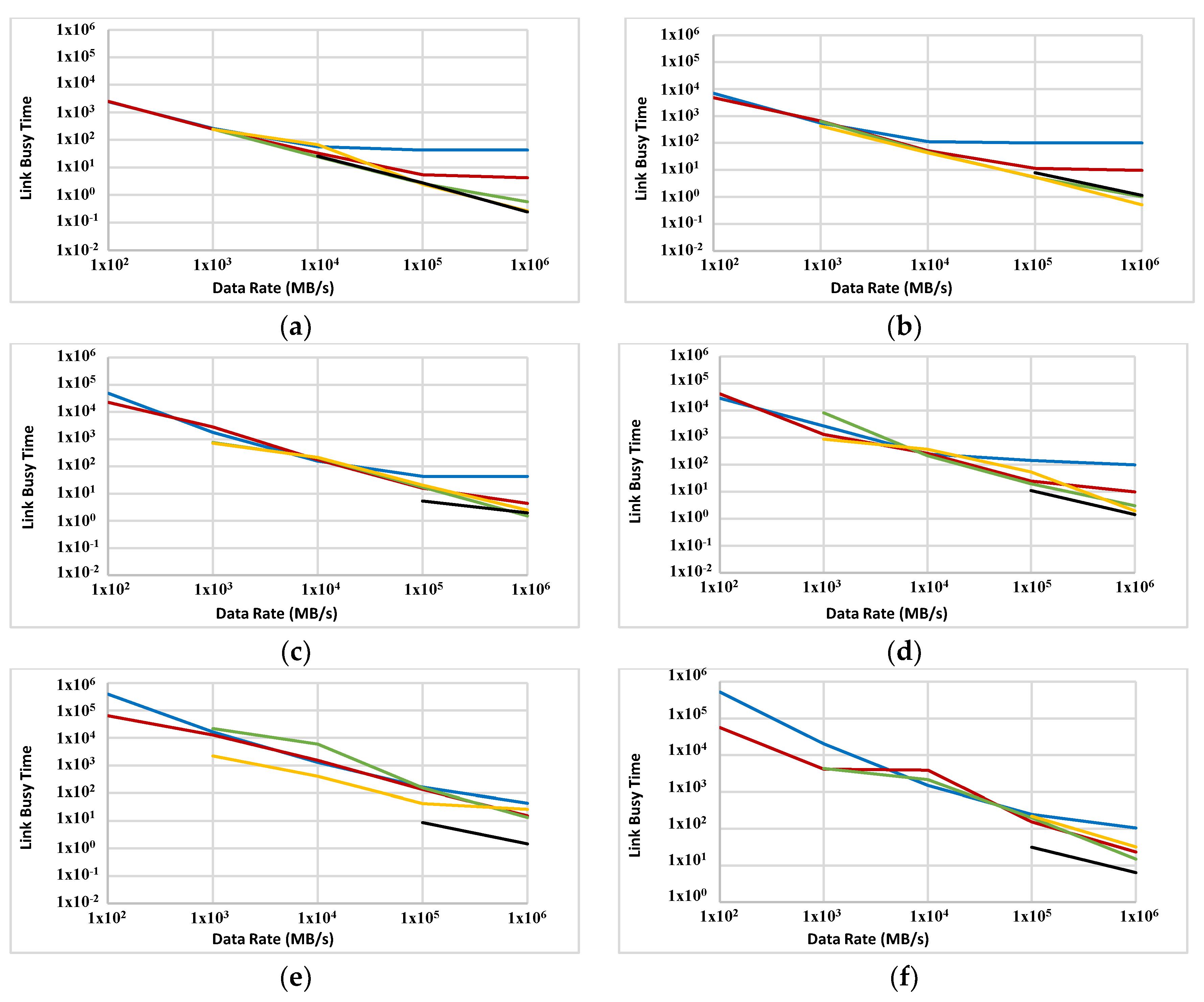

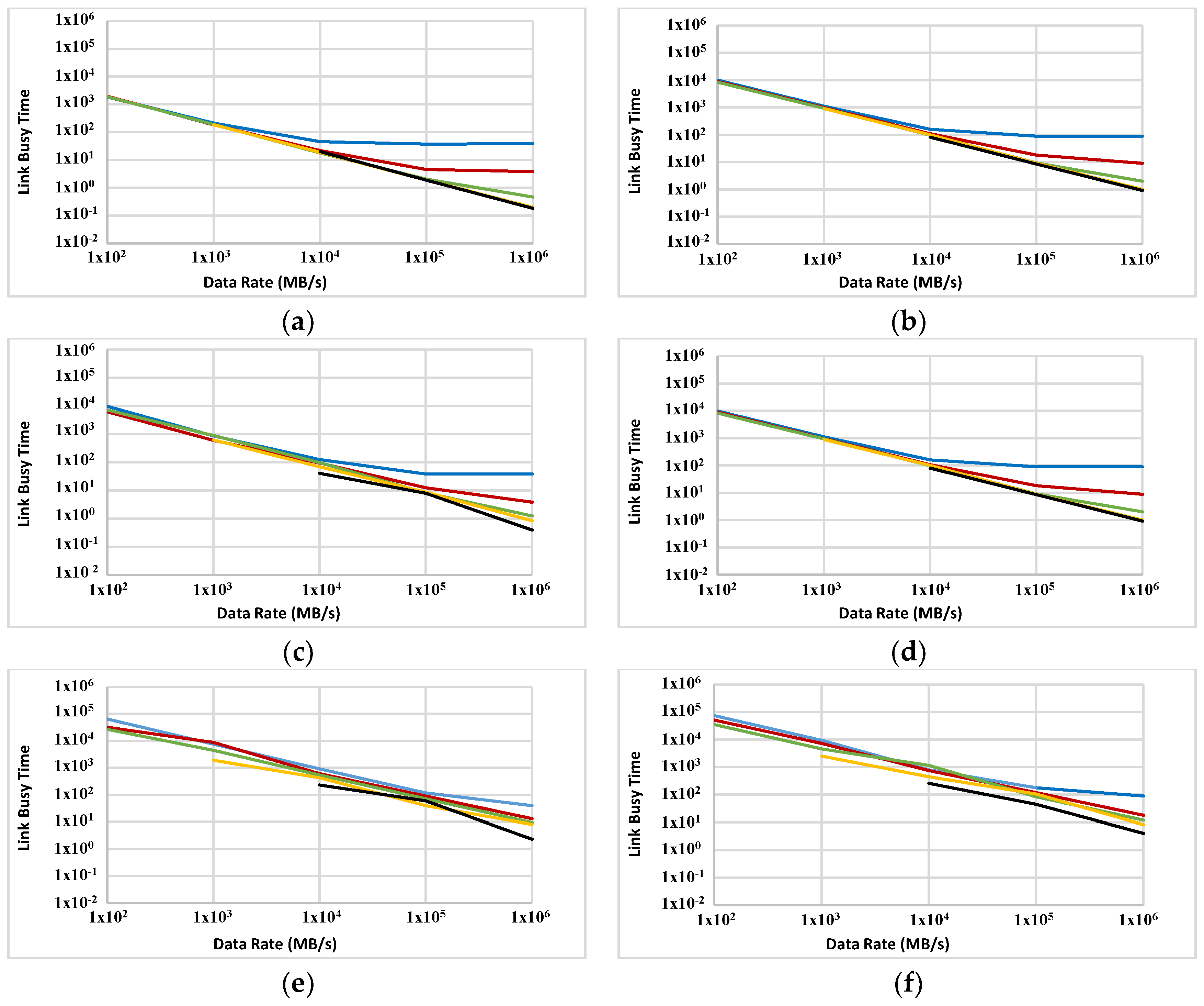

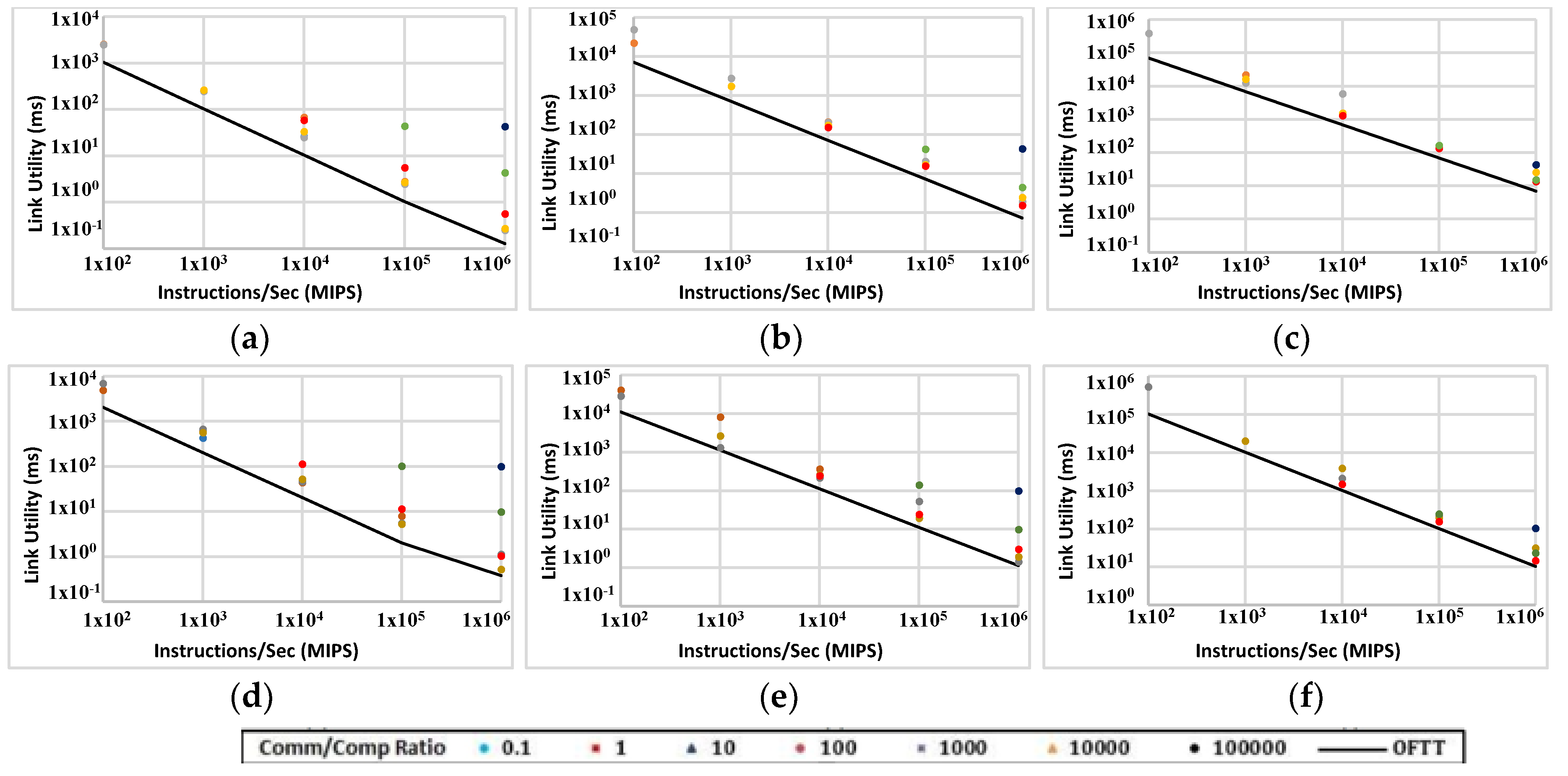

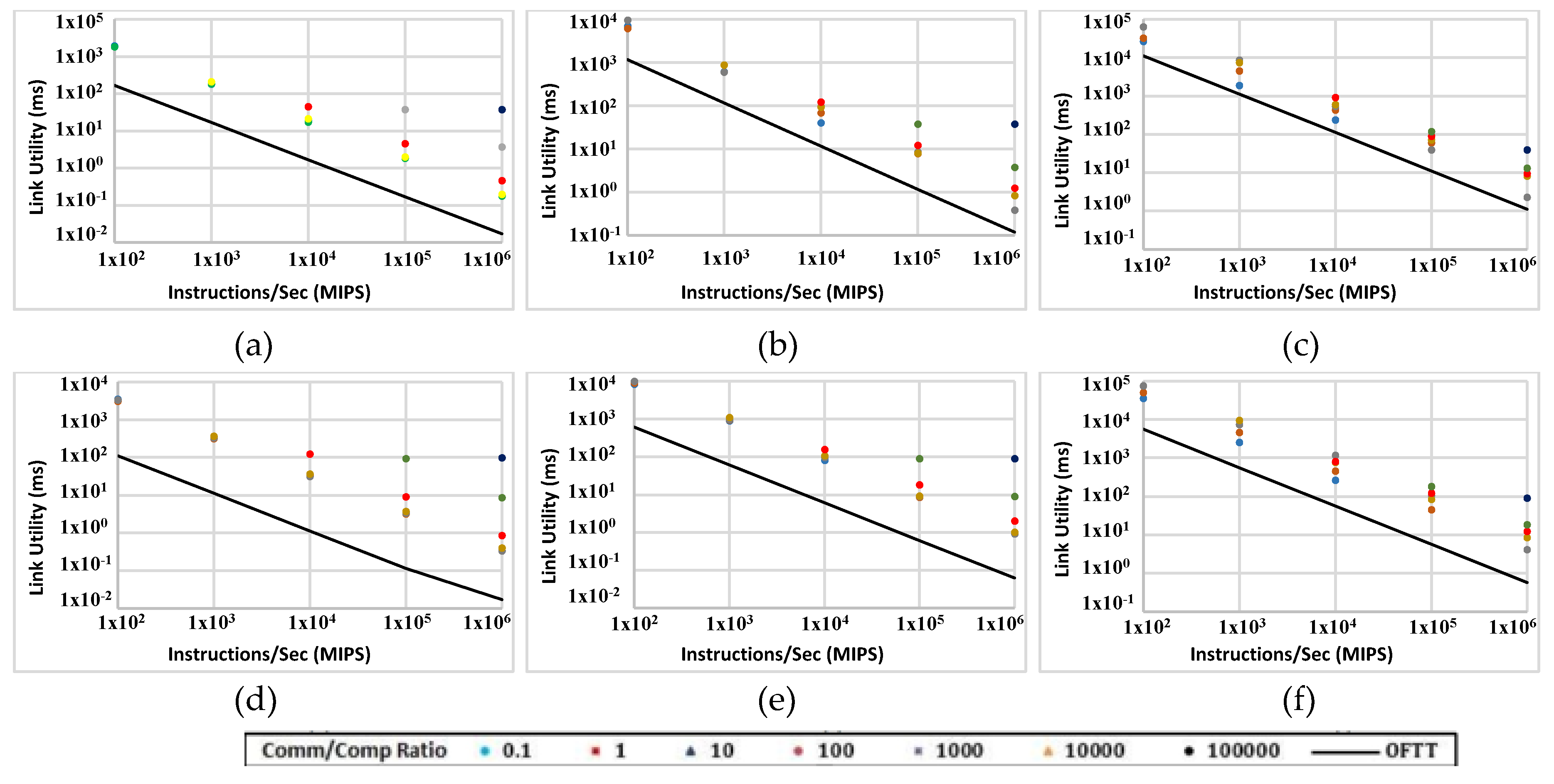

3.2. Link Utilisation Analysis

3.2.1. Overall Link Busy Time

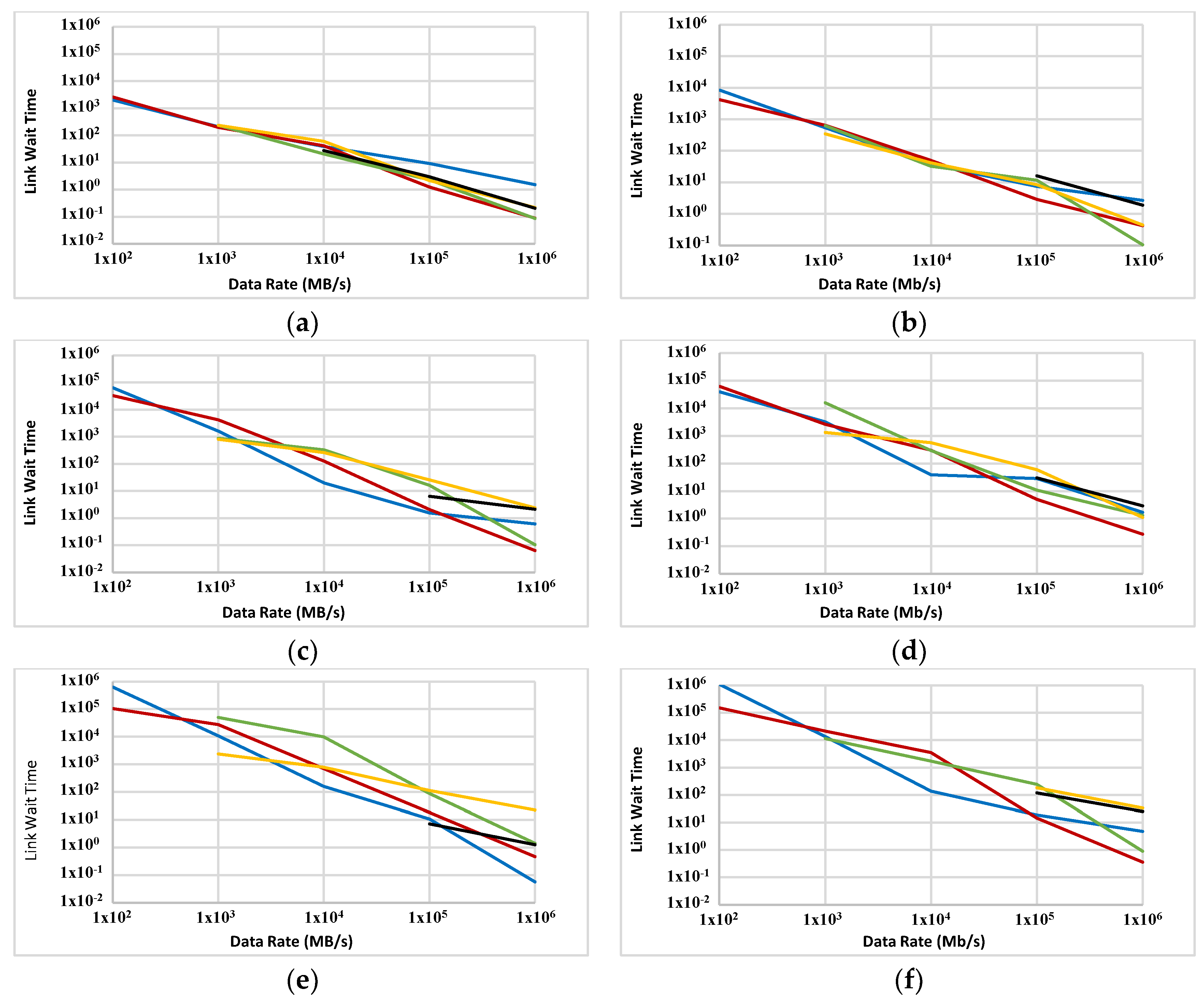

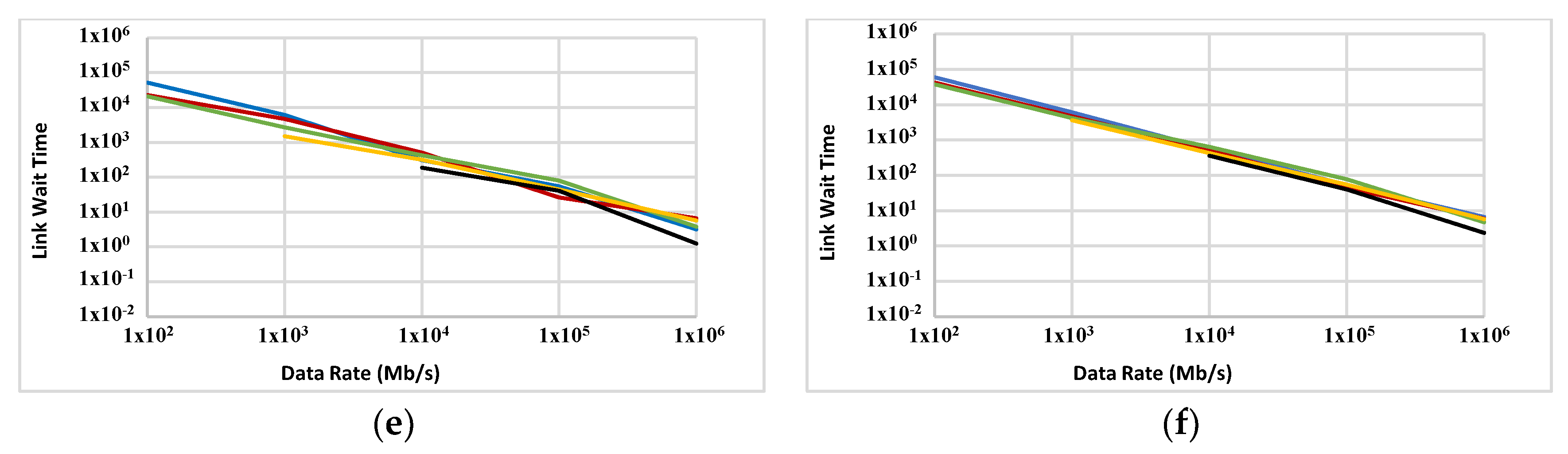

3.2.2. Overall Link Wait Time

3.2.3. Simulation Results and Overhead Effects

4. Conclusions and Future Work

Acknowledgments

Author Contributions

Conflicts of Interest

References

- Moore, B.; Sellathamby, C.; Slupsky, S.; Iniewski, K. Chip to chip communications for terabit transmission rates. In Proceedings of the IEEE Asia Pacific Conference on Circuits and Systems (APCCAS), Macao, China, 30 November–3 December 2008. [Google Scholar]

- Mamei, M.; Menezes, R.; Tolksdorf, R.; Zambonelli, F. Case studies for self-organization in computer science. J. Syst. Archit. 2006, 52, 443–460. [Google Scholar] [CrossRef]

- Vassev, E.; Sterritt, R.; Rouff, C.; Hinchey, M. Swarm Technology at NASA: Building Resilient Systems. IT Prof. 2012, 14, 36–42. [Google Scholar] [CrossRef]

- Kamali, A.M.; Crispin-Bailey, C.; Austin, J. On advantages and limitations of 3D wireless grids as parallel platforms. In Proceedings of the International Conference on Selected Topics in Mobile and Wireless Networking (MoWNeT), Montreal, QC, Canada, 19–21 August 2013. [Google Scholar]

- Kamali, A.M.; Bailey, C.; Austin, J. Evaluating 3D wireless Grids as parallel platforms. Int. J. Ad Hoc Ubiquitous Comput. 2015, 19, 279–289, in press. [Google Scholar] [CrossRef]

- Hind, R. Feasibility Study on Implementing the Ball Computer. University of York, 1 June 2014. Available online: http://etheses.whiterose.ac.uk/id/eprint/4438 (accessed on 13 July 2015).

- Kamali Sarvestani, A.M. Evaluating Techniques for Wireless Interconnected 3D Processor Arrays. 26 March 2015. Available online: http://etheses.whiterose.ac.uk/8395/ (accessed on 31 March 2015).

- Aung, M.T.L.; Lim, E.; Yoshikawa, T.; Kim, T.T.-H. Design of Simultaneous Bi-Directional Transceivers Utilizing Capacitive Coupling for 3DICs in Face-to-Face Configuration. IEEE J. Emerg. Sel. Top. Circuits Syst. 2012, 2, 257–265. [Google Scholar] [CrossRef]

- Hopkins, D.; Chow, A.; Bosnyak, R.; Coates, B.; Ebergen, J.; Fairbanks, S.; Gainsley, J.; Ho, R.; Lexau, J.; Liu, F.; et al. Circuit Techniques to Enable 430Gb/s/mm2 Proximity Communication. In Proceedings of the IEEE International Solid-State Circuits Conference, San Fransisco, CA, USA, 11–15 Feburary 2007. [Google Scholar]

- Canegallo, R.; Perugini, L.; Pasini, A.; Innocenti, M.; Scandiuzzo, M.; Guerrieri, R.; Rolandi, P. System on Chip with 1.12mW-32Gb/s AC-Coupled 3D Memory Interface. In Proceedings of the IEEE Custom Intergrated Circuits Conference (CICC), Rome, Italy, 13–16 September 2009. [Google Scholar]

- Matsubara, T.; Hayashi, I.; Johari, A.H.; Kumaki, S.; Kohira, K.; Kuroda, T.; Ishikuro, H. An 0.5 V, 0.91 pJ/bit, 1.1 Gb/s/ch Transceiver in 65 nm CMOS for High-Speed Wireless Proximity Interface. In Proceedings of the IEEE Radio and Wireless Symposium (RWS), Phoenix, AZ, USA, 16–19 Janurary 2011. [Google Scholar]

- Miura, N.; Kasuga, K.; Saito, M.; Kuroda, T. An 8 Tb/s 1 pJ/b 0.8 mm2/Tb/s QDR Inductive-Coupling Interface Between 65 nm CMOS GPU and 0.1 μm DRAM. In Proceedings of the IEEE International Solid-State Circuits Conference, San Fransisco, CA, USA, 7–11 Feburary 2010. [Google Scholar]

- Lee, S.; Song, K.; Yoo, J.; Yoo, H.-J. A Low-Energy Inductive Coupling Transceiver With Cm-Range 50-Mbps Data Communication in Mobile Device Applications. IEEE J. Solid-State Circuits 2010, 45, 2366–2374. [Google Scholar] [CrossRef]

- Defrem, N.; Reynaert, P. A 120 GHz 10 Gb/s Phase-Modulating Transmitter in 65 nm LP CMOS. In Proceedings of the IEEE International Solid-State Circuits Conference, San Fransisco, CA, USA, 20–24 Feburary 2011. [Google Scholar]

- Katayama, K.; Motoyoshi, M.; Takano, K.; Ono, N.; Fujishima, M. 28 mW 10 Gbps Transmitter for 120 GHz ASK Transceiver. In Proceedings of the IEEE International Microwave Symposium, Montréal, QC, Canada, 17–22 June 2012. [Google Scholar]

- Hu, S.; Xiong, Y.-Z.; Zhang, B.; Wang, L.; Lim, T.-G.; Je, M.; Madihian, M. A SiGe BiCMOS Transmitter/Receiver Chipset with On-Chip SIW Antennas for Terahertz Applications. IEEE J. Solid-State Circuits 2012, 47, 2654–2664. [Google Scholar] [CrossRef]

- Ishigaki, K.; Shiraishi, M.; Suzuki, S.; Asada, M.; Nishiyama, N.; Arai, S. Direct intensity modulation and wireless data transmission characteristics of terahertz-oscillating resonant tunnelling diodes. Electron. Lett. 2012, 48, 582–583. [Google Scholar] [CrossRef]

- Foulon, S.; Pruvost, S.; Loyez, C.; Rolland, N.; Avramovic, V. A 10 GBits/s 2.1 pJ/bit OOK demodulator at 60 GHz for chip-to-chip wireless communication. In Proceedings of the IEEE Radio and Wireless Symposium, Santa Clara, CA, USA, 15–18 Janurary 2012. [Google Scholar]

- Miyashita, D.; Agawa, K.; Kajihara, H.; Sami, K.; Iwanaga, M.; Ogasawara, Y.; Ito, T.; Kurose, D.; Koide, N.; Hashimoto, T.; et al. A-70dBm-Sensitivity 522 Mbps 0.19 nJ/bit-TX 0.43 nJ/bit-RX Transceiver for TransferJet™ SoC in 65 nm CMOS. In Proceedings of the IEEE Symposium on VLSI Circuits, Honolulu, HI, USA, 13–15 June 2012. [Google Scholar]

- Kanda, K.; Antono, D.D.; Ishida, K.; Kawaguchi, H.; Kuroda, T.; Sakurai, T. 1.27 Gb/s/pin 3 mW/pin Wireless Superconnect (WSC) Interface Scheme. In Proceedings of the IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 13 Feburary 2003. [Google Scholar]

- Drost, R.J.; Hopkins, R.D.; Ho, R.; Sutherland, I.E. Proximity Communication. IEEE J. Solid-State Circuits 2004, 39, 1529–1535. [Google Scholar] [CrossRef]

- Fazzi, A.; Magagni, L.; Mirandola, M.; Canegallo, R.; Schmitz, S.; Guerrieri, R. A 0.14 mW/Gbps High-Density Capacitive Interface for 3D System Integration. In Proceedings of the IEEE Custom Integrated Circuits Conference, San Jose, CA, USA, 21 September 2005. [Google Scholar]

- Canegallo, R.; Fazzi, A.; Ciccarelli, L.; Magagni, L.; Natali, F.; Rolandi, P.; Jung, E.; Di Cioccio, L.; Guerrieri, R. 3D Capacitive Interconnections for High Speed Interchip Communication. In Proceedings of the IEEE Custom Intergrated Circuits Conference (CICC), San Jose, CA, USA, 16–19 September 2007. [Google Scholar]

- Miura, N.; Mizoguchi, D.; Binti Yusof, Y.; Sakurai, T.; Kuroda, T. Analysis and Design of Transceiver Circuit and Inductor Layout for Inductive Inter-chip Wireless Superconnect. In Proceedings of the Symposium on VLSl Circuit, Honolulu, HI, USA, 17–19 June 2004. [Google Scholar]

- Sasaki, M.; Iwata, A. A 0.95 mW/1.0 Gbps Spiral-Inductor Based Wireless Chip-Interconnect with Asynchronous Communication Scheme. In Proceedings of the IEEE Symposium on VLSI Circuits, Kyoto, Japan, 16–18 June 2005. [Google Scholar]

- Miura, N.; Ishikuro, H.; Sakurai, T.; Kuroda, T. A 0.14 pJ/b Inductive-Coupling Inter-Chip Data Transceiver with Digitaly-Controlled Precise Pulse Shaping. In Proceedings of the IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 11–15 Feburary 2007. [Google Scholar]

- Lee, S.; Yoo, J.; Yoo, H.-J. A 200 Mbps 0.02 nJ/b dual-mode inductive coupling transceiver for cm-range interconnection. In Proceedings of the IEEE International Symposium on Circuits and Systems (ISCAS), Seattle, WA, USA, 18–21 May 2008. [Google Scholar]

- Lee, S.; Yoo, J.; Song, K.; Yoo, H.-J. A 1.3 pJ/b Inductive Coupling Transceiver with Adaptive Gain Control for Cm-range 50 Mbps Data Communication. In Proceedings of the IEEE Asian Solid-State Circuits Conference, Taipei, Taiwan, 16–18 November 2009. [Google Scholar]

- Terada, T.; Yoshizumi, S.; Sanada, Y.; Kuroda, T. Transceiver Circuits for pulse-based ultra-wideband. In Proceedings of the International Symposium on Circuits and Systems (ISCAS), Vancouver, BC, Canada, 23–26 May 2004. [Google Scholar]

- Terada, T.; Yoshizumi, S.; Sanada, Y.; Kuroda, T. A CMOS impulse radio ultra-wideband transceiver for 1 Mb/s data communications and ±2.5 cm range findings. In Proceedings of the Symposium on VLSI Circuits, Kyoto, Japan, 16–18 June 2005. [Google Scholar]

- Reynolds, S.K.; Floyd, B.A.; Pfeiffer, U.R.; Beukema, T.; Grzyb, J.; Haymes, C.; Gaucher, B.; Soyuer, M. A Silicon 60-GHz Receiver and Transmitter Chipset for Broadband Communications. IEEE J. Solid-State Circuits 2006, 41, 2820–2831. [Google Scholar] [CrossRef]

- Sarkar, S.; Laskar, J. A Single-Chip 25 pJ/bit Multi-Gigabit 60 GHz Receiver Module. In Proceedings of the IEEE/MTT-S International Microwave Symposium, Honolulu, HI, USA, 3–8 June 2007. [Google Scholar]

- Tomkins, A.; Aroca, R.A.; Yamamoto, T.; Nicolson, S.T.; Doi, Y.; Voinigescu, S.P. A Zero-IF 60 GHz Transceiver in 65 nm CMOS with > 3.5 Gb/s Links. In Proceedings of the IEEE CustomIntegrated Circuits Conference, San Jose, CA, USA, 21–24 September 2008. [Google Scholar]

- Marcu, C.; Chowdhury, D.; Thakkar, C.; Kong, L.-K.; Tabesh, M.; Park, J.-D.; Wang, Y.; Afshar, B.; Gupta, A.; Arbabian, A.; et al. A 90 nm CMOS Low-Power 60 GHz Transceiver with Integrated Baseband Circuitry. IEEE J. Solid-State Circuits 2009, 44, 3434–3447. [Google Scholar] [CrossRef]

- Cohen, E.; Jakobson, C.; Ravid, S.; Ritter, D. A thirty two element phased-array transceiver at 60 GHz with RF-IF conversion block in 90 nm flip chip CMOS process. In Proceedings of the IEEE Radio Frequency Integrated Circuits Symposium, Anaheim, CA, USA, 23–25 May 2010. [Google Scholar]

- Okada, K.; Li, N.; Matsushita, K.; Bunsen, K.; Murakami, R.; Musa, A.; Sato, T.; Asada, H.; Takayama, N.; Ito, S.; et al. A 60-GHz 16QAM/8PSK/QPSK/BPSK Direct-Conversion Transceiver for IEEE802.15.3c. IEEE J. Solid-State Circuits 2011, 46, 2988–3004. [Google Scholar] [CrossRef]

- Thakkar, C.; Kong, L.; Jung, K.; Frappé, A.; Alon, E. A 10 Gb/s 45 mW Adaptive 60 GHz Baseband in 65 nm CMOS. IEEE J. Solid-State Circuits 2012, 47, 952–968. [Google Scholar] [CrossRef]

- Deb, S.; Ganguly, A.; Chang, K.; Pande, P.; Belzer, B.; Heo, D. Enhancing Performance of Network-on-Chip Architectures with Millimeter-Wave Wireless Interconnects. In Proceedings of the 21st IEEE International Conference on Application-specific Systems Architectures and Processors (ASAP), Rennes, France, 7–9 July 2010. [Google Scholar]

- Kawasaki, K.; Akiyama, Y.; Komori, K.; Uno, M.; Takeuchi, H.; Itagaki, T.; Hino, Y.; Kawasaki, Y.; Ito, K.; Hajimiri, A. A Millimeter-Wave Intra-Connect Solution. IEEE J. Solid-State Circuits 2010, 45, 2655–2666. [Google Scholar] [CrossRef]

- Yu, X.; Sah, S.P.; Deb, S.; Pande, P.P.; Belzer, B.; Heo, D. A Wideband Body-Enabled Millimeter-Wave Transceiver for Wireless Network-on-Chip. In Proceedings of the IEEE 54th International Midwest Symposium on Circuits and Systems (MWSCAS), Seoul, Korea, 7–10 August 2011. [Google Scholar]

- Fukuda, S.; Hino, Y.; Ohashi, S.; Takeda, T.; Yamagishi, H.; Shinke, S.; Komori, K.; Uno, M.; Akiyama, Y.; Kawasaki, K.; et al. A 12.5+12.5 Gb/s Full-Duplex Plastic Waveguide Interconnect. IEEE J. Solid-State Circuits 2011, 46, 3113–3125. [Google Scholar] [CrossRef]

- Tanaka, Y.; Hino, Y.; Okada, Y.; Takeda, T.; Ohashi, S.; Yamagishi, H.; Kawasaki, K.; Hajimiri, A. A Versatile Multi-Modality Serial Link. In Proceedings of the IEEE International Solid-State Circuits Conference, San Fransisco, CA, USA, 19–23 Feburary 2012. [Google Scholar]

- Byeon, C.W.; Yoon, C.H.; Park, C.S. A 67-mW 10.7-Gb/s 60-GHz OOK CMOS Transceiver for Short-Range Wireless Communications. IEEE Trans. Microw. Theory Tech. 2013, 61, 3391–3401. [Google Scholar] [CrossRef]

- Yu, X.; Sah, S.P.; Rashtian, H.; Mirabbasi, S.; Pande, P.P.; Heo, D. A 1.2-pJ/bit 16-Gb/s 60-GHz OOK Transmitter in 65-nm CMOS for Wireless Network-On-Chip. IEEE Trans. Microw. Theory Tech. 2014, 62, 2357–2369. [Google Scholar] [CrossRef]

- Nakajima, K.; Maruyama, A.; Kohtani, M.; Sugiura, T.; Otobe, E.; Lee, J.; Cho, S.; Kwak, K.; Lee, J.; Yoshimasu, T.; et al. 23 Gbps 9.4 pJ/bit 80/100 GHz band CMOS transceiver with on-board antenna for short-range communication. In Proceedings of the Solid-State Circuits Conference (A-SSCC), KaoHsiung, Taiwan, 10–12 November 2014. [Google Scholar]

- Yu, X.; Rashtian, H.; Mirabbasi, S.; Pande, P.P.; Heo, D. An 18.7-Gb/s 60-GHz OOK Demodulator in 65-nm CMOS for Wireless Network-on-Chip. IEEE Trans. Circuits Syst. I Regul. Pap. 2015, 62, 799–806. [Google Scholar] [CrossRef]

- Lee, H.J.; Lee, J.G.; Lee, C.J.; Jang, T.H.; Kim, H.J.; Park, C.S. High-speed and low-power OOK CMOS transmitter and receiver for wireless chip-to-chip communication. In Proceedings of the 2015 IEEE MTT-S International Microwave Workshop Series on Advanced Materials and Processes for RF and THz Applications (IMWS-AMP), Suzhou, China, 1–3 July 2015. [Google Scholar]

- Rabaey, J. Short-Distance Wireless and Its Opportunities. In Wireless Technologies: Circuits, Systems and Devices; CRC Press: Boca Raton, FL, USA, 2007. [Google Scholar]

- Intel. Switches, What Are Forwarding Modes and How Do They Work? 17 April 2014. Available online: http://www.intel.com/support/express/switches/sb/cs-014410.htm (accessed on 1 April 2015).

- Gauss, C.F. Intersuchungen über die Eigenschaften der Positiven Ternären Quadratischen Formen Usw. Göttingsche Gelehrte Anzeigen 1831, 9, 1065. [Google Scholar]

| Ref. | Data Rate (Gb/s) | Range (mm) | Power (mW) | Energy/Bit (pJ/b) | Energy/Bit/Dist (pJ/b/mm) |

|---|---|---|---|---|---|

| [38] | 16 | 20 | 90 | 5.63 | 0.0141 |

| [39] | 11 | 14 | 70 | 6.4 | 0.0327 |

| [40] | 16 | 15 | 26.7 | 1.67 | 0.0074 |

| [41] | 25 | 120 | 140 | 5.6 | 0.0004 |

| [18] | 10 | 10 | 21 | 2.1 | 0.021 |

| [42] | 26 | 120 | 137 | 5.27 | 0.0004 |

| [42] | 20 | 5 | 137 | 5.85 | 0.234 |

| [43] | 10.7 | 100 | 67 | 6.26 | 0.0006 |

| [44] | 16 | 20 | 19 | 1.2 | 0.003 |

| [45] | 23 | 100 | 216 | 9.4 | 0.0009 |

| [46] | 18.7 | 20 | 4.6 | 0.25 | 0.0006 |

| [47] | 12 | 12 | 64 | 4.5 | 0.0313 |

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kamali Sarvestani, A.M.; Bailey, C.; Austin, J. Performance Analysis of a 3D Wireless Massively Parallel Computer. J. Sens. Actuator Netw. 2018, 7, 18. https://doi.org/10.3390/jsan7020018

Kamali Sarvestani AM, Bailey C, Austin J. Performance Analysis of a 3D Wireless Massively Parallel Computer. Journal of Sensor and Actuator Networks. 2018; 7(2):18. https://doi.org/10.3390/jsan7020018

Chicago/Turabian StyleKamali Sarvestani, Amir Mansoor, Christopher Bailey, and Jim Austin. 2018. "Performance Analysis of a 3D Wireless Massively Parallel Computer" Journal of Sensor and Actuator Networks 7, no. 2: 18. https://doi.org/10.3390/jsan7020018