A High-Density Memory Design Based on Self-Aligned Tunneling Window for Large-Capacity Memory Application

Abstract

:1. Introduction

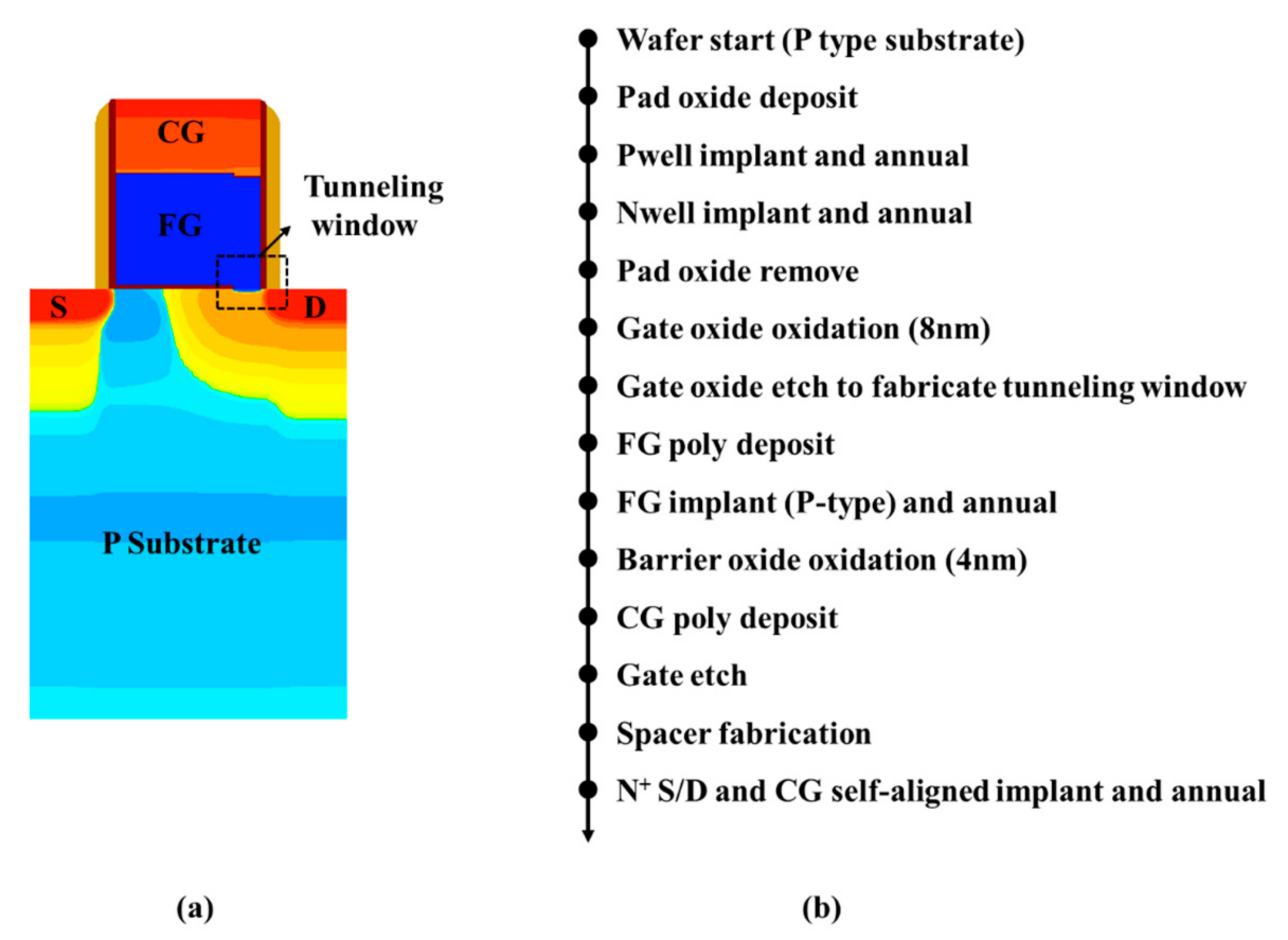

2. Device Structure and Main Process of HDM

3. Simulation Results and Discussion

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Nayak, D.; Acharya, D.P.; Mahapatra, K. A Read Disturbance Free Differential Read SRAM Cell for Low Power and Reliable Cache in Embedded Processor. AEU Int. J. Electron. Commun. 2017, 74, 192–197. [Google Scholar] [CrossRef]

- Kim, T.H.; Jeong, H.; Park, J.; Kim, H.; Song, T.; Jung, S.-O. An Embedded Level-Shifting Dual-Rail SRAM for High-Speed and Low-Power Cache. IEEE Access 2020, 8, 187126–187139. [Google Scholar] [CrossRef]

- Prasad, G.; Tandon, D.; Isha; Mandi, B.C.; Ali, M. Process Variation Analysis of 10T SRAM Cell for Low Power, High Speed Cache Memory for IoT Applications. In Proceedings of the 2020 7th International Conference on Signal Processing and Integrated Networks (SPIN), Noida, India, 27–28 February 2020. [Google Scholar] [CrossRef]

- Kerber, P.; Zhang, Q.; Koswatta, S.; Bryant, A. GIDL in Doped and Undoped FinFET Devices for Low-Leakage Applications. IEEE Trans. Electron. Devices 2012, 34, 154–159. [Google Scholar] [CrossRef]

- Lee, J.-M.; Choi, P.-H.; Kim, S.-K.; Oh, J.-H.; Shin, S.-H.; Noh, J.-Y.; Kim, H.-S.; Choi, B.-D. New Method for Reduction of the Capacitor Leakage Failure Rate Without Changing the Capacitor Structure or Materials in DRAM Mass Production. IEEE Trans. Electron. Devices 2018, 65, 4839–4845. [Google Scholar] [CrossRef]

- Yoshida, E.; Tanaka, T. A capacitorless 1T-DRAM technology using gate-induced drain-leakage (GIDL) current for low-power and high-speed embedded memory. IEEE Trans. Electron. Devices 2006, 53, 692–697. [Google Scholar] [CrossRef]

- Kim, K.; Jeong, M.-Y. The COB stack DRAM cell at technology node below 100 nm-scaling issues and directions. IEEE Trans. Semicond. Manuf. 2002, 15, 137–143. [Google Scholar] [CrossRef]

- Chen, J.-H.; Wong, S.-C.; Wang, Y.-H. An analytic three-terminal band-to-band tunneling model on GIDL in MOSFET. IEEE Trans. Electron. Devices 2001, 48, 1400–1405. [Google Scholar] [CrossRef]

- Wang, T.; Chang, T.-E.; Chiang, L.-P.; Wang, C.-H.; Zous, N.-K.; Huang, C. Investigation of oxide charge trapping and detrapping in a MOSFET by using a GIDL current technique. IEEE Trans. Electron. Devices 1998, 45, 1511–1517. [Google Scholar] [CrossRef]

- Mandelman, J.A.; Dennard, R.; Bronner, G.; Divakaruni, J.D.R.; Radens, C. Challenges and future directions for the scaling of dynamic random-access memory (DRAM). IBM J. Res. Dev. 2002, 46, 187–212. [Google Scholar] [CrossRef]

- Choi, S.-J.; Han, J.-W.; Moon, D.-I.; Choi, Y.-K. Analysis and evaluation of a BJT-based 1T-DRAM. IEEE Electron Device Lett. 2010, 31, 393–395. [Google Scholar] [CrossRef]

- Sentaurus User’s Manual; ver C-2013.03; Synopsys, Inc.: Mountain View, CA, USA, 2013; Available online: https://picture.iczhiku.com/resource/eetop/wYItAzFDYgQzfNvV.pdf (accessed on 20 May 2021).

- Hisamoto, D.; Kimura, S.; Kaga, T.; Nakagome, Y.; Isoda, M.; Nishida, T.; Takeda, E. A New Stacked Cell Structure for Giga-Bit DRAMs Using Vertical Ultra-Thin SO1 (DELTA) MOSFETs. In Proceedings of the International Electron Devices Meeting 1991 [Technical Digest], Washington, DC, USA, 8–11 December 1991; pp. 959–961. [Google Scholar]

- Wang, P.; Lin, X.; Liu, L.; Sun, Q.; Zhou, P.; Liu, X.; Liu, W.; Gong, Y.; Zhang, D.W. A Semi-Floating Gate Transistor for Low-Voltage Ultrafast Memory and Sensing Operation. Science 2013, 341, 640–643. [Google Scholar] [CrossRef] [PubMed]

- Jiang, S.Y.; Yuan, Y.; Wang, X.; Chen, L.; Zhu, H.; Sun, Q.Q.; Zhang, D.W. A Semi-Floating Gate Transistor with Enhanced Embedded Tunneling Field-Effect Transistor. IEEE Electron Device Lett. 2018, 39, 1497–1499. [Google Scholar]

- Lin, X.; Liu, X.Y.; Zhang, C.M.; Liu, L.; Shi, J.S.; Zhang, S.; Wang, W.B.; Bu, W.H.; Wu, J.; Gong, Y.; et al. Investigation of temperature dependence device scalability and modeling of semifloating-gate transistor memory cell. IEEE Trans. Electron Devices 2015, 62, 1177–1183. [Google Scholar] [CrossRef]

- Wan, J.; Le Royer, C.; Zaslavsky, A.; Cristoloveanu, S. Progress in Z2-FET 1T-DRAM: Retention time, writing modes, selective array operation, and dual bit storage. Solid State Electron. 2013, 84, 147–154. [Google Scholar] [CrossRef]

| Erase | Write0 | Write1 | Read | Retention | |

|---|---|---|---|---|---|

| VCG (V) | 1.2 | −1.5 | −1.5 | 0.6 | 0.0 |

| VD (V) | 0.6 | 1.2 | 0.6 | 0.6 | 0.6 |

| VS (V) | 0.0 | 0.0 | 0.0 | 0.0 | 0.0 |

| VBluk (V) | 0.0 | 0.0 | 0.0 | 0.0 | 0.0 |

| Time (ns) | 5.0 | 5.0 | 5.0 | 5.0 | 5.0 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wang, C.; Zhao, X.; Liu, H.; Chao, X.; Zhu, H.; Sun, Q. A High-Density Memory Design Based on Self-Aligned Tunneling Window for Large-Capacity Memory Application. Electronics 2021, 10, 1954. https://doi.org/10.3390/electronics10161954

Wang C, Zhao X, Liu H, Chao X, Zhu H, Sun Q. A High-Density Memory Design Based on Self-Aligned Tunneling Window for Large-Capacity Memory Application. Electronics. 2021; 10(16):1954. https://doi.org/10.3390/electronics10161954

Chicago/Turabian StyleWang, Chen, Xiuli Zhao, Hao Liu, Xin Chao, Hao Zhu, and Qingqing Sun. 2021. "A High-Density Memory Design Based on Self-Aligned Tunneling Window for Large-Capacity Memory Application" Electronics 10, no. 16: 1954. https://doi.org/10.3390/electronics10161954

APA StyleWang, C., Zhao, X., Liu, H., Chao, X., Zhu, H., & Sun, Q. (2021). A High-Density Memory Design Based on Self-Aligned Tunneling Window for Large-Capacity Memory Application. Electronics, 10(16), 1954. https://doi.org/10.3390/electronics10161954