MDPI

Article

# New n-p Junction Floating Gate to Enhance the Operation Performance of a Semiconductor Memory Device

Yi-Yueh Chen \* D, Su-Jien Lin and Shou-Yi Chang

Department of Materials Science and Engineering, National Tsing Hua University, Hsinchu 30013, Taiwan; sjlin@mx.nthu.edu.tw (S.-J.L.); changsy@mx.nthu.edu.tw (S.-Y.C.)

\* Correspondence: yychen@mxic.com.tw; Tel.: +886-3-578-6688

Abstract: To lower the charge leakage of a floating gate device and improve the operation performance of memory devices toward a smaller structure size and a higher component capability, two new types of floating gates composed of pn-type polysilicon or np-type polysilicon were developed in this study. Their microstructure and elemental compositions were investigated, and the sheet resistance, threshold voltages and erasing voltages were measured. The experimental results and charge simulation indicated that, by forming an n-p junction in the floating gate, the sheet resistance was increased, and the charge leakage was reduced because of the formation of a carrier depletion zone at the junction interface serving as an intrinsic potential barrier. Additionally, the threshold voltage and erasing voltage of the np-type floating gate were elevated, suggesting that the performance of the floating gate in the operation of memory devices can be effectively improved without the application of new materials or changes to the physical structure.

Keywords: semiconductor device; memory cell; floating gate; n-p junction; charge leakage

Citation: Chen, Y.-Y.; Lin, S.-J.; Chang, S.-Y. New n-p Junction Floating Gate to Enhance the Operation Performance of a Semiconductor Memory Device. *Materials* 2022, 15, 3640. https://doi.org/10.3390/ma15103640

Academic Editors: Zhenghua Tang, Marc Cretin and Sophie Tingry

Received: 1 April 2022 Accepted: 16 May 2022 Published: 19 May 2022 Corrected: 28 September 2022

**Publisher's Note:** MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations

Copyright: © 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

## 1. Introduction

Memory devices, one of the most typical and popularly used electronic devices, generally comprise a plurality of gate structures, which include a control gate and a floating gate [1,2]. The floating gate is a conductive layer normally fabricated from polysilicon that is positioned between the control gate and a silicon substrate [1,2]. The floating gate is not attached to any electrodes or power sources and is generally surrounded by an insulation material [1,2]. The operation of the memory cells is dependent upon the charge stored in the floating gate at the threshold voltage to represent information in these memory devices [3,4]. The performance of the memory cells is determined by the programming speed, which is dominated by the speed of the erasing and writing operations [1,2]. The speed is basically limited by the rate at which electrons can be pumped into (writing) and out of (erasing) the devices without causing damage to the device [1,5–7]. Typically, writing and erasing operations must be capable of operating within 1 ms at a specified applied voltage [1,6,8–11].

Aiming at a higher capability but a smaller chip size, the semiconductor industry has been increasingly driven towards smaller and more numerous electronic devices, including memory cells [2,12,13]. To reduce the size and accordingly increase the number of such devices, while simultaneously maintaining or even improving their respective capabilities, the size of components and the distance between such components need to be reduced [2,14,15]. However, as the cell size is reduced, some other issues arise that prevent a further reduction in size [15,16]. One of these issues is that charge leakage from the floating gate may increase, thereby deteriorating the performance of the devices as the individual layers of the gate structures are made smaller and placed closer to each other [15]. In particular, the tunneling oxide will be more seriously damaged with more programming and erasing sequences, resulting in more charge leakage [15]. In order to overcome the issue

Materials **2022**. 15, 3640 2 of 10

of charge leakage, many device structures have been proposed, e.g., SONOS, BE-SONOS, TAHOS and 3D FLASH [6,17–20]. The 3D NAND FLASH structure was proposed as a solution when 2D NAND FLASH reached the scaling limit of a 15 nm process node [21]. Furthermore, the ReRAM [8,22], PCRAM [23,24], FeRAM [25,26] and MRAM [27,28] devices have also attracted much attention in the past two decades as promising candidates for the next generation of nonvolatile memory cells with improved performance. However, new semiconductor devices with markedly shrunken gate structures and reduced charge leakage that do not sacrifice their performance or suffer from environmental contamination are still elusive.

Hence, in this study, two new floating gate structures, including a p-n junction and an n-p junction, were designed, investigated and processed on 300 mm wafers. In these new designs, no extra new material needs to be employed, no new process needs to be developed and no contamination risk needs to be considered when the devices are processed at the semiconductor manufacturing factory. By forming an n-p junction instead of a p-n junction in the first conductive layer (the floating gate), the charge leakage across the second dielectric layer (the inter-polysilicon dielectric layer) may be reduced. This n-p junction interface is anticipated to provide an intrinsic potential barrier to inhibit the leakage path, successfully reducing the charge leakage and enlarging the programming and erasing window. Additionally, upon the reduction of the charge leakage across the second dielectric layer, the second dielectric layer can be made thinner and/or even be completely removed from wrapping the first conductive layer. The gate structure can thereby be made more compact, allowing a smaller semiconductor device without sacrificing the performance of the device.

#### 2. Materials and Methods

#### 2.1. Device Fabrication

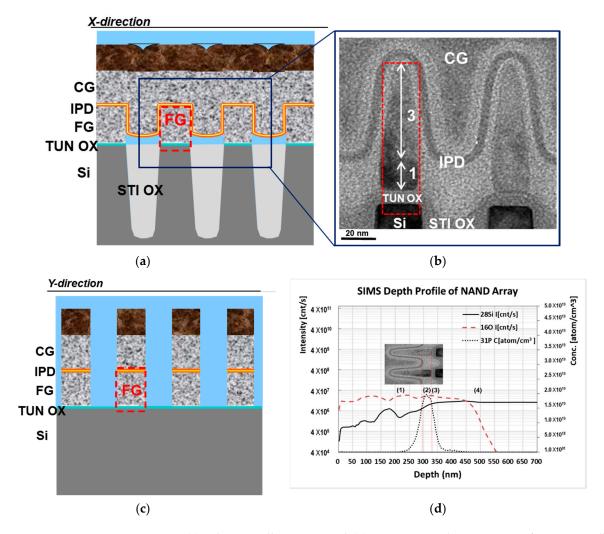

NAND FLASH memory devices with two new floating gate structures were fabricated on p-type 300 mm silicon (Si) wafers with n<sup>+</sup> junctions. As shown in Figure 1, the memory devices comprise the Si substrate, the first dielectric layer (tunneling oxide, denoted as TUN OX) disposed along the substrate, and the first conductive layer (floating gate, FG) disposed along the first dielectric layer (Figure 1a,c, schematically illustrated from the Xand Y-direction cross-sections, respectively). The second dielectric layer (inter-polysilicon dielectric, IPD) is disposed along the sidewall of the first conductive layer, and the second conductive layer (control gate, CG, such as n-type polysilicon) is afterwards deposited. Two new types of the first conductive layer, i.e., the floating gate, were proposed, including the pn-type (a bottom "p+" region followed by a top "n+" region) polysilicon and the np-type (bottom " $n^+$ " followed by top " $p^+$ ") polysilicon, for which a high-temperature chemical vapor deposition (CVD) boron-doping polysilicon process and a high-temperature furnace phosphorous-doping polysilicon process were applied at 500 °C, in sequence or vice versa. The thickness ratio of the bottom-to-top regions of the pn-type or np-type polysilicon was designed to be around 1:3. For comparison, a conventional floating gate (the control split) was also prepared, with single n<sup>+</sup> polysilicon as the first conductive layer. The concentration of dopants in the n-type and p-type polysilicon was around 1  $\times$  10  $^{19}$  cm  $^{-3}$ and  $1 \times 10^{21}$  cm<sup>-3</sup>, respectively.

Materials 2022, 15, 3640 3 of 10

**Figure 1.** (a) Schematic illustration and (b) cross-sectional TEM image of memory cells around floating gates with np-type polysilicon from the X-directional view; (c) schematic illustration of memory cells from the Y-directional view; (d) SIMS depth profile of elemental distribution along the floating gate.

# 2.2. Characterization and Measurement

Thin foils (cross-sectional) of the memory devices around the floating gates were cut by using a focused ion beam system (USA, FIB, FEI Expida1265) and milled with an ultralow current, and the microstructure was observed by using a transmission electron microscope (Netherlands, TEM, FEI Osiris). The depth profile of elemental compositions along the floating gates for understanding the distribution of dopants was determined by using a secondary ion mass spectrometer (France, SIMS, AMETEK ims-6f). The sheet resistance ( $R_s$ ) of the floating gates, programing threshold voltage ( $V_{th}$ ) and erasing voltage ( $V_{er}$ ) were measured by using a WAT system (USA, Keysight, 4082F). The charge simulation of the floating gates was performed by the TCAD (Technology Computer-Aided Design).

## 3. Results and Discussion

## 3.1. Microstructure and Chemical Composition

Figure 1b shows the cross-sectional TEM microstructure of the memory cells around the floating gates with np-type polysilicon from the X-directional view. Clearly, the tunneling oxide layer is disposed between the floating gates and the substrate, and the interpolysilicon dielectric layer is uniformly deposited on the floating gates. The image contrast indicates two regions in the floating gates: the bright region at the top and the dark region

Materials 2022, 15, 3640 4 of 10

at the bottom, and the thickness ratio of the bottom-to-top regions is roughly estimated to be around 1:3. As further illustrated in Figure 1d, the SIMS depth profile along the floating gate confirms four regions of elemental distribution along the floating gate, from top to bottom: (1) the top  $p^+$  polysilicon for a thickness of about 60 nm, with a silicon element; (2) the bottom  $n^+$  polysilicon for 20 nm, with silicon and a high concentration of phosphorous dopants; (3) the tunneling oxide and (4) the silicon substrate. It was noted that in region (1), boron dopants were not present due to the improper collection condition of light-ionized boron signals from the uneven film structure of the sample instead of a planar/blanket one. However, the gradually dropping intensity of silicon might reveal the existence of other elements that were very likely boron.

## 3.2. Sheet Resistance and Charge

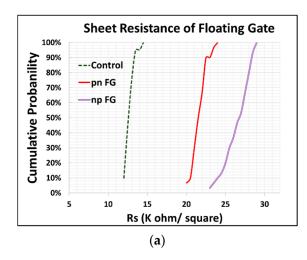

Figure 2 presents the cumulative probability plot and box plot of sheet resistance for three different floating gates, including the control split and the new pn-type and np-type floating gates. Clearly, the sheet resistance of the new floating gates was higher than that of the control split, (i.e., about 1.7 times for the pn-type floating gates and 2.1 times for the np-type floating gates), which was plausibly caused by the formation of a depletion zone and the narrowed channels for current flow. When a forward bias was applied to the np-type floating gate, or a reverse bias was applied to the pn-type floating gate, a depletion zone of carriers would be formed at the n-p or p-n junction interface [28–32], leading to an open circuit at the bottom region of the floating gates. Current flow was therefore allowed only through the top  $p^+$  or  $n^+$  polysilicon paths, respectively, and the narrowed channel would thus result in increased resistance, particularly for the np-type floating gates, as the mobility of holes in the  $p^+$  polysilicon path was lower than that of electrons in the  $n^+$  polysilicon path [29,30].

**Figure 2.** (a) Cumulative probability plot of sheet resistance of floating gates (30 data points for pn FG and np FG, and 20 data points for the control split). (b) Box plot of sheet resistance (center line: median of the data; top line: Q3, the upper quartile; bottom line: Q1, the lower quartile).

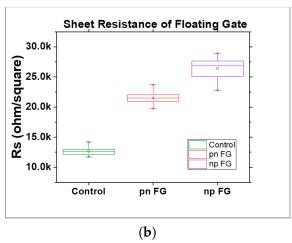

As illustrated in the band diagrams of the neutral and charged states of these three floating gates in Figure 3a,c, different band structures are expected. For the conventional n-type polysilicon floating gate (the control split, Figure 3a) at a programing voltage (positive bias,  $\Delta V$ ) applied to the control gate, the energy band near the control gate will bend downward for  $\Delta V$  to form a channel near the tunneling oxide for carriers to tunnel through the tunneling oxide into the floating gate for programming [1,2]. The charge in the floating gate depends on the gate coupling ratio (GCR) to influence the efficiency of the device programming [13,33]. In comparison, for the pn-type polysilicon floating gate (Figure 3b) and the np-type polysilicon floating gate (Figure 3c) at a thermal equilibrium state, the Fermi level (E<sub>f</sub>) is close to the valence band in the p<sup>+</sup> region (conduction by holes) and close

Materials **2022**, 15, 3640 5 of 10

to the conduction band in the  $n^+$  region (conduction by electrons). At a constant Fermi level, the distributions of carriers as well as the energy levels of the conduction band ( $E_c$ ) and valence band ( $E_v$ ) are thus different in the  $p^+$  and  $n^+$  regions at the neutral state, and a depletion zone (a thin region with very few carriers) of high electrical resistance will accordingly be formed at the p-n or n-p junction interface [29–32].

**Figure 3.** Band diagrams of the natural and charge states of (a) conventional n-type polysilicon floating gate (the control split), (b) pn-type polysilicon floating gate, and (c) np-type polysilicon floating gate. Charge simulations for (d) conventional n-type floating gate (the control split), (e) pn-type floating gate, and (f) np-type floating gate ( $V_g$  20 V: programming state,  $V_g$  0 V: retention state).

Materials 2022, 15, 3640 6 of 10

When a programming voltage  $\Delta V$  is applied to the control gate, the energy band bends downward, and the carriers will tunnel through the tunneling oxide into either the pnor the np-type floating gate in the same way as the conventional floating gate. However, owing to the different space charge distributions in the p<sup>+</sup> and n<sup>+</sup> regions, electrons stay mainly in the n<sup>+</sup> region [29,34]. The carriers (electrons) into the pn-type floating gate will induce a reverse bias in the p-n junction to cause the expansion of the depletion zone and the shrinkage of the top n<sup>+</sup> region for carrier storage, therefore reducing the total stored charge. On the contrary, in the np-type floating gate case, a forward bias will lead to the contraction of the depletion zone and the extension of the bottom n<sup>+</sup> region for carrier storage, which in turn increases the total stored charge. In addition, because the bottom n<sup>+</sup> region is close to the tunneling oxide channel and has a low energy barrier for programming, and the top p<sup>+</sup> region is adjacent to the inter-polysilicon dielectric and has a high energy barrier, the charge leakage of the control gate is expected to be inhibited, which aids in improving the programming efficiency and elevating the programming threshold voltage (V<sub>th</sub>) of the np-type floating gate as investigated below.

Furthermore, the charge simulations given in Figure 3d–f confirm the aforementioned assumption regarding charging in the three different floating gates. When the voltage applied to the control gate ( $V_g$ ) is switched from 20 V (the programming state) to 0 V (the retention state), as expected, there is no change in the amount or distribution of charge in the conventional floating gate (the control split, Figure 3d), since the n-type floating gate is simply composed of a single material (n<sup>+</sup> polysilicon). However, the charge is obviously redistributed, and a part of the charge is lost in the pn-type and np-type floating gates when the gate voltage  $V_g$  is switched. Clearly, at  $V_g$  = 20 V, the charge in the n<sup>+</sup> or p<sup>+</sup> region of the np-type floating gate is larger than that of the pn-type floating gate. At  $V_g$  = 0 V, in addition to the fact that more charge in the n<sup>+</sup> region of the np-type floating gate is retained, a portion of charge in the p<sup>+</sup> region is retained as well, suggesting that this n-p junction design in the floating gate will benefit the retention of charge, particularly because the p<sup>+</sup> region is much farther away from the tunneling oxide, making it less likely that a charge leakage will occur.

## 3.3. Threshold Voltage and Erasing Voltage

Two other important factors dominating the programming (writing) window and performance of memory devices include the threshold voltage (V<sub>th</sub>, the gate voltage required to create strong inversion under the gate when the floating gate contains the electrons [35]) and the erasing voltage (Ver, the voltage required for removing the stored charge (electrons) in the floating gates [36]). When the gate voltage is below the threshold voltage, this device is no longer in strong inversion. This region of device operation is called the "cutoff", which corresponds to a logical "0" stored in the cell [37]. A higher threshold voltage yields a wider programming window and thereafter benefits more precise control over the read operation state of the devices. For example, two states with programming threshold voltages of 4 V and 2 V define a memory window,  $\Delta V$ , of 2 V, which is clearly better than a window of 1.5 V attained in the case where the programming threshold voltages of the 0 and 1 states are, respectively, 3 V and 1.5 V. On the other hand, a higher erasing voltage is conducive for a more stable state and more effective retention of the stored charge in the memory devices. However, a higher programming threshold voltage may also cause a more serious impact on the tunneling oxide and induce larger current leakage to lower the erasing voltage.

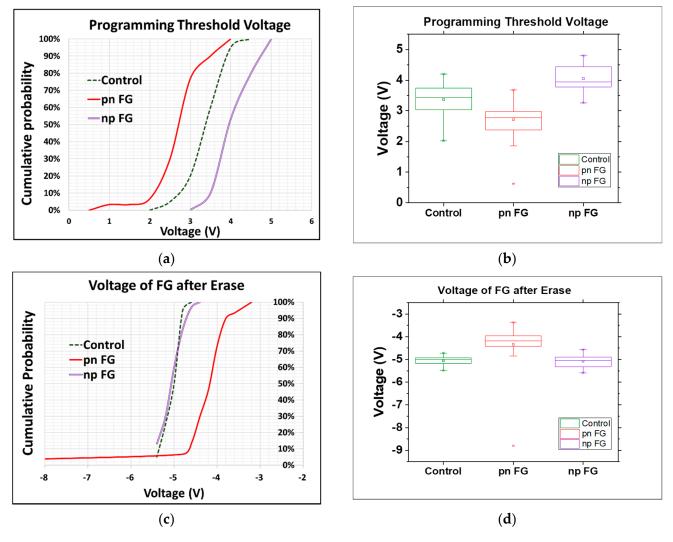

As mentioned above and presented below in Figure 4, the new types of floating gates, in particular the np-type, are observed to effectively improve the performance of the memory devices fabricated without the application of any new materials or changes to their physical structure. As clearly seen in the cumulative probability plot and box plot, the programming threshold voltage of the np-type floating gate was as high as about 1.2 times that of the conventional one (the control split) and much higher than that of the pn-type one (Figure 4a,b), while the erasing voltage of the np-type floating gate was close to that

Materials **2022**, 15, 3640 7 of 10

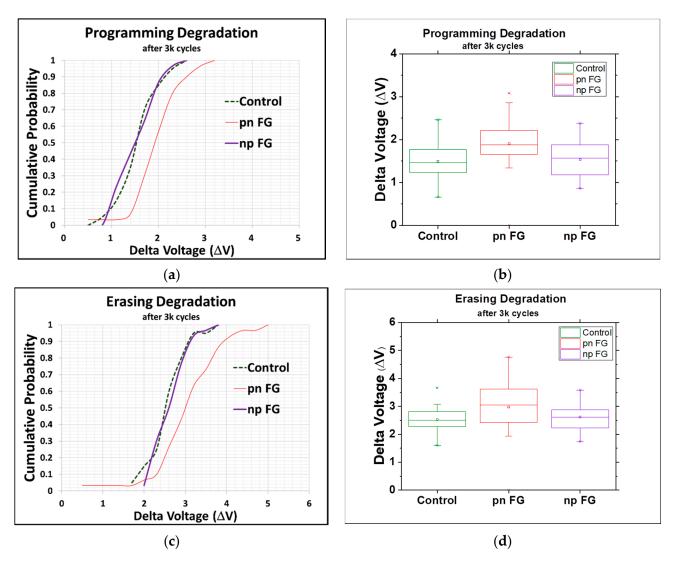

of the conventional one and also higher than that of the pn-type one, both suggesting the better performance of the np-type floating gate in controlling the operation of the memory devices (Figure 4c,d). The erasing voltages of the floating gates that we showed in Figure 4 were actually measured with a deliberately designed test key to check the floating gate state after the charges of the floating gate were cleaned up by applying a high voltage on the substrate. The lower the  $\|V_{er}\|$ , the easier it is for the cell to be turned on, which typically corresponds to a logical "1" stored in the cell. The degradations of the programming and erasing operation (after 3000 cycles) were also investigated to understand the performance of the different types of floating gates, as given in Figure 5. It was clear that the np-type floating gate showed a much better performance than the pn-type one and had the same performance as the control split, indicating no extra current leakage from the tunneling oxide even at a higher threshold voltage.

**Figure 4.** (a) Cumulative probability plot of programming threshold voltage of floating gates. (b) Box plot of programming threshold voltage. (c) Cumulative probability plot of erasing voltage of floating gates. (d) Box plot of erasing voltage (center line: median of the data; top line: Q3, the upper quartile; bottom line: Q1, the lower quartile).

Materials 2022, 15, 3640 8 of 10

**Figure 5.** (a) Cumulative probability plot of degradation of programming voltage of floating gates. (b) Box plot of degradation of programming voltage. (c) Cumulative probability plot of degradation of erasing voltage of floating gates. (d) Box plot of degradation of erasing voltage (all after 3000 cycles; center line: median of the data; top line: Q3, the upper quartile; bottom line: Q1, the lower quartile).

# 4. Conclusions

In summary, a new np-type floating gate with n-p junction polysilicon (bottom "n+" followed by top "p+" with a thickness ratio of 1:3) was developed in this study to reduce the charge leakage and improve the operation performance of memory devices. A depletion zone of carriers was formed at the n-p junction interface, leading to a narrowed channel and thus an increased sheet resistance that was 2.1 times that of the conventional floating gate. The relatively high charge storage and retention in the np-type floating gate is able to inhibit the charge leakage, owing to the high energy barrier at the n-p junction interface. Moreover, the programming threshold voltage difference between the 0 and 1 states (i.e., the memory window) of the np-type floating gate was effectively elevated by 1.2 times, while the erasing voltage and its degradation were close to that of the conventional one, indicative of no extra current leakage even at a higher programming threshold voltage and the better operation performance of the memory devices.

Materials **2022**, 15, 3640 9 of 10

**Author Contributions:** Conceptualization, Y.-Y.C.; methodology, Y.-Y.C.; formal analysis, Y.-Y.C.; investigation, Y.-Y.C.; resources, Y.-Y.C.; data curation, Y.-Y.C.; writing—original draft, Y.-Y.C. and S.-Y.C.; writing—review & editing, Y.-Y.C. and S.-Y.C.; supervision, S.-J.L. and S.-Y.C.; project administration, Y.-Y.C.; funding acquisition, S.-J.L. All authors have read and agreed to the published version of the manuscript.

Funding: This research was funded by Macronix International Co., Ltd.

Institutional Review Board Statement: Not Applicable.

Informed Consent Statement: Not Applicable.

**Data Availability Statement:** The data presented in this study are available on request from corresponding author.

**Acknowledgments:** The authors gratefully acknowledge Macronix International Co., Ltd. for their support and technical discussions about this work.

Conflicts of Interest: The authors declare no conflict of interest.

#### References

- 1. Kahng, D.; Sze, S.M. A Floating Gate and It's Application to Memory Devices. Bell Syst. Tech. J. 1967, 46, 1283. [CrossRef]

- 2. Sze, S.M. Evolution of nonvolatile semiconductor memory: From floating-gate concept to single-electron memory cell. In *Future Trends in Microelectronics*; Luryi, S., Xu, J., Zaslavsky, A., Eds.; John Wiley & Sons: Hoboken, NJ, USA, 1999; pp. 291–303.

- 3. Yau, L.D. A simple theory to predict the threshold voltage of short-channel IGFET's. *Solid State Electron.* **1974**, 17, 1059–1063. [CrossRef]

- 4. Himeno, T.; Matsukawa, N.; Hazama, H.; Sakui, K.; Oshikiri, M.; Masuda, K.; Kanda, K.; Itoh, Y.; Miyamoto, J. A new technique for measuring threshold voltage distribution in flash EEPROM devices. In Proceedings of the International Conference on Microelectronic Test Structures, Cork, Ireland, 8–11 April 2002; IEEE: New York, NY, USA, 2002. [CrossRef]

- 5. Lee, C.H.; Yang, I.C.; Cheng, C.H.; Chong, L.H.; Chen, K.F.; Huang, J.S.; Ku, S.H.; Zous, N.K.; Huang, I.J.; Han, T.T.; et al. Junction optimization for Reliability issues in floating gate NAND flash cells. In Proceedings of the 2011 International Reliability Physics Symposium, Monterey, MA, USA, 24 January 2011; IEEE: New York, NY, USA, 2011. [CrossRef]

- 6. Lue, H.T.; Wang, S.Y.; Lai, E.K.; Hsieh, K.Y.; Liu, R.; Lu, C.Y. A BE-SONOS (bandgap engineered SONOS) NAND for post-floating gate era flash memory. In Proceedings of the 2007 International Symposium on VLSI Technology, Systems and Applications (VLSI-TSA), Hsinchu, Taiwan, 23–25 April 2007; IEEE: New York, NY, USA, 2007.

- 7. Jin, Y.; Lee, B. A comprehensive survey of issues in solid state drives. Adv. Comput. 2019, 114, 1–69.

- 8. Zahoor, F.; Azni Zulkifli, T.Z.; Khanday, F.A. Resistive random access memory (RRAM): An overview of materials, switching mechanism, performance, multilevel cell (MLC) storage, modeling, and applications. *Nanoscale Res. Lett.* **2020**, *15*, 90. [CrossRef] [PubMed]

- 9. Meena, J.S.; Sze, S.M.; Chand, U.; Tseng, T.-Y. Overview of emerging nonvolatile memory technologies. *Nanoscale Res. Lett.* **2014**, 9, 526. [CrossRef] [PubMed]

- 10. Aritome, S. Advanced flash memory technology and trends for file storage application. In Proceedings of the International Electron Devices Meeting 2000, San Francisco, CA, USA, 10–13 December 2000; IEEE: New York, NY, USA, 2002; pp. 763–766.

- 11. Waser, R. Nanoelectronics and Information Technology: Advanced Electronic Materials and Novel Devices, 2nd ed.; Wiley-VCH: Weinheim, Berlin, Germany, 2012; Chapter IV; p. 548.

- 12. Afshari, K. Nonvolatile Memory with Multi-Stack Nanocrystals as Floating Gates. In 2007 REU Research Accomplishments; National Nanotechnology Infrastructure Network: Ithaca, NY, USA, 2007; pp. 38–39.

- 13. Blomme, P.; Rosmeulen, M.; Cacciato, A.; Kostermans, M.; Vrancken, C.; Van Aerde, S.; Schram, T.; Debusschere, I.; Jurczak, M.; Van Houdt, J. Novel dual layer floating gate structure as enabler of fully planar flash memory. In Proceedings of the 2010 Symposium on VLSI Technology, Honolulu, HI, USA, 15–17 June 2010; IEEE: New York, NY, USA, 2010; pp. 129–130.

- 14. Soin, N. Dependency of threshold voltage on floating gate and inter-polysilicon dielectric thickness for nonvolatile memory devices. In Proceedings of the 2010 IEEE International Conference on Semiconductor Electronics (ICSE2010), Malacca, Malaysia, 28–30 June 2010; IEEE: New York, NY, USA, 2010; pp. 83–87.

- 15. Lee, M.C.; Wong, H.Y. The Impact of Tunnel Oxide Nitridation to Reliability Performance of Charge Storage Non-Volatile Memory Devices. *J. Nanosci. Nanotechnol.* **2014**, *14*, 1508–1520. [CrossRef] [PubMed]

- 16. Ohba, R.; Sugiyama, N.; Uchida, K.; Koga, J.; Toriumi, A. Nonvolatile Si quantum memory with self-aligned doubly-stacked dots. *IEEE Trans. Electron Devices* **2002**, *49*, 1392–1398. [CrossRef]

- 17. Lin, Y.H.; Yang, Y.Y. Work Function Adjustment by Using Dipole Engineering for TaN-Al2O3-Si3N4-HfSiOx-Silicon Nonvolatile Memory. *Materials* **2015**, *8*, 5112–5120. [CrossRef] [PubMed]

- 18. Spassov, D.; Paskaleva, A.; Guziewicz, E.; Davidović, V.; Stanković, S.; Djorić-Veljković, S.; Ivanov, T.; Stanchev, T.; Stojadinović, N. Radiation Tolerance and Charge Trapping Enhancement of ALD HfO2/Al2O3 Nanolaminated Dielectrics. *Materials* **2021**, *14*, 849. [CrossRef] [PubMed]

Materials 2022, 15, 3640 10 of 10

19. Yoon, J.H. Fabrication of Sn@Al2O3 Core-shell Nanoparticles for Stable Nonvolatile Memory Applications. *Materials* **2019**, 12, 3111. [CrossRef] [PubMed]

- 20. Wang, B.; Gao, B.; Wu, H.; Qian, H. A drain leakage phenomenon in poly silicon channel 3D NAND flash caused by conductive paths along grain boundaries. *Microelectron. Eng.* **2018**, *192*, 66–69. [CrossRef]

- 21. Goda, A. Recent Progress on 3D NAND Flash Technologies. *Electronics* 2021, 10, 3156. [CrossRef]

- 22. Kim, H.-J.; Kim, D.-W.; Lee, W.-Y.; Kim, K.; Lee, S.-H.; Bae, J.-H.; Kang, I.-M.; Kim, K.; Jang, J. Flexible Sol-Gel-Processed Y2O3 RRAM Devices Obtained via UV/Ozone-Assisted Photochemical Annealing Process. *Materials* **2022**, *15*, 1899. [CrossRef] [PubMed]

- Le Gallo, M.; Sebastian, A. An overview of phase-change memory device physics. J. Phys. D Appl. Phys. 2020, 53, 213002.

[CrossRef]

- 24. Hatayama, S.; Sutou, Y.; Shindo, S.; Saito, Y.; Song, Y.-H.; Ando, D.; Koike, J. Inverse Resistance Change Cr2Ge2Te6-Based PCRAM Enabling Ultralow-Energy Amorphization. *ACS Appl. Mater. Interfaces* **2018**, *10*, 2725–2734. [CrossRef] [PubMed]

- 25. Fan, Z.; Chen, J.; Wang, J. Ferroelectric HfO2-based materials for next-generation ferroelectric memories. *J. Adv. Dielectr.* **2016**, 6, 1630003. [CrossRef]

- 26. Park, M.H.; Lee, Y.H.; Mikolajick, T.; Schroeder, U.; Hwang, C.S. Review and perspective on ferroelectric HfO<sub>2</sub>-based thin films for memory applications. *MRS Commun.* **2018**, *8*, 795–808. [CrossRef]

- 27. Guo, Z.; Yin, J.; Bai, Y.; Zhu, D.; Shi, K.; Wang, G.; Cao, K.; Zhao, W. Spintronics for Energy- Efficient Computing: An Overview and Outlook. *Proc. IEEE* 2021, 109, 1398–1417. [CrossRef]

- 28. Nehra, V. High-Performance Computing-in-Memory Architecture Using STT-/SOT-Based Series Triple-Level Cell MRAM. *IEEE Trans. Magn.* **2021**, *57*, 1–12. [CrossRef]

- 29. Shockley, W. Electrons and Holes in Semiconductors; Van Nostrand: Princeton, NJ, USA, 1950.

- Grove, A.S. Physics and Technology of Semiconductor Devices; Wiley: New York, NY, USA, 1967.

- 31. Nicollian, E.H.; Brews, J.R. MOS Physical and Technology; Wiley: New York, NY, USA, 1982.

- 32. Saatci, A.E.; Özdemir, O.; Kutlu, K. Conduction Mechanism Analysis of Inversion Current in MOS Tunnel Diodes. *Mater. Sci. Appl.* **2013**, *04*, 794–801. [CrossRef]

- 33. Hoefflinger, B. ITRS: The International Technology Roadmap for Semiconductors, 2007th ed.; Springer: Berlin/Heidelberg, Germany, 2011.

- 34. Kim, G.; Sun, M.-C.; Kim, S.W.; Kim, H.W.; Kim, J.H.; Park, E.H.; Kim, H.; Park, B.-G.; Byung-Gook, P. Novel MOSFET structure using p-n junction gate for ultra-low subthreshold-swing. In Proceedings of the 2011 International Semiconductor Device Research Symposium (ISDRS), Baltimore, MD, USA, 7–9 December 20; IEEE: New York, NY, USA, 2011; pp. 1–2. [CrossRef]

- 35. Misra, V.; Ozturk, M.C. Electrical Engineering Handbook; Elsevier: Amsterdam, The Netherlands, 2004; Chapter 3.2.4.

- Micheloni, R.; Crippa, L. Advances in Non-volatile Memory and Storage Technology; Woodhead Publishing: Sawston, Cambridge, UK, 2019; Chapter 3.3.4.

- 37. Boukhobza, J.; Olivier, P. Flash Memory Integration; Elsevier: Amsterdam, The Netherlands, 2017; Chapter 2.1.2.