Article

# A Novel L-Gate InGaAs/GaAsSb TFET with Improved Performance and Suppressed Ambipolar Effect

Boyang Ma <sup>(D)</sup>, Shupeng Chen \*, Shulong Wang \*<sup>(D)</sup>, Tao Han, Hao Zhang <sup>(D)</sup>, Chenyu Yin, Yaolin Chen and Hongxia Liu

Key Laboratory of Wide Band-Gap Semiconductor Materials and Devices of Education, The School of Microelectronics, Xidian University, Xi'an 710071, China

\* Correspondence: spchen@xidian.edu.cn (S.C.); slwang@xidian.edu.cn (S.W.)

**Abstract:** A heterojunction tunneling field effect transistor with an L-shaped gate (HJ-LTFET), which is very applicable to operate at low voltage, is proposed and studied by TCAD tools in this paper. InGaAs/GaAsSb heterojunction is applied in HJ-LTFET to enhance the ON-state current (I<sub>ON</sub>). Owing to the quasi-broken gap energy band alignment of InGaAs/GaAsSb heterojunction, height and thickness of tunneling barrier are greatly reduced. However, the OFF-state leakage current (I<sub>OFF</sub>) also increases significantly due to the reduced barrier height and thickness and results in an obvious source-to-drain tunneling (SDT). In order to solve this problem, an HfO2 barrier layer is inserted between source and drain. Result shows that the insertion layer can greatly suppress the horizontal tunneling leakage appears at the source and drain interface. Other optimization studies such as work function modulation, doping concentration optimization, scaling capability, and analog/RF performance analysis are carried out, too. Finally, the HJ-LTFET with a large I<sub>ON</sub> of 213  $\mu$ A/ $\mu$ m, a steep average SS of 8.9 mV/dec, and a suppressed I<sub>OFF</sub> of 10<sup>-12</sup>  $\mu$ A/ $\mu$ m can be obtained. Not only that, but the fT and GBP reached the maximum values of 68.3 GHz and 7.3 GHz under the condition of Vd = 0.5 V, respectively.

Keywords: band-to-band tunneling; InGaAs/GaAsSb; L-shaped gate; analog/RF performance

# 1. Introduction

The performance and density of integrated circuits have been significantly enhanced by scaling down of the MOSFET in the past several decades [1]. However, the conventional MOSFETs has a minimum subthreshold swing limited at 60 mV/dec. On the premise of maintaining device performance, scaling of the supply voltage will unavoidably be accompanied with the increasing I<sub>OFF</sub>, which will finally result in increased static power consumption. Therefore, researchers have to find other ways to solve the contradiction between static power consumption and performance [2–4]. Due to their steeper switching behavior than MOSFET, the tunneling field effect transistors (TFET), based on the band-toband tunneling (BTBT) operation mechanism, have been considered as a potential substitute for ultra-low power applications [5–9].

However, low ON-state current, large leakage current, and poor analog performance are three deficiencies that conventional TFETs need to confront [10–13]. These need to further optimize the conventional TFET for low-power and high-frequency application. In recent years, many research groups have done valuable work to improve the performance of TFET. Many novel TFETs with various structures have been proposed, such as L-TFET [14–16], U-TFET, and TGTFET [17–19]. Due to larger tunnel junction area and stronger gate-controlled capability, higher ON-state current and lower subthreshold swing than conventional planar TFET can be obtained. In spite of these advantages, the low ON-state current is still one of the greatest challenges of the TFET design. TFET still cannot meet the demand in commercial applications. To further improve the ON-state current, multimaterial heterojunction engineering is applied to improve the band-to-band tunneling

Citation: Ma, B.; Chen, S.; Wang, S.; Han, T.; Zhang, H.; Yin, C.; Chen, Y.; Liu, H. A Novel L-Gate InGaAs/GaAsSb TFET with Improved Performance and Suppressed Ambipolar Effect. *Micromachines* 2022, *13*, 1474. https://doi.org/10.3390/mi13091474

Academic Editors: Yeong-Her Wang and Kuan-Wei Lee

Received: 8 July 2022 Accepted: 3 September 2022 Published: 5 September 2022

**Publisher's Note:** MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations.

**Copyright:** © 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https:// creativecommons.org/licenses/by/ 4.0/). rate [20]. Compared with conventional homojunction TFET, research shows that HJTFETs have superior performances, such as Si/SiGe heterojunction [21–24], SiGeSn/GeSn heterojunction [25], and III–V heterojunction [26–32]. By selecting appropriate materials to form heterojunction, on the one hand, the height and thickness of the tunneling barrier can be effectively reduced. On the other hand, smaller carrier mass and higher carrier mobility can be achieved than with Si-based TFET. In this way, the tunneling rate can be further improved, and the larger ON-state current can be obtained. However, for HJTFETs, large OFF current, poor analog performance, and bipolar effect still need to be improved.

In this work, a novel InGaAs/GaAsSb HJ-LTFET with a remarkably good switching performance and suppressed ambipolar effect is proposed. Benefiting from the quasibroken gap energy band alignment of InGaAs/GaAsSb heterojunction and high tunneling efficiency of the L-shaped gate structure, HJ-LTFET obtained maximum I<sub>ON</sub> of 213  $\mu$ A/ $\mu$ m. Moreover, the insertion of barrier layer between the source and drain obviously suppressed the OFF-state source-to-drain tunneling on horizontal direction. On the other hand, the application of multiple-gate work functions by electrode work function modulation technics [33] obviously suppressed the OFF-state source-to-drain tunneling in the diagonal direction, which can help to achieve the I<sub>OFF</sub> of 10<sup>-12</sup>  $\mu$ A/ $\mu$ m.

#### 2. Structure and Mechanism of the HJ-LTFET

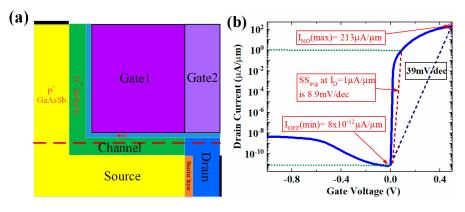

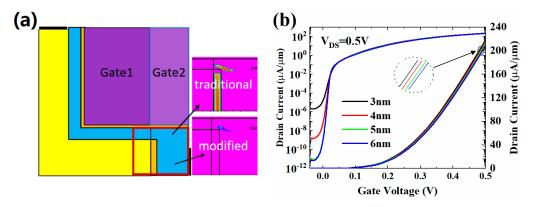

Figure 1a shows the structure of the proposed InGaAs/GaAsSb HJ-LTFET. The tunneling junction consists of a p+ GaAs<sub>0.9</sub>Sb<sub>0.1</sub> source with doping concentration of  $2 \times 10^{19}$  cm<sup>-3</sup> and a n<sup>+</sup> In<sub>0.9</sub>Ga<sub>0.1</sub>As channel layer with doping concentration of  $1 \times 10^{18}$  cm<sup>-3</sup>. To maximize the effective area of line tunneling junction, the source region and channel layer are overlapped as much as possible by structural design. The defined gate length ( $L_g$ ) and gate height ( $H_g$ ) are equal to 50 nm, and the thickness of channel ( $T_C$ ) is 10 nm. In order to suppress the source-to-drain tunneling (SDT) leakage current effectively, a 5 nm thickness HfO2 barrier layer is inserted to suppress the OFF-state tunneling between the source and the drain on the horizontal direction. On the other hand, the metal work function is modified to further reduce the OFF-state tunneling in other directions, such as vertical and diagonal directions. As shown in Figure 1, the metal work function of the dark purple region on the left is 4.75 eV, and that of the light purple region on the right is 4.85 eV. Furthermore, an HfO2 layer with 2 nm thickness is selected as the gate dielectric, which remarkably improves the gate control ability while maintaining enough gate dielectric thickness [34].

**Figure 1.** (a) Structure of the proposed InGaAs/GaAsSb HJ-LTFET; (b) the transfer characteristic of HJ-LTFET.

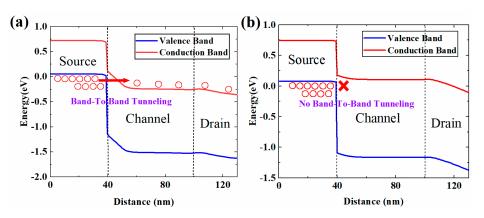

Figure 2 shows the ON-state and OFF-state energy band diagram of HJ-LTFET. The cutline positions are shown by the red dotted lines. In the ON-state, as shown in Figure 2a, electrons are tunneling from p+ GaAsSb source to n+ InGaAs channel. with the gate voltage increasing, the energy bands near the heterojunction will bend downward to meet the BTBT condition. After tunneling, the electrons will transfer from channel to drain and finally be

collected by the drain electrode. In the OFF-state, as shown in Figure 2b, there no BTBT occurs, and no tunneling current is observed in HJ-LTFET.

Figure 2. Band diagram in the (a) ON-state and (b) OFF-state.

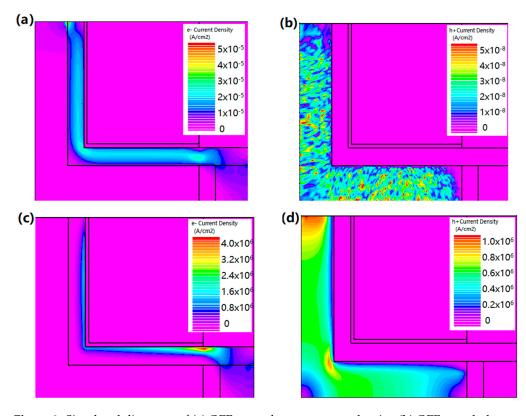

Correspondingly, the electron and hole current density distribution also show the current switching mechanism of HJ-LTFET, as shown in Figure 3. It is not difficult to see from Figure 3a,b that a small amount of free electrons flows from the channel layer to the drain electrode, forming the  $I_{OFF}$ . The OFF-state holes have no contribution to the  $I_{OFF}$  because the existence of the HfO2 barrier layer blocks the hole conductive path between the source and drain electrode. This indicates that in the OFF-state, there is no electron tunneling from the source region to the channel. Additionally, the presence of the space charge region results in significant resistance close to the p-n junction. However, in the ON-state, the electron current density and hole current density are extraordinarily high, as shown in Figure 3c,d. These electrons and holes mainly tunnel from heterojunction.

**Figure 3.** Simulated diagrams of (**a**) OFF-state electron current density, (**b**) OFF-state hole current density, (**c**) ON-state electron current density, and (**d**) ON-state hole current density at  $V_{DS} = 0.5$  V.

The transfer characteristic curve simulated by Silvaco TCAD is shown in Figure 1b. For the InGaAs/GaAsSb material used in the simulation, we obtained the fitting parameters in [35]. In order to accurately calculate the tunneling process under reverse bias condition, the hurkx BTBT model was used in this work, and models of Fermi–Dirac distribution, SRH recombination, non-local BTBT and field-dependent mobility were also used along with a band gap narrowing model. Considering both the high-doped source region and the low-doped channel, the BTBT parameters used to calculate the tunneling current are  $A_{\text{BTBT}=} 1.3 \times 10^{20} \text{ (cm}^{-3} \text{ s}^{-1})$ , and  $B_{\text{BTBT}=} 5.7 \times 10^{6} \text{ (V cm}^{-1})$ , respectively [36].

## 3. Discussion of Simulation Results

# 3.1. Effect of Doping Concentration in Source, Channel, and Drain on Device Performance

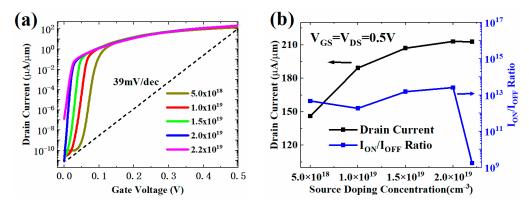

Figure 4 shows the change of the transfer characteristic, ON-state current ( $I_{ON}$ ), and switching current ratio ( $I_{ON}/I_{OFF}$ ) of HJ-LTFET with different source doping concentrations ( $N_S$ ). The subthreshold region shifts to the left with the increase of NS, as shown in Figure 4a. This is because the higher the  $N_S$  value, the easier the formation of the BTBT channel, and the smaller the  $V_{GS}$  value required to turn ON the BTBT process. When NS is more than  $2.0 \times 10^{19}$  cm<sup>-3</sup>, an OFF-state BTBT phenomenon can be found near the source/channel interface in Figure 4b, which can cause a large  $I_{OFF}$  and a small  $I_{ON}/I_{OFF}$ . When  $N_S$  is lower than  $2.0 \times 10^{19}$  cm<sup>-3</sup>, the BTBT leakage channel is switched OFF, and the  $I_{OFF}$ is decreased with the increasing  $N_S$ . This is because large  $N_S$  can reduce the electron concentration flowing from the source region to the channel, thereby inhibiting the leakage current composed of electron current in the OFF-state. Meanwhile, Figure 4b shows rapid  $I_{ON}$  increase due to the increasing of ON-state BTBT rate.

Figure 4. (a) Transfer characteristic and (b)  $I_{ON}$  and  $I_{ON}/I_{OFF}$  with different N<sub>S</sub> values.

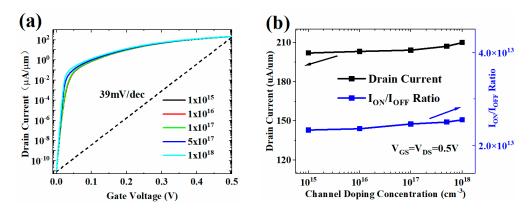

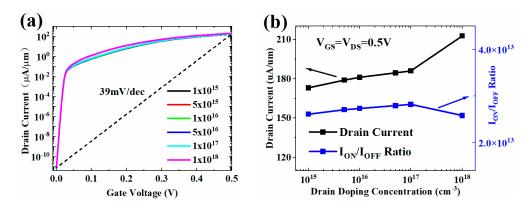

The HJ-LTFET is robust to variations in channel doping concentration (N<sub>C</sub>) and drain doping concentration (N<sub>D</sub>). Changes in N<sub>C</sub> and N<sub>D</sub> have little effect on the transfer characteristic, I<sub>ON</sub>, and I<sub>ON</sub>/I<sub>OFF</sub>, as shown in Figures 5 and 6. The increase of N<sub>C</sub> and N<sub>D</sub> will reduce the channel resistance, resulting in a slight increase in the I<sub>ON</sub>, as shown in Figures 5b and 6b. However, when the drain doping increases to  $1 \times 10^{18}$  cm<sup>-3</sup>, Figure 6b shows that the I<sub>OFF</sub> will increase sharply, resulting in a decrease in the I<sub>ON</sub>/I<sub>OFF</sub>. This is because the tunneling barrier between source and drain region will decrease with the increase of N<sub>D</sub>. When the barrier is lower than a certain value, SDT leakage current will be generated.

Figure 5. (a) Transfer characteristic and (b) I<sub>ON</sub> and I<sub>ON</sub>/I<sub>OFF</sub> with different N<sub>C</sub> values.

Figure 6. (a) Transfer characteristic and (b)  $I_{ON}$  and  $I_{ON}/I_{OFF}$  with different  $N_D$  values.

# 3.2. Effect of Geometric Dimensions on Device Performance

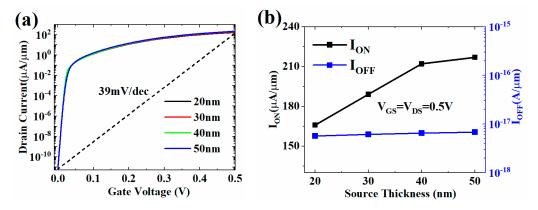

Figure 7 shows the change of the transfer characteristic, ON-state current, and OFFstate current of HJ-LTFET with different source thickness ( $T_S$ ). It is not difficult to find that, with the increasing  $T_S$ , the I<sub>ON</sub> increases continuously, and the variation of I<sub>OFF</sub> can be ignored, which is maintained at around  $6 \times 10^{-12} \mu A/\mu m$ . This is because the increase of  $T_S$  promotes the generation of free electrons in the source region, thereby increasing the number of tunneling electrons from source to channel and ultimately increasing the current density in the ON-state.

**Figure 7.** (a) Transfer characteristic and (b)  $I_{ON}$  and  $I_{ON}/I_{OFF}$  with different  $T_S$  values.

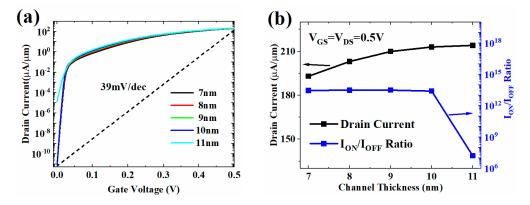

Figure 8 shows the change of the transfer characteristic, ON-state current, and switching current ratio of HJ-LTFET with different channel thickness ( $T_C$ ). Since the increase of  $T_C$ increases the area of diagonal tunneling between source and drain, the I<sub>ON</sub> increases with the increase of  $T_C$ , as shown in Figure 8b. However, when the  $T_C$  is greater than 10 nm, it will also form an extremely serious tunneling current in the OFF-state, resulting in a decline in device switching performance. In general, it is necessary to compromise between high  $I_{ON}$  and low  $I_{OFF}$ .

**Figure 8.** (a) Transfer characteristic and (b)  $I_{ON}$  and  $I_{ON}/I_{OFF}$  with different  $T_C$  values.

Figure 9 compares the effect of traditional low-doped spacer layer and modified HFO2 barrier layer with varying thickness between the source and drain on suppressing SDT leakage in OFF-state. It is not hard to find, in Figure 9a, that the SDT phenomenon (consisting of source-to-drain horizontal tunneling and source-to-drain diagonal tunneling) of the traditional structure in OFF-state is particularly serious. After the HfO2 barrier layer is used, the OFF-state electron tunneling on the horizontal direction of source and drain is completely suppressed, which shows that the performance of the modified structure has been greatly improved. For the diagonal tunneling between source and drain, the OFF-state leakage can be further reduced by increasing the thickness of the barrier layer, as shown in Figure 9b. This is because the increased barrier thickness weakens the drain voltage and increases the barrier height of SDT. At the same time, the I<sub>ON</sub> marginally declines as the barrier layer's thickness increases.

**Figure 9.** (**a**) OFF-state tunneling rate distribution with traditional low-doped spacer layer or modified HFO2barrier layer and (**b**) transfer characteristic curves with different thickness of HfO2 barrier layer.

## 3.3. Effect of Metal Work-Function on Device Performance

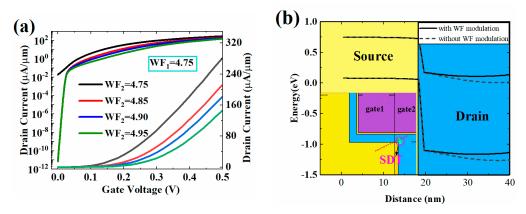

Figure 10 shows the impact of multi-metal work function modulation on device performance. It can be seen from Figure 10a that the  $I_{OFF}$  is reduced by 10 orders of magnitude through raising the work function of the gate2 (WF<sub>2</sub>) to 4.85 eV. When the WF<sub>2</sub> is improved further, the  $I_{OFF}$  changes slightly, and the  $I_{ON}$  will decrease gradually. Therefore, the WF<sub>2</sub> can be appropriately improved by the work function modulation method to optimize the device structure.

Figure 10. (a) Transfer characteristic and (b) band diagram with work-function modulation.

In order to analyze the reasons for the above results, the distribution of energy band with or without work function modulation in OFF-state is shown in Figure 10b. The source-to-drain diagonal tunneling is the main cause of OFF-state leakage, and increasing  $WF_2$  appropriately can reduce the probability of such tunneling. This is because the energy band close to the drain is raised with the increase of  $WF_2$ , and the elevation of the conduction band in the drain region increases the barrier of SDT. Therefore, by the application of multimetal work function, the OFF-state tunneling phenomenon can be suppressed greatly.

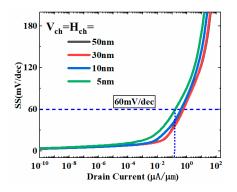

#### 3.4. Effect of Channel Length on Device Performance

Figure 11 shows the curve of subthreshold swing (SS) varying with channel length. It is clear to find that the SS changes weakly as the channel length decreases in the vertical and horizontal directions ( $V_{ch}$  and  $H_{ch}$ ). The SS is still lower than 60 mv/dec at Id = 0.1  $\mu$ A, even if the channel length is reduced to 5 nm in both vertical and horizontal directions. This is because the L-shaped channel expands the length to a certain extent by making full use of the vertical space. Compared with conventional planar TFET, the short-channel effects is not prominent with the scaling of the device. Therefore, this structure has excellent scaling capability and device reliability.

Figure 11. Subthreshold swing curve varying with channel length.

## 3.5. Analog/RF Performance of the HJTFET

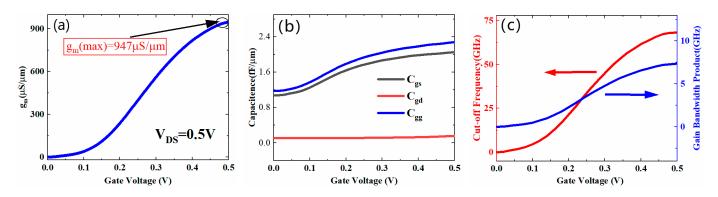

Figure 12a shows the transconductance curves of the HJTFET at Vds = 0.5 V. The transconductance ( $g_m$ ) can be obtained from the first derivative of the transfer characteristic curve [29], as shown in Equation (1):

$$g_m = dI_{ds}/dV_{gs} \tag{1}$$

**Figure 12.** (**a**) Transconductance curves, (**b**) parasitic capacitance curves, and (**c**) f<sub>T</sub> and GBP curves of the HJTFET.

As a result, the maximum transconductance of 947  $\mu$ S/ $\mu$ m can be achieved at Vg = 0.5 V, as shown in Figure 12a. This is benefited from the high current gain contributed by In-GaAs/GaAsSb heterojunction and L-shaped gate.

It is generally believed that the parasitic capacitance of devices is crucial to the frequency characteristics of integrated circuits, especially the gate capacitance ( $C_{gg}$ ). For proposed device structure,  $C_{gg}$  generally consists of gate-to-source capacitance ( $C_{gs}$ ) and gate-to-drain capacitance ( $C_{gd}$ ). Therefore, the characteristics of  $C_{gg}$ ,  $C_{gs}$ , and  $C_{gd}$  are of great significance for evaluating the frequency characteristics and analog application ability of devices. As shown in Figure 12b, the  $C_{gd}$  of the HJTFET under 0.5 V gate voltage is 0.15 fF/µm at Vd = 0.5 V, which is much smaller than that of the  $C_{gs}$  (2.0 fF/µm at Vd = 0.5 V). Thus, the  $C_{gg}$  of the HJTFET is mainly determined by  $C_{gs}$ , unlike the general heterojunction devices. This is closely related to the bias voltage applied on the gate and drain.

In addition to parasitic capacitance, cut-off frequency ( $f_T$ ) and gain bandwidth product (GBP) are also significant performance indicators to evaluate the frequency characteristics of devices. The fT depends on the ratio of transconductance to total capacitance [37], as shown in Equation (2). If a specific DC gain of 10 is assumed, the GBP can be expressed by Equation (3) [37,38].

$$f_{\rm T} = g_m / 2\pi (C_{gs} + C_{gd}) = g_m / 2\pi C_{gg}$$

(2)

$$GBP = g_m / 2\pi 10C_{gs} \tag{3}$$

Figure 12c shows the characteristic curves of  $f_T$  and GBW versus Vg at  $V_d = 0.5$  V. Benefiting from structural advantages, such as L-shaped channel and source, the HJTFET obtains the most outstanding frequency characteristics compared with others [21–32]. As shown in Figure 12b, the  $f_T$  and GBP of the HJTFET reached the maximum values of 68.3 GHz and 7.3 GHz under the condition of  $V_d = 0.5$  V, respectively.

By comparison with similar HJ-TFET, the superior DC and high-frequency characteristics of the proposed structure are highlighted, as shown in Table 1.

Table 1. Comparison with key parameters of similar device structures.

|                                        | InGaAs/InP<br>HJ-TTFET [28] | InGaAs/InP<br>HJ-LTFET [14,28] | Proposed<br>InGaAs/GaAsSb<br>HJ-LTFET |

|----------------------------------------|-----------------------------|--------------------------------|---------------------------------------|

| Channel length <i>Lch</i> (nm)         | 20                          | 20                             | 20                                    |

| Drain voltage Vds (V)                  | 0.5                         | 0.5                            | 0.5                                   |

| Gate voltage Vgs (V)                   | 0.5                         | 0.5                            | 0.5                                   |

| Source doping $Ns$ (cm <sup>-3</sup> ) | $5	imes 10^{19}$            | $5	imes 10^{19}$               | $2	imes 10^{19}$                      |

|                                       | InGaAs/InP<br>HJ-TTFET [28] | InGaAs/InP<br>HJ-LTFET [14,28] | Proposed<br>InGaAs/GaAsSb<br>HJ-LTFET |

|---------------------------------------|-----------------------------|--------------------------------|---------------------------------------|

| Drain doping $Nd$ (cm <sup>-3</sup> ) | $5	imes 10^{18}$            | $5	imes 10^{18}$               | $1	imes 10^{18}$                      |

| Ion $(\mu A/\mu m)$                   | 163                         | 85                             | 196                                   |

| Ion/Ioff                              | $5	imes 10^8$               | $4	imes 10^7$                  | $2	imes 10^{13}$                      |

| $gm$ ( $\mu$ S/ $\mu$ m)              | 500                         | 140                            | 950                                   |

| Cgg (fF/µm)                           | 1.7                         | 1.0                            | 2.2                                   |

| fT (GHz)                              | 46.8                        | 22.3                           | 68.3                                  |

Table 1. Cont.

#### 4. Conclusions

In this paper, a novel InGaAs/GaAsSb HJ-LTFET device structure based on the line tunneling mechanism is proposed. To reduce the leakage current in the OFF-state, the insertion of a HfO2 barrier layer separates the source region from the drain region to prevent the source-to-drain horizontal tunneling leakage. In addition, by adjusting the electrode work function, the gate metal work function above the drain region is improved to suppress the source drain diagonal tunneling. Meanwhile, the InGaAs/GaAsSb heterojunction of quasi-fault gap energy band alignment as well as large overlap area with an L-shaped between source region and channel layer greatly improve the I<sub>ON</sub> of the device. Through TCAD simulation, the HJ-LTFET with a large I<sub>ON</sub> of 213  $\mu$ A/ $\mu$ m, a steep average SS of 8.9mV/dec, and a maximum fT and GBP of 68.3 GHz and 7.3 GH, respectively, can be obtained. Therefore, the device structure is expected to be widely used in ultra-low power circuits in the future.

**Author Contributions:** Conceptualization and writing—original draft preparation, B.M.; methodology and funding acquisition, S.C. and S.W.; validation, C.Y. and Y.C.; writing—review and editing, T.H. and H.Z.; funding acquisition, H.L. All authors have read and agreed to the published version of the manuscript.

**Funding:** This research is financially supported by the National Natural Science Foundation of China (Grant No. 61904136), the Postdoctoral Research Foundation of China (CN) (Grant No. 2019M653551), the "Tong Xin project", the special scientific research projects of 772 institute (Grant No. TX-P21-01), and the Fundamental Research Funds for the Central Universities (Grant No. XJS211109).

Institutional Review Board Statement: Not applicable.

Informed Consent Statement: Not applicable.

Data Availability Statement: Data are contained within the article.

**Conflicts of Interest:** We declare that we do not have any commercial or associative interest that represents a conflict of interest in connection with the submitted work.

#### References

- 1. Hoefflinger, B. *ITRS: The International Technology Roadmap for Semiconductors. Chips* 2020. *The Frontiers Collection;* Springer: Berlin/Heidelberg, Germany, 2011; pp. 161–174.

- Jo, J.; Shin, C. Negative Capacitance Field Effect Transistor with Hysteresis-Free Sub-60-mV/Decade Switching. *IEEE Electron* Device Lett. 2016, 37, 245–248. [CrossRef]

- Kobayashi, M.; Jang, K.; Ueyama, N.; Hiramoto, T. Negative Capacitance for Boosting Tunnel FET performance. *IEEE Trans.* Nanotechnol. 2017, 16, 253–258. [CrossRef]

- Sun, J.; Schmidt, M.E.; Muruganathan, M.; Chong, H.M.H.; Mizuta, H. Large-scale nanoelectromechanical switches based on directly deposited nanocrystalline graphene on insulating substrates. *Nanoscale* 2016, *8*, 6659–6665. [CrossRef] [PubMed]

- Chen, Z.X.; Yu, H.Y.; Singh, N.; Shen, N.S.; Sayanthan, R.D.; Lo, G.Q.; Kwong, D.-L. Demonstration of Tunneling FETs Based on Highly Scalable Vertical Silicon Nanowires. *IEEE Electron Device Lett.* 2009, 30, 754–756. [CrossRef]

- 6. Zhang, Q.; Zhao, W.; Seabaugh, A. Low-subthreshold-swing tunnel transistors. *IEEE Electron Device Lett.* **2006**, 27, 297–300. [CrossRef]

- Choi, W.Y.; Park, B.-G.; Lee, J.D.; Liu, T.-J.K. Tunneling Field-Effect Transistors (TFETs) With Subthreshold Swing (SS) Less Than 60 mV/dec. *IEEE Electron Device Lett.* 2007, 28, 743–745. [CrossRef]

- 8. Seabaugh, A.C.; Zhang, Q. Low-Voltage Tunnel Transistors for Beyond CMOS Logic. Proc. IEEE. 2010, 98, 2095–2110. [CrossRef]

- 9. Ionescu, A.; Riel, H. Tunnel field-effect transistors as energy-efficient electronic switches. *Nature* 2011, 479, 329–337. [CrossRef]

- Abdi, D.B.; Kumar, M.J. Controlling Ambipolar Current in Tunneling FETs Using Overlapping Gate-on-Drain. IEEE J. Electron Devices Soc. 2014, 2, 187–190. [CrossRef]

- Cho, S.; Lee, J.S.; Kim, K.R.; Park, B.-G.; Harris, J.S.; Kang, I.M. Analyses on Small-Signal Parameters and Radio-Frequency Modeling of Gate-All-Around Tunneling Field-Effect Transistors. *IEEE Trans. Electron Devices* 2011, 58, 4164–4171. [CrossRef]

- 12. Luong, G.V.; Narimani, K.; Tiedemann, A.T.; Bernardy, P.; Trellenkamp, S.; Zhao, Q.T.; Mantl, S. Complementary Strained Si GAA Nanowire TFET Inverter with Suppressed Ambipolarity. *IEEE Electron Device Lett.* **2016**, *37*, 950–953. [CrossRef]

- 13. Raad, B.; Nigam, K.; Sharma, D.; Kondekar, P. Dielectric and Work function Engineered TFET for Ambipolar Suppression and RF Performance Enhancement. *Electron. Lett.* **2016**, *52*, 770–772. [CrossRef]

- Kim, S.W.; Kim, J.H.; Liu, T.-J.K.; Choi, W.Y.; Park, B.-G. Demonstration of L-Shaped Tunnel Field-Effect Transistors. *IEEE Trans. Electron Devices* 2016, 63, 1774–1778. [CrossRef]

- 15. Zhang, H.; Chen, S.; Liu, H.; Wang, S.; Wang, D.; Fan, X.; Chong, C.; Yin, C.; Gao, T. Polarization Gradient Effect of Negative Capacitance LTFET. *Micromachines* **2022**, *13*, 344. [CrossRef] [PubMed]

- 16. Yang, Z. Tunnel Field-Effect Transistor With an L-Shaped Gate. IEEE Electron Device Lett. 2016, 37, 839–842. [CrossRef]

- 17. Wang, W.; Wang, P.-F.; Zhang, C.-M.; Lin, X.; Liu, X.-Y.; Sun, Q.-Q.; Zhou, P.; Zhang, D.W. Design of U-Shape Channel Tunnel FETs With SiGe Source Regions. *IEEE Trans. Electron Devices* **2014**, *61*, 193–197. [CrossRef]

- Li, W.; Liu, H.; Wang, S.; Chen, S. Reduced Miller Capacitance in U-Shaped Channel Tunneling FET by Introducing Heterogeneous Gate Dielectric. *IEEE Electron Device Lett.* 2017, *38*, 403–406. [CrossRef]

- Chen, S.; Liu, H.; Wang, S.; Li, W.; Wang, X.; Zhao, L. Analog/RF Performance of T-Shape Gate Dual-Source Tunnel Field-Effect Transistor. *Nanoscale Res. Lett.* 2018, 13, 321. [CrossRef]

- 20. Jariwala, D.; Marks, T.; Hersam, M. Mixed-dimensional van der Waals heterostructures. Nat. Mater. 2017, 16, 170–181.

- 21. Li, W.; Woo, J.C.S. Vertical P-TFET With a P-Type SiGe Pocket. *IEEE Trans. Electron Devices* 2020, 67, 1480–1484. [CrossRef]

- Kato, K.; Jo, K.-W.; Matsui, H.; Tabata, H.; Mori, T.; Morita, Y.; Matsukawa, T.; Takenaka, M.; Takagi, S. p-Channel TFET Operation of Bilayer Structures with Type-II Heterotunneling Junction of Oxide- and Group-IV Semiconductors. *IEEE Trans. Electron Devices* 2020, 67, 1880–1886.

- 23. Chen, S.; Wang, S.; Liu, H.; Han, T.; Zhang, H. A high performance trench gate tunneling field effect transistor based on quasi-broken gap energy band alignment heterojunction. *Nanotechnology* **2022**, *33*, 225205.

- 24. Han, T.; Liu, H.; Chen, S.; Wang, S.; Xie, H. TCAD Simulation of the Doping-Less TFET with Ge/SiGe/Si Hetero-Junction and Hetero-Gate Dielectric for the Enhancement of Device Performance. *Coatings* **2020**, *10*, 278.

- Wang, H.; Han, G.; Liu, Y.; Zhang, J.; Hao, Y.; Jiang, X. The performance improvement in SiGeSn/GeSn p-channel hetero Line Tunneling FET (HL-TFET). In Proceedings of the 2017 IEEE Electrical Design of Advanced Packaging and Systems Symposium (EDAPS), Haining, China, 14–16 December 2017; pp. 1–3.

- Avci, U.E.; Young, I.A. Heterojunction TFET Scaling and resonant-TFET for steep subthreshold slope at sub-9nm gate-length. In Proceedings of the 2013 IEEE International Electron Devices Meeting, Washington, DC, USA, 9–11 December 2013; pp. 4.3.1–4.3.4.

- Chen, C.; Ilatikhameneh, H.; Huang, J.Z.; Klimeck, G.; Povolotskyi, M. Impact of Body Thickness and Scattering on III–V Triple Heterojunction TFET Modeled With Atomistic Mode-Space Approximation. *IEEE Trans. Electron Devices* 2020, 67, 3478–3485.

- Dubey, P.K.; Kaushik, B.K. T-Shaped III-V Heterojunction Tunneling Field-Effect Transistor. IEEE Trans. Electron Devices 2017, 64, 3120–3125.

- 29. Duan, X.; Zhang, J.; Wang, S.; Li, Y.; Xu, S.; Hao, Y. A High-Performance Gate Engineered InGaN Dopingless Tunnel FET. *IEEE Trans. Electron Devices* **2018**, *65*, 1223–1229. [CrossRef]

- 30. Bijesh, R.; Liu, H.; Madan, H.; Mohata, D.; Li, W.; Nguyen, N.V.; Gundlach, D.; Richter, C.A.; Maier, J.; Wang, K.; et al. Demonstration of In0.9Ga0.1As/GaAs0.18Sb0.82 near broken-gap tunnel FET with ION = 740 μA/μm, GM = 70 μS/μm and gigahertz switching performance at VDs = 0.5 V. In Proceedings of the 2013 IEEE International Electron Devices Meeting, Washington, DC, USA, 9–11 December 2013; pp. 28.2.1–28.2.4.

- Ahn, D.-H.; Yoon, S.-H.; Kato, K.; Fukui, T.; Takenaka, M.; Takagi, S. Effects of ZrO2/Al2O3 Gate-Stack on the Performance of Planar-Type InGaAs TFET. *IEEE Trans. Electron Devices* 2019, 66, 1862–1867.

- Xie, H.; Liu, H.; Chen, S.; Han, T.; Wang, S. Electrical performance of InAs/GaAs 0.1 Sb 0.9 heterostructure junctionless TFET with dual-material gate and Gaussian-doped source. *Semicond. Sci. Technol.* 2020, 35, 095004.

- 33. Sahoo, S.; Dash, S.; Mishra, G.P. Work-function modulated hetero gate charge plasma TFET to enhance the device performance. In Proceedings of the 2019 Devices for Integrated Circuit (DevIC), Kalyani, India, 23–24 March 2019; pp. 461–464.

- 34. Boucart, K.; Ionescu, A.M. Length scaling of the double gate tunnel FET with a high-k gate dielectric. *Solid State Electron*. **2007**, *51*, 1500–1507.

- Physical Properties of Semiconductors. 2016. Available online: http://www.ioffe.ru/SVA/NSM/Semicond/ (accessed on 15 January 1999).

- Smets, Q.; Verreck, D.; Verhulst, A.S.; Rooyackers, R.; Merckling, C.; Van De Put, M.; Simoen, E.; Vandervorst, W.; Collaert, N.; Thean, V.Y.; et al. InGaAs tunnel diodes for the calibration of semiclassical and quantum mechanical band-to-band tunneling models. J. Appl. Phys. 2014, 115, 184503. [CrossRef]

- 37. Wang, Q.; Wang, S.; Liu, H.; Li, W.; Chen, S. Analog/RF performance of L- and U-shaped channel tunneling field-effect transistors and their application as digital inverters. *Jpn. J. Appl. Phys.* **2017**, *56*, 064102.

- 38. Gupta, S.; Baishya, S. Analog and RF Performance Evaluation of Dual Metal Double Gate High-k Stack (DMDG-HKS) MOSFETs. *J. Nano-Electron. Phys.* **2013**, *5*, 30088.