Reproducible Non-Volatile Multi-State Storage and Emulation of Synaptic Plasticity Based on a Copper-Nanoparticle-Embedded HfOx/ZnO Bilayer with Ultralow-Switching Current and Ideal Data Retention

Abstract

:1. Introduction

2. Materials and Methods

3. Results and Discussion

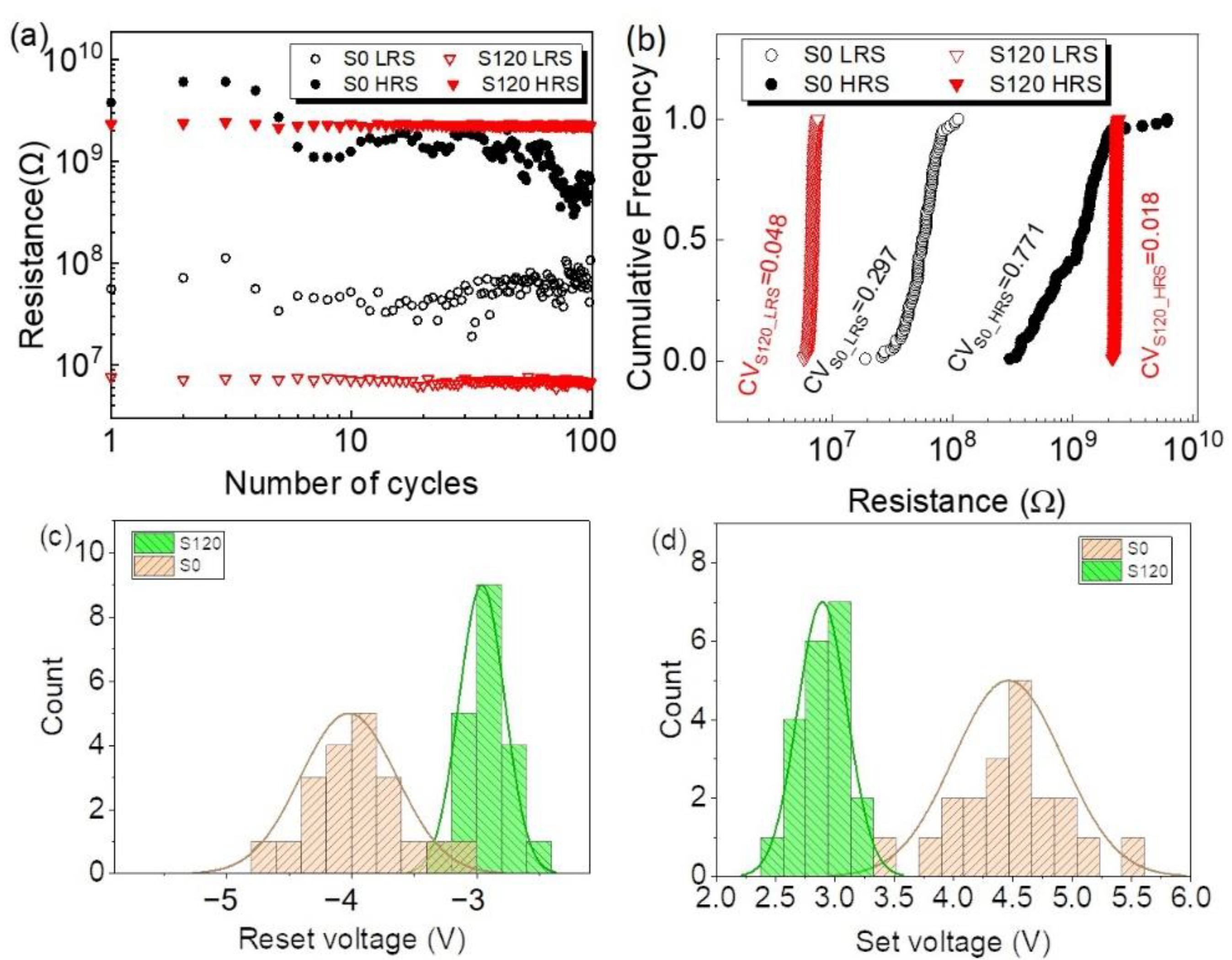

3.1. Bistable Storage Properties

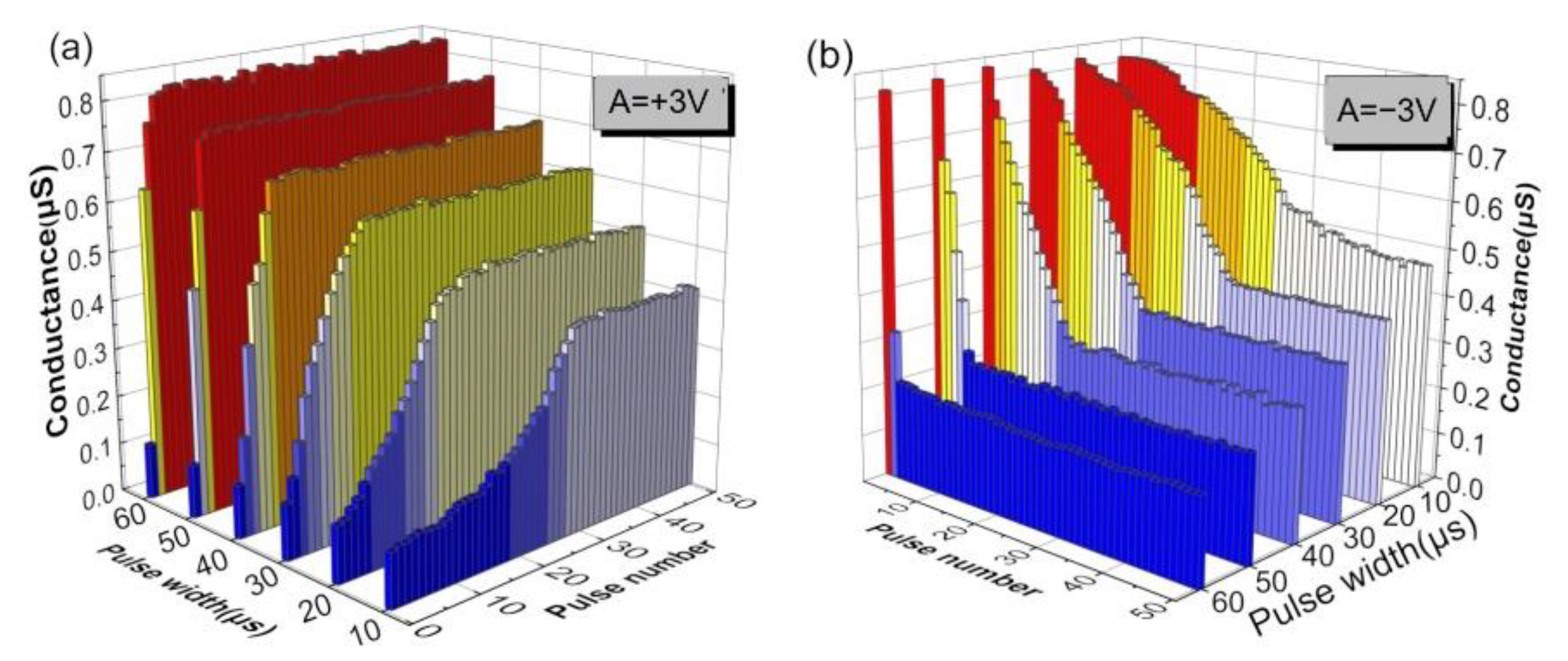

3.2. Multilevel Properties and Data Retention of Multiple Storage States

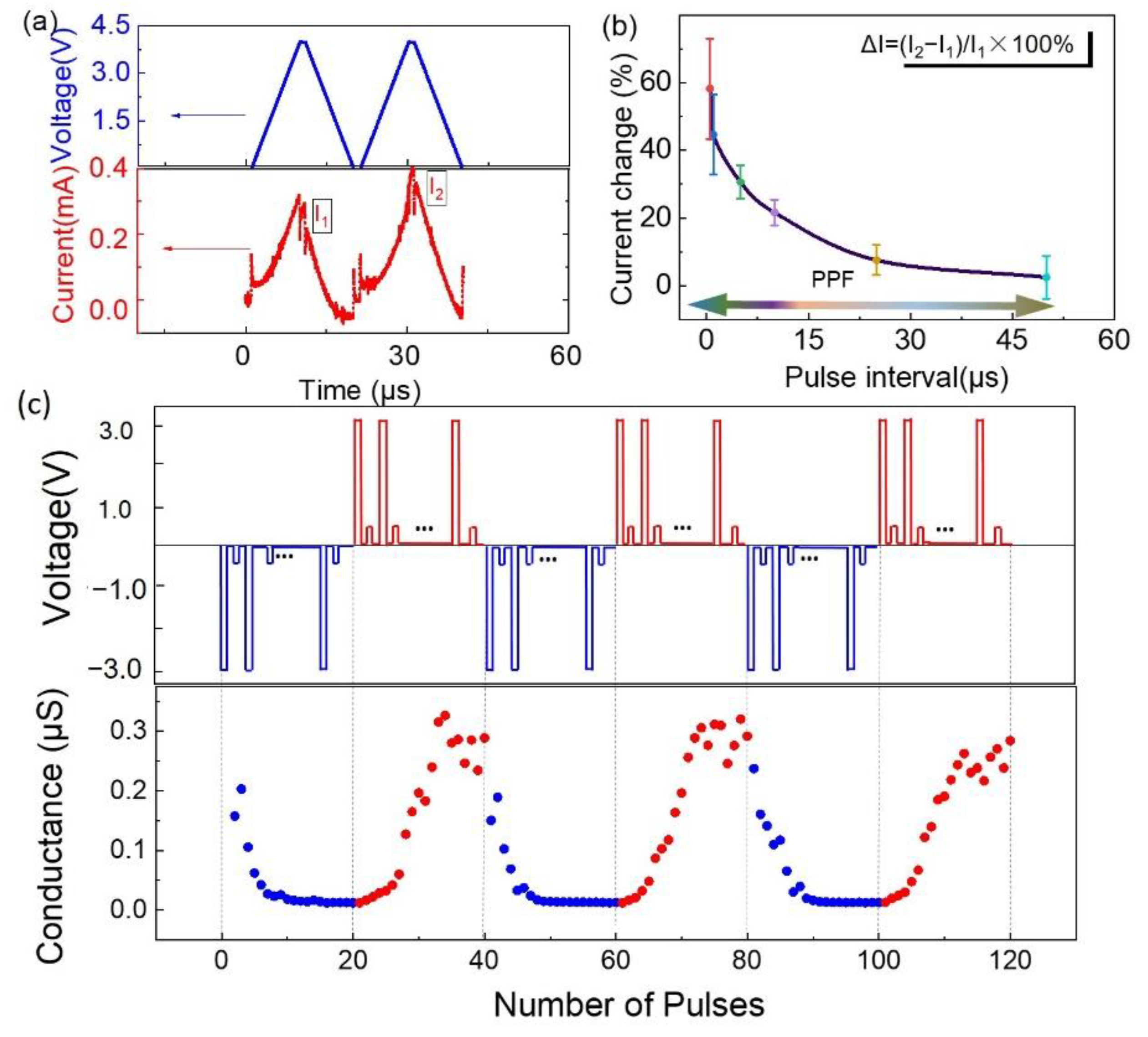

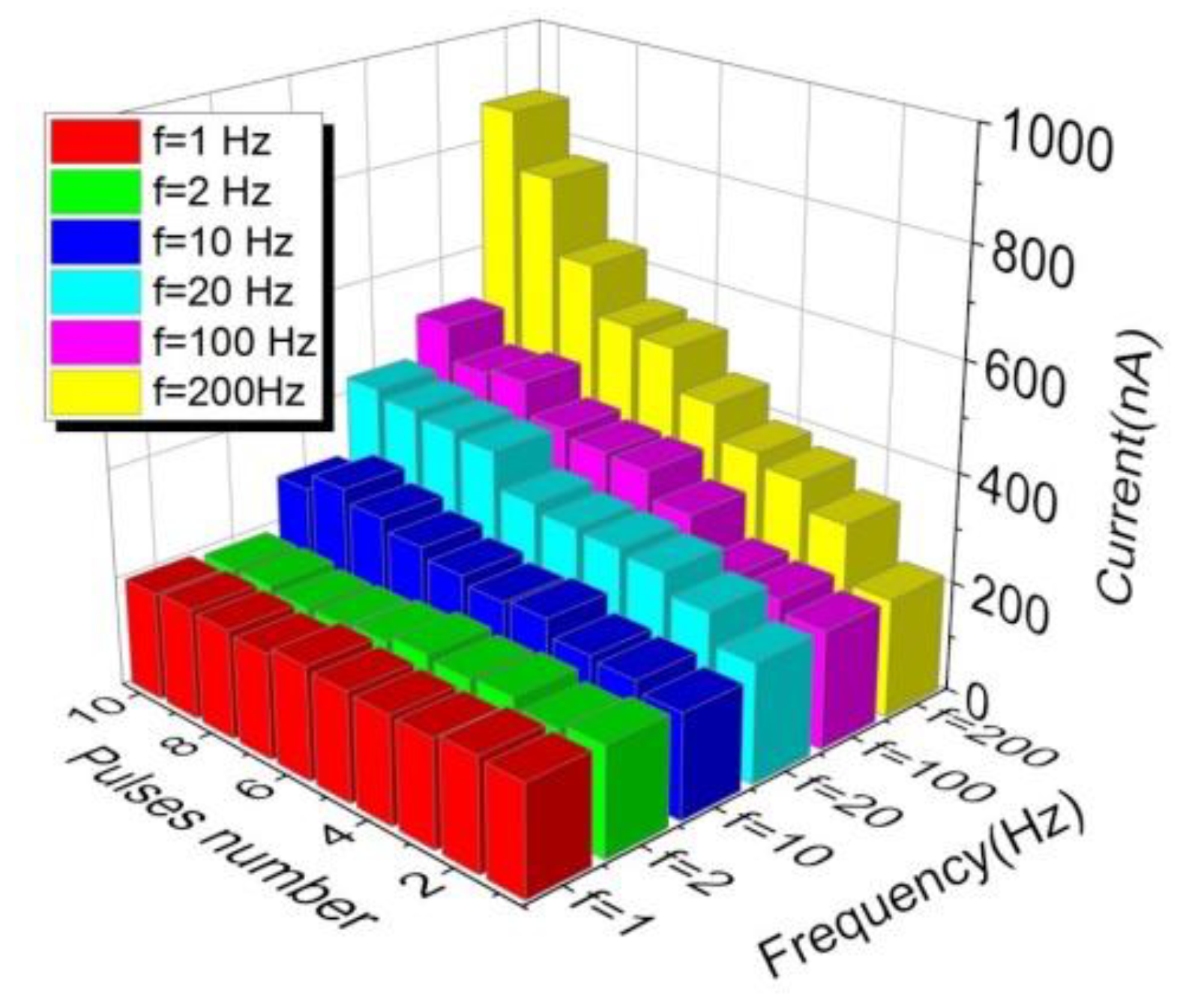

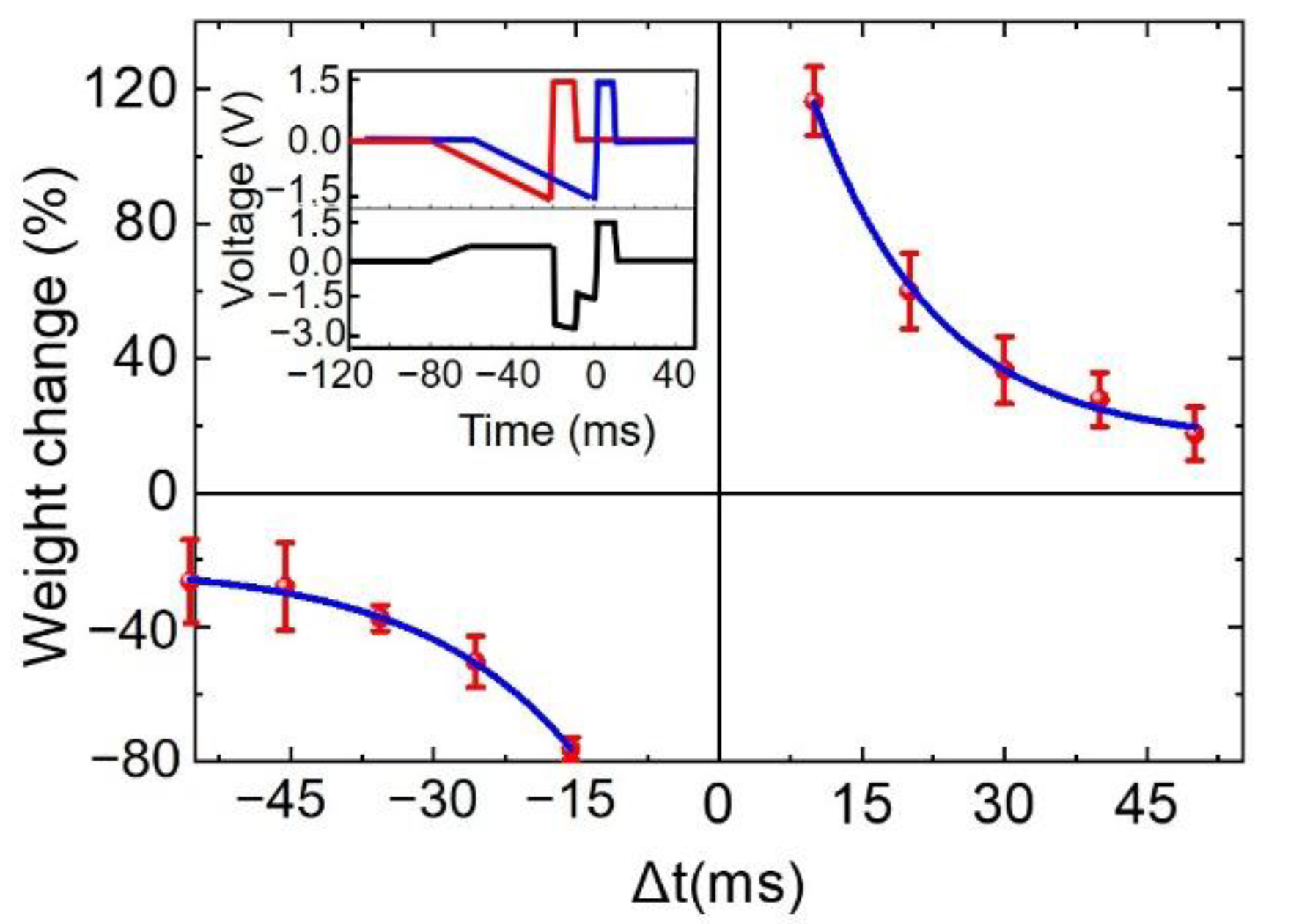

3.3. Simulation of Synaptic Behaviors

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Ding, G.; Zeng, K.; Zhou, K.; Li, Z.; Zhou, Y.; Zhai, Y.; Zhou, L.; Chen, X.; Han, S. Configurable Multi-State Non-Volatile Memory Behaviors in Ti3C2 Nanosheets. Nanoscale 2019, 11, 9. [Google Scholar] [CrossRef] [PubMed]

- Moon, J.; Ma, W.; Shin, J.H.; Cai, F.; Du, C.; Lee, S.H.; Lu, W.D. Temporal Data Classification and Forecasting Using a Memristor-Based Reservoir Computing System. Nat. Electron. 2019, 2, 480–487. [Google Scholar] [CrossRef]

- Wang, Z.; Joshi, S.; Savel’ev, S.E.; Jiang, H.; Midya, R.; Lin, P.; Hu, M.; Ge, N.; Strachan, J.P.; Li, Z.; et al. Memristors with Diffusive Dynamics as Synaptic Emulators for Neuromorphic Computing. Nat. Mater. 2017, 16, 101–108. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Pedretti, G.; Lelmini, D. In-Memory Computing with Resistive Memory Circuits: Status and Outlook. Electronics 2021, 10, 1063. [Google Scholar] [CrossRef]

- Luo, Q.; Cheng, Y.; Yang, J.G.; Cao, R.R.; Ma, H.L.; Yang, Y.; Huang, R.; Wei, W.; Zheng, Y.H.; Gong, T.C.; et al. A Highly CMOS Compatible Hafnia-Based Ferroelectric Diode. Nat. Commun. 2020, 11, 1391. [Google Scholar] [CrossRef] [Green Version]

- Sivan, M.; Li, Y.D.; Veluri, H.; Zhao, Y.S.; Tang, B.S.; Wang, X.H.; Zamburg, E.; Leong, J.F.; Niu, J.X.; Chand, U.; et al. All WSe2 1T1R Resistive RAM Cell for Future Monolithic 3D Embedded Memory Integration. Nat. Commun. 2019, 10, 12. [Google Scholar] [CrossRef] [Green Version]

- Han, X.; Privat, A.; Holbert, K.E.; Seo, J.; Yu, S.; Barnaby, H.J. Total Ionizing Dose Effects on Multistate HfOx-Based RRAM Synaptic Array. IEEE Trans. Nucl. Sci. 2021, 68, 756–761. [Google Scholar] [CrossRef]

- Shi, T.; Wang, R.; Wu, Z.; Sun, Y.; An, J.; Liu, Q. A Review of Resistive Switching Devices: Perforance Improvement, Characterization, and Applications. Small Struct. 2021, 2, 2000109. [Google Scholar] [CrossRef]

- Lu, W.; Li, C.; Zheng, L.; Xiao, J.; Lin, W.; Li, Q.; Wang, X.; Huang, Z.; Zeng, S.; Han, K.; et al. Multi-Nonvolatile State Resistive Switching Arising from Ferroelectricity and Oxygen Vacancy Migration. Adv. Mater. 2017, 29, 1606165. [Google Scholar] [CrossRef]

- Zhang, Y.; Cai, W.; Kang, W.; Yang, J.; Deng, E.; Zhang, Y.G.; Zhao, W.; Ravelosona, D. Demonstration of Multi-State Memory Device Combining Resistive and Magnetic Switching Behaviors. IEEE Electron Dev. Lett. 2018, 39, 684–687. [Google Scholar] [CrossRef]

- Cao, Y.; Rushforth, A.W.; Sheng, Y.; Zheng, H.; Wang, K. Tuning a Binary Ferromagnet into a Multistate Synapse with Spin-Orbit-Torque-Induced Plasticity. Adv. Funct. Mater. 2019, 29, 1808104. [Google Scholar] [CrossRef] [Green Version]

- Kirn, Y.; Choi, H.; Park, H.S.; Kang, M.S.; Shin, K.Y.; Lee, S.S.; Park, J.H. Reliable Multistate Data Storage with Low Power Consumption by Selective Oxidation of Pyramid-Structured Resistive Memory. ACS Appl. Mater. Interfaces 2017, 9, 38643–38650. [Google Scholar]

- Mahata, C.; Kang, M.; Kim, S. Multi-Level Analog Resistive Switching Characteristics in Tri-Layer HfO2/Al2O3/HfO2 Based Memristor on ITO Electrode. Nanomaterials 2020, 10, 2069. [Google Scholar] [CrossRef] [PubMed]

- Lee, H.; Beom, K.; Kim, M.; Kang, C.H.; Yoon, T. Nonvolatile Memory and Artificial Synaptic Characteristics in Thin-Film Transistors with Atomic Layer Deposited HfOx Gate Insulator and ZnO Channel Layer. Adv. Electron. Mater. 2020, 6, 2000412. [Google Scholar] [CrossRef]

- Wang, W.X.; Yang, L.; Yue, W.J.; Gao, S.; Zhang, C.W.; Chen, Z.X.; Chen, Y.H. Study on Multilevel Resistive Switching Behavior with Tunable ON/OFF Ratio Capability in Forming-Free ZnO QDs-Based RRAM. IEEE Trans. Electron Dev. 2020, 67, 4884–4890. [Google Scholar] [CrossRef]

- Rana, A.M.; Ismail, M.; Akber, T.; Nadeem, M.Y.; Kim, S. Transition from Unipolar to Bipolar, Multilevel Switching, Abrupt and Gradual Reset Phenomena in a TaN/CeO2/Ti: /Pt Memory Devices. Mater. Res. Bull. 2019, 117, 41–47. [Google Scholar] [CrossRef]

- Sun, C.; Lu, S.M.; Jin, F.; Mo, W.Q.; Song, J.L.; Dong, K.F. FePt Metallic Nanoparticle Dispersion-Induced Evolution of Resistive Switching Performance in SiO2-Based RRAM Devices. J. Electron. Mater. 2020, 49, 530–536. [Google Scholar] [CrossRef]

- Yan, X.B.; Pei, Y.F.; Chen, H.W.; Zhao, J.H.; Zhou, Z.Y.; Wang, H.; Zhang, L.; Wang, J.; Li, X.Y.; Qin, C.; et al. Self-Assembled Networked PbS Distribution Quantum Dots for Resistive Switching and Artificial Synapse Performance Boost of Memristors. Adv. Mater. 2019, 31, 1805284. [Google Scholar] [CrossRef]

- Giovinazzo, C.; Sandrini, J.; Shahrabi, E.; Celik, O.T.; Leblebici, Y.; Ricciardi, C. Analog Control of Retainable Resistance Multistates in HfO2 Resistive-Switching Random Access Memories (ReRAMs). ACS Appl. Electron. Mater. 2019, 1, 900–909. [Google Scholar] [CrossRef]

- Sedghi, N.; Li, H.; Brunell, I.F.; Dawson, K.; Potter, R.J.; Guo, Y.; Gibbon, J.T.; Dhanak, V.R.; Zhang, W.D.; Zhang, J.F.; et al. The Role of Nitrogen Doping in ALD Ta2O5 and Its Influence on Multilevel Cell Switching in RRAM. Appl. Phys. Lett. 2017, 110, 102902. [Google Scholar] [CrossRef] [Green Version]

- Lai, Y.F.; Xin, P.C.; Cheng, S.Y.; Yu, J.L.; Zheng, Q. Plasma Enhanced Multistate Storage Capability of Single ZnO Nanowire Based Memory. Appl. Phys. Lett. 2015, 106, 031603. [Google Scholar] [CrossRef]

- Abbas, H.; Ali, A.; Jung, J.; Hu, Q.; Park, M.R.; Lee, H.H.; Yoon, T.S.; Kang, C.J. Reversible Transition of Volatile to Non-Volatile Resistive Switching and Compliance Current-Dependent Multistate Switching in IGZO/MnO RRAM Devices. Appl. Phys. Lett. 2019, 114, 093503. [Google Scholar] [CrossRef]

- Bhattacharjee, S.; Caruso, E.; McEvoy, N.; Coileain, C.O.; O’Neill, K.; Ansari, L.; Duesberg, G.S.; Nagle, R.; Cherkaoui, K.; Gity, F.; et al. Insights into Multilevel Resistive Switching in Monolayer MoS2. ACS Appl. Mater. Interfaces 2020, 12, 6022–6029. [Google Scholar] [CrossRef] [PubMed]

- Zhang, T.; Yang, K.; Xu, X.; Cai, Y.; Yang, Y.; Huang, R. Memristive Devices and Networks for Brain-Inspired Computing. Phys. Status Solidi RRL 2019, 13, 1900029. [Google Scholar] [CrossRef]

- Ng, S.; John, R.; Yang, J.T.; Mathews, N. Forming-Less Compliance-Free Multistate Memristors as Synaptic Connections for Brain-Inspired Computing. ACS Appl. Electron. Mater. 2020, 2, 817–826. [Google Scholar] [CrossRef]

- Mahate, C.; Ismail, M.; Kim, S. Conductance Quantization Control and Neuromorphic Properties in Pt-Nanoparticle Incorporated HfAlOx Alloy Memristor. Appl. Phys. Lett. 2021, 119, 221601. [Google Scholar] [CrossRef]

- Algadi, H.; Mahata, C.; Alsuwian, T.; Ismail, M.; Kwon, D.; Kim, S. Gradual Resistive Switching and Synaptic Properties of ITO/HfAlO/ITO Device Embedded with Pt Nanoparticles. Mater. Lett. 2021, 298, 130011. [Google Scholar] [CrossRef]

- Niu, Y.; Yu, X.; Dong, X.; Zheng, D.; Liu, S.; Gan, Z.; Chang, K.; Liu, B.; Jiang, K.; Li, Y.; et al. Improved Al2O3 RRAM Performance Based on SiO2/MoS2 Quantum Dots Hybrid Structure. Appl. Phys. Lett. 2022, 120, 022106. [Google Scholar] [CrossRef]

- Sakellaropoulos, D.; Bousoulas, P.; Tsoukalas, D. Impact of Pt Embedded Nanocrystals on the Resistive Switching and Synaptic Properties of Forming Free TiO2−x/TiO2−y Based Bilayer Structure. J. Appl. Phys. 2019, 126, 044501. [Google Scholar] [CrossRef]

- Vishwanath, S.K.; Woo, H.; Jeon, S. Enhancement of Resistive Switching Properties in Al2O3 Bilayer-Based Atomic Switches: Multilevel Resistive Switching. Nanotechnology 2018, 29, 235202. [Google Scholar] [CrossRef]

- Lai, Y.; Zeng, C.; Liao, C.; Cheng, S.; Yu, J.; Zheng, Q.; Lin, P. Ultralow Switching Current in HfOx/ZnO Bilayer with Tunable Switching Power Enabled by Plasma Treatment. Appl. Phys. Lett. 2016, 109, 063501. [Google Scholar] [CrossRef]

- Wang, Y.; Liu, Q.; Long, S.; Wang, W.; Wang, Q.; Zhang, M.; Zhang, S.; Li, Y.; Zuo, Q.; Yang, J.; et al. Investigation of Resistive Switching in Cu-Doped HfO2 Thin Film for Multilevel Non-Volatile Memory Applications. Nanotechnology 2010, 21, 045202. [Google Scholar] [CrossRef] [PubMed]

- Liu, Q.; Long, S.B.; Wang, W.; Tanachutiwat, S.; Li, Y.T.; Wang, Q.; Zhang, M.; Huo, Z.; Chen, J.; Liu, M. Low-Power and Highly Uniform Switching in ZrO2-Based ReRAM with a Cu Nanocrystal Insertion Layer. IEEE Electron Dev. Lett. 2010, 31, 1299–1301. [Google Scholar]

- Chu, T.J.; Tsai, T.M.; Chang, T.C.; Chang, K.C.; Pan, C.H.; Chen, K.H.; Chen, J.H.; Chen, H.L.; Huang, H.C.; Shih, C.C.; et al. Ultra-High Resistive Switching Mechanism Induced by Oxygen Ion Accumulation on Nitrogen-Doped Resistive Random Access Memory. Appl. Phys. Lett. 2014, 105, 223514. [Google Scholar] [CrossRef]

- Simmons, J.G. Poole-Frenkel Effect and Schottky Effect in Metal-Insulator-Metal Systems. Phys. Rev. 1967, 155, 657–660. [Google Scholar] [CrossRef]

- Chiu, F.C. A Review on Conduction Mechanisms in Dielectric Films. Adv. Mater. Sci. Eng. 2014, 2014, 578168. [Google Scholar] [CrossRef] [Green Version]

- Verrelli, E.; Tsoukalas, D. Investigation of the Gate Oxide Leakage Current of Low Temperature Formed Hafnium Oxide Films. J. Appl. Phys. 2013, 113, 114103. [Google Scholar] [CrossRef]

- Gao, B.; Kang, J.F.; Zhang, H.W.; Sun, B.; Chen, B.; Liu, L.F.; Liu, X.Y.; Han, R.Q.; Wang, Y.Y.; Fang, Z.; et al. Oxide-Based RRAM: Physical Based Retention Projection. In Proceedings of the 40th European Solid-Sate Device Research Conference, Seville, Spain, 13–17 September 2010. [Google Scholar]

- Traoré, B.; Blaise, P.; Vianello, E.; Grampeix, H.; Jeannot, S.; Perniola, L.; De Salvo, B.; Nishi, Y. On the Origin of Low-Resistance State Retention Failure in HfO2-Based RRAM and Impact of Doping/Alloying. IEEE Trans. Electron Dev. 2015, 62, 4029–4036. [Google Scholar] [CrossRef]

- Yu, S.; Chen, Y.Y.; Guan, X.; Wong, H.-S.P.; Kittl, J.A. A Monte Carlo Study of the Low Resistance State Retention of HfOx Based Resistive Switching Memory. Appl. Phys. Lett. 2012, 100, 043507. [Google Scholar] [CrossRef]

- Frascaroli, J.; Volpe, F.G.; Brivio, S.; Spiga, S. Effect of Al Doping on the Retention Behavior of HfO2 Resistive Switching Memories. Microelectron. Eng. 2015, 147, 104–107. [Google Scholar] [CrossRef]

- Wu, M.C.; Lin, Y.W.; Jang, W.Y.; Lin, C.H.; Tseng, T.Y. Low-Power and Highly Reliable Multilevel Operation in ZrO2 1T1R RRAM. IEEE Electron Dev. Lett. 2011, 32, 1026–1028. [Google Scholar] [CrossRef]

- Park, J.; Jo, M.; Bourim, E.M.; Yoon, J.; Seong, D.J.; Lee, J.; Lee, W.; Hwang, H. Inevstigation of State Stability of Low-Resistance State in Resistive Memory. IEEE Electron Dev. Lett. 2010, 31, 485–487. [Google Scholar] [CrossRef]

- Tuomisto, F.; Saarinen, K.; Look, D.C.; Farlow, G.C. Introduction and Recovery of Point Defects in Electron-Irradiated ZnO. Phys. Rev. B 2005, 72, 085206. [Google Scholar] [CrossRef] [Green Version]

- Broglia, G.; Ori, G.; Larcher, L.; Montorsi, M. Molecular Dynamics Simulation of Amorphous HfO2 for Resistive RAM Applications. Model. Simul. Mater. Sci. Eng. 2014, 22, 065006. [Google Scholar] [CrossRef]

- Ishibe, T.; Uematsu, Y.; Naruse, N.; Mera, Y.; Nakamura, Y. Impact of Metal Silicide Nanocrystals on the Resistance Ratio in Resistive Switching of Epitaxial Fe3O4 Films on Si Substrates. Appl. Phys. Lett. 2020, 116, 181601. [Google Scholar] [CrossRef]

- Lai, Y.; Chen, F.; Zeng, Z.C.; Lin, P.; Cheng, S.Y.; Yu, J.L. Thermal Stability and Data Retention of Resistive Random Access Memory with HfOx/ZnO Double Layers. Chin. Phys. B 2017, 26, 087305. [Google Scholar] [CrossRef]

- Ohno, T.; Hasegawa, T.; Tsuruoka, T.; Terabe, K.; Gimzewski, J.K.; Aono, M. Short-Term Plasticity and Long-Term Potentiation Mimicked in Single Inorganic Synapses. Nat. Mater. 2011, 10, 591–595. [Google Scholar] [CrossRef]

- Martin, S.J.; Grimwood, P.D.; Morris, R.G.M. Synaptic Plasticity and Memory: An Evaluation of the Hypothesis. Annu. Rev. Neurosci. 2000, 23, 649–711. [Google Scholar] [CrossRef] [Green Version]

- Natalia, C.; Yang, D. Spike Timing-Dependent Plasticity: A Hebbian Learning Rule. Annu. Rev. Neurosci. 2008, 31, 25–46. [Google Scholar]

- Abbott, L.F.; Nelson, S.B. Synaptic Plasticity: Taming the Beast. Nat. Neurosci. 2000, 3, 1178–1183. [Google Scholar] [CrossRef]

| States | Device S0 (s) | Device S120 (s) | ||||

|---|---|---|---|---|---|---|

| @160 °C | @180 °C | @200 °C | @160 °C | @180 °C | @200 °C | |

| level 0 | 31,370 | 3280 | 440 | 26,340 | 3260 | 650 |

| level 1 | 4770 | 990 | 450 | 25,170 | 3000 | 820 |

| level 2 | 5720 | 1000 | 620 | 19,320 | 3380 | 750 |

| level 3 | 20,200 | 2400 | 310 | 15,240 | 2400 | 620 |

| Device | Level 0 (eV) | Level 1 (eV) | Level 2 (eV) | Level 3 (eV) |

|---|---|---|---|---|

| S0 | 1.92 | 1.05 | 1.07 | 1.90 |

| S120 | 1.65 | 1.53 | 1.44 | 1.43 |

| Device Structure | ROFF/RON | Retention (s) | Maximal Current (mA) | Reference |

|---|---|---|---|---|

| Ag/Ga2O3:PbS QDs/Pt | 106 | 104 at 85 °C for three states | 100 | [18] |

| TaN/HfO2/Al2O3/HfO2/ITO | 102 | 104 | 1 | [13] |

| Al/PMMA/ZnO QDs/PMMA/ZnO QDs/PMMA/FTO | 102 | 5 × 103 | 20 | [15] |

| TaN/CeO2/Ti (1 nm)/CeO2/Pt | >102 | 104 at 85 °C | 10 | [16] |

| Ag/IGZO/MnO/Pt | 106 | 5 × 104 at 80 °C | 5 | [22] |

| Al/AlOy/SnOx/FTO | 20 | 5 × 103 | 20 | [25] |

| ITO/HfAlO/Pt NPs/HfAlO/ITO | >10 | 104 | 3 | [27] |

| Cu/AlOx/Al2O3/Pt | 105 | 104 | 10 | [30] |

| Ti/HfOx/Cu NPs/HfOx/ZnO/ITO | ~3 × 102 | ~1 year at 85 °C for 4 states | <0.01 | This work |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Chen, S.; Chen, H.; Lai, Y. Reproducible Non-Volatile Multi-State Storage and Emulation of Synaptic Plasticity Based on a Copper-Nanoparticle-Embedded HfOx/ZnO Bilayer with Ultralow-Switching Current and Ideal Data Retention. Nanomaterials 2022, 12, 3769. https://doi.org/10.3390/nano12213769

Chen S, Chen H, Lai Y. Reproducible Non-Volatile Multi-State Storage and Emulation of Synaptic Plasticity Based on a Copper-Nanoparticle-Embedded HfOx/ZnO Bilayer with Ultralow-Switching Current and Ideal Data Retention. Nanomaterials. 2022; 12(21):3769. https://doi.org/10.3390/nano12213769

Chicago/Turabian StyleChen, Shuai, Hao Chen, and Yunfeng Lai. 2022. "Reproducible Non-Volatile Multi-State Storage and Emulation of Synaptic Plasticity Based on a Copper-Nanoparticle-Embedded HfOx/ZnO Bilayer with Ultralow-Switching Current and Ideal Data Retention" Nanomaterials 12, no. 21: 3769. https://doi.org/10.3390/nano12213769