A Ka-Band Doherty Power Amplifier in a 150 nm GaN-on-SiC Technology for 5G Applications

Abstract

:1. Introduction

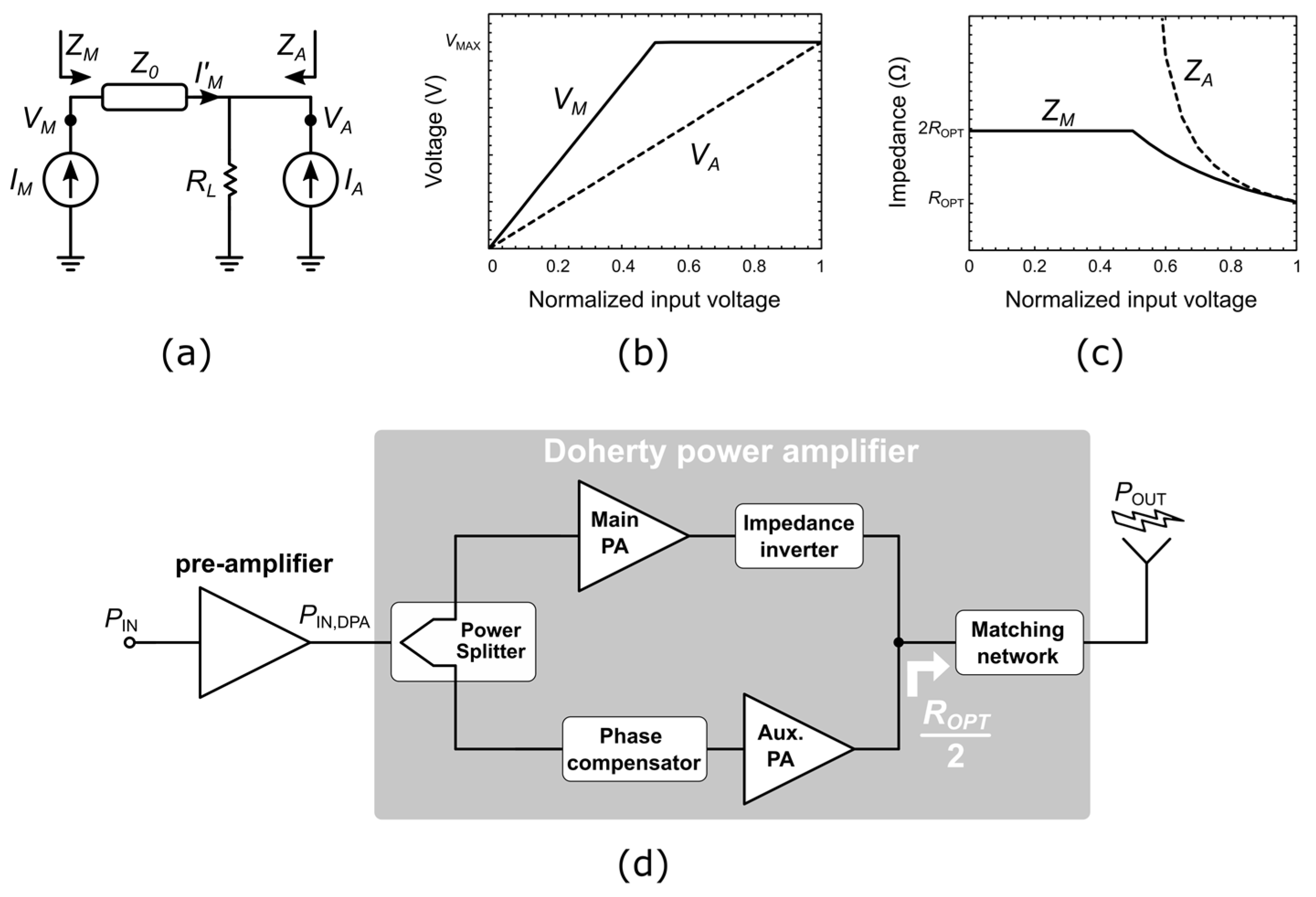

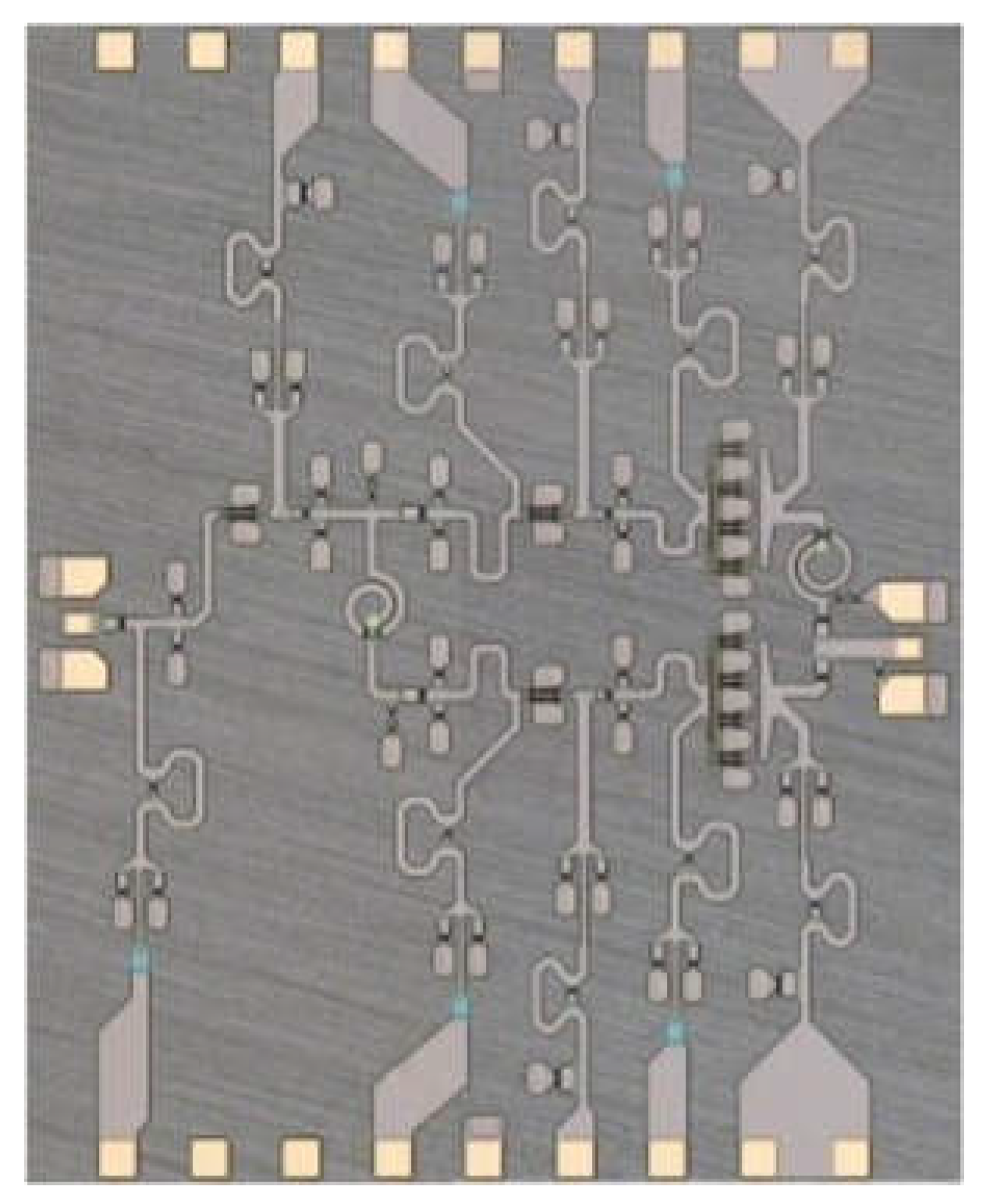

2. The Doherty Operation

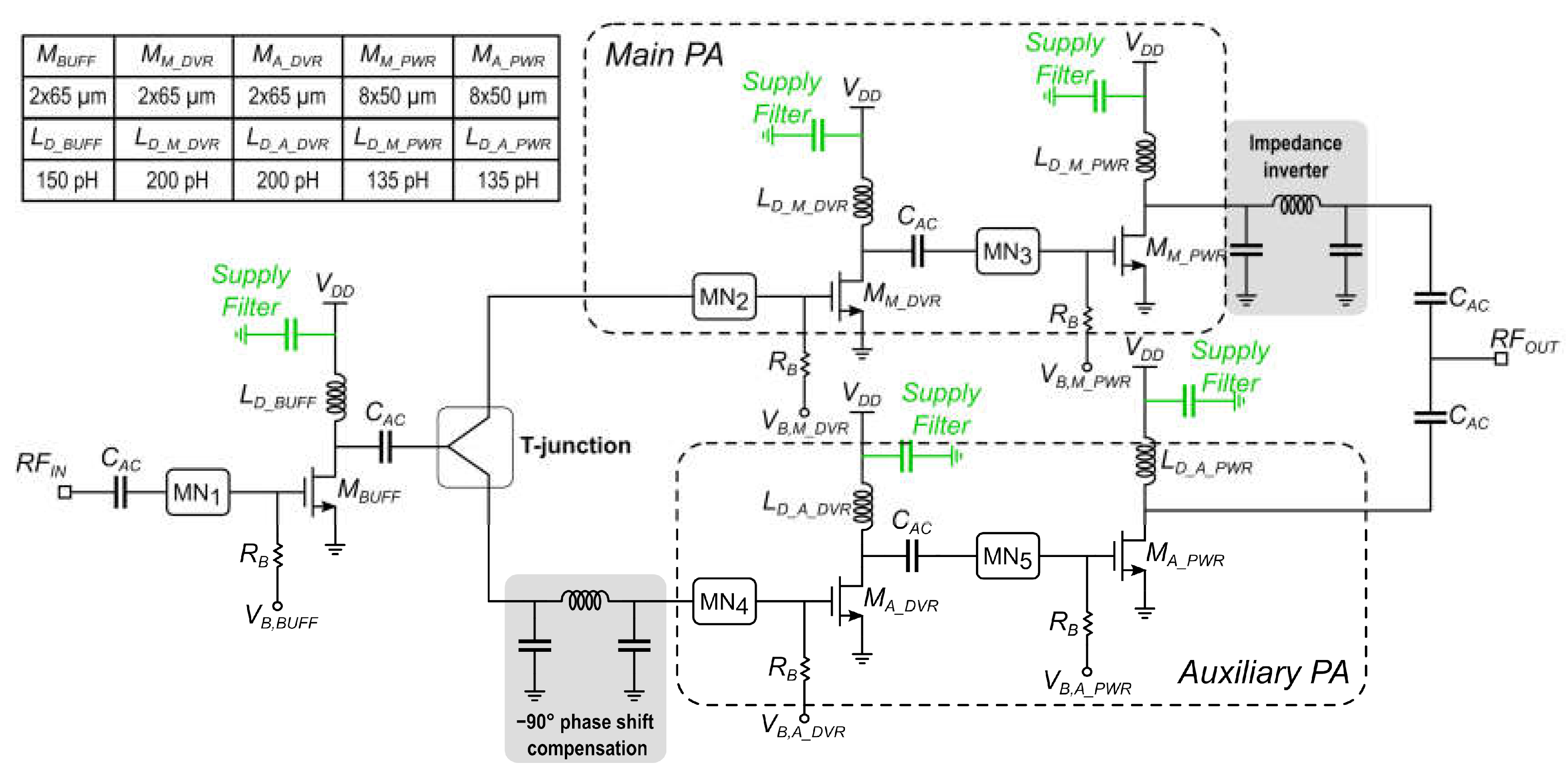

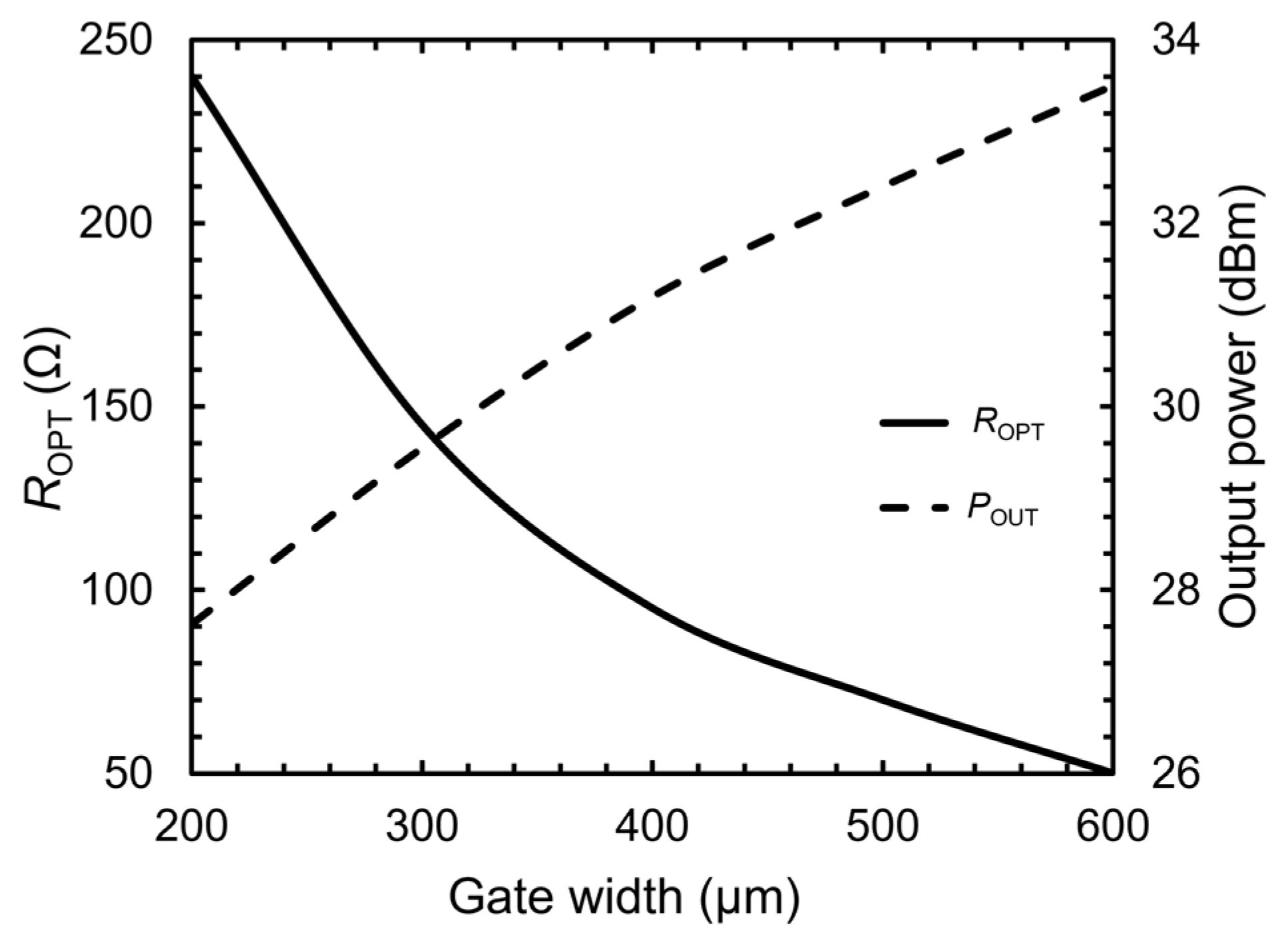

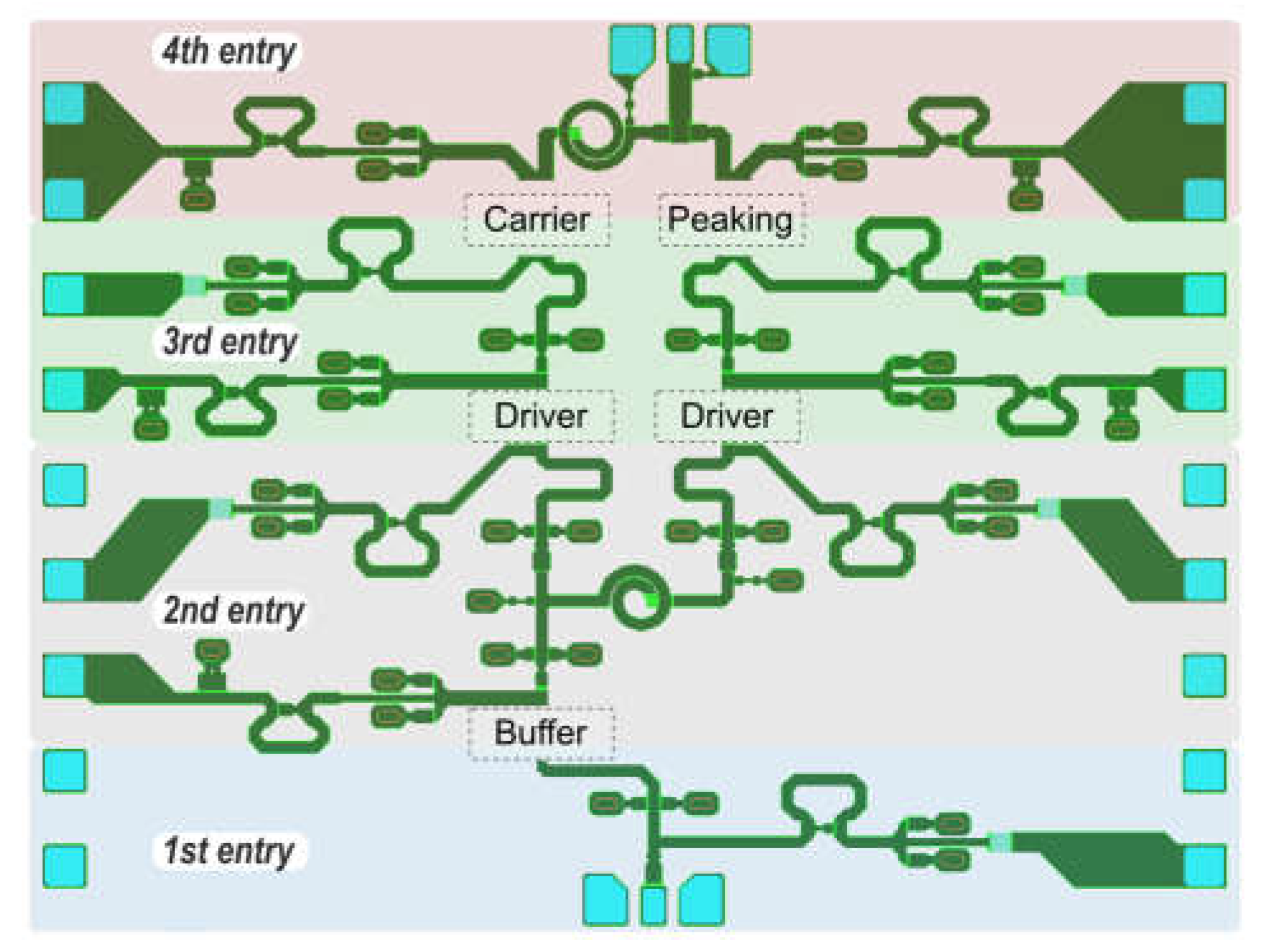

3. Circuit Design

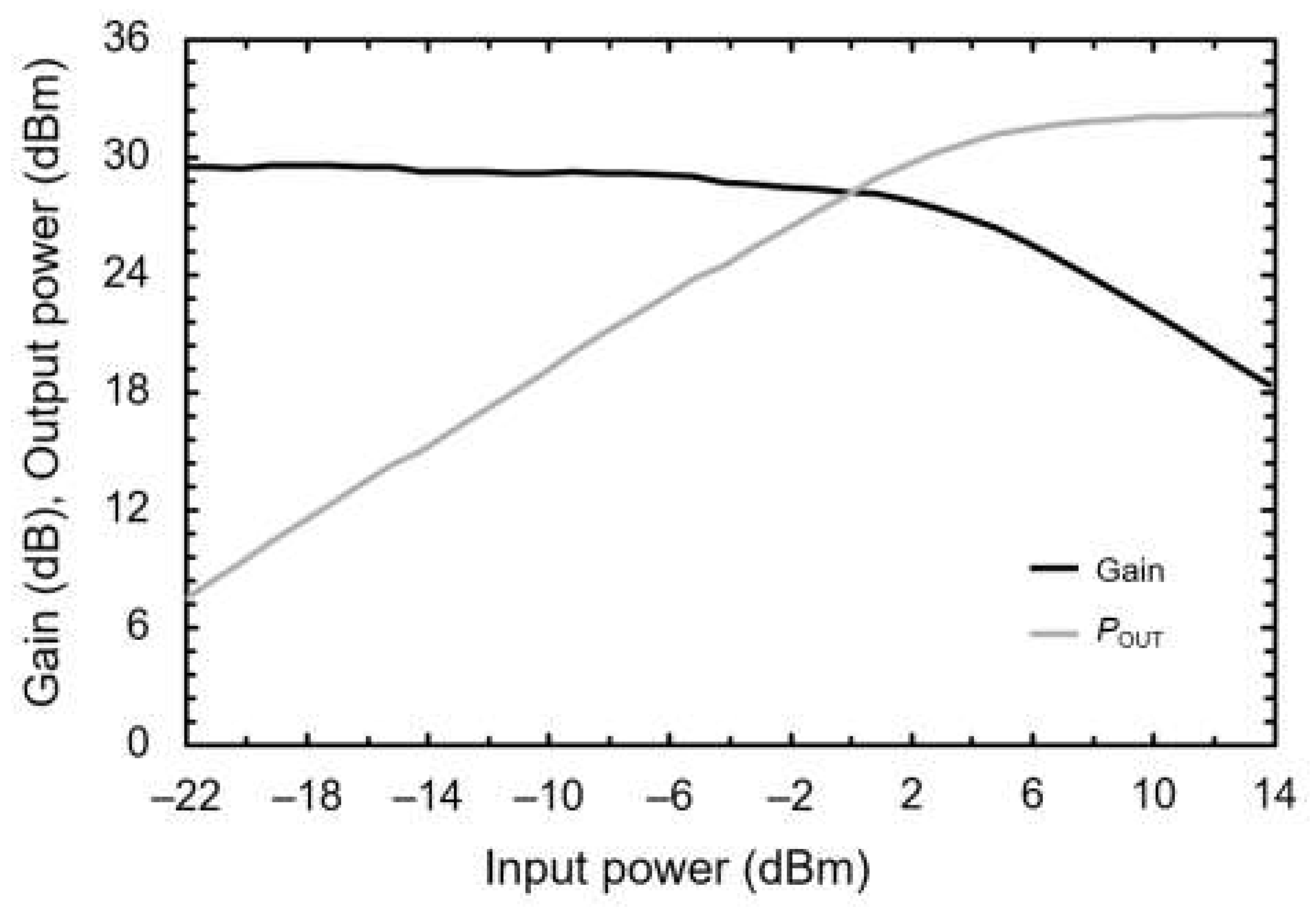

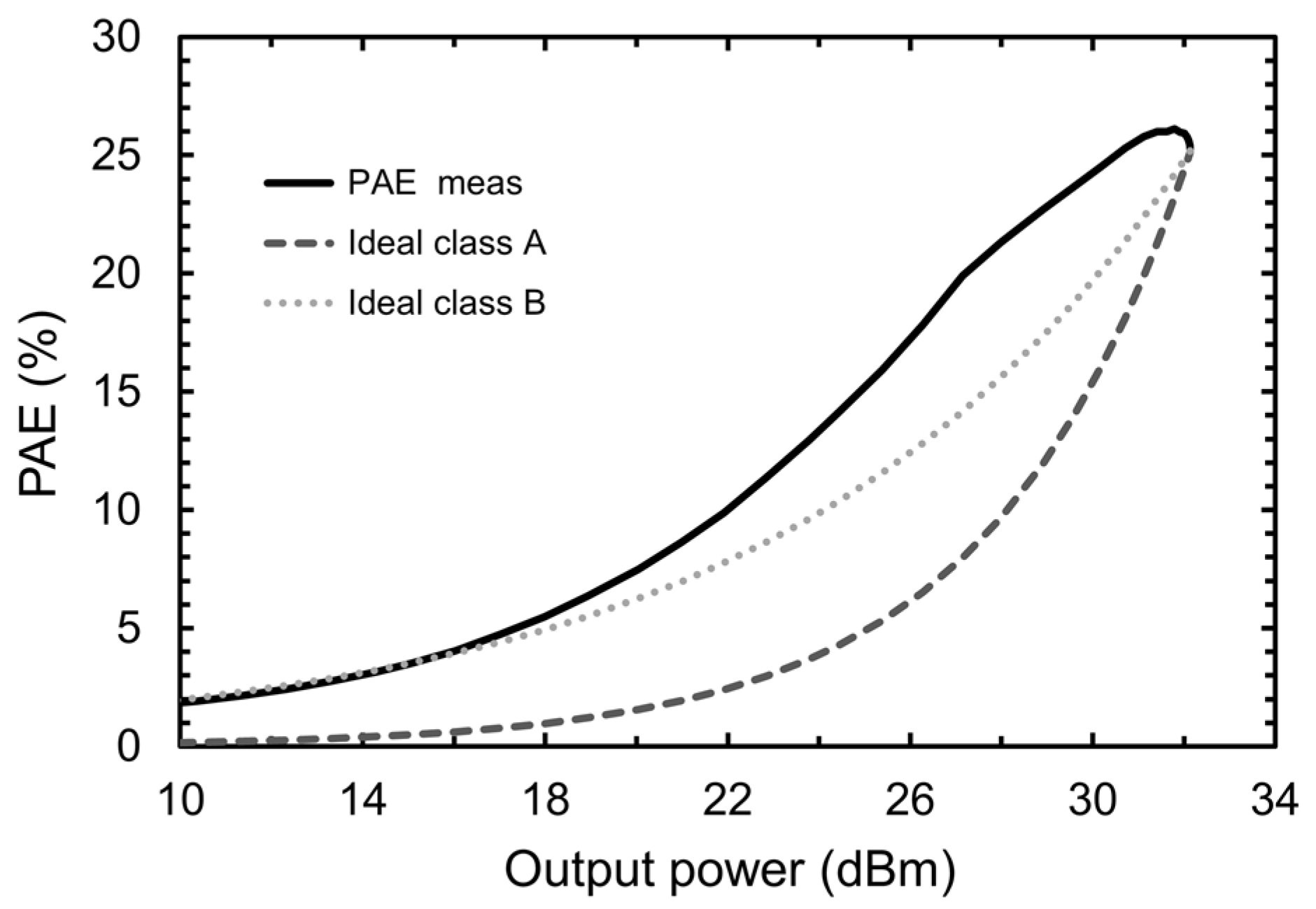

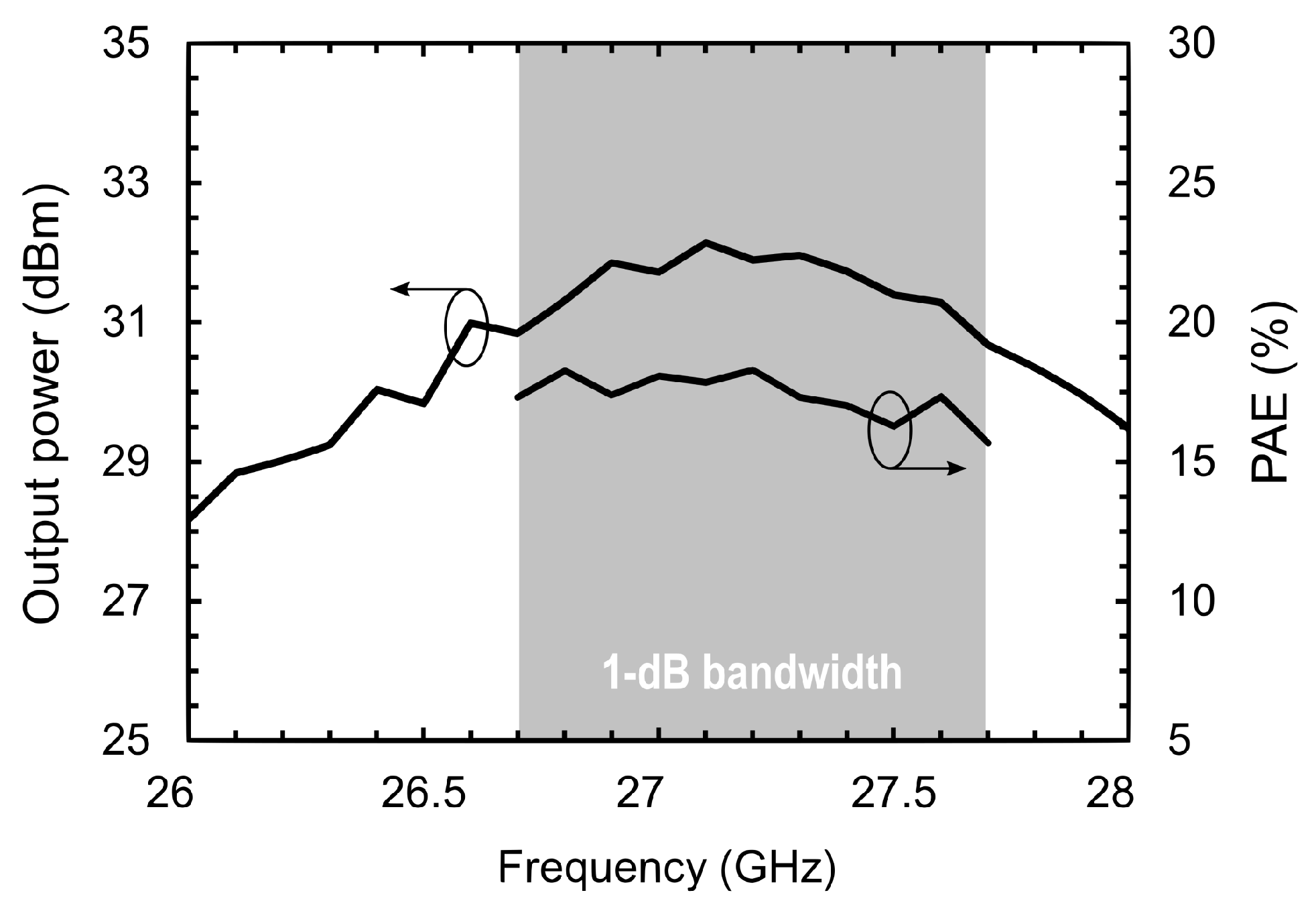

4. Experimental Results

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Erunkulu, O.O.; Zungeru, A.M.; Lebekwe, C.K.; Mosalaosi, M.; Chuma, J.M. 5G Mobile Communication Applications: A Survey and Comparison of Use Cases. IEEE Access 2021, 9, 97251–97295. [Google Scholar] [CrossRef]

- Agiwal, M.; Roy, A.; Saxena, N. Next generation 5G wireless networks: A comprehensive survey. IEEE Commun. Surv. Tutor. 2016, 18, 1617–1655. [Google Scholar] [CrossRef]

- Parvez, I.; Rahmati, A.; Guvenc, I.; Sarwat, A.I.; Dai, H. A survey on low latency towards 5G: RAN, core network and caching solutions. IEEE Commun. Surv. Tutor. 2018, 20, 3098–3130. [Google Scholar] [CrossRef]

- Gupta, A.; Jha, R.K. A survey of 5g network: Architecture and emerging technologies. IEEE Access 2015, 3, 1206–1232. [Google Scholar] [CrossRef]

- Asbeck, P.M. Will doherty continue to rule for 5g? In Proceedings of the 2016 IEEE MTT-S International Microwave Symposium (IMS), San Francisco, CA, USA, 22–27 May 2016; pp. 1–4. [Google Scholar]

- Yu, C.; Feng, J.; Zhao, D. A 28-GHz Doherty power amplifier with a compact transformer-based quadrature hybrid in 65-nm CMOS. IEEE Trans. Circuits Syst. II Exp. Briefs 2021, 68, 2790–2794. [Google Scholar] [CrossRef]

- Wang, D.; Chen, W.; Chen, X.; Liu, X.; Ghannouchi, F.M.; Feng, Z. A 24–29.5 GHz Voltage-Combined Doherty Power Amplifier Based on Compact Low-Loss Combiner. IEEE Trans. Circuits Syst. II Exp. Briefs 2021, 68, 2342–2346. [Google Scholar] [CrossRef]

- Ma, Z.; Ma, K.; Wang, K.; Meng, F. A 28 GHz Compact 3-Way Transformer-Based Parallel-Series Doherty Power Amplifier with 20.4%/14.2% PAE at 6-/12-dB Power Back-off and 25.5 dBm PSAT in 55nm Bulk CMOS. In Proceedings of the 2022 IEEE International Solid- State Circuits Conference (ISSCC), San Francisco, CA, USA, 20–26 February 2022; pp. 320–322. [Google Scholar]

- Piacibello, A.; Camarchia, V.; Colantonio, P.; Giofrè, R. 3-Way Doherty Power Amplifiers: Design Guidelines and MMIC Implementation at 28 GHz. IEEE Trans. Microw. Theory Tech. 2022, 71, 2016–2028. [Google Scholar] [CrossRef]

- Guo, R.; Tao, H.; Zhang, B. A 26 GHz Doherty power amplifier and a fully integrated 2 × 2 PA in 0.15 μm GaN HEMT process for heterogeneous integration and 5G. In Proceedings of the 2018 IEEE MTT-S International Wireless Symposium (IWS), Chengdu, China, 6–10 May 2018; pp. 1–4. [Google Scholar]

- Nakatani, K.; Yamaguchi, Y.; Komatsuzaki, Y.; Sakata, S.; Shinjo, S.; Yamanaka, K. A Ka-band high efficiency Doherty power amplifier MMIC using GaN-HEMT for 5G application. In Proceedings of the 2018 IEEE MTT-S International Microwave Workshop Series on 5G Hardware and System Technologies (IMWS-5G), Dublin, Ireland, 30–31 August 2018; pp. 1–3. [Google Scholar]

- Yamaguchi, Y.; Nakatani, K.; Shinjo, S. A wideband and high efficiency Ka-band GaN Doherty power amplifier for 5G communications. In Proceedings of the 2020 IEEE BiCMOS and Compound Semiconductor Integrated Circuits and Technology Symposium (BCICTS), Monterey, CA, USA, 16–19 November 2020; pp. 1–4. [Google Scholar]

- Giofre, R.; Gaudio, A.D.; Ciccognani, W.; Colangeli, S.; Limiti, E. A GaN-on-Si MMIC Doherty power amplifier for 5G applications. In Proceedings of the 2018 Asia-Pacific Microwave Conference (APMC), Kyoto, Japan, 6–9 November 2018; pp. 971–973. [Google Scholar]

- Wohlert, D.; Peterson, B.; Kywe, T.R.M.; Ledezma, L.; Gengler, J. 8-Watt Linear Three-Stage GaN Doherty Power Amplifier for 28 GHz 5G Applications. In Proceedings of the 2019 IEEE BiCMOS and Compound Semiconductor Integrated Circuits and Technology Symposium (BCICTS), Nashville, TN, USA, 3–6 November 2019; pp. 1–4. [Google Scholar]

- Zhao, C.; Liu, H.; Wu, Y.; Kang, K. Analysis and Design of CMOS Doherty Power Amplifier Based on Voltage Combining Method. IEEE Access 2017, 5, 5001–5012. [Google Scholar] [CrossRef]

- Srirattana, N.; Raghavan, A.; Heo, D.; Allen, P.E.; Laskar, J. Analysis and design of a high-efficiency multistage Doherty power amplifier for wireless communications. IEEE Trans. Microw. Theory Technol. 2005, 53, 852–860. [Google Scholar] [CrossRef]

- Reynaert, P.; Cao, Y.; Vigilante, M.; Indirayanti, P. Doherty techniques for 5G RF and mm-wave power amplifiers. In Proceedings of the 2016 International Symposium on VLSI Technology, Systems and Application (VLSI-TSA), Hsinchu, Taiwan, 25–27 April 2016; pp. 1–2. [Google Scholar]

- Nasri, A.; Estebsari, M.; Toofan, S.; Piacibello, A.; Pirola, M.; Camarchia, V.; Ramella, C. Broadband Class-J GaN Doherty Power Amplifier. Electronics 2022, 11, 552. [Google Scholar] [CrossRef]

- Cheng, P.; Wang, Q.; Li, W.; Jia, Y.; Liu, Z.; Feng, C.; Jiang, L.; Xiao, H.; Wang, X. A Broadband Asymmetrical GaN MMIC Doherty Power Amplifier with Compact Size for 5G Communications. Electronics 2021, 10, 311. [Google Scholar] [CrossRef]

- Zong, Z.; Tang, X.; Khalaf, K.; Yan, D.; Mangraviti, G.; Nguyen, J.; Liu, Y.; Wambacq, P. A 28 GHz Voltage-Combined Doherty Power Amplifier with a Compact Transformer-based Output Combiner in 22nm FD-SOI. In Proceedings of the 2020 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Los Angeles, CA, USA, 4–6 August 2020; pp. 299–302. [Google Scholar]

- Abounemra, A.M.E.; Chen, W.; Huang, F.; Maktoomi, M.; Zhang, W.; Helaoui, M.; Ghannouchi, F.M. Systematic Design Methodology of Broadband Doherty Amplifier Using Unified Matching/Combining Networks with an Application to GaN MMIC Design. IEEE Access 2021, 9, 5791–5805. [Google Scholar] [CrossRef]

- Zong, Z.; Tang, X.; Khalaf, K.; Yan, D.; Mangraviti, G.; Nguyen, J.; Liu, Y.; Wambacq, P. A 28-GHz SOI-CMOS Doherty power amplifier with a compact transformer-based output combiner. IEEE Trans. Microw. Theory Technol. 2021, 69, 2795–2808. [Google Scholar] [CrossRef]

- Generation Partnership Project; Technical Specification Group Radio Access Network; NR; Base Station (BS) Radio Transmission and Reception (Release 15). Standard TS 38.104, 3rd Generation Partnership Project-3GPP. v.15.5.0. Section 9. 2019. Available online: https://www.etsi.org/deliver/etsi_ts/138100_138199/138104/15.05.00_60/ts_138104v150500p.pdf (accessed on 1 March 2019).

| [9] | [10] | [11] | [12] | [13] | This Work | |

|---|---|---|---|---|---|---|

| Channel length [nm] | 150 * | 150 * | 150 * | 150 * | 100 ** | 150 * |

| Frequency [GHz] | 28 | 26 | 28 | 30 | 28 | 27 |

| PSAT [dBm] | 34 | 32 | 35.6 | 36.5 | 33 | 32.1 |

| Linear gain [dB] | 20 | 13.6 | 15.8 | 15.7 | 13.7 | 30 |

| Saturated gain [dB] | 10 | 8 | 12 | 10 | 12.5 | 22 |

| PAEMAX [%] | 22 | 21.7 | 25.5 | 31.8 | 36.2 | 26 |

| PAE @ 6 dB OPBO [%] | 15 | 20 | 22.7 | 27 | 30 | 18 |

| VDD [V] | 20 | 24 | 24 | 24 | 12 | 20 |

| Die size [mm2] | 15.6 | 5 | 4.3 | 3.5 | 6 | 7.75 |

| FoM [W/mm2] | 0.05 | 0.09 | 0.77 | 1.1 | 0.64 | 1.5 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Parisi, A.; Papotto, G.; Nocera, C.; Castorina, A.; Palmisano, G. A Ka-Band Doherty Power Amplifier in a 150 nm GaN-on-SiC Technology for 5G Applications. Electronics 2023, 12, 3639. https://doi.org/10.3390/electronics12173639

Parisi A, Papotto G, Nocera C, Castorina A, Palmisano G. A Ka-Band Doherty Power Amplifier in a 150 nm GaN-on-SiC Technology for 5G Applications. Electronics. 2023; 12(17):3639. https://doi.org/10.3390/electronics12173639

Chicago/Turabian StyleParisi, Alessandro, Giuseppe Papotto, Claudio Nocera, Alessandro Castorina, and Giuseppe Palmisano. 2023. "A Ka-Band Doherty Power Amplifier in a 150 nm GaN-on-SiC Technology for 5G Applications" Electronics 12, no. 17: 3639. https://doi.org/10.3390/electronics12173639