A 12-Bit 1-GS/s Pipelined ADC with a Novel Timing Strategy in 40-nm CMOS Process

Abstract

:1. Introduction

2. Proposed ADC Architecture and Pre-Quantization Timing

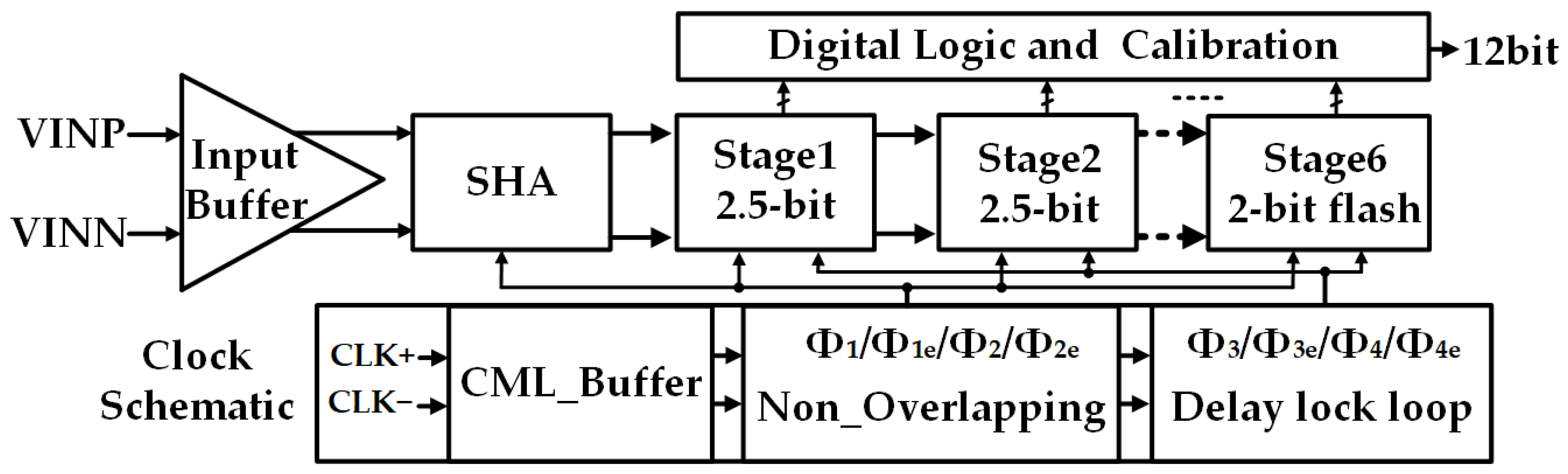

2.1. ADC Architecture

2.2. Working Timing Strategy

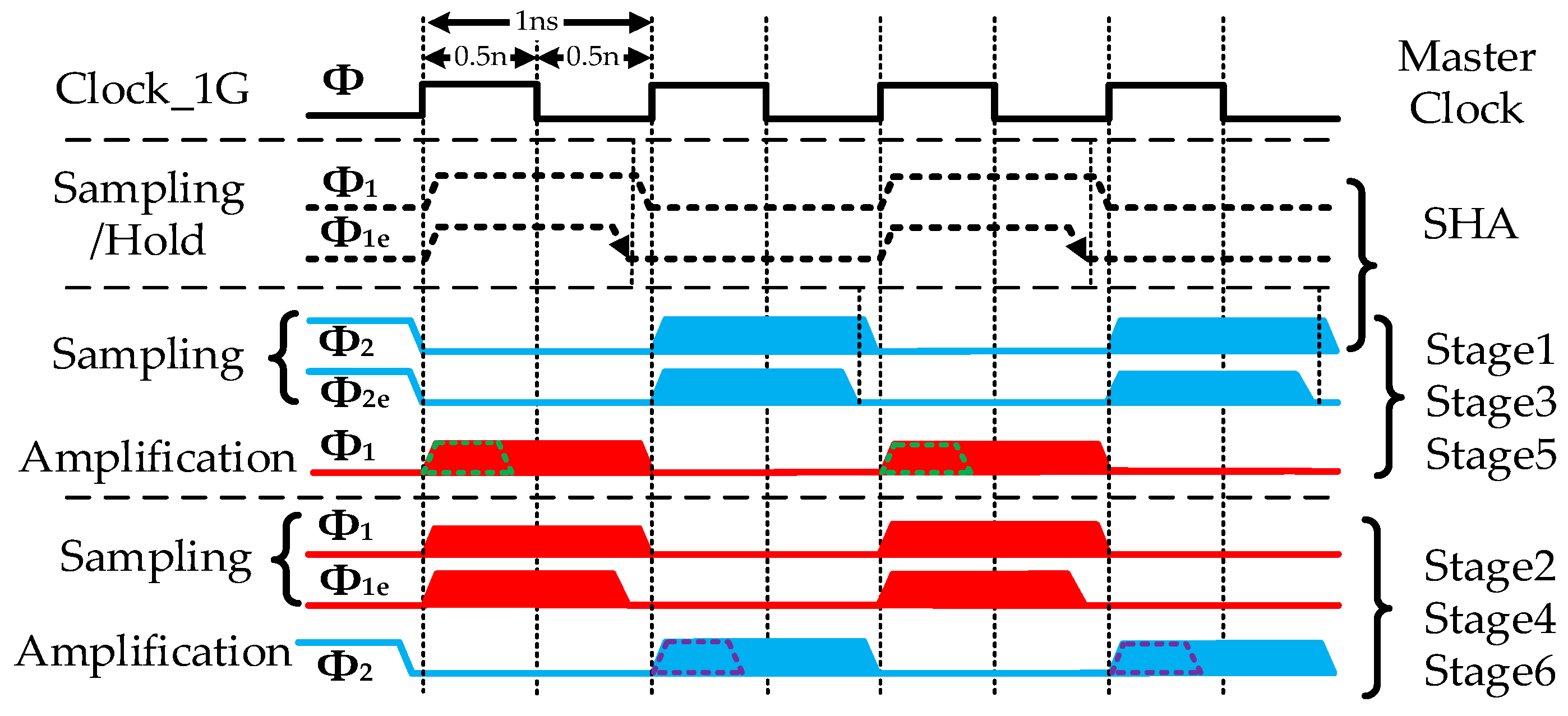

2.2.1. Traditional Working Timing

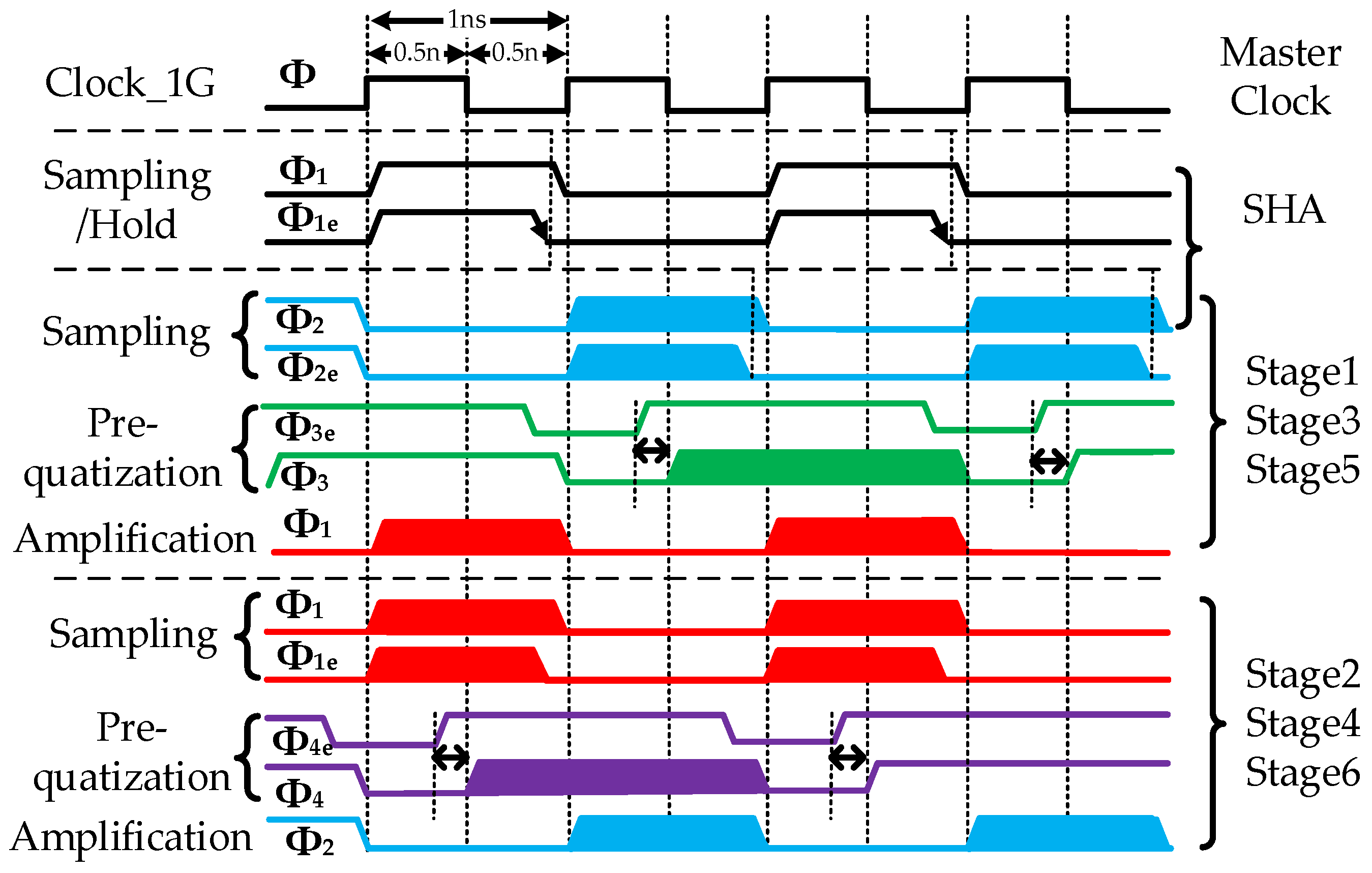

2.2.2. Pre-Quantization Timing

- Sampling: The period of Ф1 or Ф2 is double to that of Ф; when Ф1 or Ф2 are sampling clock signal, it is the square wave signal that controls the switched capacitor circuit to start sampling.

- The bottom plate sampling: Ф1e and Ф2e are early shut-down clocks; the falling edge of Ф1 is earlier than that of Ф1e, and the falling edge of Ф2e is earlier than that of Ф2, which are used to ensure the bottom plate sampling technology;

- Pre-quantization: Ф3 and Ф4 are clocks for the comparator. The high voltages of Ф3 and Ф4 are at the half voltages of Ф2 or Ф1, respectively. The comparator occupies about 250 ps of time to complete quantization. During the phases of Ф3 and Ф4, comparators reset the output to a high voltage 100 ps early.

- Amplification: clock for amplification. Ф1 is the non-overlapping clock signal of Ф2 (Ф2 is the non-overlapping clock signal of Ф1), used to control the op-amp to start amplifying at the high level.

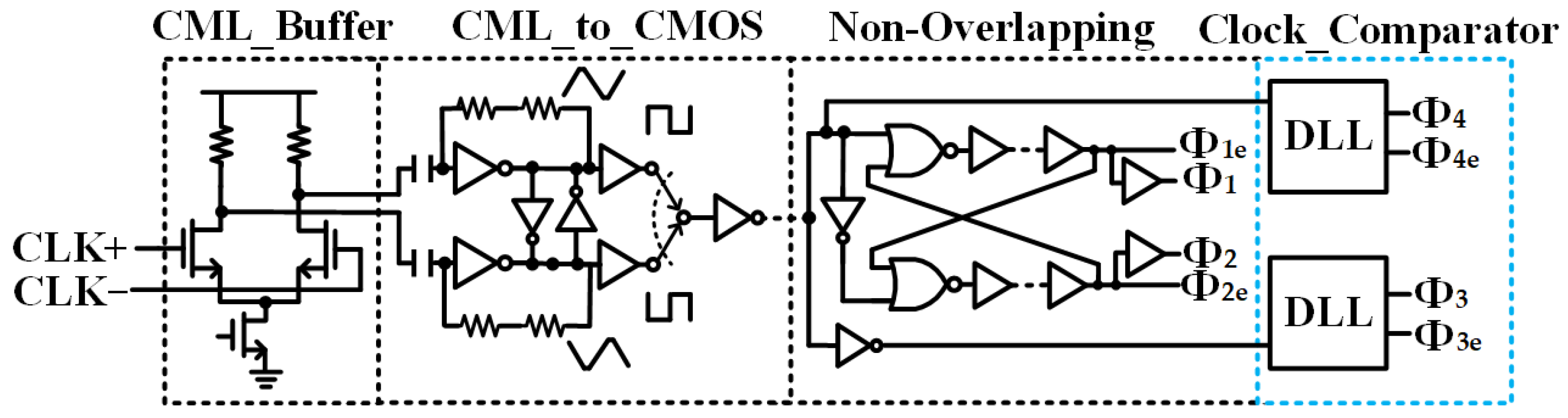

2.2.3. Clock Generation Circuit of PQT

3. Circuit Implementation and Calibration

3.1. DLL in Clock Generation Circuit

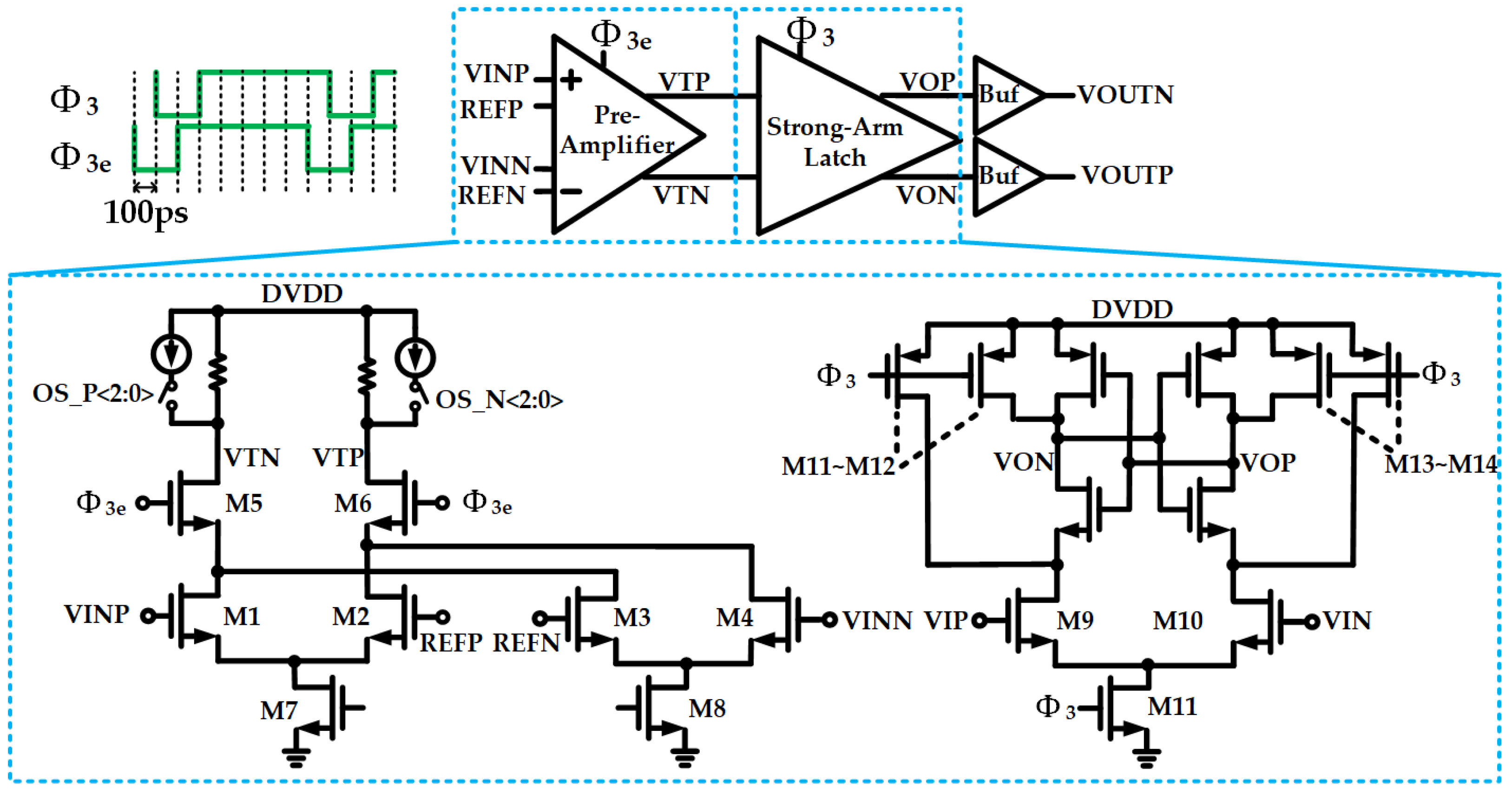

3.2. Four-Port Comparator in Sub-ADCs

3.3. Flip-Around Sample and Hold Amplifier (SHA)

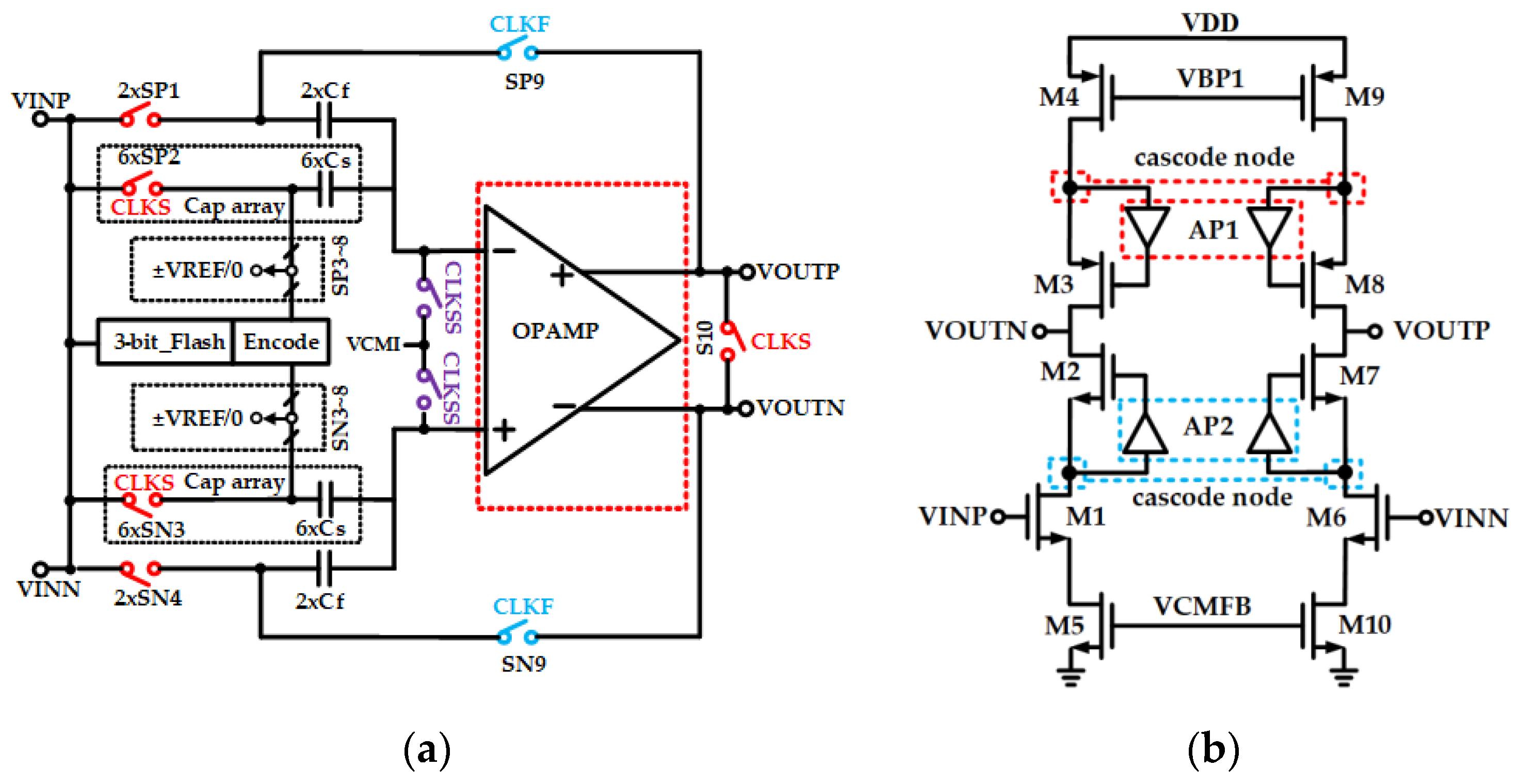

3.4. Operational Amplifier (Op-Amp) in the SHA or MDACs

3.5. Calibration of Mismatches and Errors

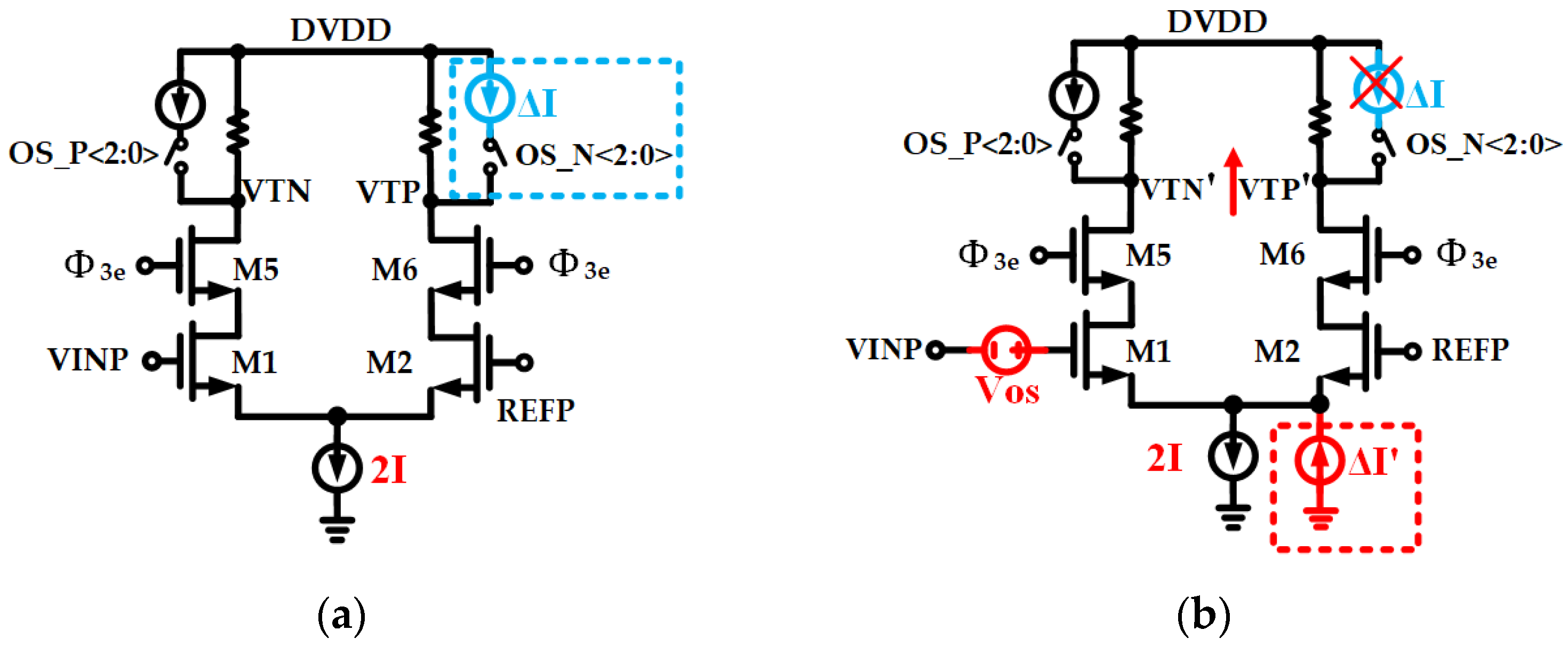

3.5.1. Calibration of Offset Voltage

- The first method is to add an adjustable capacitor to the output of the comparator. However, this method increases the load on the circuit and affects the switching speed of the comparator [32];

- The second option is to reduce the input offset of the comparator by adjusting the substrate voltage. However, separating the substrates of MOSFETs in a CMOS process requires the use of special deep-well devices [11];

- The third way is to calibrate the offset of the comparator through the auxiliary differential pair. By adding auxiliary differential pairs, this solution inevitably increases the noise of the comparator [33];

- In theory, adding an adjustable current source can adjust the offset of the comparator [34]. As can be seen from Section 3.3, bias current is placed in the output of the preamplifier in this design. The advantages of this method are low noise and ease in matching the calibration of the residual curve.

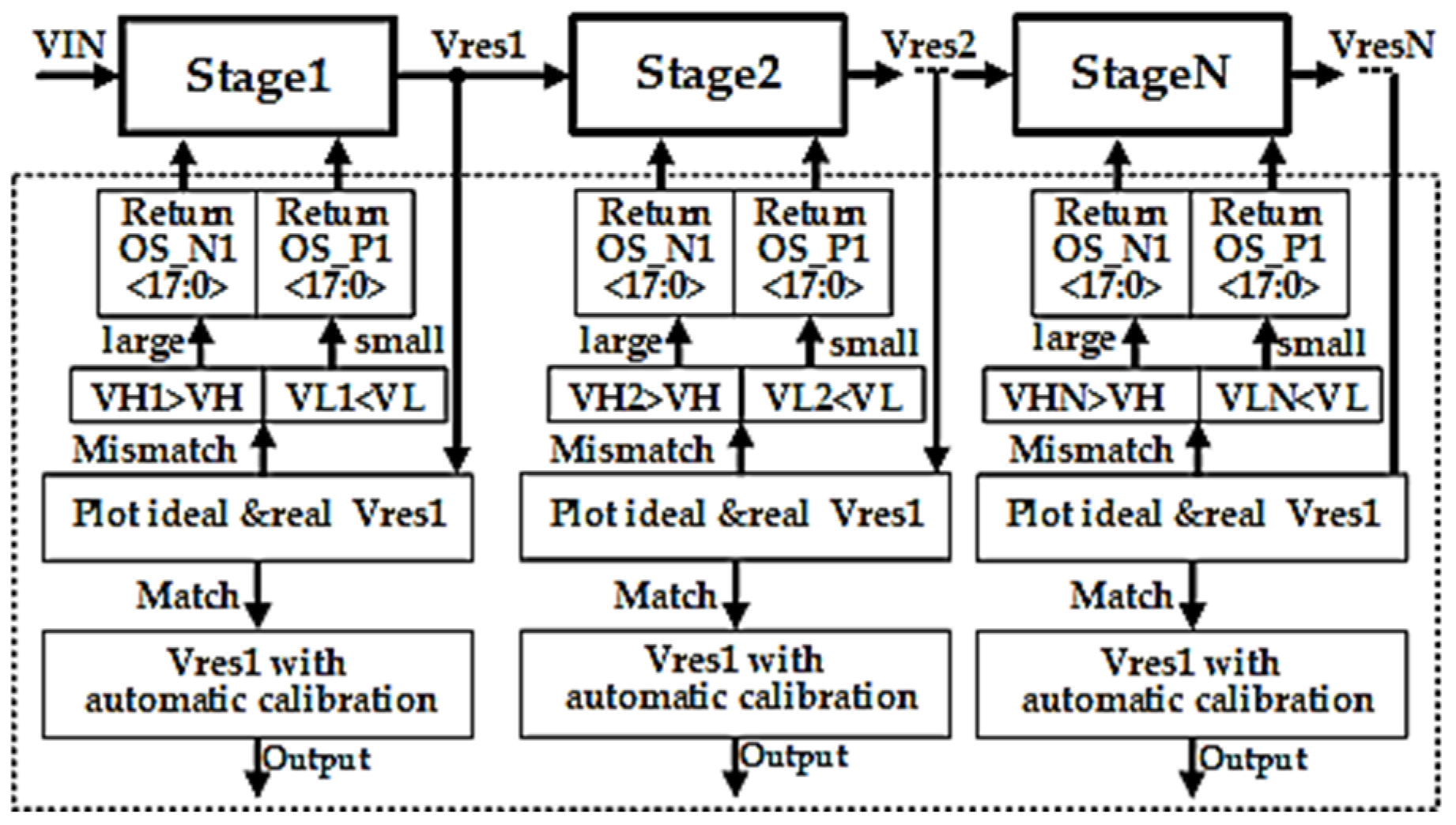

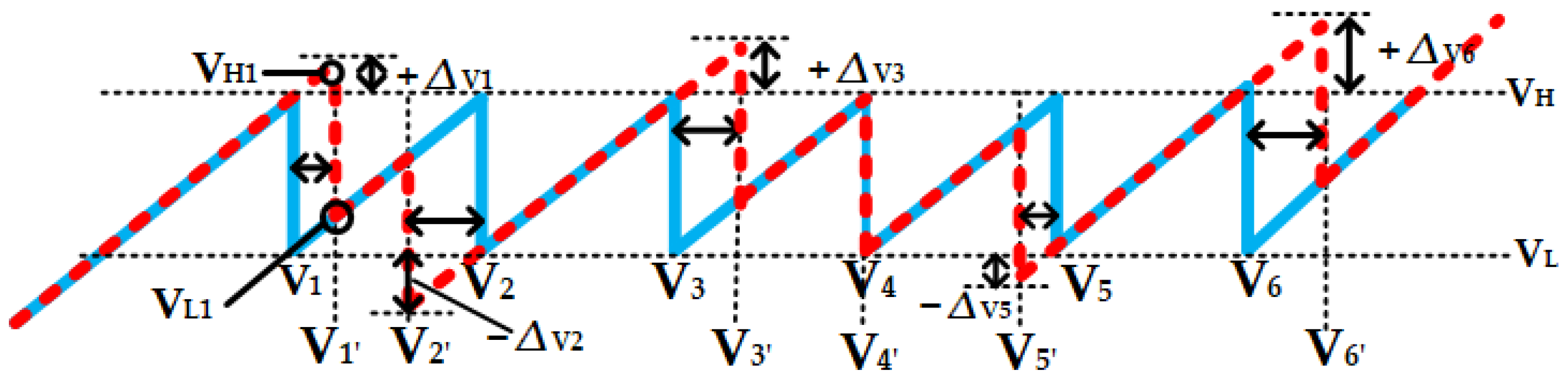

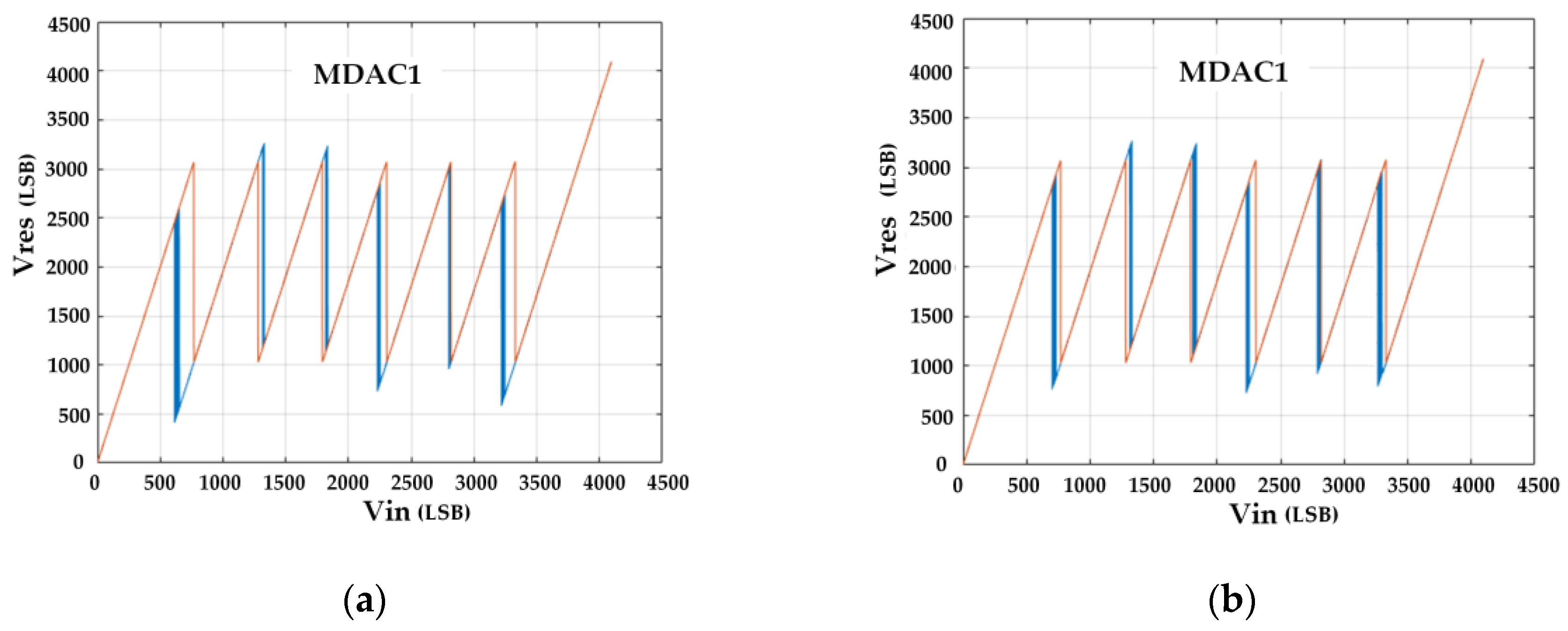

3.5.2. Automatic Calibration of Residual Curves

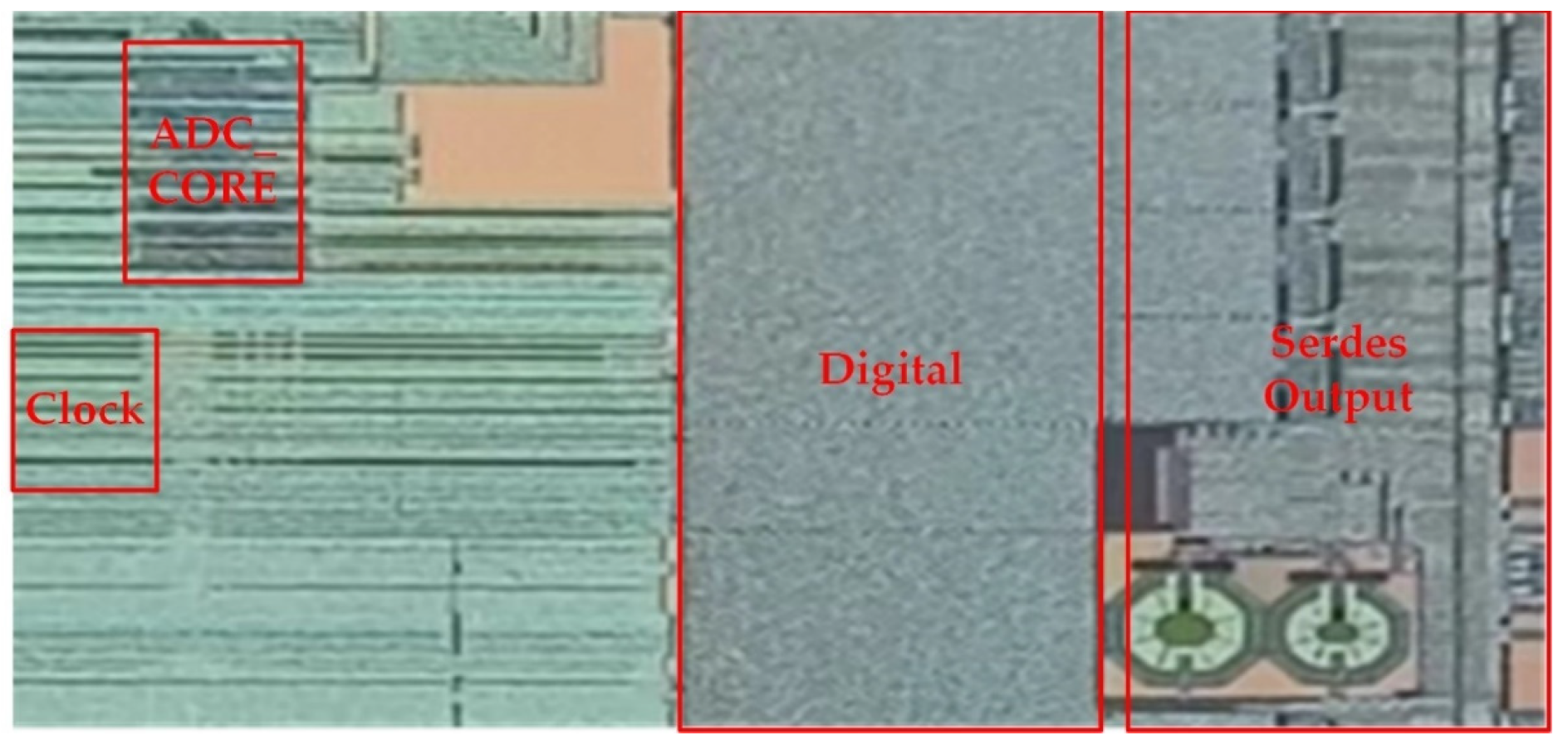

4. Measured Results and Discussion

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Niu, H.; Yuan, J. A Spectral-Correlation-Based Blind Calibration Method for Time-Interleaved ADCs. IEEE Trans. Circuits Syst. I Regul. Pap. 2020, 67, 5007–5017. [Google Scholar] [CrossRef]

- Jiang, W.; Zhu, Y.; Zhang, M.; Chan, C.H.; Martins, R.P. A Temperature-Stabilized Single-Channel 1-GS/s 60-dB SNDR SAR-Assisted Pipelined ADC with Dynamic Gm-R-Based Amplifier. IEEE J. Solid-State Circuits 2020, 55, 322–332. [Google Scholar] [CrossRef]

- Ramkaj, A.T.; Ramos, J.C.P.; Pelgrom, M.J.M.; Steyaert, M.S.J.; Verhelst, M.; Tavernier, F. A 5-GS/s 158.6-mW 9.4-ENOB Passive-Sampling Time-Interleaved Three-Stage Pipelined-SAR ADC with Analog–Digital Corrections in 28-nm CMOS. IEEE J. Solid-State Circuits 2020, 55, 1553–1564. [Google Scholar] [CrossRef]

- Wu, C.; Yuan, J. A 12-Bit, 300-MS/s Single-Channel Pipelined-SAR ADC With an Open-Loop MDAC. IEEE J. Solid-State Circuits 2019, 54, 1446–1454. [Google Scholar] [CrossRef]

- Guangming, Y.; Sansen, W. A high-frequency and high-resolution fourth-order /spl Sigma//spl Delta/ A/D converter in BiCMOS technology. IEEE J. Solid-State Circuits 1994, 29, 857–865. [Google Scholar] [CrossRef]

- Walden, R.H. Analog-to-digital converter survey and analysis. IEEE J. Sel. Areas Commun. 1999, 17, 539–550. [Google Scholar] [CrossRef]

- Li, J.; Guo, X.; Luan, J.; Wu, D.; Zhou, L.; Huang, Y.; Wu, N.; Jia, H.; Zheng, X.; Wu, J.; et al. A 3GSps 12-bit four-channel time-interleaved pipelined ADC in 40 nm CMOS process. Electronics 2019, 8, 1551. [Google Scholar] [CrossRef]

- Bae, C.; Shin, S.; Jung, J.; Park, M.; Kwon, K.; Kim, J.; Jung, T.; Choi, J. An 11-bit Ring Amplifier Pipeline ADC with Settling-Time Improvement Scheme. In Proceedings of the 2020 International Conference on Electronics, Information, and Communication (ICEIC), Shenzhen, China, 19–22 January 2020; pp. 1–4. [Google Scholar]

- Hershberg, B.; Dermit, D.; Liempd, B.; Martens, E.; Markulic, N.; Lagos, J.; Craninckx, J. 3.1 A 3.2GS/s 10 ENOB 61mW Ringamp ADC in 16 nm with Background Monitoring of Distortion. In Proceedings of the 2019 IEEE International Solid-State Circuits Conference—(ISSCC), San Francisco, CA, USA, 17–21 February 2019; pp. 58–60. [Google Scholar]

- Louwsma, S.M.; Tuijl, A.J.M.; Vertregt, M.; Nauta, B. A 1.35 GS/s, 10 b, 175 mW Time-Interleaved AD Converter in 0.13 µm CMOS. IEEE J. Solid-State Circuits 2008, 43, 778–786. [Google Scholar] [CrossRef]

- Zheng, X.; Wang, Z.; Li, F.; Zhao, F.; Yue, S.; Zhang, C.; Wang, Z. A 14-bit 250 MS/s IF Sampling Pipelined ADC in 180 nm CMOS Process. IEEE Trans. Circuits Syst. I Regul. Pap. 2016, 63, 1381–1392. [Google Scholar] [CrossRef]

- Carnes, J.; Un-Ku, M. The Effect of Switch Resistance on Pipelined ADC MDAC Settling Time. In Proceedings of the 2006 IEEE International Symposium on Circuits and Systems (ISCAS), Island of Kos, Greece, 21–24 May 2006; p. 4. [Google Scholar]

- Li, F.; Wang, Z.; Li, D. An Incomplete Settling Technique for Pipelined Analog-to-Digital Converters. In Proceedings of the 2007 IEEE International Symposium on Circuits and Systems, New Orleans, LA, USA, 27–30 May 2007; pp. 3590–3593. [Google Scholar]

- Zhang, M.; Zhu, Y.; Chan, C.H.; Martins, R.P. An 8-Bit 10-GS/s 16× Interpolation-Based Time-Domain ADC with <1.5-ps Uncalibrated Quantization Steps. IEEE J. Solid-State Circuits 2020, 55, 3225–3235. [Google Scholar]

- Zhu, S.; Wu, B.; Cai, Y.; Chiu, Y. A 2-GS/s 8-bit Non-Interleaved Time-Domain Flash ADC Based on Remainder Number System in 65-nm CMOS. IEEE J. Solid-State Circuits 2018, 53, 1172–1183. [Google Scholar] [CrossRef]

- Sahoo, B.D.; Razavi, B. A 10-b 1-GHz 33-mW CMOS ADC. IEEE J. Solid-State Circuits 2013, 48, 1442–1452. [Google Scholar] [CrossRef]

- Kratyuk, V.; Hanumolu, P.K.; Ok, K.; Moon, U.K.; Mayaram, K. A Digital PLL with a Stochastic Time-to-Digital Converter. IEEE Trans. Circuits Syst. I Regul. Pap. 2009, 56, 1612–1621. [Google Scholar] [CrossRef]

- Xu, H.; Abidi, A.A. Analysis and Design of Regenerative Comparators for Low Offset and Noise. IEEE Trans. Circuits Syst. I Regul. Pap. 2019, 66, 2817–2830. [Google Scholar] [CrossRef]

- Ali, A.M.A.; Dillon, C.; Sneed, R.; Morgan, A.S.; Bardsley, S.; Kornblum, J.; Wu, L. A 14-bit 125 MS/s IF/RF Sampling Pipelined ADC with 100 dB SFDR and 50 fs Jitter. IEEE J. Solid-State Circuits 2006, 41, 1846–1855. [Google Scholar] [CrossRef]

- Li, J.; Zeng, X.; Xie, L.; Chen, J.; Zhang, J.; Guo, Y. A 1.8-V 22-mW 10-bit 30-MS/s Pipelined CMOS ADC for Low-Power Subsampling Applications. IEEE J. Solid-State Circuits 2008, 43, 321–329. [Google Scholar] [CrossRef]

- Yang, P.; Wang, X.; Wang, C.; Li, F.; Jiang, H.; Wang, Z. A 14-bit 200-Ms/s SHA-Less Pipelined ADC with Aperture Error Reduction. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2020, 28, 2004–2013. [Google Scholar] [CrossRef]

- Naderi, M.H.; Silva-Martinez, J. Algorithmic-Pipelined ADC with a Modified Residue Curve for Better Linearity. In Proceedings of the 2017 IEEE 60th International Midwest Symposium on Circuits and Systems (MWSCAS), Boston, MA, USA, 6–9 August 2017; pp. 1446–1449. [Google Scholar]

- Lee, Z.M.; Wang, C.Y.; Wu, J.T. A CMOS 15-bit 125-MS/s Time-Interleaved ADC with Digital Background Calibration. IEEE J. Solid-State Circuits 2007, 42, 2149–2160. [Google Scholar] [CrossRef]

- Cao, Y.; Zhang, S.; Zhang, T.; Chen, Y.; Zhao, Y.; Chen, C.; Ye, F.; Ren, J. A 91.0-dB SFDR Single-Coarse Dual-Fine Pipelined-SAR ADC with Split-Based Background Calibration in 28-nm CMOS. IEEE Trans. Circuits Syst. I Regul. Pap. 2021, 68, 641–654. [Google Scholar] [CrossRef]

- Jia, H.; Guo, X.; Wu, D.; Zhou, L.; Luan, J.; Wu, N.; Huang, Y.; Zheng, X.; Wu, J.; Liu, X. A 12-Bit 2.4 GS/s Four-Channel Pipelined ADC with a Novel On-Chip Timing Mismatch Calibration. Electronics 2020, 9, 910. [Google Scholar] [CrossRef]

- Jithin, G.; Prasad, G.B.V.S.V.; Krishna, J.V.N.S.; Pande, K.S. Strong Single-Arm Latch Comparator with Reduced Power Consumption. In Proceedings of the 2021 Fourth International Conference on Electrical, Computer and Communication Technologies (ICECCT), Erode, India, 15–17 September 2021; pp. 1–6. [Google Scholar]

- Brandolini, M.; Shin, Y.J.; Raviprakash, K.; Wang, T.; Wu, R.; Geddada, H.M.; Ko, Y.J.; Ding, Y.; Huang, C.S.; Shih, W.T.; et al. A 5 GS/s 150 mW 10 b SHA-Less Pipelined/SAR Hybrid ADC for Direct-Sampling Systems in 28 nm CMOS. IEEE J. Solid-State Circuits 2015, 50, 2922–2934. [Google Scholar] [CrossRef]

- Devarajan, S.; Singer, L.; Kelly, D.; Pan, T.; Silva, J.; Brunsilius, J.; Rey-Losada, D.; Murden, F.; Speir, C.; Bray, J.; et al. A 12-b 10-GS/s Interleaved Pipeline ADC in 28-nm CMOS Technology. IEEE J. Solid-State Circuits 2017, 52, 3204–3218. [Google Scholar] [CrossRef]

- Zhu, C.; Lin, J.; Wang, Z. Background Calibration of Comparator Offsets in SHA-Less Pipelined ADCs. IEEE Trans. Circuits Syst. II Express Briefs 2019, 66, 357–361. [Google Scholar] [CrossRef]

- Huang, P.; Hsien, S.; Lu, V.; Wan, P.; Lee, S.C.; Liu, W.; Chen, B.W.; Lee, Y.P.; Chen, W.T.; Yang, T.Y.; et al. SHA-Less Pipelined ADC with In Situ Background Clock-Skew Calibration. IEEE J. Solid-State Circuits 2011, 46, 1893–1903. [Google Scholar] [CrossRef]

- Chuang, S.Y.; Sculley, T.L. A digitally self-calibrating 14-bit 10-MHz CMOS pipelined A/D converter. IEEE J. Solid-State Circuits 2002, 37, 674–683. [Google Scholar] [CrossRef]

- Chan, C.H.; Zhu, Y.; Chio, U.F.; Sin, S.W.; Seng-Pan, U.; Martins, R.P. A Voltage-Controlled Capacitance Offset Calibration Technique for High Resolution Dynamic Comparator. In Proceedings of the 2009 International SoC Design Conference (ISOCC), Busan, Republic of Korea, 22–24 November 2009; pp. 392–395. [Google Scholar]

- Atherton, J.H.; Simmonds, H.T. An offset reduction technique for use with CMOS integrated comparators and amplifiers. IEEE J. Solid-State Circuits 1992, 27, 1168–1175. [Google Scholar] [CrossRef]

- Katyal, V.; Geiger, R.L.; Chen, D.J. A New High Precision Low Offset Dynamic Comparator for High Resolution High Speed ADCs. In Proceedings of the 2006 IEEE Asia Pacific Conference on Circuits and Systems, Singapore, 4–7 December 2006; pp. 5–8. [Google Scholar]

- Guhados, S.; Hurst, P.J.; Lewis, S.H. A Pipelined ADC with Metastability Error Rate <10−15 Errors/Sample. IEEE J. Solid-State Circuits 2012, 47, 2119–2128. [Google Scholar]

- Lagos, J.; Hershberg, B.; Martens, E.; Wambacq, P.; Craninckx, J. A 1Gsps, 12-bit, Single-Channel Pipelined ADC with Dead-Zone-Degenerated Ring Amplifiers. In Proceedings of the 2018 IEEE Custom Integrated Circuits Conference (CICC), San Diego, CA, USA, 8–11 April 2018; pp. 1–4. [Google Scholar]

- Naderi, M.H.; Park, C.; Prakash, S.; Kinyua, M.; Soenen, E.G.; Silva-Martinez, J. A 27.7 fJ/conv-step 500 MS/s 12-Bit Pipelined ADC Employing a Sub-ADC Forecasting Technique and Low-Power Class AB Slew Boosted Amplifiers. IEEE Trans. Circuits Syst. I Regul. Pap. 2019, 66, 3352–3364. [Google Scholar] [CrossRef]

- Moon, K.J.; Oh, D.R.; Choi, M.; Ryu, S.T. A 28-nm CMOS 12-Bit 250-MS/s Voltage-Current-Time Domain 3-Stage Pipelined ADC. IEEE Trans. Circuits Syst. II Express Briefs 2020, 67, 2843–2847. [Google Scholar] [CrossRef]

- Hung, T.C.; Liao, F.W.; Kuo, T.H. A 12-Bit Time-Interleaved 400-MS/s Pipelined ADC with Split-ADC Digital Background Calibration in 4,000 Conversions/Channel. IEEE Trans. Circuits Syst. II Express Briefs 2019, 66, 1810–1814. [Google Scholar] [CrossRef]

| Mismatches and Errors | Calibration Method | On Chip |

|---|---|---|

| Threshold offset | Adjustable current source | Yes |

| Cap mismatches | Efuse combined with multi-target search | No |

| Finite inter-stage gain | Injection of dither in stage1~3 | No |

| Residual curve | Automatic calibration by plotting Vres | Yes |

| [35] | [36] | [37] | [38] | [39] | This Work | |

|---|---|---|---|---|---|---|

| Technology | 250 nm | 28 nm | 40 nm | 28 nm | 40 nm | 40 nm |

| Voltage (V) | - | 0.9 | 1.1 | 1.0 | 1 | 1.8 |

| Resolution (bit) | 10 | 12 | 12 | 12 | 12 | 12 |

| Sampling Rate (Gsps) | 0.08 | 1 | 0.5 | 0.25 | 400 | 1 |

| ENOB (bit) * | - | 9.1 | - | - | 9.40 | 9.2 |

| SNDR (dB) * | 58.3 | 56.6 | 64.10 | 61.5 | 58.4 | 57.3 |

| SFDR (dB) * | - | 73.1 | 75.51 | - | - | 78.54 |

| Area (mm2) | 4 | 0.54 | 0.9 | 0.032 | 0.71 | 2.16 |

| Power(mW) | 72 | 24.8 | 18.15 | 5.4 | 74 | 97.6 |

| FoM (pj/step) | - | 45 | 27.71 | 22.2 | 339 | 172.9 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Xu, F.; Guo, X.; Li, Z.; Jia, H.; Wu, D.; Wu, J. A 12-Bit 1-GS/s Pipelined ADC with a Novel Timing Strategy in 40-nm CMOS Process. Electronics 2023, 12, 924. https://doi.org/10.3390/electronics12040924

Xu F, Guo X, Li Z, Jia H, Wu D, Wu J. A 12-Bit 1-GS/s Pipelined ADC with a Novel Timing Strategy in 40-nm CMOS Process. Electronics. 2023; 12(4):924. https://doi.org/10.3390/electronics12040924

Chicago/Turabian StyleXu, Fangyuan, Xuan Guo, Zeyu Li, Hanbo Jia, Danyu Wu, and Jin Wu. 2023. "A 12-Bit 1-GS/s Pipelined ADC with a Novel Timing Strategy in 40-nm CMOS Process" Electronics 12, no. 4: 924. https://doi.org/10.3390/electronics12040924