A Non-Linear Successive Approximation Finite State Machine for ADCs with Robust Performance

Abstract

:1. Introduction

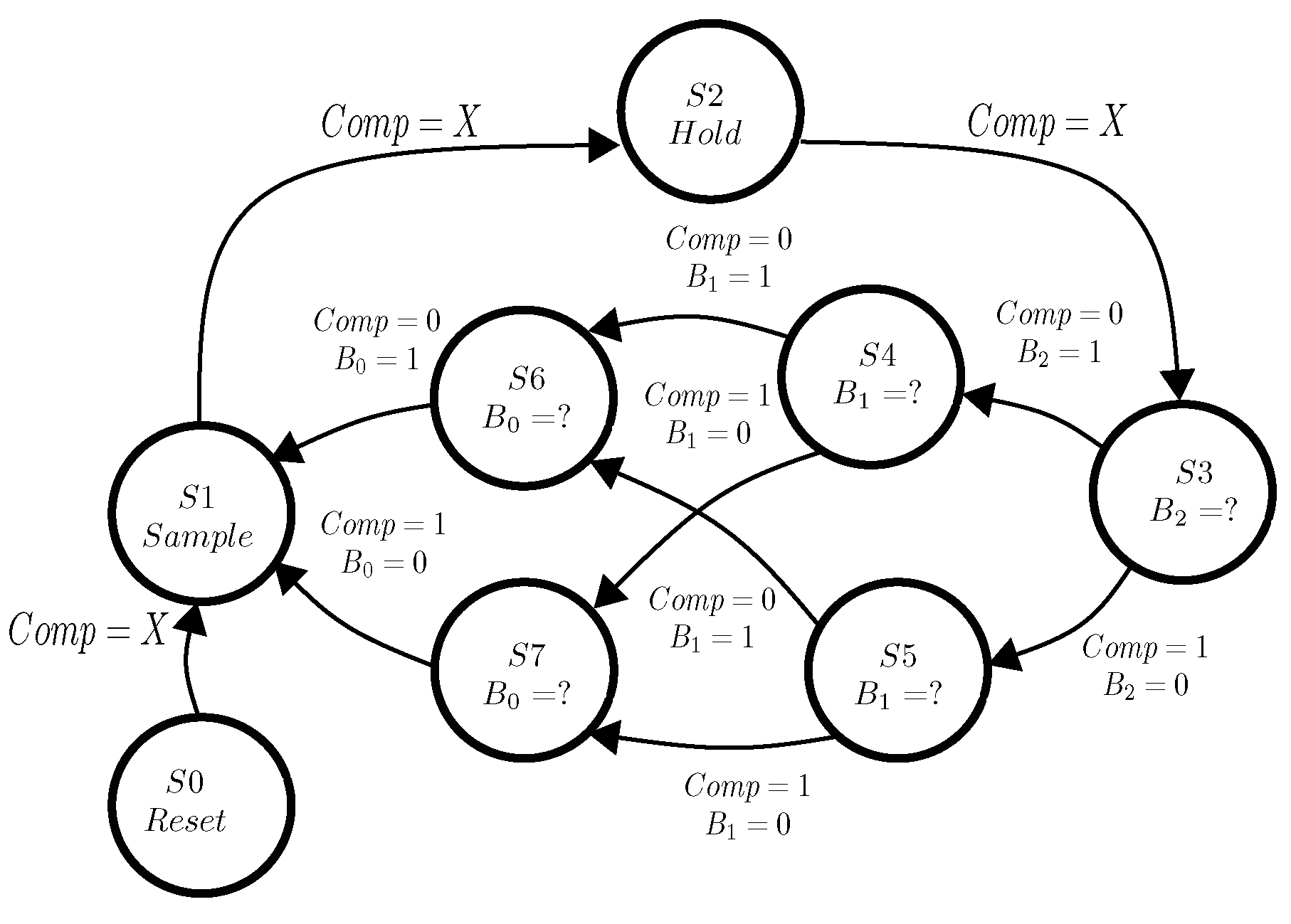

2. Successive Approximation Register (SAR) Control

| Listing 1. FSM Logic SAR for ADC 3 bits single-ended Unipolar. |

|

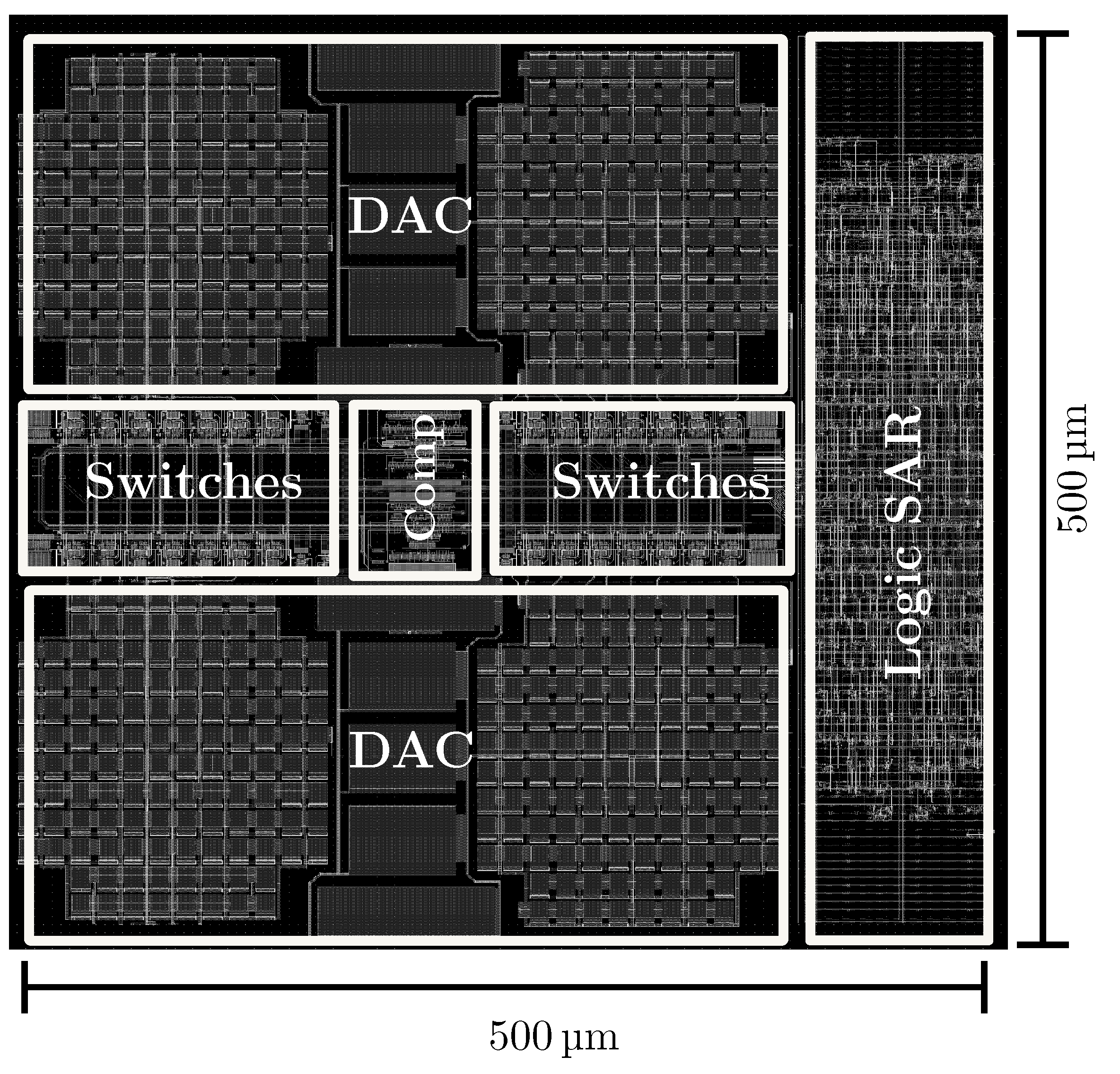

3. The ADC SAR Circuit Design

3.1. DAC Split Capacitor Array

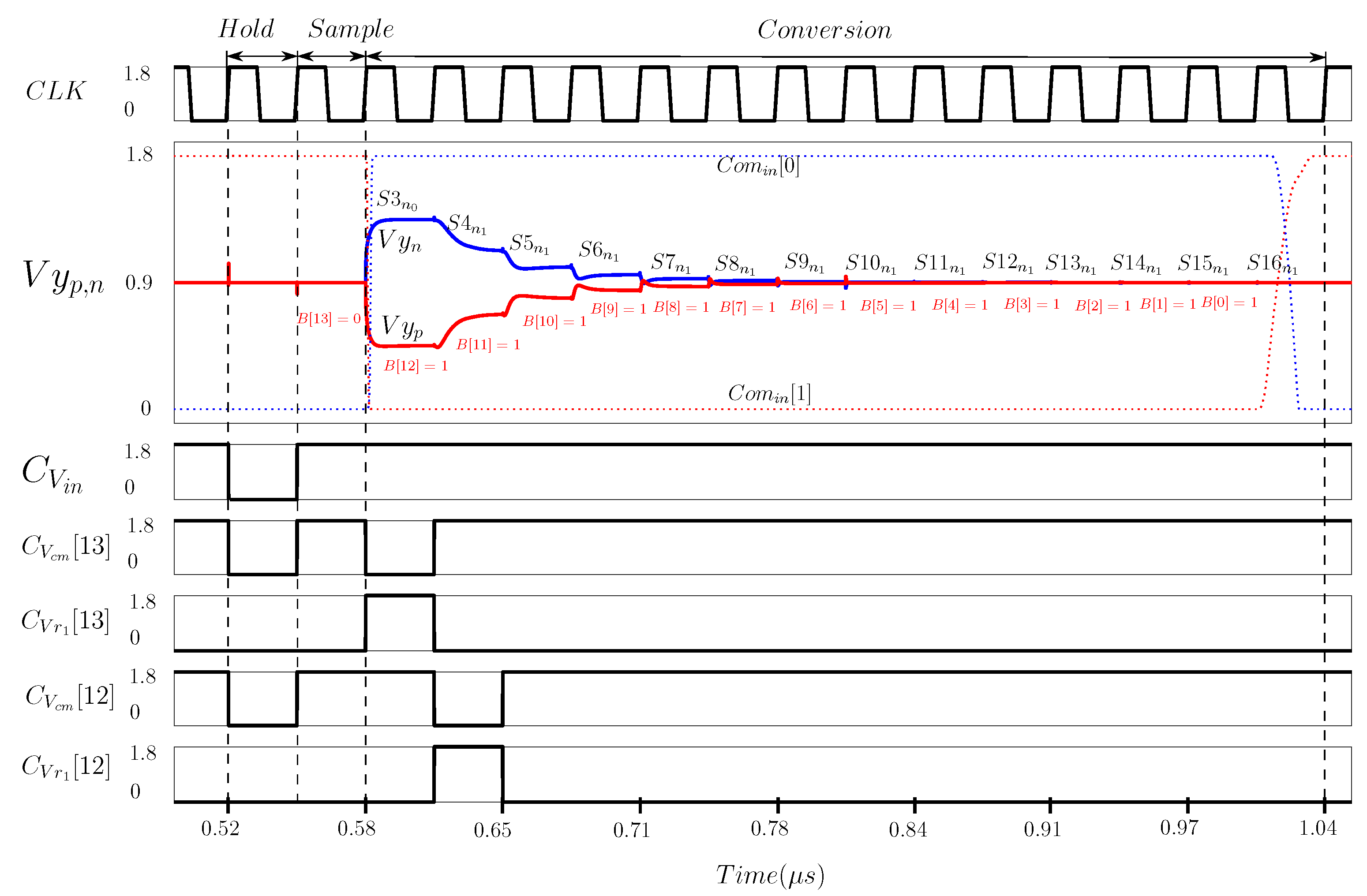

3.2. Nonlinear Successive Approximation Logic

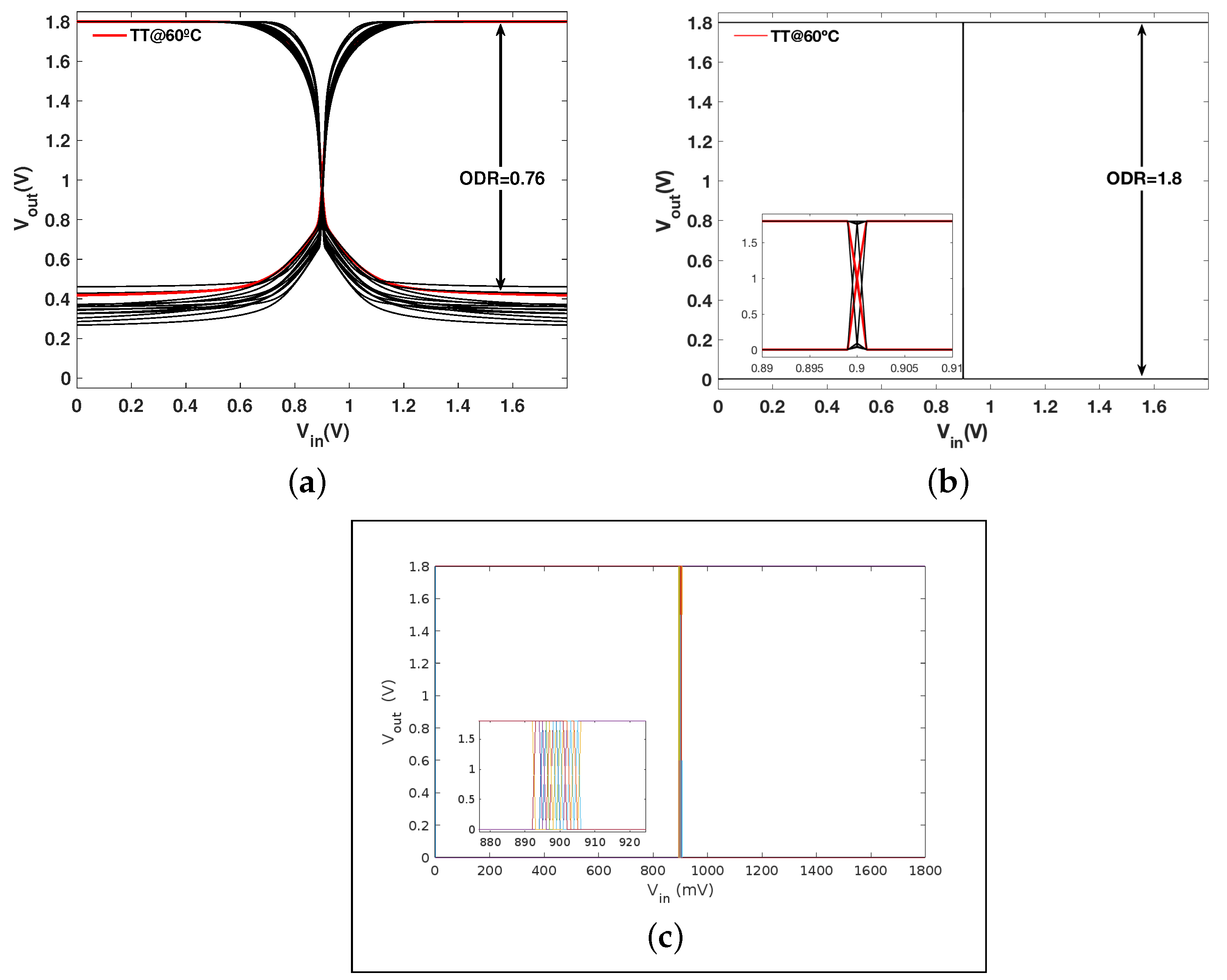

3.3. Fully Differential Robust Comparator Design

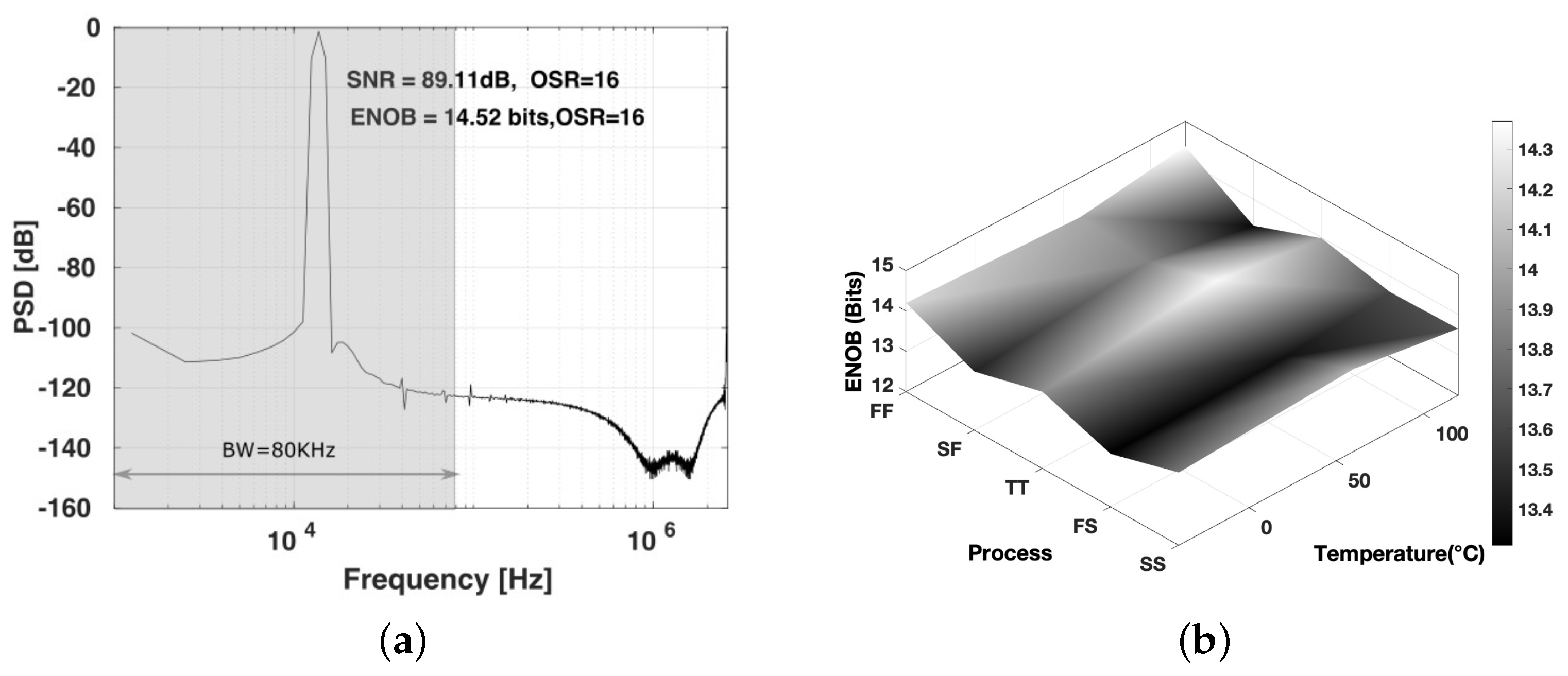

4. Post-Layout Characterization and Results

Comments on the Simulation Results

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Lakshmi, P.V.; Musala, S.; Srinivasulu, A.; Ravariu, C. Design of a 0.4 V, 8.43 ENOB, 5.29 nW, 2 kS/s SAR ADC for Implantable Devices. Electronics 2023, 12, 4691. [Google Scholar] [CrossRef]

- Chung, Y.H.; Chiang, M.S. A 12-Bit Synchronous-SAR ADC for IoT Applications. In Proceedings of the 2019 IEEE International Symposium on Circuits and Systems (ISCAS), Hokkaido, Japan, 26–29 May 2019; pp. 1–5. [Google Scholar] [CrossRef]

- Wei, Y.; Wu, T.; Ma, S.; Ren, J. A Multi-channel 12-bits 100MS/s SAR ADC in 65nm CMOS. In Proceedings of the 2023 IEEE 15th International Conference on ASIC (ASICON), Nanjing, China, 24–27 October 2023; pp. 1–4. [Google Scholar] [CrossRef]

- Meier, D.; Ackermann, J.; Olsen, A.; Kristian, H.; Berge, H.; Hasanbegovic, A.; Altan, A.; Azman, S.; Najafiuchevler, B.; Talebi, J.; et al. SIPHRA 16-Channel Silicon Photomultiplier Readout ASIC. In Proceedings of the AMICSA and DSP 2016, Gothenburg, Sweden, 12–16 June 2016. [Google Scholar] [CrossRef]

- Murmann, B. ADC Performance Survey 1997–2023. Available online: https://github.com/bmurmann/ADC-survey (accessed on 1 February 2024.).

- Mendonca, L.; Bhandarkar, R. Implementation of SAR ADC for Biomedical Applications—A Review. In Advances in Communication, Signal Processing, VLSI, and Embedded Systems; Kalya, S., Kulkarni, M., Shivaprakasha, K., Eds.; Springer: Singapore City, Singapore, 2020; pp. 151–159. [Google Scholar]

- Hu, J.; Li, D.; Liu, M.; Zhu, Z. A 10-kS/s 625-Hz-Bandwidth 65-dB SNDR Second-Order Noise-Shaping SAR ADC for Biomedical Sensor Applications. IEEE Sensors J. 2020, 20, 13881–13891. [Google Scholar] [CrossRef]

- Sadollahi, M.; Hamashita, K.; Sobue, K.; Temes, G.C. An 11-Bit 250-nW 10-kS/s SAR ADC With Doubled Input Range for Biomedical Applications. IEEE Trans. Circuits Syst. I Regul. Pap. 2018, 65, 61–73. [Google Scholar] [CrossRef]

- Hu, Y.; Chen, L.; Chen, H.; Wen, Y.; Zhang, H.; Wu, Z.; Li, B. A 7.6-nW 1-kS/s 10-bit SAR ADC for Biomedical Applications. In Proceedings of the 2019 IEEE Asia Pacific Conference on Circuits and Systems (APCCAS), Bangkok, Thailand, 11–14 November 2019; pp. 129–132. [Google Scholar] [CrossRef]

- Wang, S.H.; Hung, C.C. A 0.3V 10b 3MS/s SAR ADC With Comparator Calibration and Kickback Noise Reduction for Biomedical Applications. IEEE Trans. Biomed. Circuits Syst. 2020, 14, 558–569. [Google Scholar] [CrossRef] [PubMed]

- De La Fuente-Cortes, G.; Espinosa Flores-Verdad, G.; Gonzalez-Diaz, V.R.; Diaz-Mendez, A. A new CMOS comparator robust to process and temperature variations for SAR ADC converters. Analog Integr. Circuits Signal Process. 2017, 90, 301–308. [Google Scholar] [CrossRef]

- Jie, L.; Tang, X.; Liu, J.; Shen, L.; Li, S.; Sun, N.; Flynn, M.P. An Overview of Noise-Shaping SAR ADC: From Fundamentals to the Frontier. IEEE Open J. Solid-State Circuits Soc. 2021, 1, 149–161. [Google Scholar] [CrossRef]

- Kim, S.B.; Kwon, K.W. A hybrid ADC combining capacitive DAC-based multi-bit/cycle SAR ADC with flash ADC. In Proceedings of the 2016 International Conference on Electronics, Information, and Communications (ICEIC), Harbin, China, 20–22 August 2016; pp. 1–4. [Google Scholar] [CrossRef]

- Kobayashi, Y.; Matsuura, T.; Kishida, R.; Hyogo, A. Investigation of Hybrid ADC Combined with First-order Feedforward Incremental and SAR ADCs. In Proceedings of the 2019 International Symposium on Intelligent Signal Processing and Communication Systems (ISPACS), Taipei, Taiwan, 3–6 December 2019; pp. 1–2. [Google Scholar] [CrossRef]

- Anderson, T.O. Optimum Control Logic for Successive Approximation Analog-to-Digital Converters. Deep Space Netw. Prog. Rep. 1972, 13, 168–176. [Google Scholar]

- Yue, X. Determining the reliable minimum unit capacitance for the DAC capacitor array of SAR ADCs. Microelectron. J. 2013, 44, 473–478. [Google Scholar] [CrossRef]

- Qin, C.; Cai, Z. Bootstrapped Complementary Switches for High-Precision Sampling. In Proceedings of the 2023 IEEE International Symposium on Circuits and Systems (ISCAS), Jeju, Korea, 24–25 October 2023; pp. 1–5. [Google Scholar] [CrossRef]

- Eriksson, H.; Larsson-Edefors, P.; Henriksson, T.; Svensson, C. Full-custom vs. standard-cell design flow - an adder case study. In Proceedings of the ASP-DAC Asia and South Pacific Design Automation Conference, New York, NY, USA, 21–24 January 2003; pp. 507–510. [Google Scholar] [CrossRef]

- Gregorian, R. Introduction to CMOS OPAMPs and Comparators; John Wiley & Sons: Hoboken, NJ, USA, 1999. [Google Scholar]

- Chen, L.; Ma, J.; Sun, N. Capacitor mismatch calibration for SAR ADCs based on comparator metastability detection. In Proceedings of the 2014 IEEE International Symposium on Circuits and Systems (ISCAS), Melbourne, Australia, 1–5 June 2014; pp. 2357–2360. [Google Scholar] [CrossRef]

- Fateh, S.; Schönle, P.; Bettini, L.; Rovere, G.; Benini, L.; Huang, Q. A Reconfigurable 5-to-14 bit SAR ADC for Battery-Powered Medical Instrumentation. IEEE Trans. Circuits Syst. I Regul. Pap. 2015, 62, 2685–2694. [Google Scholar] [CrossRef]

- Yang, X.; Zhao, M.; Dong, Y.; Wu, X. A 14.9 μW analog front-end with capacitively-coupled instrumentation amplifier and 14-bit SAR ADC for epilepsy diagnosis system. In Proceedings of the 2016 IEEE Biomedical Circuits and Systems Conference (BioCAS), Shanghai, China, 17–19 October 2016; pp. 268–271. [Google Scholar] [CrossRef]

- Shen, Y.; Li, H.; Bindra, H.S.; Cantatore, E.; Harpe, P. A 14-Bit Oversampled SAR ADC With Mismatch Error Shaping and Analog Range Compensation. IEEE Trans. Circuits Syst. II Express Briefs 2023, 70, 1719–1723. [Google Scholar] [CrossRef]

| Specification | [7] | [8] | [9] | [10] |

|---|---|---|---|---|

| Architecture | NS | Single | Single | Single |

| SAR | Ended | Ended | Ended | |

| Technology (nm) | 180 | 180 | 180 | 90 |

| Resolution (Bits) | 7 | 11 | 10 | 10 |

| Bandwidth (MHz) | 0.000625 | – | – | – |

| Supply Voltage (V) | 1.0 | 0.75 | 1.8 | 0.3 |

| Sampling Rate (MS/s) | 0.01 | 0.01 | 0.001 | 3 |

| Core area (mm2) | 0.12 | 0.128 | 0.15 | 0.08 |

| ENoB (Bits) | 10.5 | 9.76 | 7.2 | 9.08 |

| Power consumption (μW) | 0.09 | 0.25 | 0.76 | 6.6 |

| FoM (fJ/conv-lev) | 50 | 28.8 | 51.7 | 4.065 |

| Signal | Bandwidth (Hz) | Amplitude Range |

|---|---|---|

| Electroencephalogram (EEG) | 0.01 to 150 | <1 μV to 1 mV |

| Electrooculography (EOG) | 0.01 to 50 | <10 μV to 10 mV |

| Electrocardiography (ECG) | 0.01 to 300 | <50 μV to 10 mV |

| Electromyography (EMG)-Internal | 0.01 to 15 k | <200 μV to 20 mV |

| Electromyography (EMG)-External | 10 to 8 k | <10 μV to 100 mV |

| Parameter | Expression | Value |

|---|---|---|

| Bits resolution | N | 14 |

| Voltage reference | 1.8 V | |

| Capacitance density | 100 fF | |

| 18 fF | ||

| 16 fF |

| Design | Flow Step | Time |

|---|---|---|

| Logic | Design Entry (HDL) | 2 h |

| Logic Synthesis | 2 min | |

| Post-synthesis simulation | 40 min | |

| Physical | Floor Planning | 10 min |

| Placement and routing | 2 min | |

| Post-Layout simulation | 40 min | |

| Interconnections | 1 h |

| Specification | This Work |

|---|---|

| Architecture | Fully Differential |

| Technology (nm) | 180 |

| Supply Voltage (V) | 1.8 |

| Resolution (Bits) | 14 |

| Sampling Rate (MS/s) | 2.56 |

| Core area (mm2 | 0.25 |

| SNDR (dB) | 84.66 |

| Power consumption (μW) | 310.3 |

| OSR | 16 |

| Bandwidth (MHz) | 0.08 |

| ENoB (Bits) | 14.07 |

| ( /) | |

| (dB) |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Fuente-Cortes, G.D.L.; Espinosa Flores-Verdad, G.; Díaz-Méndez, A.; Gonzalez-Diaz, V.R. A Non-Linear Successive Approximation Finite State Machine for ADCs with Robust Performance. Electronics 2024, 13, 2756. https://doi.org/10.3390/electronics13142756

Fuente-Cortes GDL, Espinosa Flores-Verdad G, Díaz-Méndez A, Gonzalez-Diaz VR. A Non-Linear Successive Approximation Finite State Machine for ADCs with Robust Performance. Electronics. 2024; 13(14):2756. https://doi.org/10.3390/electronics13142756

Chicago/Turabian StyleFuente-Cortes, Gisela De La, Guillermo Espinosa Flores-Verdad, Alejandro Díaz-Méndez, and Victor R. Gonzalez-Diaz. 2024. "A Non-Linear Successive Approximation Finite State Machine for ADCs with Robust Performance" Electronics 13, no. 14: 2756. https://doi.org/10.3390/electronics13142756