Schottky Barrier Formation Mechanism and Thermal Stability in Au-Free Cu/Metal–Silicide Contacts to GaN-Cap/AlGaN/AlN-Spacer/GaN-on-Si Heterostructure

Abstract

:1. Introduction

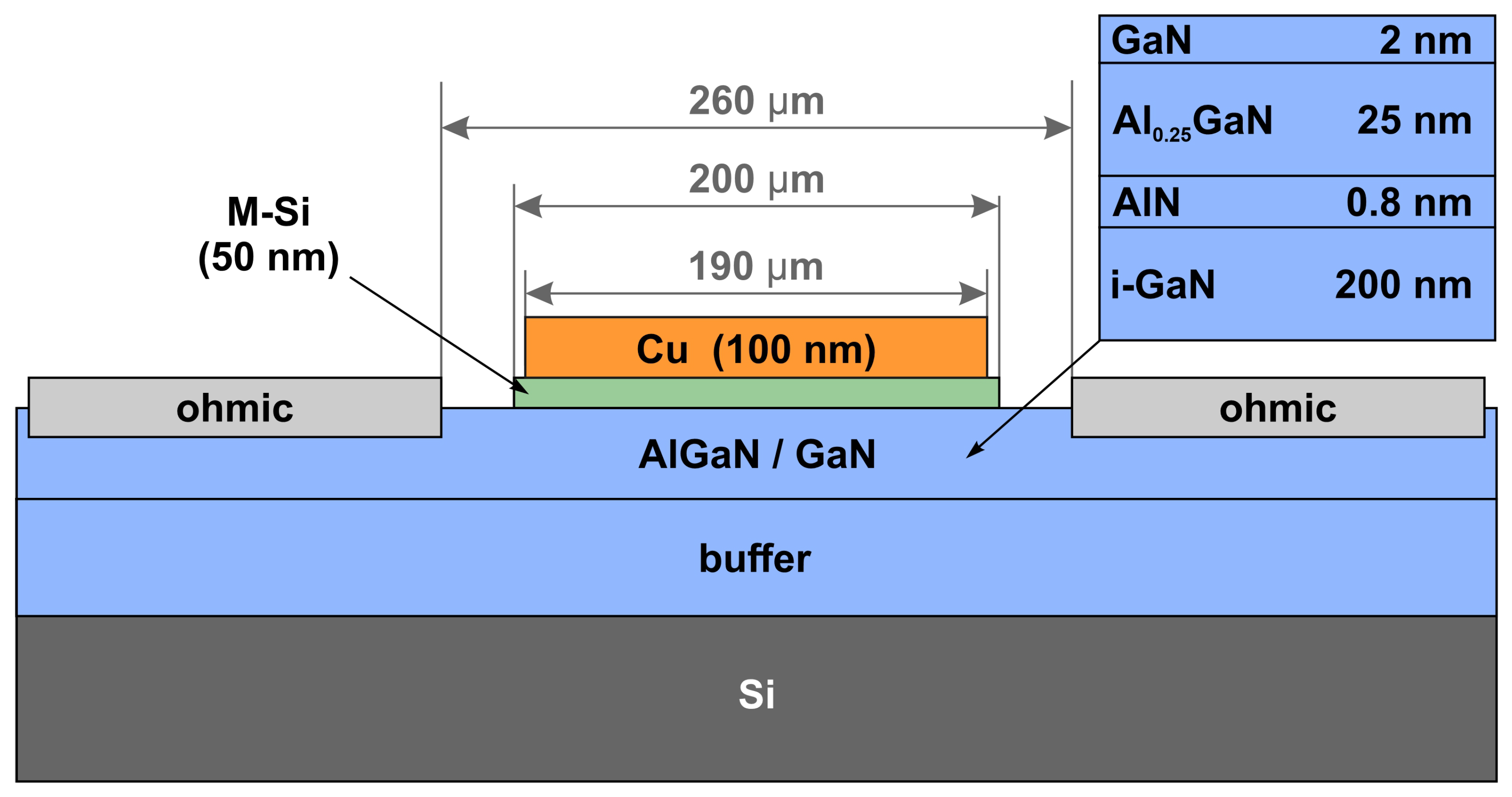

2. Materials and Methods

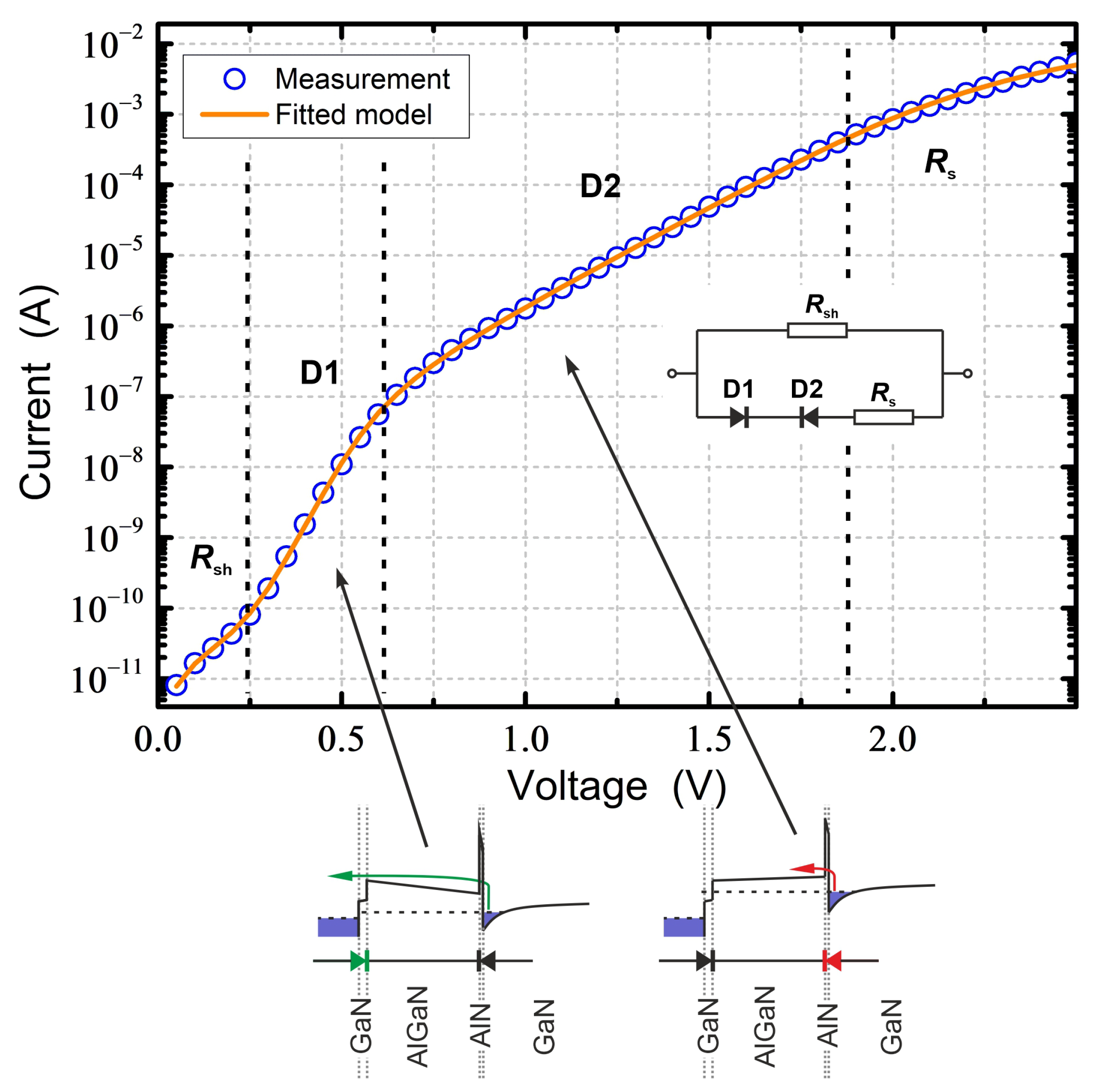

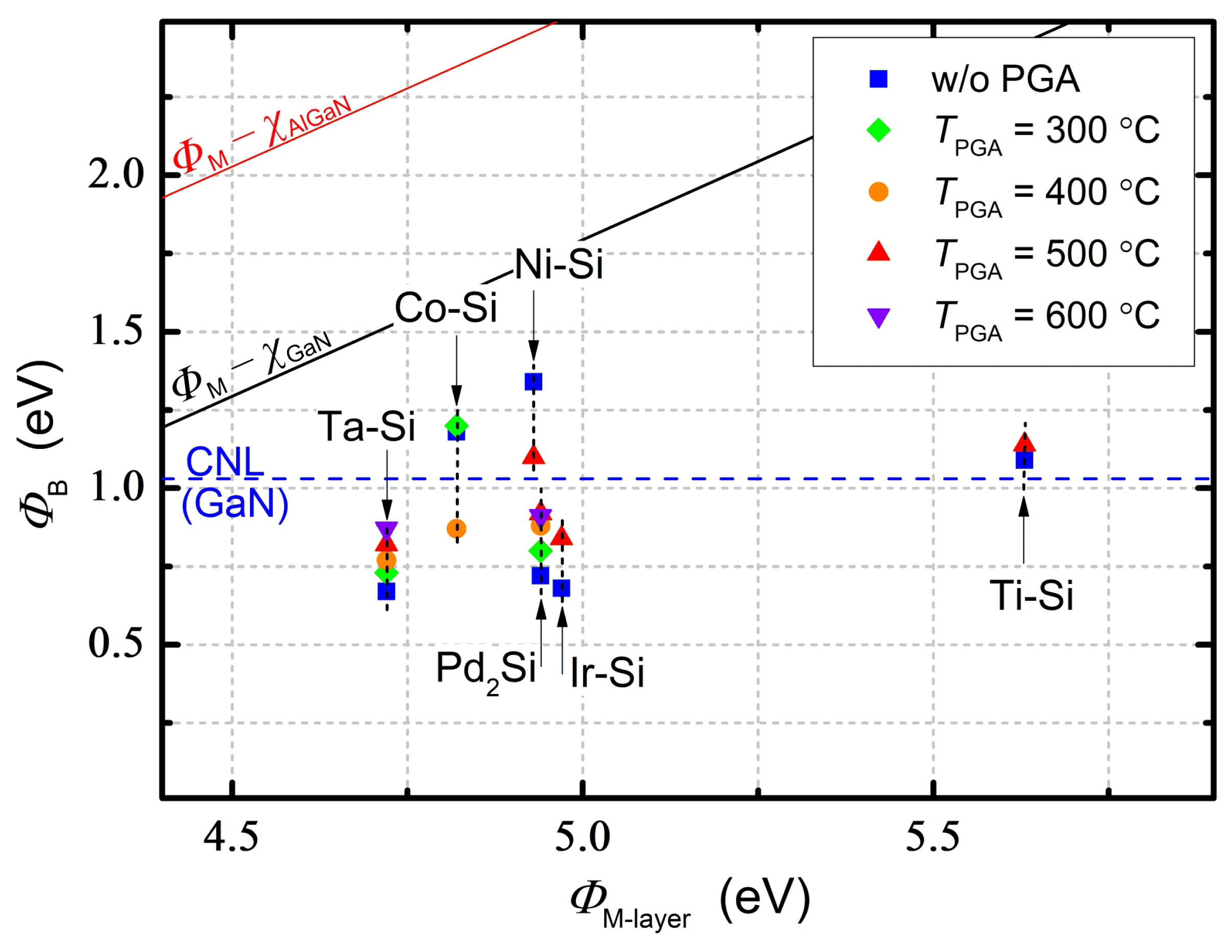

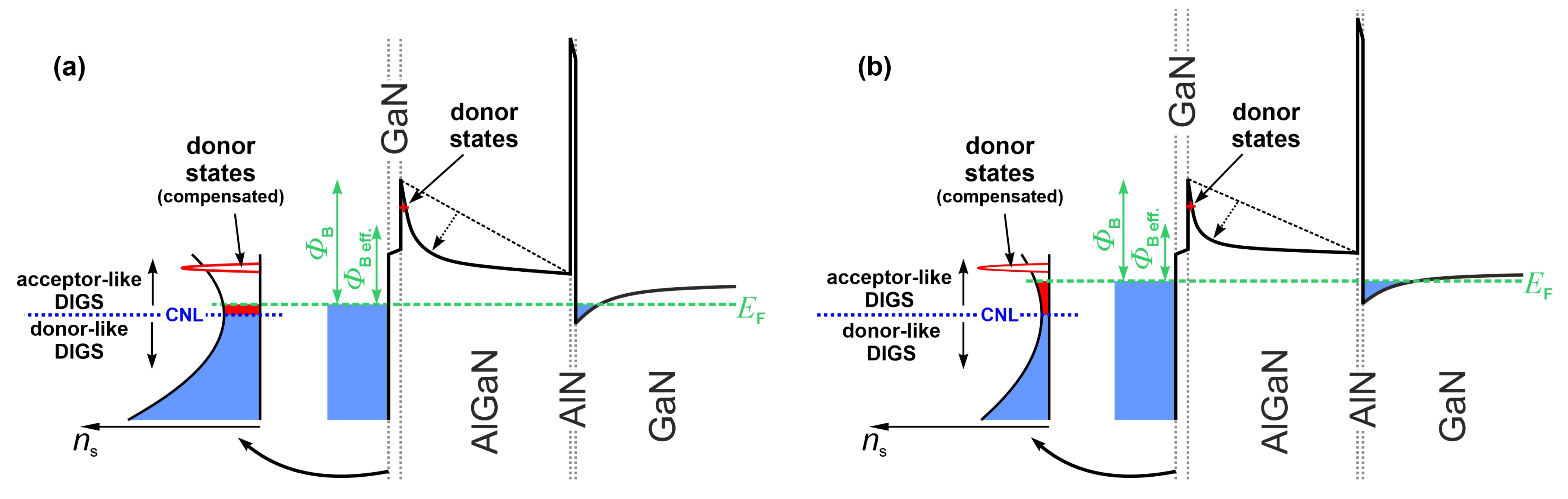

3. Results and Discussion

4. Summary and Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Buffolo, M.; Favero, D.; Marcuzzi, A.; De Santi, C.; Meneghesso, G.; Zanoni, E.; Meneghini, M. Review and Outlook on GaN and SiC Power Devices: Industrial State-of-the-Art, Applications, and Perspectives. IEEE Trans. Electron Devices 2024, 71, 1344–1355. [Google Scholar] [CrossRef]

- Chen, K.J.; Häberlen, O.; Lidow, A.; Tsai, C.L.; Ueda, T.; Uemoto, Y.; Wu, Y. GaN-on-Si Power Technology: Devices and Applications. IEEE Trans. Electron Devices 2017, 64, 779–795. [Google Scholar] [CrossRef]

- Liu, Z.; Sun, M.; Lee, H.S.; Heuken, M.; Palacios, T. AlGaN/AlN/GaN High-Electron-Mobility Transistors Fabricated with Au-Free Technology. Appl. Phys. Express 2013, 6, 096502. [Google Scholar] [CrossRef]

- Arulkumaran, S.; Ng, G.I.; Vicknesh, S.; Wang, H.; Ang, K.S.; Kumar, C.M.; Teo, K.L.; Ranjan, K. Demonstration of Submicron-Gate AlGaN/GaN High-Electron-Mobility Transistors on Silicon with Complementary Metal–Oxide–Semiconductor-Compatible Non-Gold Metal Stack. Appl. Phys. Express 2012, 6, 016501. [Google Scholar] [CrossRef]

- Tham, W.H.; Bera, L.K.; Ang, D.S.; Dolmanan, S.B.; Bhat, T.N.; Tripathy, S. AlxGa1-xN/GaN MISHEMTs with a Common Gold-Free Metal-Stack for Source/Drain/Gate. IEEE Electron Device Lett. 2015, 36, 1291–1294. [Google Scholar] [CrossRef]

- Li, Y.; Ng, G.I.; Arulkumaran, S.; Liu, Z.H.; Ranjan, K.; Xing, W.C.; Ang, K.S.; Murmu, P.P.; Kennedy, J. AlGaN/GaN high electron mobility transistors on Si with sputtered TiN gate. Phys. Status Solidi (a) 2017, 214, 1600555. [Google Scholar] [CrossRef]

- Yoon, S.; Lee, S.M.; Kim, J.; Lee, H.D.; Cha, H.Y.; Oh, J. Evaluation of titanium disilicide/copper Schottky gate for AlGaN/GaN high electron mobility transistors. Semicond. Sci. Technol. 2017, 32, 035012. [Google Scholar] [CrossRef]

- Greco, G.; Franco, S.D.; Bongiorno, C.; Grzanka, E.; Leszczynski, M.; Giannazzo, F.; Roccaforte, F. Thermal annealing effect on electrical and structural properties of Tungsten Carbide Schottky contacts on AlGaN/GaN heterostructures. Semicond. Sci. Technol. 2020, 35, 105004. [Google Scholar] [CrossRef]

- Garg, M.; Kumar, A.; Sun, H.; Liao, C.H.; Li, X.; Singh, R. Temperature dependent electrical studies on Cu/AlGaN/GaN Schottky barrier diodes with its microstructural characterization. J. Alloy. Compd. 2019, 806, 852–857. [Google Scholar] [CrossRef]

- Ao, J.P.; Kikuta, D.; Kubota, N.; Naoi, Y.; Ohno, Y. Copper gate AlGaN/GaN HEMT with low gate leakage current. IEEE Electron Device Lett. 2003, 24, 500–502. [Google Scholar] [CrossRef]

- Sun, H.F.; Alt, A.R.; Bolognesi, C.R. Submicrometer Copper T-Gate AlGaN/GaN HFETs: The Gate Metal Stack Effect. IEEE Electron Device Lett. 2007, 28, 350–353. [Google Scholar] [CrossRef]

- Esposto, M.; Lecce, V.D.; Bonaiuti, M.; Chini, A. The Influence of Interface States at the Schottky Junction on the Large Signal Behavior of Copper-Gate GaN HEMTs. J. Electron. Mater. 2013, 42, 15–20. [Google Scholar] [CrossRef]

- Park, J.; Lee, K.; Cha, H.Y.; Seo, K. Thermal instability of copper gate AlGaN/GaN HEMT on Si substrate. Electron. Lett. 2010, 46, 1011–1012. [Google Scholar] [CrossRef]

- Wzorek, M.; Ekielski, M.; Tarenko, J.; Borysiewicz, M.A.; Brzozowski, E.; Taube, A. Thermal Stability of Cu/Pd2Si/, Cu/, and Au/Ni/ Schottky Contacts to AlGaN/GaN Heterostructures. IEEE Trans. Electron Devices 2024, 71, 490–495. [Google Scholar] [CrossRef]

- Tallarico, A.N.; Stoffels, S.; Magnone, P.; Hu, J.; Lenci, S.; Marcon, D.; Sangiorgi, E.; Fiegna, C.; Decoutere, S. Reliability of Au-Free AlGaN/GaN-on-Silicon Schottky Barrier Diodes Under ON-State Stress. IEEE Trans. Electron Devices 2016, 63, 723–730. [Google Scholar] [CrossRef]

- Hu, J.; Stoffels, S.; Lenci, S.; Bakeroot, B.; De Jaeger, B.; Van Hove, M.; Ronchi, N.; Venegas, R.; Liang, H.; Zhao, M.; et al. Performance Optimization of Au-Free Lateral AlGaN/GaN Schottky Barrier Diode with Gated Edge Termination on 200-mm Silicon Substrate. IEEE Trans. Electron Devices 2016, 63, 997–1004. [Google Scholar] [CrossRef]

- Acurio, E.; Trojman, L.; Crupi, F.; Moposita, T.; De Jaeger, B.; Decoutere, S. Reliability Assessment of AlGaN/GaN Schottky Barrier Diodes Under ON-State Stress. IEEE Trans. Device Mater. Reliab. 2020, 20, 167–171. [Google Scholar] [CrossRef]

- Sun, H.; Liu, M.; Liu, P.; Lin, X.; Chen, J.; Wang, M.; Chen, D. Optimization of Au-Free Ohmic Contact Based on the Gate-First Double-Metal AlGaN/GaN MIS-HEMTs and SBDs Process. IEEE Trans. Electron Devices 2018, 65, 622–628. [Google Scholar] [CrossRef]

- Chen, Y.C.; Tang, S.W.; Lin, P.H.; Chen, Z.C.; Lu, M.H.; Kao, K.H.; Wu, T.L. Silicon Nitride-induced Threshold Voltage Shift in p-GaN HEMTs with Au-free Gate-first Process. In Proceedings of the 2020 IEEE International Symposium on the Physical and Failure Analysis of Integrated Circuits (IPFA), Singapore, 20–23 July 2020; pp. 1–5. [Google Scholar] [CrossRef]

- Lenci, S.; De Jaeger, B.; Carbonell, L.; Hu, J.; Mannaert, G.; Wellekens, D.; You, S.; Bakeroot, B.; Decoutere, S. Au-Free AlGaN/GaN Power Diode on 8-in Si Substrate with Gated Edge Termination. IEEE Electron Device Lett. 2013, 34, 1035–1037. [Google Scholar] [CrossRef]

- Hu, J.; Stoffels, S.; Lenci, S.; Wu, T.L.; Ronchi, N.; You, S.; Bakeroot, B.; Groeseneken, G.; Decoutere, S. Investigation of constant voltage off-state stress on Au-free AlGaN/GaN Schottky barrier diodes. Jpn. J. Appl. Phys. 2015, 54, 04DF07. [Google Scholar] [CrossRef]

- Hu, J.; Stoffels, S.; Lenci, S.; Bakeroot, B.; Venegas, R.; Groeseneken, G.; Decoutere, S. Current transient spectroscopy for trapping analysis on Au-free AlGaN/GaN Schottky barrier diode. Appl. Phys. Lett. 2015, 106, 083502. [Google Scholar] [CrossRef]

- Posthuma, N.E.; You, S.; Stoffels, S.; Wellekens, D.; Liang, H.; Zhao, M.; De Jaeger, B.; Geens, K.; Ronchi, N.; Decoutere, S.; et al. An industry-ready 200 mm p-GaN E-mode GaN-on-Si power technology. In Proceedings of the 2018 IEEE 30th International Symposium on Power Semiconductor Devices and ICs (ISPSD), Chicago, IL, USA, 13–17 May 2018; pp. 284–287. [Google Scholar] [CrossRef]

- Ao, J.P.; Naoi, Y.; Ohno, Y. Thermally stable TiN Schottky contact on AlGaN/GaN heterostructure. Vacuum 2013, 87, 150–154. [Google Scholar] [CrossRef]

- Wu, Y.; Zhang, W.; Zhang, J.; Zhao, S.; Luo, J.; Tan, X.; Mao, W.; Zhang, C.; Zhang, Y.; Cheng, K.; et al. Au-Free Al0.4Ga0.6N/Al0.1Ga0.9N HEMTs on Silicon Substrate with High Reverse Blocking Voltage of 2 kV. IEEE Trans. Electron Devices 2021, 68, 4543–4549. [Google Scholar] [CrossRef]

- Niranjan, S.; Rao, A.; Muralidharan, R.; Sen, P.; Nath, D.N. Performance Comparison of Au-Based and Au-Free AlGaN/GaN HEMT on Silicon. IEEE Trans. Electron Devices 2022, 69, 1014–1019. [Google Scholar] [CrossRef]

- Fontserè, A.; Pérez-Tomás, A.; Banu, V.; Godignon, P.; Millán, J.; De Vleeschouwer, H.; Parsey, J.M.; Moens, P. A HfO2 based 800 V/300 °C Au-free AlGaN/GaN-on-Si HEMT technology. In Proceedings of the 2012 24th International Symposium on Power Semiconductor Devices and ICs, Bruges, Belgium, 3–7 June 2012; pp. 37–40. [Google Scholar] [CrossRef]

- Hsieh, T.E.; Lin, Y.C.; Chu, C.M.; Chuang, Y.L.; Huang, Y.X.; Shi, W.C.; Dee, C.F.; Majlis, B.Y.; Lee, W.I.; Chang, E.Y. Au-Free GaN High-Electron-Mobility Transistor with Ti/Al/W Ohmic and WNX Schottky Metal Structures for High-Power Applications. J. Electron. Mater. 2016, 45, 3285–3289. [Google Scholar] [CrossRef]

- Wzorek, M.; Ekielski, M.; Brzozowski, E.; Taube, A. Electrical properties of Cu/Pd2Si Schottky contacts to AlGaN/GaN-on-Si HEMT heterostructures. Mater. Sci. Semicond. Process. 2023, 153, 107157. [Google Scholar] [CrossRef]

- Kim, J.; Ren, F.; Baca, A.G.; Pearton, S.J. Thermal stability of WSix and W Schottky contacts on n-GaN. Appl. Phys. Lett. 2003, 82, 3263–3265. [Google Scholar] [CrossRef]

- Bucher, E.; Schulz, S.; Lux-Steiner, M.C.; Munz, P.; Gubler, U.; Greuter, F. Work function and barrier heights of transition metal silicides. Appl. Phys. A 1986, 40, 71–77. [Google Scholar] [CrossRef]

- Piskorski, K.; Wzorek, M.; Ekielski, M.; Dobrzański, L.; Gaca, J.; Malinowska, A.; Michałowski, P.; Borysiewicz, M. Photoelectric, optical and microstructural characterization of thin palladium silicide (Pd2Si) layers fabricated by magnetron sputtering from a stoichiometric target. Mater. Sci. Eng. B 2022, 283, 115831. [Google Scholar] [CrossRef]

- Taube, A.; Borysiewicz, M.A.; Sadowski, O.; Wójcicka, A.; Tarenko, J.; Piskorski, K.; Wzorek, M. Investigation of amorphous (Ir,Ru)-Si and (Ir,Ru)-Si-O Schottky contacts to (001) β-Ga2O3. Mater. Sci. Semicond. Process. 2023, 154, 107218. [Google Scholar] [CrossRef]

- Tung, R.T. The physics and chemistry of the Schottky barrier height. Appl. Phys. Rev. 2014, 1, 011304. [Google Scholar] [CrossRef]

- Chen, C.H.; Baier, S.; Arch, D.; Shur, M. A new and simple model for GaAs heterojunction FET gate characteristics. IEEE Trans. Electron Devices 1988, 35, 570–577. [Google Scholar] [CrossRef]

- Lv, Y.; Lin, Z.; Corrigan, T.D.; Zhao, J.; Cao, Z.; Meng, L.; Luan, C.; Wang, Z.; Chen, H. Extraction of AlGaN/GaN heterostructure Schottky diode barrier heights from forward current-voltage characteristics. J. Appl. Phys. 2011, 109, 074512. [Google Scholar] [CrossRef]

- Lü, Y.-J.; Feng, Z.-H.; Gu, G.-D.; Dun, S.-B.; Yin, J.-Y.; Han, T.-T.; Sheng, B.-C.; Cai, S.-J.; Liu, B.; Lin, Z.-J. Directly extracting both threshold voltage and series resistance from the conductance—Voltage curve of an AlGaN/GaN Schottky diode. Chin. Phys. B 2013, 22, 077102. [Google Scholar] [CrossRef]

- Chen, C.-h.; Wang, D.; Hou, D.; Yang, Y.; Yau, W.; Sadler, R.; Sutton, W.; Shim, J.; Wang, S. The Impact of AlN Spacer on Forward Gate Current and Stress-Induced Leakage Current (SILC) of GaN HEMT. In Proceedings of the 2016 IEEE Compound Semiconductor Integrated Circuit Symposium (CSICS), Austin, TX, USA, 23–26 October 2016; pp. 1–4. [Google Scholar] [CrossRef]

- Greco, G.; Giannazzo, F.; Roccaforte, F. Temperature dependent forward current-voltage characteristics of Ni/Au Schottky contacts on AlGaN/GaN heterostructures described by a two diodes model. J. Appl. Phys. 2017, 121, 045701. [Google Scholar] [CrossRef]

- Kim, H.; Schuette, M.; Jung, H.; Song, J.; Lee, J.; Lu, W.; Mabon, J.C. Passivation effects in Ni/AlGaN/GaN Schottky diodes by annealing. Appl. Phys. Lett. 2006, 89, 053516. [Google Scholar] [CrossRef]

- Persano, A.; Pio, I.; Tasco, V.; Cuscunà, M.; Passaseo, A.; Cola, A. Electrical properties of planar AlGaN/GaN Schottky diodes: Role of 2DEG and analysis of non-idealities. J. Appl. Phys. 2017, 121, 135701. [Google Scholar] [CrossRef]

- Jin Ha, W.; Chhajed, S.; Jae Oh, S.; Hwang, S.; Kyu Kim, J.; Lee, J.H.; Kim, K.S. Analysis of the reverse leakage current in AlGaN/GaN Schottky barrier diodes treated with fluorine plasma. Appl. Phys. Lett. 2012, 100, 132104. [Google Scholar] [CrossRef]

- Grabowski, S.P.; Schneider, M.; Nienhaus, H.; Mönch, W.; Dimitrov, R.; Ambacher, O.; Stutzmann, M. Electron affinity of AlxGa1-xN(0001) surfaces. Appl. Phys. Lett. 2001, 78, 2503–2505. [Google Scholar] [CrossRef]

- Hasegawa, H.; Inagaki, T.; Ootomo, S.; Hashizume, T. Mechanisms of current collapse and gate leakage currents in AlGaN/GaN heterostructure field effect transistors. J. Vac. Sci. Technol. B Microelectron. Nanometer Struct. Process. Meas. Phenom. 2003, 21, 1844–1855. [Google Scholar] [CrossRef]

- Yan, D.; Lu, H.; Cao, D.; Chen, D.; Zhang, R.; Zheng, Y. On the reverse gate leakage current of AlGaN/GaN high electron mobility transistors. Appl. Phys. Lett. 2010, 97, 153503. [Google Scholar] [CrossRef]

- Turuvekere, S.; Karumuri, N.; Rahman, A.A.; Bhattacharya, A.; DasGupta, A.; DasGupta, N. Gate Leakage Mechanisms in AlGaN/GaN and AlInN/GaN HEMTs: Comparison and Modeling. IEEE Trans. Electron Devices 2013, 60, 3157–3165. [Google Scholar] [CrossRef]

- Bae, S.H.; Lu, K.; Han, Y.; Kim, S.; Qiao, K.; Choi, C.; Nie, Y.; Kim, H.; Kum, H.S.; Chen, P.; et al. Graphene-assisted spontaneous relaxation towards dislocation-free heteroepitaxy. Nat. Nanotechnol. 2020, 15, 272–276. [Google Scholar] [CrossRef]

- Meng, Y.; Feng, J.; Han, S.; Xu, Z.; Mao, W.; Zhang, T.; Kim, J.S.; Roh, I.; Zhao, Y.; Kim, D.H.; et al. Photonic van der Waals integration from 2D materials to 3D nanomembranes. Nat. Rev. Mater. 2023, 8, 498–517. [Google Scholar] [CrossRef]

- Besendörfer, S.; Meissner, E.; Medjdoub, F.; Derluyn, J.; Friedrich, J.; Erlbacher, T. The impact of dislocations on AlGaN/GaN Schottky diodes and on gate failure of high electron mobility transistors. Sci. Rep. 2020, 10, 17252. [Google Scholar] [CrossRef]

- Chen, Y.; Haller, C.; Liu, W.; Karpov, S.Y.; Carlin, J.F.; Grandjean, N. GaN buffer growth temperature and efficiency of InGaN/GaN quantum wells: The critical role of nitrogen vacancies at the GaN surface. Appl. Phys. Lett. 2021, 118, 111102. [Google Scholar] [CrossRef]

- Lin, Y.J.; Ker, Q.; Ho, C.Y.; Chang, H.C.; Chien, F.T. Nitrogen-vacancy-related defects and Fermi level pinning in n-GaN Schottky diodes. J. Appl. Phys. 2003, 94, 1819–1822. [Google Scholar] [CrossRef]

- Hashizume, T.; Nakasaki, R. Discrete surface state related to nitrogen-vacancy defect on plasma-treated GaN surfaces. Appl. Phys. Lett. 2002, 80, 4564–4566. [Google Scholar] [CrossRef]

- Look, D.C.; Farlow, G.C.; Drevinsky, P.J.; Bliss, D.F.; Sizelove, J.R. On the nitrogen vacancy in GaN. Appl. Phys. Lett. 2003, 83, 3525–3527. [Google Scholar] [CrossRef]

- Schwarz, C.; Yadav, A.; Shatkhin, M.; Flitsiyan, E.; Chernyak, L.; Kasiyan, V.; Liu, L.; Xi, Y.Y.; Ren, F.; Pearton, S.J.; et al. Gamma irradiation impact on electronic carrier transport in AlGaN/GaN high electron mobility transistors. Appl. Phys. Lett. 2013, 102, 062102. [Google Scholar] [CrossRef]

- Reddy, P.; Bryan, I.; Bryan, Z.; Tweedie, J.; Washiyama, S.; Kirste, R.; Mita, S.; Collazo, R.; Sitar, Z. Charge neutrality levels, barrier heights, and band offsets at polar AlGaN. Appl. Phys. Lett. 2015, 107, 091603. [Google Scholar] [CrossRef]

- Hasegawa, H.; Oyama, S. Mechanism of anomalous current transport in n-type GaN Schottky contacts. J. Vac. Sci. Technol. B Microelectron. Nanometer Struct. Process. Meas. Phenom. 2002, 20, 1647–1655. [Google Scholar] [CrossRef]

- Mahne, N.; Čekada, M.; Panjan, M. Energy Distribution of Sputtered Atoms Explored by SRIM Simulations. Coatings 2023, 13, 1448. [Google Scholar] [CrossRef]

| M–Si | M-layer (eV) (This Work, [32,33]) | M-bulk (eV) from Ref. [31] |

|---|---|---|

| Ta–Si | 4.72 | 4.71 (TaSi2) |

| Co–Si | 4.82 | 4.77 (CoSi2) |

| Ni–Si | 4.93 | 4.96 (Ni2Si) |

| Pd2Si | 4.94 [32] | 5.0 (Pd2Si) |

| Ir–Si | 4.97 [33] | 5.08 (IrSi) |

| Ti–Si | 5.63 | 4.53 (TiSi2) |

| Anode Stack | IS (A) | B (eV) | n | IS2 (A) | 2(0) (eV) | n2 | Ir(−10 V) (A/cm2) |

|---|---|---|---|---|---|---|---|

| Cu/Ta–Si/ | 9.3 × 10−12 | 0.82 | 1.89 | 1.2 × 10−7 | 0.57 | 6.66 | 9.1 × 10−2 |

| Cu/Co–Si/ | 5.9 × 10−18 | 1.18 | 1.23 | 1.1 × 10−7 | 0.57 | 3.04 | 6.6 × 10−3 |

| Cu/Ni–Si/ | 1.0 × 10−20 | 1.34 | 1.30 | 3.4 × 10−7 | 0.54 | 3.60 | 8.0 × 10−6 |

| Cu/Pd2Si/ | 1.4 × 10−13 | 0.92 | 1.59 | 1.6 × 10−7 | 0.56 | 4.65 | 2.7 × 10-3 |

| Cu/Ir–Si/ | 3.6 × 10−12 | 0.84 | 1.43 | 8.8 × 10−7 | 0.52 | 3.91 | 3.0 × 10−2 |

| Cu/Ti–Si/ | 2.5 × 10−17 | 1.14 | 1.67 | 8.9 × 10−8 | 0.58 | 2.76 | 4.2 × 10−5 |

| Cu/Pt–Si/ | 6.3 × 10−12 | 0.83 | 1.71 | 9.0 × 10−7 | 0.52 | 4.54 | 3.9 × 10−3 |

| Au/Ni/ | 3.0 × 10−13 | 0.90 | 1.56 | 2.5 × 10−7 | 0.55 | 5.01 | 4.0 × 10−4 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wzorek, M.; Ekielski, M.; Piskorski, K.; Tarenko, J.; Borysiewicz, M.A.; Brzozowski, E.; Taube, A. Schottky Barrier Formation Mechanism and Thermal Stability in Au-Free Cu/Metal–Silicide Contacts to GaN-Cap/AlGaN/AlN-Spacer/GaN-on-Si Heterostructure. Electronics 2024, 13, 3429. https://doi.org/10.3390/electronics13173429

Wzorek M, Ekielski M, Piskorski K, Tarenko J, Borysiewicz MA, Brzozowski E, Taube A. Schottky Barrier Formation Mechanism and Thermal Stability in Au-Free Cu/Metal–Silicide Contacts to GaN-Cap/AlGaN/AlN-Spacer/GaN-on-Si Heterostructure. Electronics. 2024; 13(17):3429. https://doi.org/10.3390/electronics13173429

Chicago/Turabian StyleWzorek, Marek, Marek Ekielski, Krzysztof Piskorski, Jarosław Tarenko, Michał A. Borysiewicz, Ernest Brzozowski, and Andrzej Taube. 2024. "Schottky Barrier Formation Mechanism and Thermal Stability in Au-Free Cu/Metal–Silicide Contacts to GaN-Cap/AlGaN/AlN-Spacer/GaN-on-Si Heterostructure" Electronics 13, no. 17: 3429. https://doi.org/10.3390/electronics13173429