Dynamic Current-Limitation Strategy of Grid-Forming Inverters Based on SR Latches

Abstract

:1. Introduction

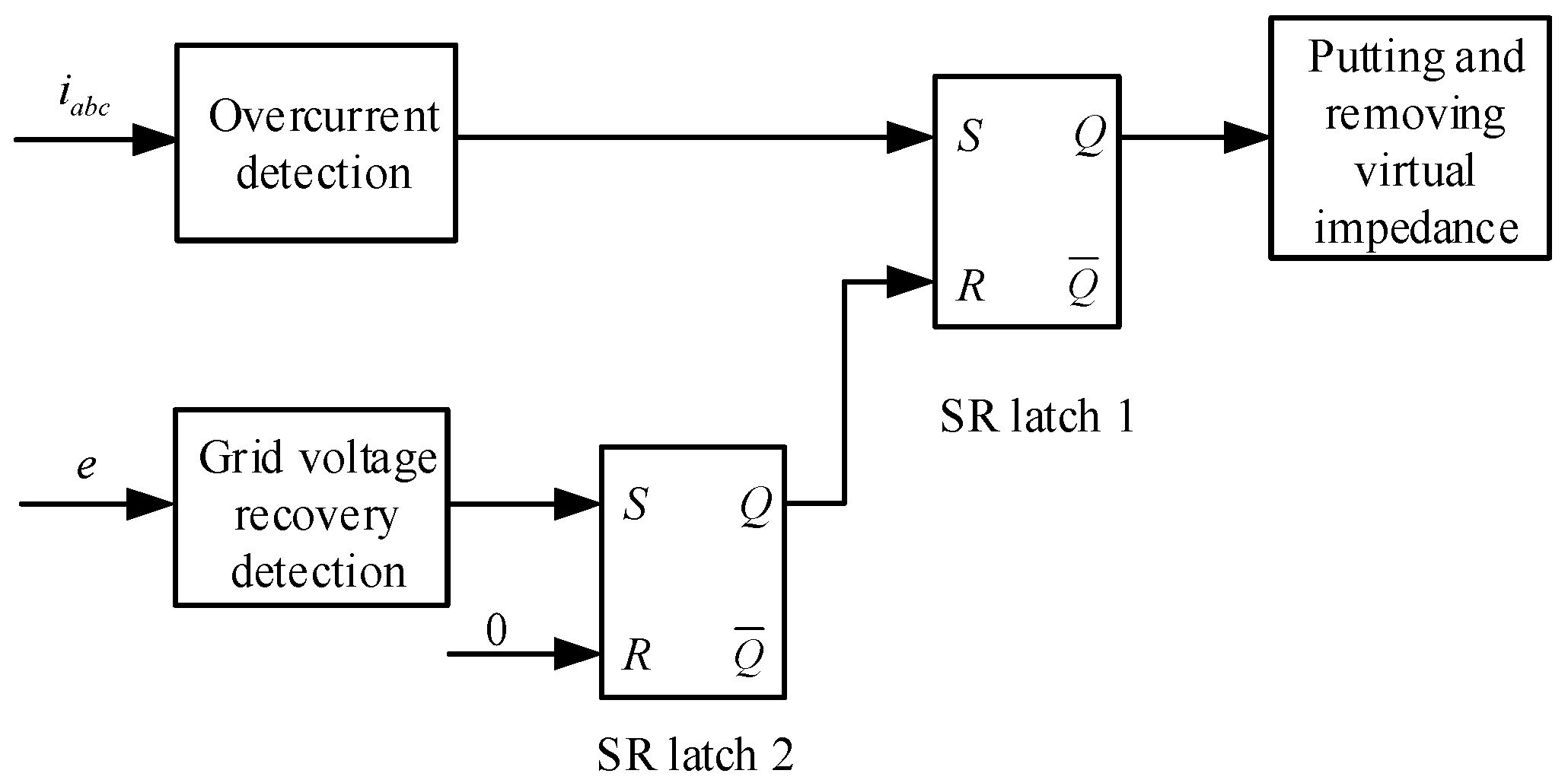

- The proposed dynamic current-limitation strategy based on SR latch logic not only suppresses transient overcurrents during grid-voltage drops but also effectively addresses the issue of irregular toggling of virtual impedance. Furthermore, it enables rapid power recovery after fault clearance.

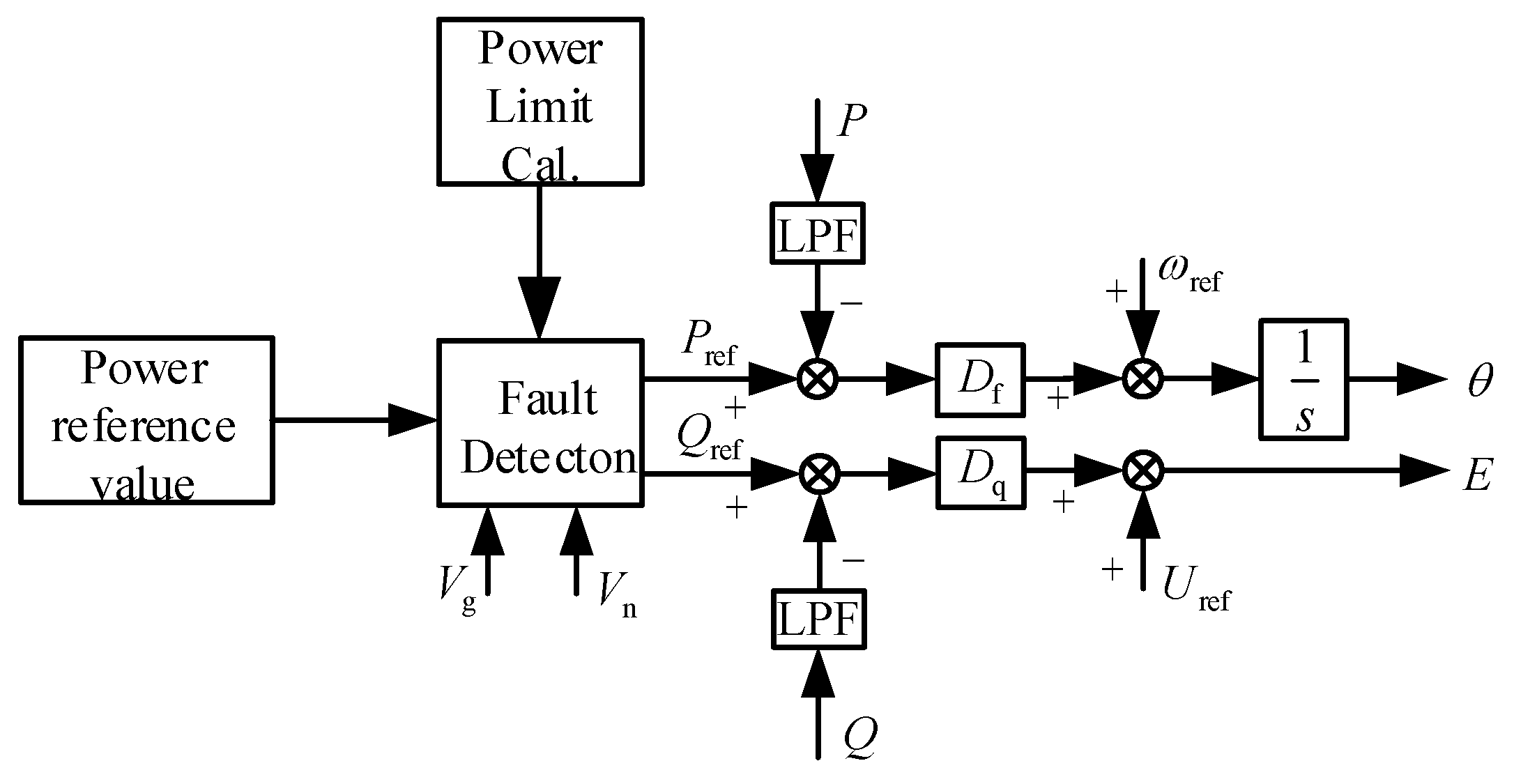

- The virtual-impedance method with power reference regulation based on grid codes is proposed for enhancing transient synchronization stability, and transient synchronization instability is effectively avoided under grid fault. The inverter reaches a new operating point quickly after the grid fault, and the dynamic performance is improved effectively.

- The proposed method is similar to the hardware SR latch, which has high speed and is not affected by time-triggered interruptions. Therefore, both the real-time triggering of SR hardware and the flexibility of digital controllers are taken into account, and the inverter control and fast overcurrent protection can be realized by digital control.

2. Mathematical Model of Grid-Forming Inverters

2.1. System Description

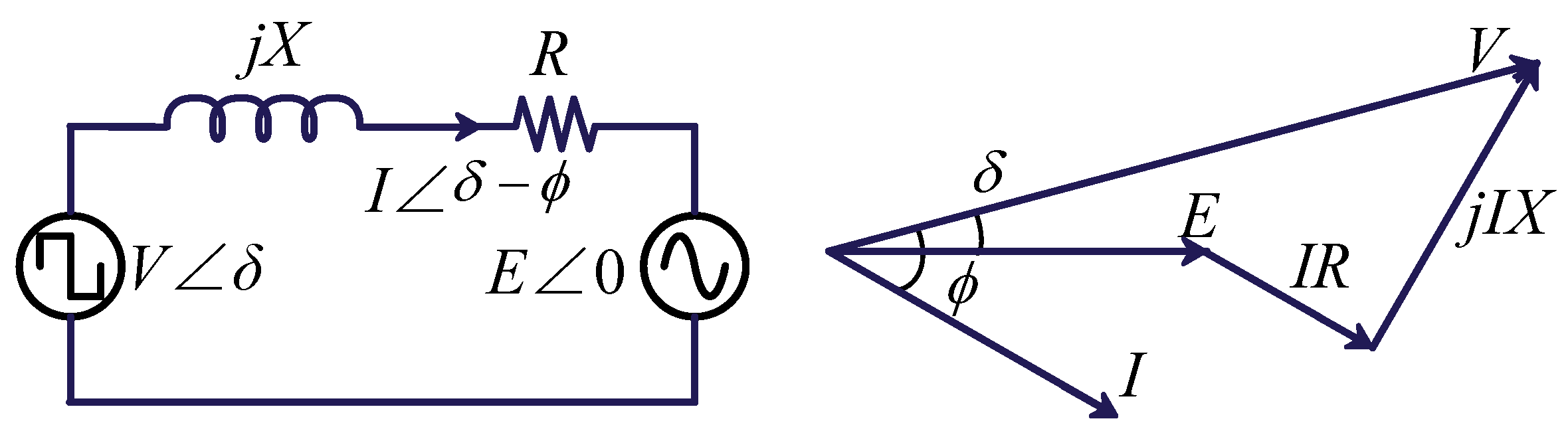

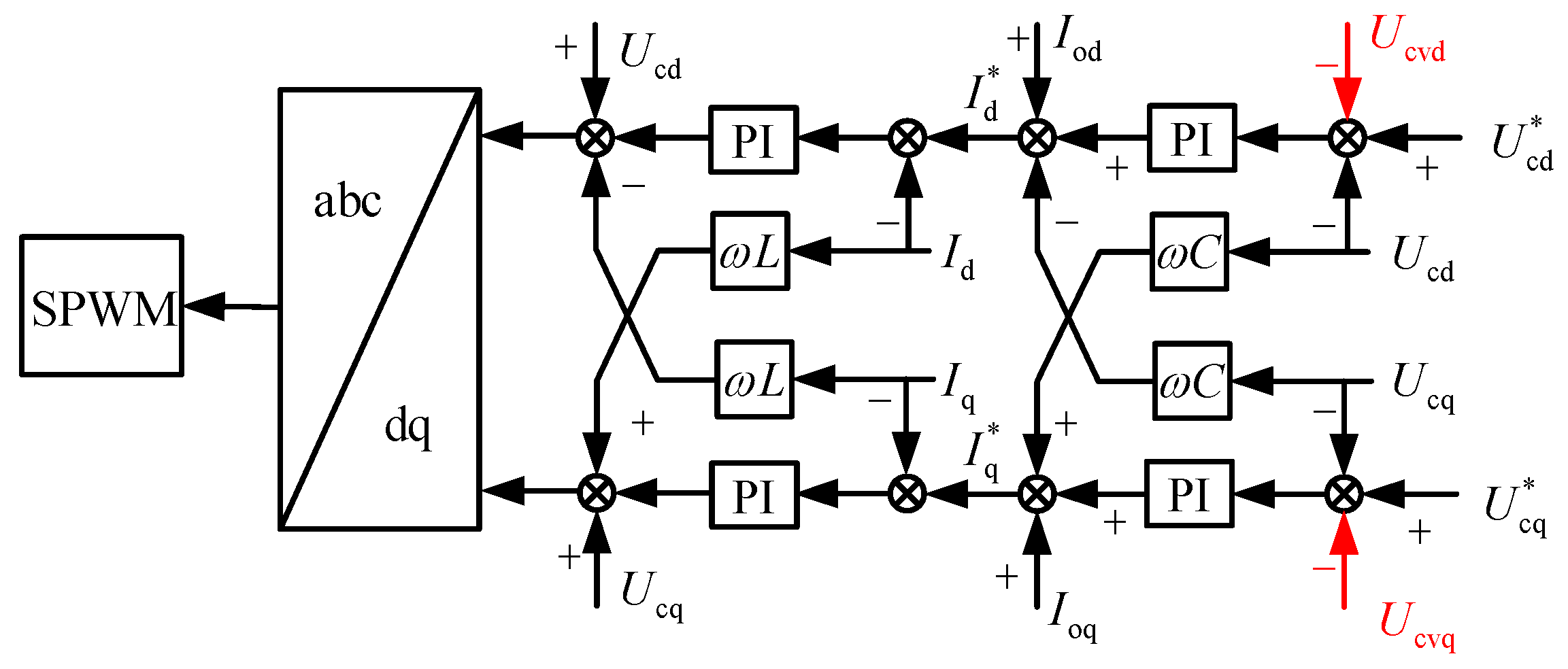

2.2. Power Control

3. GFM Inverter Operation Characteristics under Grid Faults

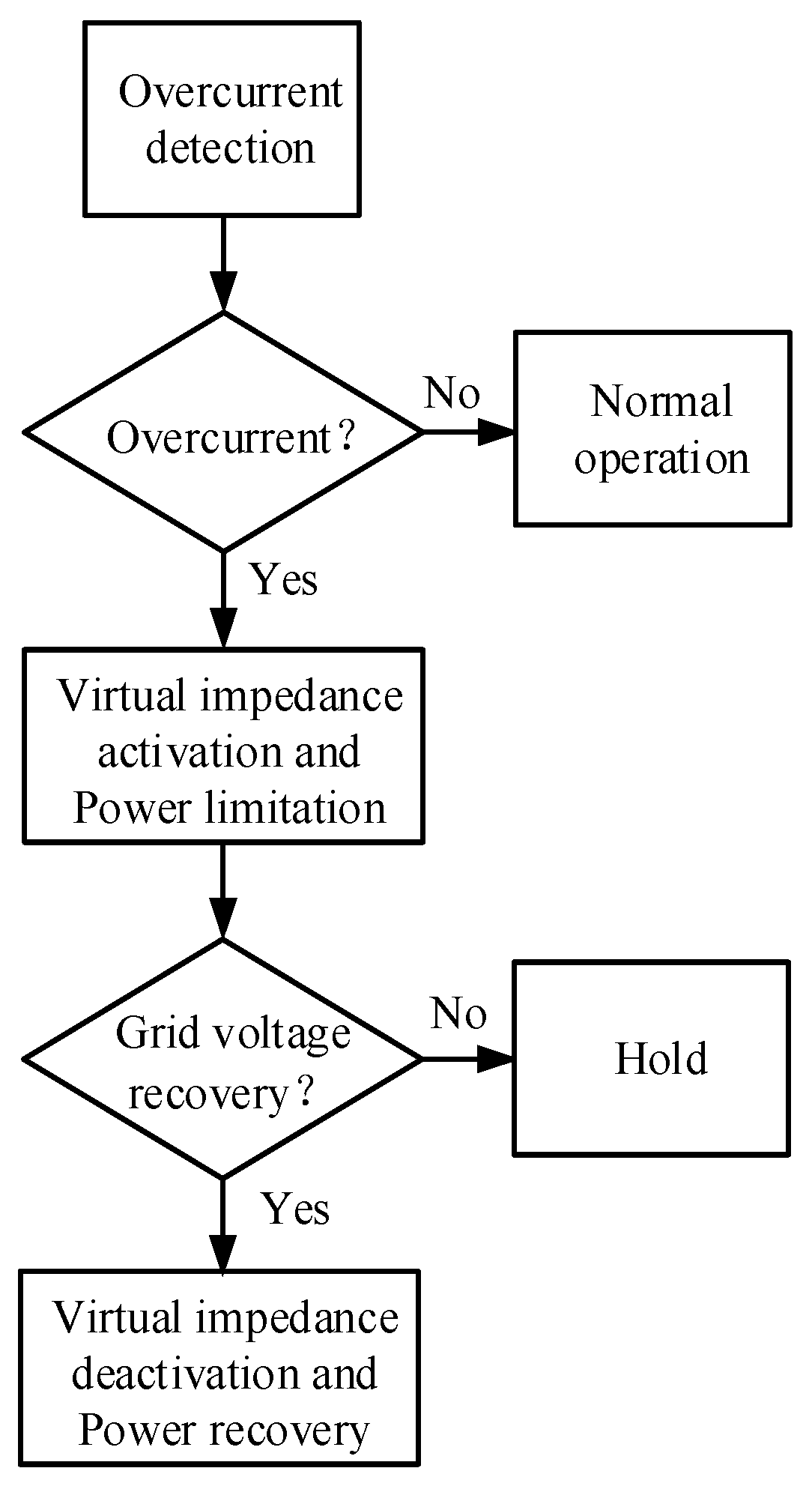

4. Dynamic Current-Limitation Strategy with Virtual Impedance and Power Limitation

5. Simulation and Experiment Verification

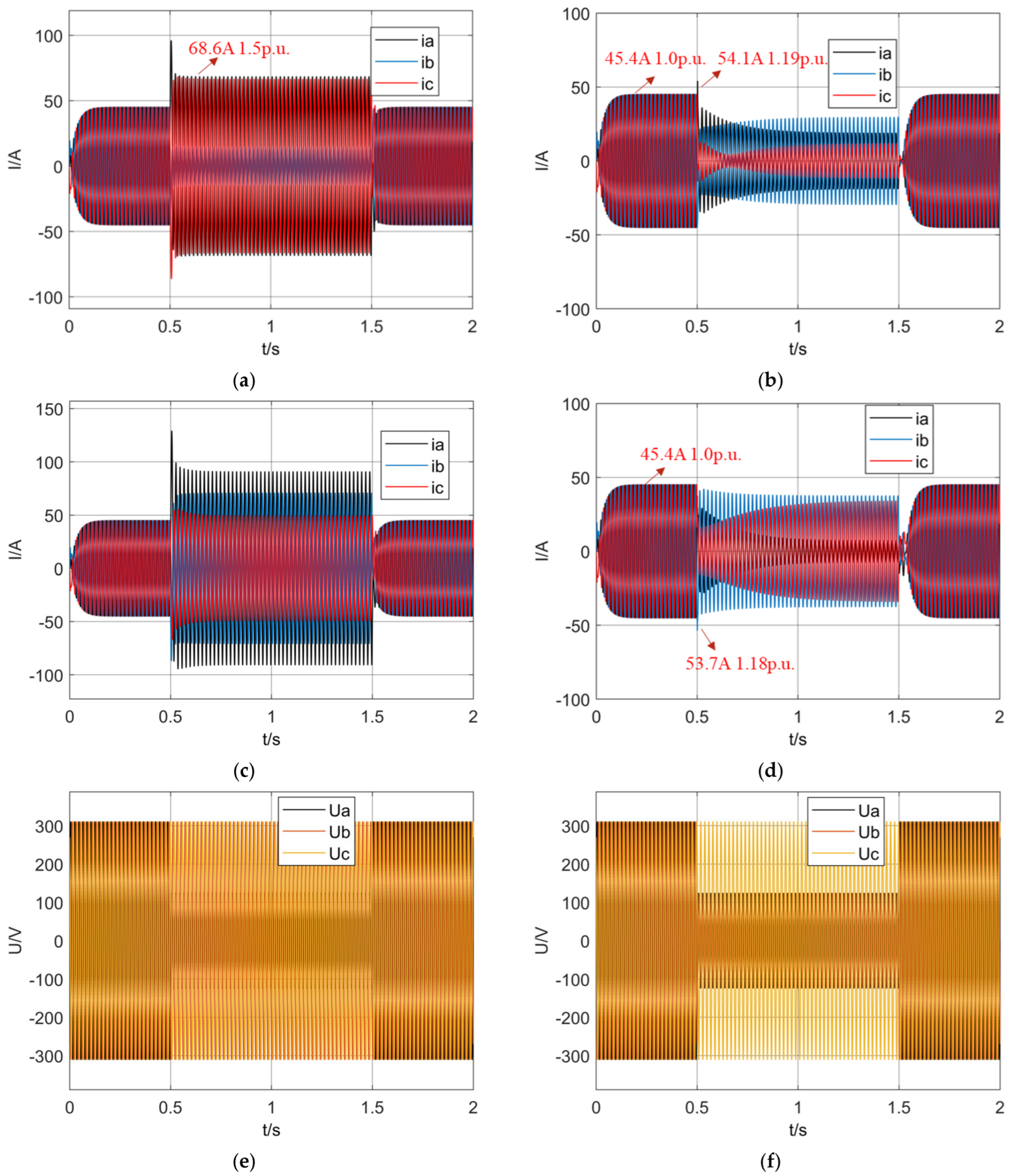

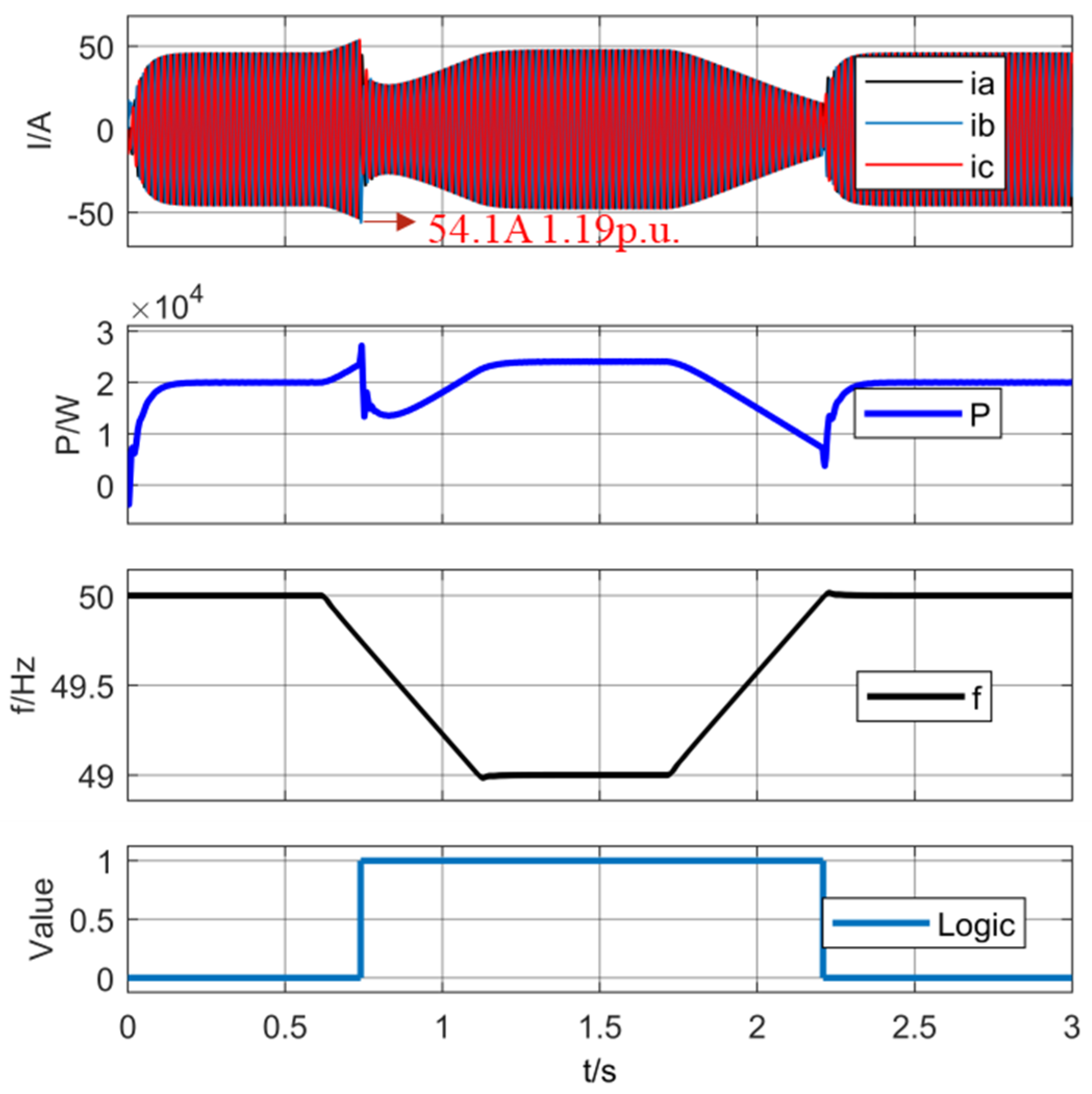

5.1. Simulation Verification

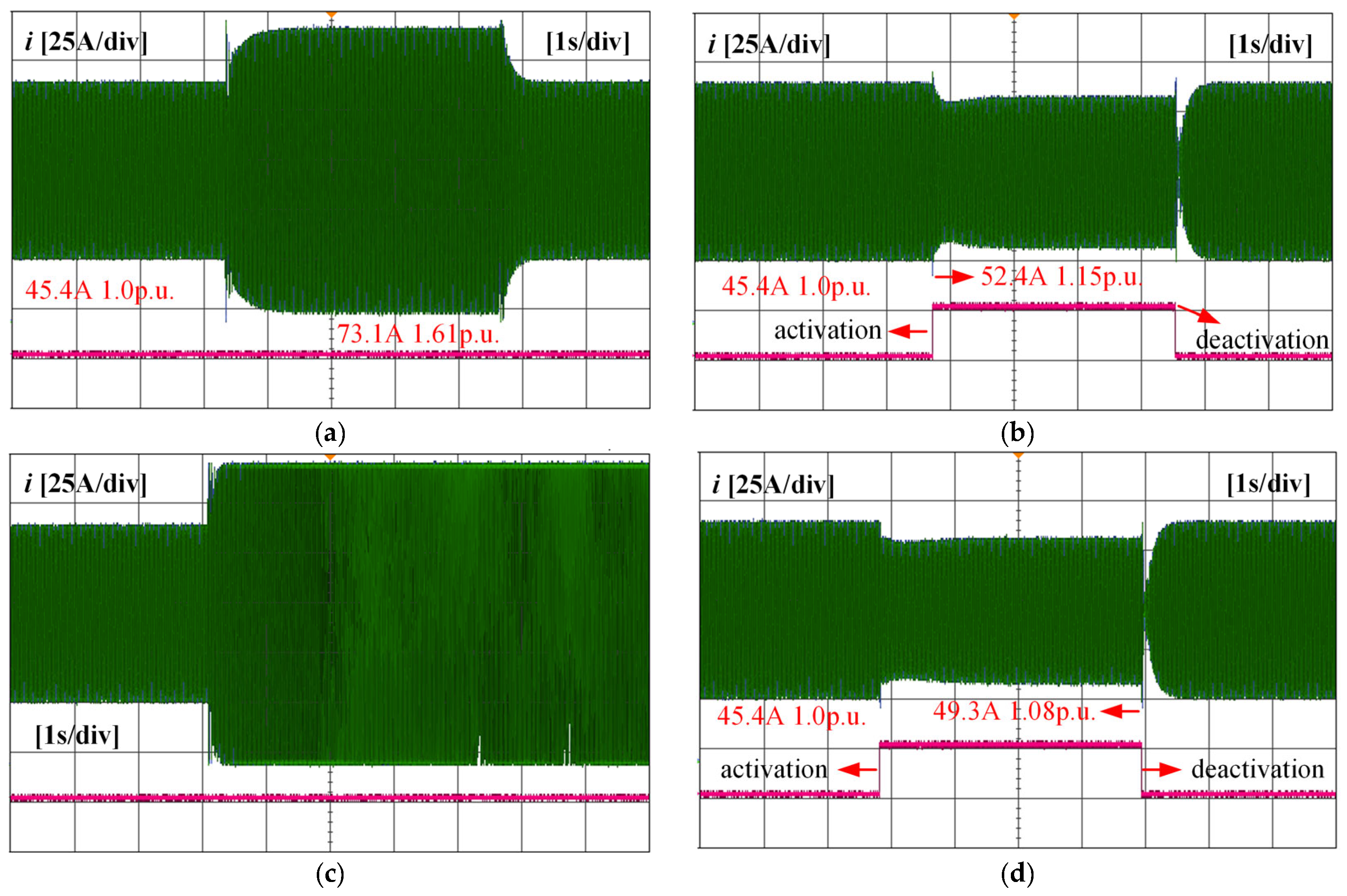

5.2. Experiment Verification

6. Conclusions

- SR latch-based virtual impedance control scheme can retain current-limitation ability during grid fault. In addition, compared with other current-limitation schemes, the proposed current-limitation method can not only avoid the saturation of the voltage loop, but also avoid the repeated switching of virtual impedance.

- Virtual impedance control with a power modification can effectively achieve fault current limitation without synchronization instability problems during grid fault.

- The event-triggered control logic is applied in a digital controller, which can suppress the inrush current induced by time delay.

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Han, X.; LI, T.; Zhang, D. New Issues and Key Technologies of New Power System Planning under Double Carbon Goals. High Volt. Eng. 2021, 346, 3036–3046. [Google Scholar]

- Liu, Y.; Chen, L.; Han, X. The Key Problem Analysis on the Alternative New Energy under the Energy Transition. Proc. CSEE 2022, 42, 515–524. [Google Scholar]

- Xu, J.; Liu, W.; Liu, S. Current State and Development Trends of Power System Converter Grid-forming Control Technology. Power Syst. Technol. 2022, 46, 3586–3595. [Google Scholar]

- Zhou, X.; Chen, S.; Lu, Z. Technology Features of the New Generation Power System in China. Proc. CSEE 2018, 38, 1893–1904+2205. [Google Scholar]

- Taul, M.G.; Wang, X.; Davari, P. An Overview of Assessment Methods for Synchronization Stability of Grid-Connected Converters under Severe Symmetrical Grid Faults. IEEE Trans. Power Electron. 2019, 34, 9655–9670. [Google Scholar] [CrossRef]

- Ebinyu, E.; Abdel-Rahim, O.; Mansour, D.A.; Shoyama, M.; Abdelkader, S.M. Grid-Forming Control: Advancements towards 100% Inverter-Based Grids—A Review. Energies 2023, 16, 7579. [Google Scholar] [CrossRef]

- Zhang, H.; Xiang, W.; Lin, W.; Wen, J. Grid Forming Converters in Renewable Energy Sources Dominated Power Grid: Control Strategy, Stability, Application, and Challenges. J. Mod. Power Syst. Clean Energy 2021, 9, 1239–1256. [Google Scholar] [CrossRef]

- Henninger, S.; Schroeder, M.; Jaeger, J. Grid-Forming Droop Control of a Modular Multilevel Converter in Laboratory. In Proceedings of the 2018 IEEE Power & Energy Society General Meeting (PESGM), Portland, OR, USA, 5–10 August 2018. [Google Scholar]

- D’Arco, S.; Suul, J.A. Equivalence of Virtual Synchronous Machines and Frequency-Droops for Converter-Based MicroGrids. IEEE Trans. Smart Grid 2014, 5, 394–395. [Google Scholar] [CrossRef]

- Liu, J.; Miura, Y.; Ise, T. Comparison of Dynamic Characteristics Between Virtual Synchronous Generator and Droop Control in Inverter-Based Distributed Generators. IEEE Trans. Power Electron. 2015, 31, 3600–3611. [Google Scholar] [CrossRef]

- Ding, M.; Yang, X.; Su, X. Microgrid inverter power supply control strategy based on the idea of virtual synchronous generator. Autom. Electr. Power Syst. 2009, 33, 89–93. [Google Scholar]

- Sakimoto, K.; Miura, Y.; Ise, T. Stabilization of a power system with a distributed generator by a Virtual Synchronous Generator function. In Proceedings of the 8th International Conference on Power Electronics—ECCE Asia, Jeju, Republic of Korea, 30 May–3 June 2011; pp. 1498–1505. [Google Scholar]

- Baltas, G.N.; Lai, N.B.; Marini, L. Grid-forming Power Converter controller with Artificial Intelligence to Attenuate Inter-Area Modes. In Proceedings of the 2020 IEEE 21st Workshop on Control and Modeling for Power Electronics (COMPEL), Aalborg, Denmark, 9–12 November 2020; IEEE: Piscataway, NJ, USA, 2020. [Google Scholar]

- Seo, G.S.; Colombino, M.; Subotic, I. Dispatchable Virtual Oscillator Control for Decentralized Inverter-dominated Power Systems: Analysis and Experiments. In Proceedings of the Applied Power Electronics Conference, Anaheim, CA, USA, 17–21 March 2019; IEEE: Piscataway, NJ, USA, 2019. [Google Scholar]

- Zhao, X.; Flynn, D. Freezing Grid-Forming Converter Virtual Angular Speed to Enhance Transient Stability under Current Reference Limiting. In Proceedings of the 2020 IEEE 21st Workshop on Control and Modeling for Power Electronics (COMPEL), Aalborg, Denmark, 9–12 November 2020; IEEE: Piscataway, NJ, USA, 2020. [Google Scholar]

- Li, T.; Li, Y.; Chen, X.; Li, S.; Zhang, W. Research on AC Microgrid with Current-Limiting Ability Using Power-State Equation and Improved Lyapunov-Function Method. IEEE J. Emerg. Sel. Top. Power Electron. 2021, 9, 7306–7319. [Google Scholar] [CrossRef]

- Mahamedi, B.; Eskandari, M.; Fletcher, J.E.; Zhu, J. Sequence-Based Control Strategy with Current Limiting for the Fault Ride-Through of Inverter-Interfaced Distributed Generators. IEEE Trans. Sustain. Energy 2020, 11, 165–174. [Google Scholar] [CrossRef]

- Fan, B.; Wang, X. Fault Recovery Analysis of Grid-Forming Inverters with Priority-Based Current Limiters. IEEE Trans. Power Syst. 2023, 38, 5102–5112. [Google Scholar] [CrossRef]

- Camacho, A.; Castilla, M.; Miret, J. Active and Reactive Power Strategies with Peak Current Limitation for Distributed Generation Inverters During Unbalanced Grid Faults. IEEE Trans. Ind. Electron. 2015, 62, 1515–1525. [Google Scholar] [CrossRef]

- Paquette, A.; Divan, D. Virtual Impedance Current Limiting for Inverters in Microgrids with Synchronous Generators. IEEE Trans. Ind. Appl. 2015, 51, 1630–1638. [Google Scholar] [CrossRef]

- Lu, X.; Wang, J.; Guerrero, J.M.; Zhao, D. Virtual-Impedance-Based Fault Current Limiters for Inverter Dominated AC Microgrids. IEEE Trans. Smart Grid 2018, 9, 1599–1612. [Google Scholar] [CrossRef]

- Wu, H.; Wang, X. Small-Signal Modeling and Controller Parameters Tuning of Grid-Forming VSCs with Adaptive Virtual Impedance-Based Current Limitation. IEEE Trans. Power Electron. 2022, 37, 7185–7199. [Google Scholar] [CrossRef]

- Xiong, X.; Wu, C.; Blaabjerg, F. Effects of Virtual Resistance on Transient Stability of Virtual Synchronous Generators under Grid Voltage Sag. IEEE Trans. Ind. Electron. 2022, 69, 4754–4764. [Google Scholar] [CrossRef]

- Wang, P.; Wang, P.; Li, S. Dynamic Current-Limiting Control Strategy of Grid-Forming Inverter under Grid Fault. High Volt. Eng. 2022, 48, 3829–3837. [Google Scholar]

- Shang, L.; Hu, J.; Yuan, X. Modeling and Improved Control of Virtual Synchronous Generators under Symmetrical Faults of Grid. Proc. CSEE 2017, 37, 403–412. [Google Scholar]

- Zhou, L.; Liu, S.; Chen, Y.; Yi, W.; Wang, S.; Zhou, X.; Wu, W.; Zhou, J.; Xiao, C.; Liu, A. Harmonic Current and Inrush Fault Current Coordinated Suppression Method for VSG under Non-ideal Grid Condition. IEEE Trans. Power Electron. 2021, 36, 1030–1042. [Google Scholar] [CrossRef]

- Erdocia, J.; Urtasun, A.; Marroyo, L. Dual Voltage–Current Control to Provide Grid-Forming Inverters with Current Limiting Capability. IEEE J. Emerg. Sel. Top. Power Electron. 2022, 10, 3950–3962. [Google Scholar] [CrossRef]

- Fan, B.; Wang, X. Equivalent Circuit Model of Grid-Forming Converters with Circular Current Limiter for Transient Stability Analysis. IEEE Trans. Power Syst. 2022, 37, 3141–3144. [Google Scholar] [CrossRef]

- Huang, L.; Xin, H.; Wang, Z.; Zhang, L.; Wu, K.; Hu, J. Transient Stability Analysis and Control Design of Droop-Controlled Voltage Source Converters Considering Current Limitation. IEEE Trans. Smart Grid 2019, 10, 578–591. [Google Scholar] [CrossRef]

- Zhuang, K.; Xin, H.; Hu, P.; Wang, Z. Current Saturation Analysis and Anti-Windup Control Design of Grid-Forming Voltage Source Converter. IEEE Trans. Energy Convers. 2022, 37, 2790–2802. [Google Scholar] [CrossRef]

- Laaksonen, H.; Saari, P.; Komulainen, R. Voltage and frequency control of inverter based weak LV network microgrid. In Proceedings of the 2005 International Conference on Future Power Systems, Amsterdam, The Netherlands, 18 November 2005; IEEE: Piscataway, NJ, USA, 2005. [Google Scholar]

- Xu, F.; Hu, C.; Wang, F. Research on Droop Control Strategy of Improved Gird-connected Inverters. High Volt. Appar. 2017, 53, 106–112. [Google Scholar]

- Li, Y.; Gu, Y.; Zhu, Y. Impedance Circuit Model of Grid-Forming Inverter: Visualizing Control Algorithms as Circuit Elements. IEEE Trans. Power Electron. 2021, 36, 3377–3395. [Google Scholar] [CrossRef]

| Current-Limitation Method | Advantage | Defect |

|---|---|---|

| High-power device | Strong overcurrent ability | High cost |

| Current loop limitation [15,16,17,18] | Simple design and control | Voltage loop saturation, may fail to restore [18] |

| Output power limitation | Avoid voltage loop saturation | Ignore dynamic response |

| Virtual impedance [20,21,22,23,24,25] | Avoid voltage loop saturation, good to restore | Difficulty in switching |

| Voltage loop limitation [26,27] | Good to restore | Anti-saturation algorithm complexity, low applicability [28,29,30] |

| S | R | State |

|---|---|---|

| 1 | 0 | 1 |

| 0 | 1 | 0 |

| 0 | 0 | hold |

| Parameter | Value | Parameter | Value |

|---|---|---|---|

| DC bus voltage Udc | 800 V | Grid-side equivalent inductance Lg | 5 mH |

| Switching frequency fs | 10 kHz | Grid-side equivalent resistance Rg | 0.9 Ω |

| Inductance Lf | 10 mH | Reactive droop coefficient Dq | 3 × 10−4 |

| Capacitance Cf | 50 μF | Active droop coefficient Dp | 3.33 × 10−4 |

| Current controller P gain kip | 50 | Active power reference Pref | 20 kW |

| Virtual resistor Rv | 1 Ω | Voltage controller P gain kup | 0.5 |

| Virtual inductance Lv | 5 mH | Voltage controller I gain kui | 100 |

| Voltage magnitude reference value E | 311 V | Frequency reference ωref | 50 Hz |

| Parameter | Value | Parameter | Value |

|---|---|---|---|

| DC bus voltage Udc | 800 V | Grid-side equivalent inductance Lg | 10 mH |

| Switching frequency fs | 10 kHz | Current controller I gain kii | 333 |

| Inductance Lf | 3 mH | Reactive droop coefficient Dq | 2 × 10−4 |

| Capacitance Cf | 100 μF | Active droop coefficient Dp | 3 × 10−4 |

| Current controller P gain kip | 30 | Active power reference Pref | 20 kW |

| Virtual resistor Rv | 2 Ω | Voltage controller P gain kup | 0.15 |

| Virtual inductance Lv | 5 mH | Voltage controller I gain kui | 75 |

| Voltage magnitude reference value E | 311 V | Frequency reference ωref | 50 Hz |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhang, H.; Ma, J.; Li, X. Dynamic Current-Limitation Strategy of Grid-Forming Inverters Based on SR Latches. Electronics 2024, 13, 3432. https://doi.org/10.3390/electronics13173432

Zhang H, Ma J, Li X. Dynamic Current-Limitation Strategy of Grid-Forming Inverters Based on SR Latches. Electronics. 2024; 13(17):3432. https://doi.org/10.3390/electronics13173432

Chicago/Turabian StyleZhang, Huajie, Junpeng Ma, and Xiaopeng Li. 2024. "Dynamic Current-Limitation Strategy of Grid-Forming Inverters Based on SR Latches" Electronics 13, no. 17: 3432. https://doi.org/10.3390/electronics13173432