A Voltage Equalization Strategy for Series-Connected SiC MOSFET Applications

Abstract

:1. Introduction

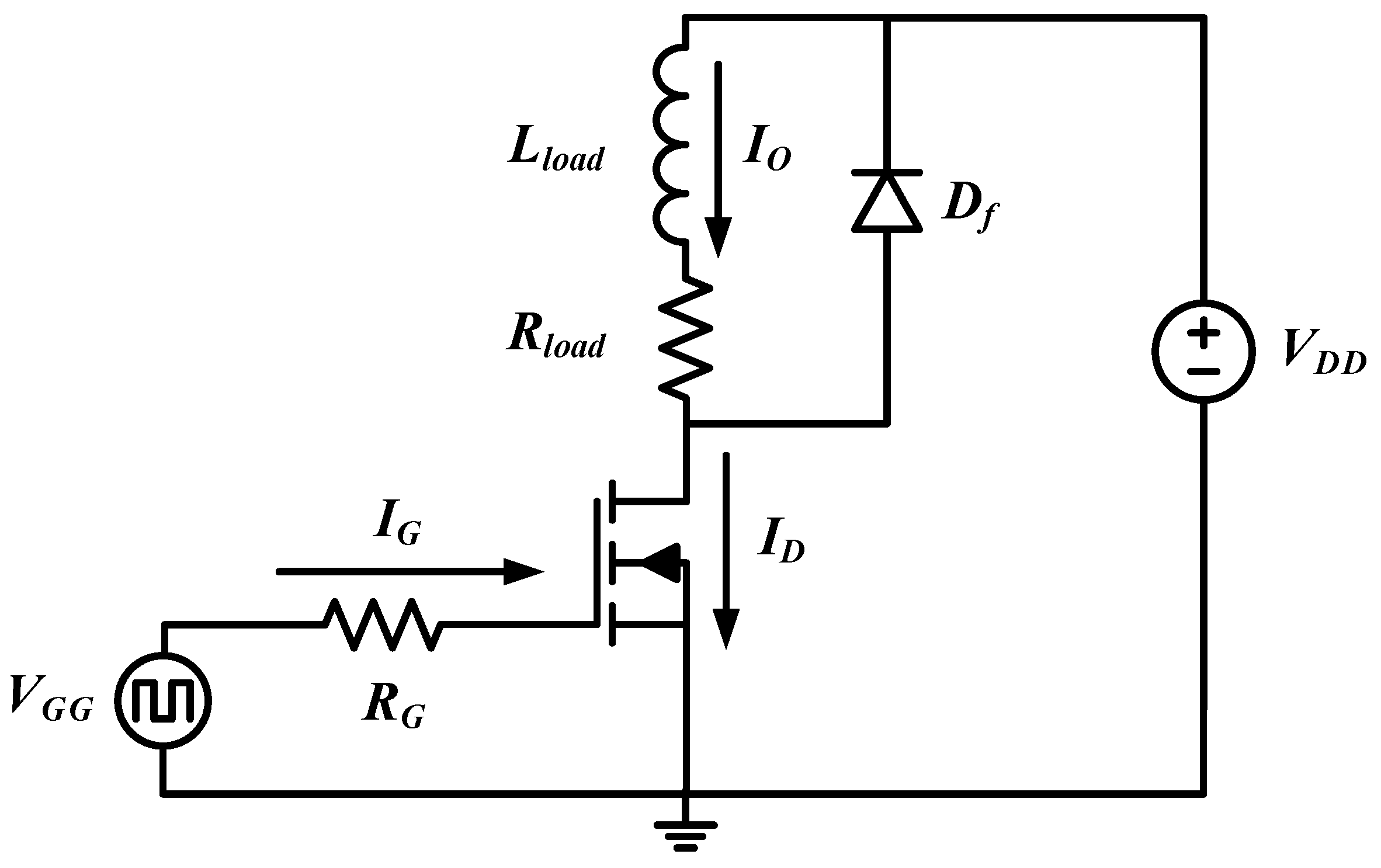

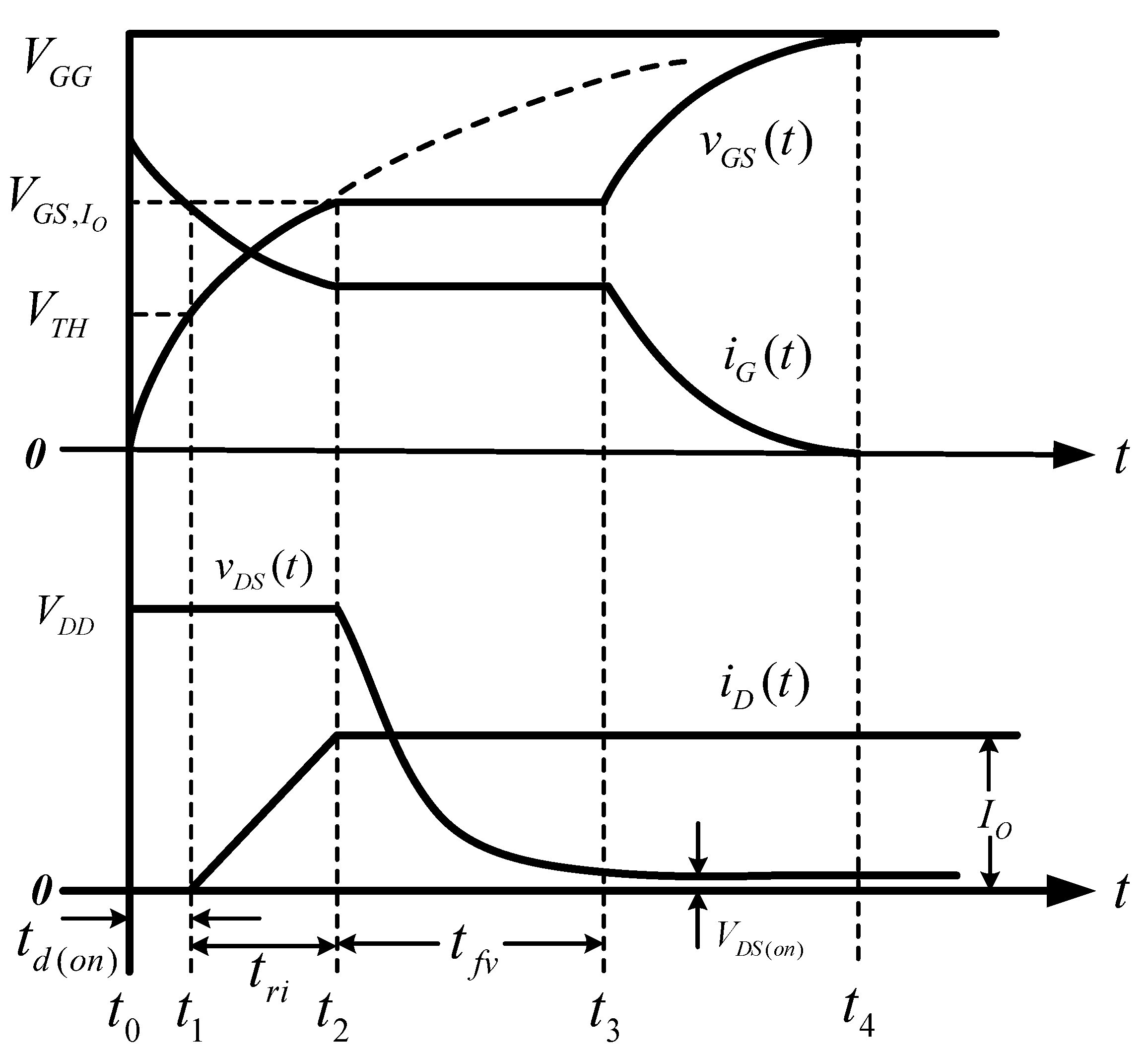

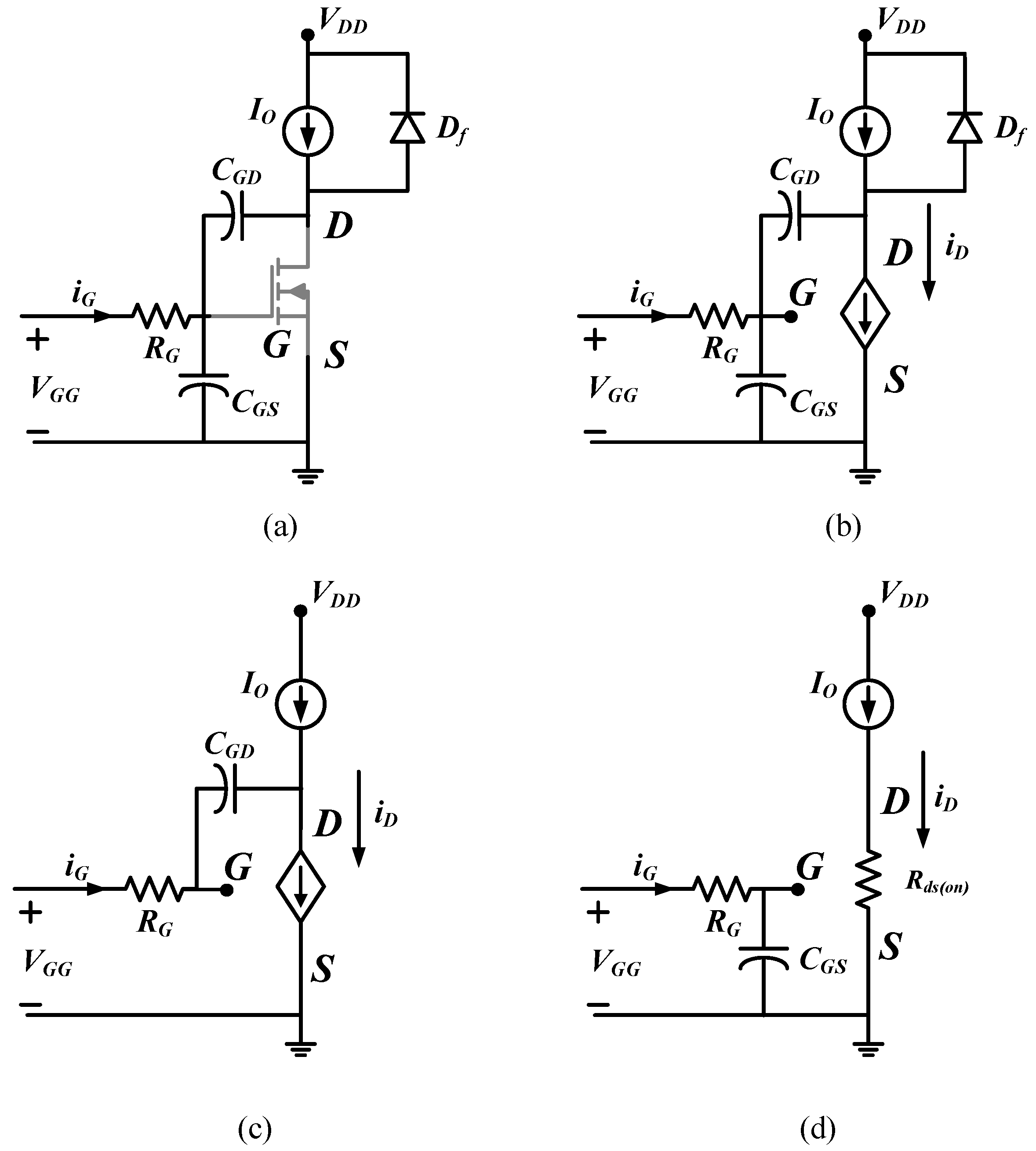

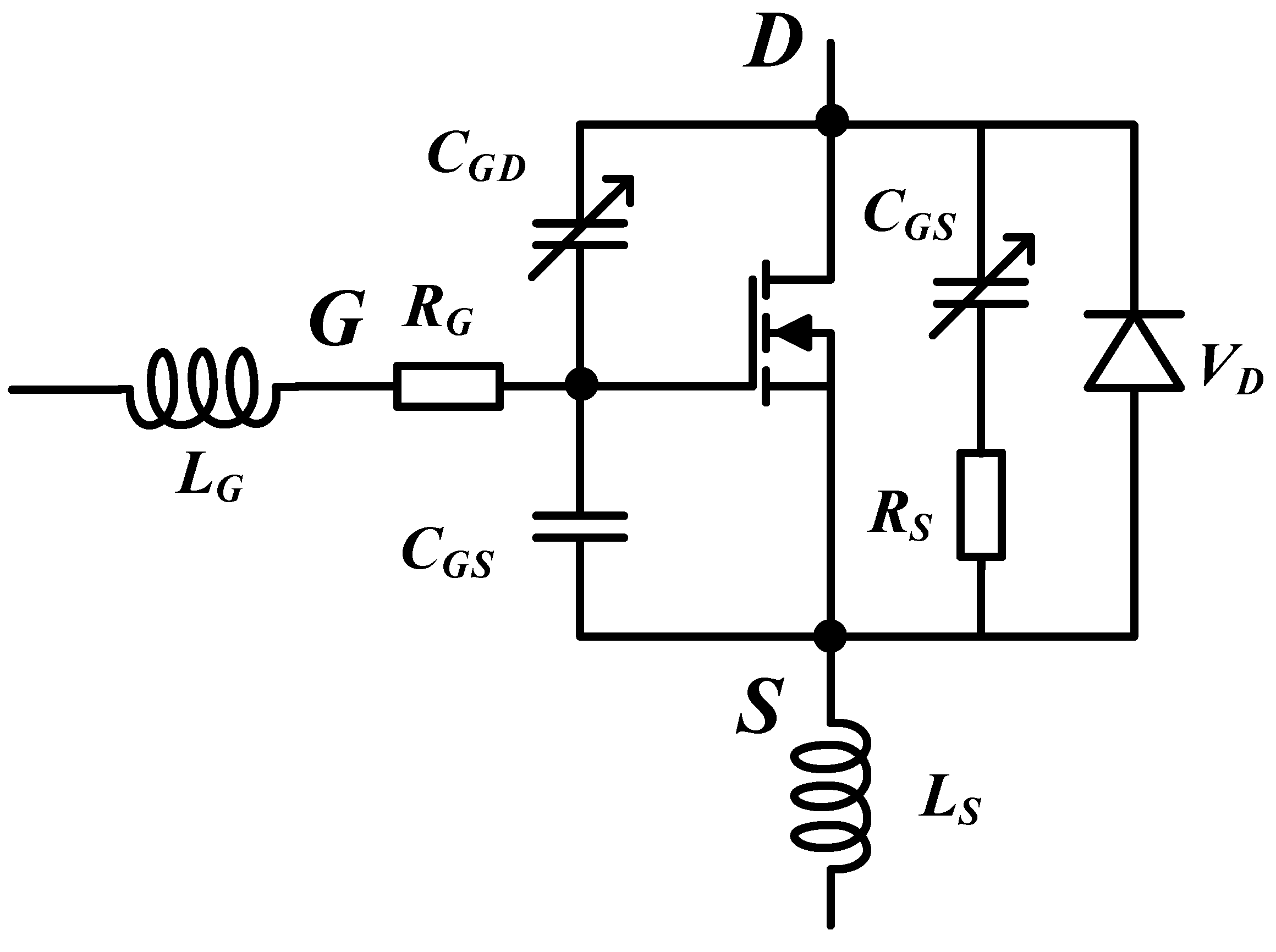

2. The Analysis of the Dynamic Characteristics

2.1. The Switching Characteristics of the SiC MOSFET

2.2. The Dynamic Voltage Distribution Analysis of the Series-Connected SiC MOSFETs

- (1)

- The difference at the moment when the MOSFET enters the current rise phase (). There are two sources of this difference, one is the gate drive delay difference, which is due to the gate drive circuit difference; the other is the difference in the turn-on delay time () of individual MOSFETs, which is mainly due to the threshold voltage and input capacitance differences. During the current rise interval, the MOSFET can be equated to a gate voltage-controlled current source. At this point, the MOSFET can be viewed as an ever-decreasing resistor from the drain–source point of view. If the MOSFET enters this stage later, its equivalent drain–source resistance is relatively large, and, thus, its drain–source voltage is large. The difference in the stage of current rise entered by each MOSFET can lead to uneven voltage.

- (2)

- MOSFETs have different rates of current change during the current rise interval (). According to (8), the difference in transconductance of each MOSFET will result in a different rate of current rise. This is due to unavoidable differences in device fabrication. From the drain–source point of view, the equivalent resistance of each MOSFET will be different. Uneven voltage may occur at this stage.

- (3)

- MOSFETs have different rates of voltage change during the voltage drop interval (). In this interval, MOSFET can be equivalent to a variable capacitor, and its capacitance rises as the drain–source voltage falls. Thus, the difference in output equivalent capacitance can lead to uneven voltage. However, since the total voltage to which the series MOSFETs are subjected at this stage has already begun to fall, voltage unevenness does not normally lead to serious problems.

- (1)

- The difference at the moment when the MOSFET enters the voltage rise phase (). There are two sources of this difference, one is the gate drive delay difference, which is due to the gate drive circuit difference; the second is the difference in the turn-off delay time () of each MOSFET, which is mainly due to the difference in the threshold voltage and the input capacitance . In this interval, the MOSFET can be equated to a variable capacitor and its capacitance decreases as the drain–source voltage rises. The voltage rise interval can be considered as a charging process of the ever-smaller MOSFET output capacitance. MOSFETs that turn off early are necessarily subjected to higher drain–source voltages. If the difference in MOSFET turn-off delay is too large, it is easy to cause overvoltage damage to the MOSFET. According to theoretical analyses and experimental results, the turn-off delay difference [27] is considered to be the main factor affecting the turn-off voltage equalization of series-connected SiC MOSFETs. Thus, it is quite important to ensure that the series SiC MOSFET turn-off delay is synchronized.

- (2)

- The difference in the rate of voltage change of MOSFETs during the voltage rise phase (). Even though the drain–source voltage of each MOSFET in the series starts to rise at the same time, the difference in the rate of voltage change of the MOSFETs at this stage is difficult to avoid. The MOSFET at this stage can be equated to the charging process of a variable capacitor. The rate of voltage change during the Miller plateau period is mainly determined by the gate drive current and the MOSFET feedback capacitance . Due to device fabrication differences, the feedback capacitance is different, causing the MOSFET voltage imbalance at this stage.

- (3)

- Circuit stray capacitance. Relevant studies have shown that [28] even if the driver circuit and the MOSFET are kept the same, the difference in stray parasitic capacitance will still cause uneven turn-off voltage. There are two main sources of stray capacitance. The first is the unavoidable stray capacitance that exists between the gate driver and ground, mainly the transformer coupling capacitance. The second is the parasitic stray capacitance between each port of the MOSFET on the main circuit and ground, which is related to device placement and PCB layout.

- (4)

- MOSFETs have different rates of current change during the current drop phase (). At this point in this interval, the MOSFET can be regarded as an ever-increasing resistance from the drain–source point of view. The unavoidable difference in transconductance between the MOSFETs will result in a difference in the equivalent resistance of each MOSFET, which leads to an imbalance in the MOSFET drain–source voltage.

2.3. The Simulation of the Dynamic Voltage Distribution

The Driver Delay Variance Affection

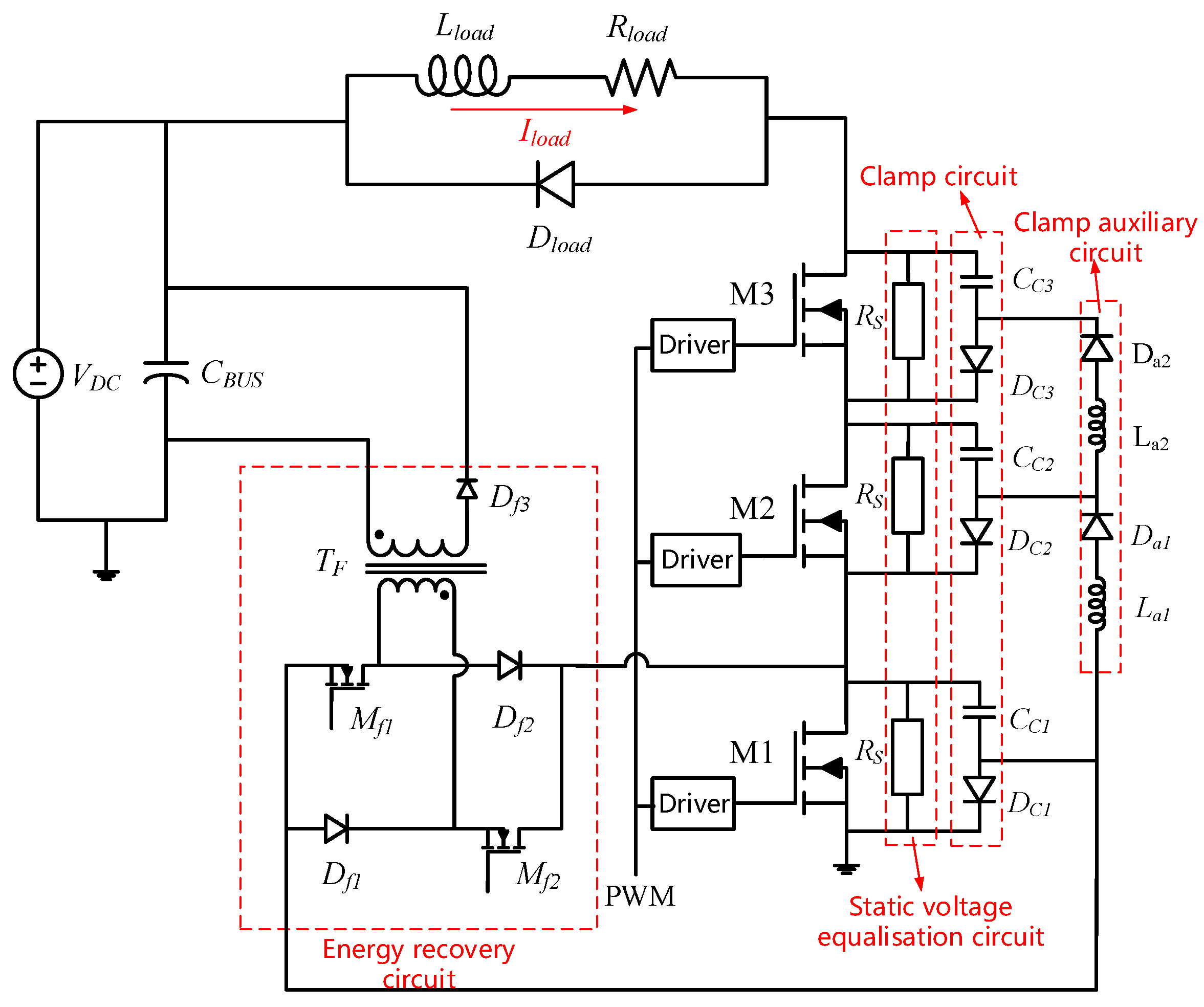

3. The Novel Series SiC MOSFET Topology Design

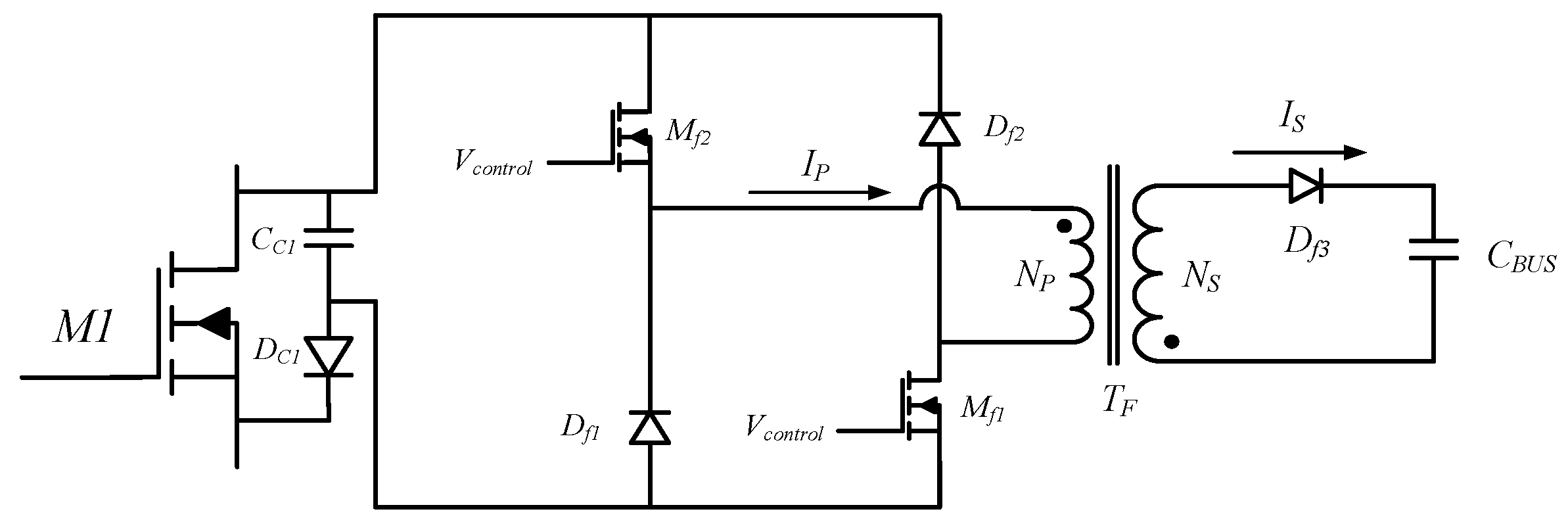

3.1. The Energy Recovery Circuit Design

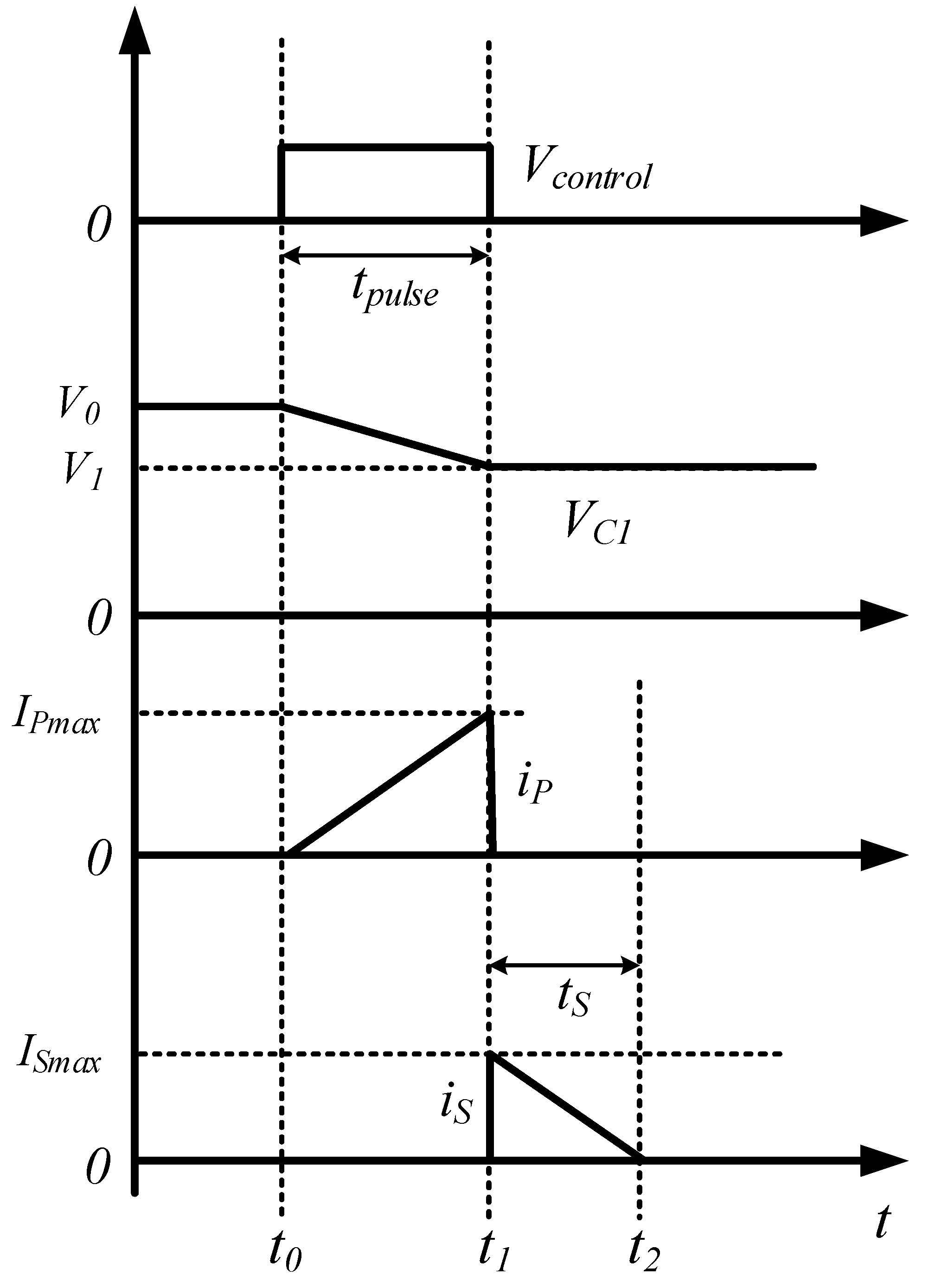

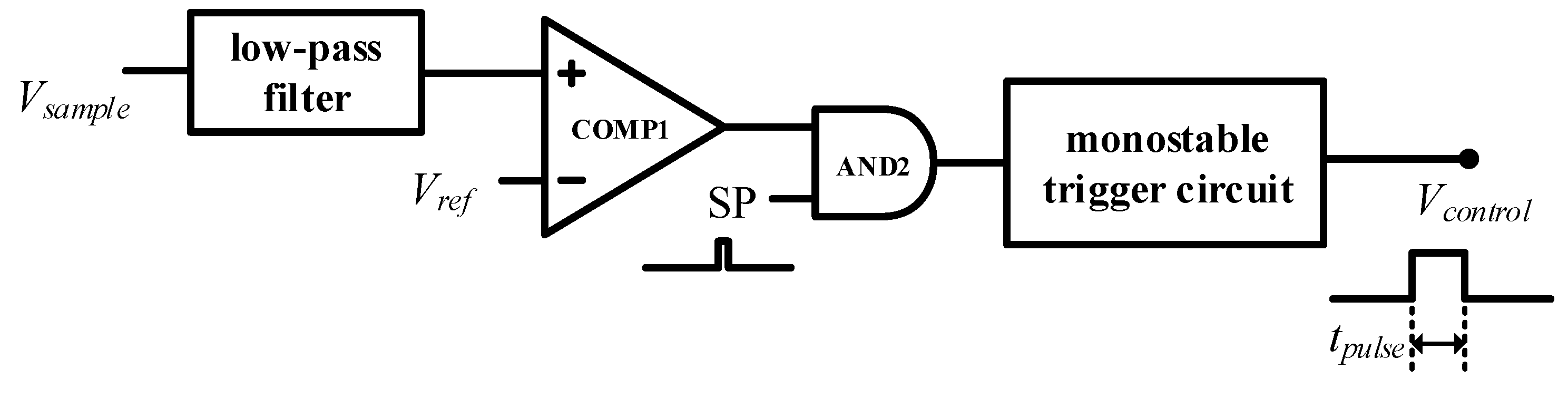

3.2. The Feedback Control Circuit Analysis

- (1)

- Before , since is high enough, the will be higher than , and then, COMP1’s output is high. However, SP is low and AND2’s output is still low.

- (2)

- At , SP becomes high and lasts for a short time. Since the COMP1 output is high, the AND2 output changes from low to high. This rising edge will trigger a monostable trigger to generate a signal with a pulse width of for controlling the energy recovery circuit. The operation of the energy recovery circuit is shown in Figure 10. During phase [–], the switching tube of the energy recovery circuit is switched on. During this phase, the continues to drop and energy is transferred to the primary coil of the flyback transformer.

- (3)

- At , becomes low. The switching tube of the energy recovery circuit turns off, and the transformer’s secondary coil back-excites the current. Although has dropped to the permissible value, the comparator COMP1’s output is still high. This is due to the delay of the Hall voltage sensor, which does not reduce the COMP1 output until the moment after the time. During the [–] phase, may rise due to the activation of the clamp capacitor and the clamp auxiliary circuit.

- (4)

- At , the SP signal becomes high and the period of the SP signal is . If ’s voltage rises more in the phase [–], causing the COMP1 output to be high at , the monostable flip-flop will be activated next, repeating the process (1)–(3). If is small and does not exceed the predetermined voltage in the phase [–], the COMP1 output is low at , the AND2 output is low and the monostable flip-flop will not operate. The monostable circuit operation will be decided Until the next rising edge of the SP signal according to the COMP1 output.

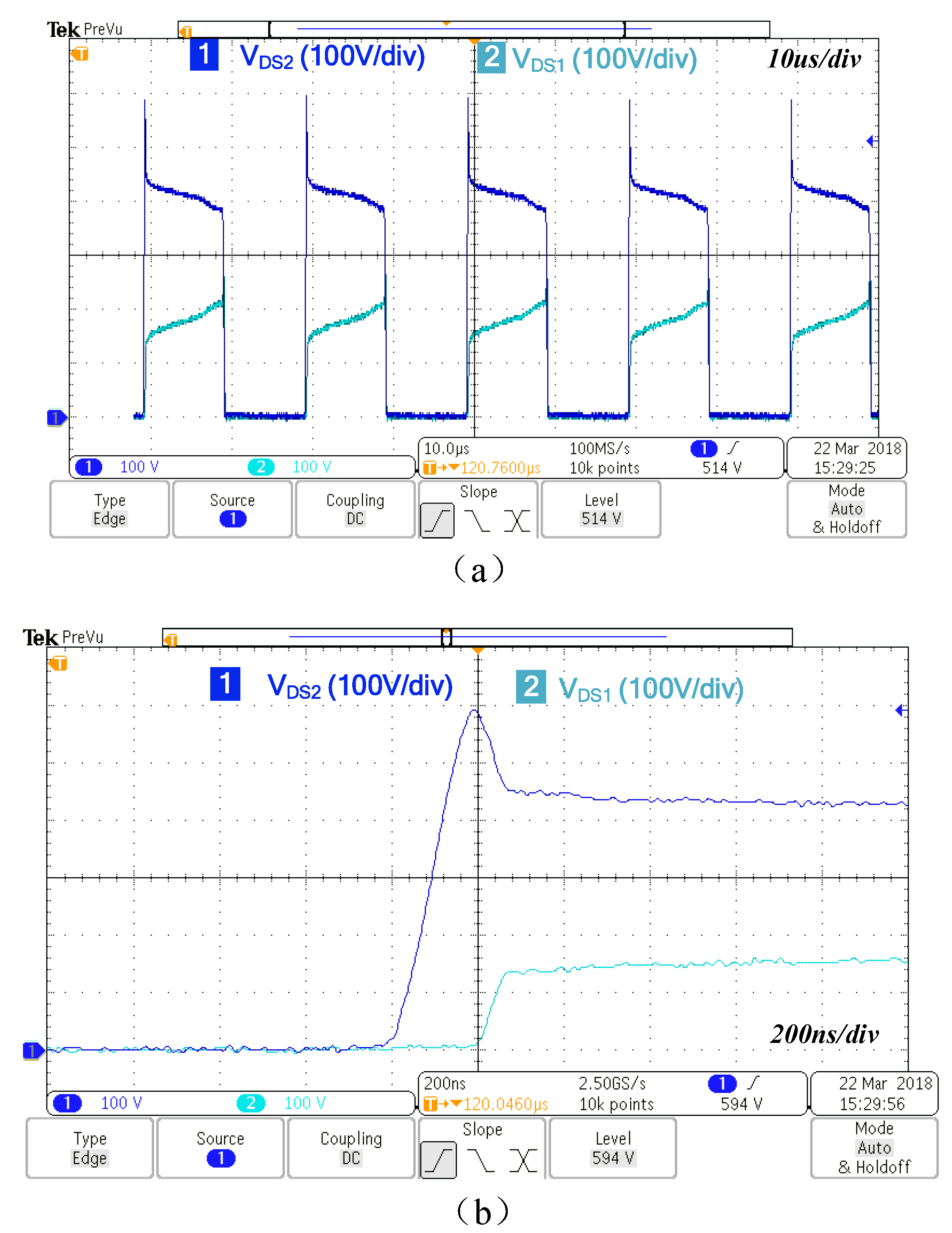

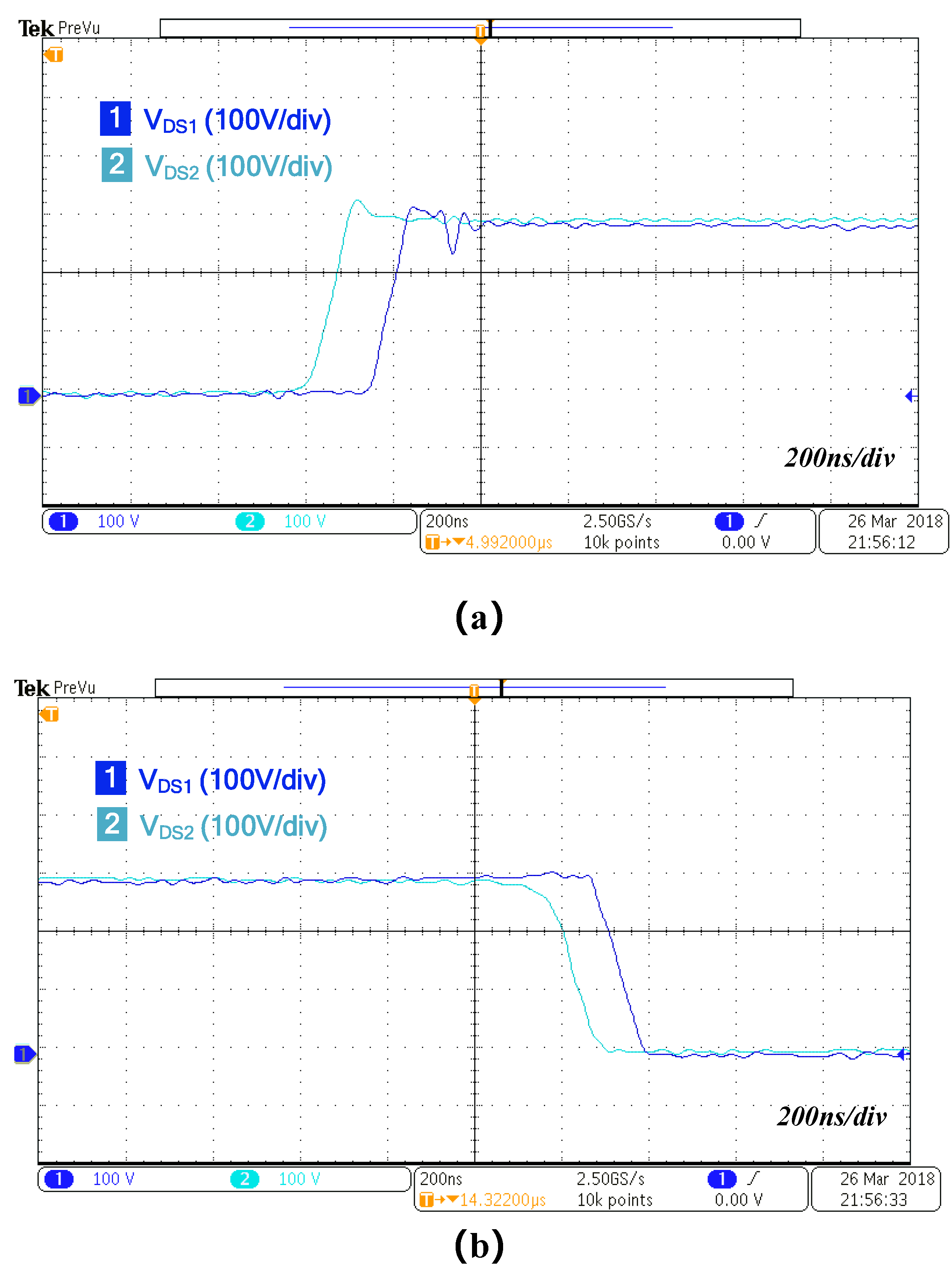

4. The Experimental Results

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Millán, J.; Godignon, P.; Perpiñà, X.; Pérez-Tomás, A.; Rebollo, J. A Survey of Wide Bandgap Power Semiconductor Devices. IEEE Trans. Power Electron. 2014, 29, 2155–2163. [Google Scholar] [CrossRef]

- Palmour, J.W. Silicon carbide power device development for industrial markets. In Proceedings of the 2014 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 15–17 December 2014; pp. 1.1.1–1.1.8. [Google Scholar] [CrossRef]

- Song, Q.; Yang, S.; Tang, G.; Han, C.; Zhang, Y.; Tang, X.; Zhang, Y.; Zhang, Y. 4H-SiC Trench MOSFET With L-Shaped Gate. IEEE Electron Device Lett. 2016, 37, 463–466. [Google Scholar] [CrossRef]

- She, X.; Huang, A.Q.; Lucía, O.; Ozpineci, B. Review of Silicon Carbide Power Devices and Their Applications. IEEE Trans. Ind. Electron. 2017, 64, 8193–8205. [Google Scholar] [CrossRef]

- Song, Q.; Yuan, H.; Sun, Q.; Han, C.; Tang, X.; Zhang, Y.; Yuan, L.; Yang, S.; Zhang, Y. Reverse-Bias Stress-Induced Electrical Parameters Instability in 4H-SiC JBS Diodes Terminated Nonequidistance FLRs. IEEE Trans. Electron Devices 2019, 66, 3935–3939. [Google Scholar] [CrossRef]

- Yu, L.; Sheng, K. Modeling and Optimal Device Design for 4H-SiC Super-Junction Devices. IEEE Trans. Electron Devices 2008, 55, 1961–1969. [Google Scholar] [CrossRef]

- Bolotnikov, A.; Losee, P.; Permuy, A.; Dunne, G.; Kennerly, S.; Rowden, B.; Nasadoski, J.; Harfman-Todorovic, M.; Raju, R.; Tao, F.; et al. Overview of 1.2–2.2 kV SiC MOSFETs targeted for industrial power conversion applications. In Proceedings of the 2015 IEEE Applied Power Electronics Conference and Exposition (APEC), Charlotte, NC, USA, 15–19 March 2015; pp. 2445–2452. [Google Scholar] [CrossRef]

- Ferraro, A. An overview of low-loss snubber technology for transistor converters. In Proceedings of the 1982 IEEE Power Electronics Specialists conference, Cambridge, MA, USA, 14–17 June 1982; pp. 466–477. [Google Scholar] [CrossRef]

- Vechalapu, K.; Negi, A.; Bhattacharya, S. Comparative performance evaluation of series connected 15 kV SiC IGBT devices and 15 kV SiC MOSFET devices for MV power conversion systems. In Proceedings of the Energy Conversion Congress and Exposition (ECCE), Milwaukee, WI, USA, 18–22 September 2016; pp. 1–8. [Google Scholar]

- Busatto, G.; Cascone, B.; Fratelli, L.; Luciano, A. Series connection of IGBTs in hard-switching applications. In Proceedings of the Industry Applications Conference, 1998. Thirty-Third IAS Annual Meeting, St. Louis, MO, USA, 12–15 October 1998; Volume 2, pp. 825–830. [Google Scholar]

- Robinson, F.V.; Hamidi, V. Series connecting devices for high-voltage power conversion. In Proceedings of the 2007 42nd International Universities Power Engineering Conference, Brighton, UK, 4–6 September 2007; pp. 1134–1139. [Google Scholar] [CrossRef]

- Lim, T.C.; Williams, B.W.; Finney, S.J. Active Snubber Energy Recovery Circuit for Series-Connected IGBTs. IEEE Trans. Power Electron. 2011, 26, 1879–1889. [Google Scholar] [CrossRef]

- Zheng, S.; Wang, Y.; Wu, X.; Qian, Z.; Peng, F.Z. The voltage sharing of commercial IGBTS in series with passive components. In Proceedings of the 2011 IEEE Energy Conversion Congress and Exposition, Phoenix, AZ, USA, 17–22 September 2011; pp. 3008–3012. [Google Scholar] [CrossRef]

- Gerster, C. Fast high-power/high-voltage switch using series-connected IGBTs with active gate-controlled voltage-balancing. In Proceedings of the Applied Power Electronics Conference and Exposition—APEC’94, Orlando, FL, USA, 13–17 February 1994; Volume 1, pp. 469–472. [Google Scholar] [CrossRef]

- Sasagawa, K.; Abe, Y.; Matsuse, K. Voltage-balancing method for IGBTs connected in series. IEEE Trans. Ind. Appl. 2004, 40, 1025–1030. [Google Scholar] [CrossRef]

- Palmer, P.R.; Zhang, J.; Zhang, X. SiC MOSFETs connected in series with active voltage control. In Proceedings of the 2015 IEEE 3rd Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Blacksburg, VA, USA, 2–4 November 2015; pp. 60–65. [Google Scholar] [CrossRef]

- Raciti, A.; Belverde, G.; Galluzzo, A.; Greco, G.; Melito, M.; Musumeci, S. Control of the switching transients of IGBT series strings by high-performance drive units. IEEE Trans. Ind. Electron. 2001, 48, 482–490. [Google Scholar] [CrossRef]

- Bruckmann, M.; Sommer, R.; Fasching, M.; Sigg, J. Series connection of high voltage IGBT modules. In Proceedings of the Conference Record of 1998 IEEE Industry Applications Conference. Thirty-Third IAS Annual Meeting (Cat. No.98CH36242), St. Louis, MO, USA, 12–15 October 1998; Volume 2, pp. 1067–1072. [Google Scholar] [CrossRef]

- Saiz, J.; Mermet, M.; Frey, D.; Jeannin, P.O.; Schanen, J.L.; Muszicki, P. Optimisation and integration of an active clamping circuit for IGBT series association. In Proceedings of the Conference Record of the 2001 IEEE Industry Applications Conference. 36th IAS Annual Meeting (Cat. No.01CH37248), Chicago, IL, USA, 30 September–4 October 2001; Volume 2, pp. 1046–1051. [Google Scholar] [CrossRef]

- Nakatake, H.; Iwata, A. Series connection of IGBTs used multilevel clamp circuit and turn off timing adjustment circuit. In Proceedings of the Power Electronics Specialist Conference, 2003. PESC’03, Acapulco, Mexico, 15–19 June 2003; Volume 4, pp. 1910–1915. [Google Scholar] [CrossRef]

- Hess, H.L.; Baker, R.J. Transformerless capacitive coupling of gate signals for series operation of power MOS devices. IEEE Trans. Power Electron. 2000, 15, 923–930. [Google Scholar] [CrossRef]

- Kim, J.H.; Min, B.D.; Shenderey, S.V.; Rim, G.H. High voltage pulsed power supply using IGBT stacks. IEEE Trans. Dielectr. Electr. Insul. 2007, 14, 921–926. [Google Scholar] [CrossRef]

- Teerakawanich, N.; Johnson, C.M. Design optimization of quasi-active gate control for series-connected power devices. IEEE Trans. Power Electron. 2014, 29, 2705–2714. [Google Scholar] [CrossRef]

- Wu, X.; Cheng, S.; Xiao, Q.; Sheng, K. A 3600 V/80 A Series–Parallel-Connected Silicon Carbide MOSFETs Module with a Single External Gate Driver. IEEE Trans. Power Electron. 2014, 29, 2296–2306. [Google Scholar] [CrossRef]

- Xiao, Q.; Yan, Y.; Wu, X.; Ren, N.; Sheng, K. A 10 kV/200 A SiC MOSFET module with series-parallel hybrid connection of 1200 V/50 A dies. In Proceedings of the Power Semiconductor Devices & IC’s (ISPSD), Hong Kong, China, 10–14 May 2015; pp. 349–352. [Google Scholar]

- Maniktala, S. Chapter 8—Conduction and Switching Losses. In Switching Power Supplies A–Z, 2nd ed.; Maniktala, S., Ed.; Newnes: Oxford, UK, 2012; pp. 311–341. [Google Scholar] [CrossRef]

- Van Nguyen, T.; Jeannin, P.O.; Vagnon, E.; Frey, D.; Crebier, J.C. Series connection of IGBT. In Proceedings of the Applied Power Electronics Conference and Exposition (APEC), Palm Springs, CA, USA, 21–25 February 2010; pp. 2238–2244. [Google Scholar]

- Han, Y.; Chen, W.; Chen, X.; Ma, X.; Sha, Y.; Yang, X.; Li, X. A 4000 V input auxiliary power supply with series connected SiC MOSFETs for MMC-based HVDC system. In Proceedings of the Power Electronics and Motion Control Conference (IPEMC-ECCE Asia), Hefei, China, 22–26 May 2016; pp. 279–284. [Google Scholar]

- Zhao, M.; Lin, H.; Wang, T. An Adaptive Driving Signals Delay Control for Voltage Balancing of Multiple Series-Connected SiC MOSFETs. In Proceedings of the 2022 IEEE Applied Power Electronics Conference and Exposition (APEC), Houston, TX, USA, 20–24 March 2022; pp. 1619–1624. [Google Scholar] [CrossRef]

- Zhao, M.; Lin, H.; Wang, T. The Application of Series-Connected SiC MOSFETs in Buck Converter Based on Active Driving Signal Delay Control for Voltage Balancing. In Proceedings of the 2022 IEEE Applied Power Electronics Conference and Exposition (APEC), Houston, TX, USA, 20–24 March 2022; pp. 1614–1618. [Google Scholar] [CrossRef]

- Gao, Z.; Pei, X.; Cui, W.; Wu, H.; Shao, S.; Zhang, J. Voltage Balancing Method for Series-Connected SiC MOSFETs Under No Load Condition. In Proceedings of the 2023 20th China International Forum on Solid State Lighting & 2023 9th International Forum on Wide Bandgap Semiconductors (SSLCHINA: IFWS), Xiamen, China, 27–30 November 2023; pp. 157–160. [Google Scholar] [CrossRef]

- Gao, Z.; Shao, S.; Cui, W.; Wu, Y.; Zhang, J.; Sheng, K. A Control Strategy for Reducing Voltage Ripples in Series-Connected SiC MOSFETs Using Active Clamping Modules in High Power VSCs. IEEE Trans. Power Electron. 2024, 39, 12149–12155. [Google Scholar] [CrossRef]

| Parameters | Parameters | ||

|---|---|---|---|

| Power MOSFET | SCH2080KE | Freewheeling diode | SDT12S60 |

| Bus voltage | 2800 V | PWM frequency | 50 kHz |

| Load resistance | 200 Ω | Load inductance | 200 μH |

| Circuit Parameters | Circuit Parameters | ||

|---|---|---|---|

| The main MOSFET | SCH2080KE | Diode and | SCS240KE2 |

| Bus voltage | 600 V | Working frequency | 50 kHz |

| Load inductance | 400 μH | Output capacitance | 340 μF |

| Clamp capacitance | 2 μF | Clamp diode | ES1J |

| Auxiliary diode | ES1J | Current limiting Inductance | 15 μH |

| SP working frequency | 10 kHz | Static Resistor | 100 kΩ |

| Break voltage | 1200 V | Leakage current | 400 μA |

|---|---|---|---|

| Threshold voltage | 4.0 V | on-state resistance@ = 18 V | 80 mΩ |

| Input capacitance | 1850 pF | Output capacitance | 175 pF |

| The Approaches | Extra Devices | Complexity | Energy Recovery |

|---|---|---|---|

| This work | 10 power devices and 2 analog devices | Moderate | Yes |

| Ref. [29] | 11 analog devices | High | No |

| Ref. [30] | 7 analog devices | High | No |

| Ref. [31] | 3 power devices and 6 analog devices | High | No |

| Ref. [32] | 3 power devices and 6 analog devices | High | No |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Li, P.; Liu, J.; Sun, S.; Yang, W.; Sun, Y.; Zhang, Y. A Voltage Equalization Strategy for Series-Connected SiC MOSFET Applications. Electronics 2024, 13, 3766. https://doi.org/10.3390/electronics13183766

Li P, Liu J, Sun S, Yang W, Sun Y, Zhang Y. A Voltage Equalization Strategy for Series-Connected SiC MOSFET Applications. Electronics. 2024; 13(18):3766. https://doi.org/10.3390/electronics13183766

Chicago/Turabian StyleLi, Peng, Jialin Liu, Shikai Sun, Wenhao Yang, Yuyin Sun, and Yuming Zhang. 2024. "A Voltage Equalization Strategy for Series-Connected SiC MOSFET Applications" Electronics 13, no. 18: 3766. https://doi.org/10.3390/electronics13183766