Diagnosis of DC-DC Converter Semiconductor Faults Based on the Second-Order Derivative of the Converter Input Current

Abstract

:1. Introduction

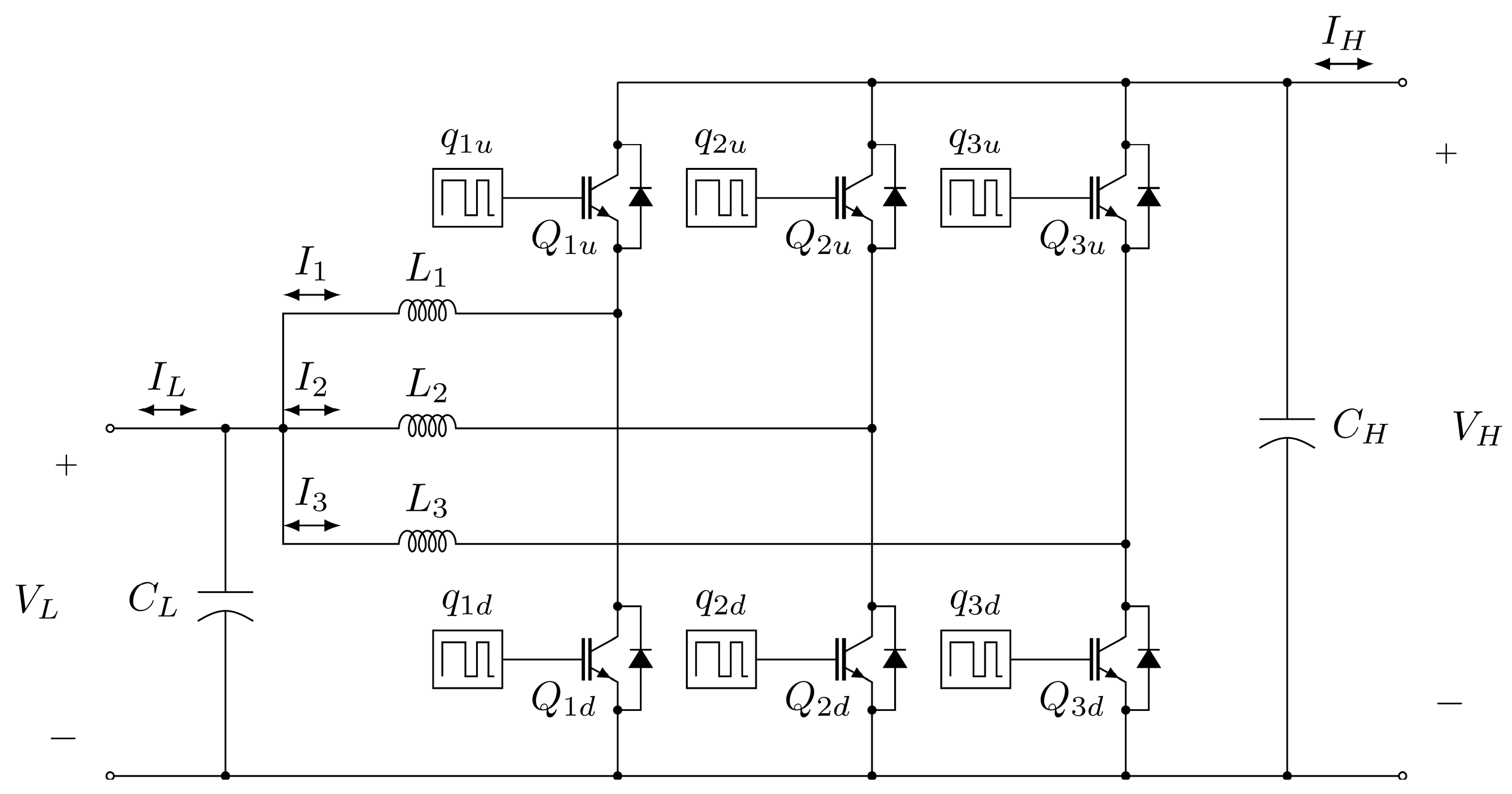

2. Converter Operation

2.1. Operation under Healthy Condition

2.2. Operation under Faulty Condition

2.3. Comparison between Healthy and Faulty Condition

- (1)

- Considering the converter steady-state condition, it is possible to assume that variables D and DM do not suffer significant oscillations along one switching period and, consequently, these variables remain constant.

- (2)

- DM is always equal or higher than D. In practice, this means that condition DM − D is always positive.

- (3)

- The turn-on and turn-off periods are assumed to be identical, resulting in the following conditions:

- For the intervals where D is variable (i.e., 0 < D < 1/3, 1/3 < D < 2/3, and 2/3 < D < 1), d2IL/dt2 approaches to zero for at least one state transition, when an OC fault occurs;

- When D is either equal to 1/3 or 2/3, d2IL/dt2 is positive for the ON → OFF transition; under healthy state, d2IL/dt2 is either null or negative.

- For the intervals where D is variable (i.e., 0 < D < 1/3, 1/3 < D < 2/3, and 2/3 < D < 1), d2IL/dt2 is null for at least one state transition; these conditions are identical to those observed for the boost mode;

- When D is either equal to 1/3 or 2/3, d2IL/dt2 is negative for the ON → OFF transition; under healthy state, d2IL/dt2 is either null or positive; these conditions are complementary to those observed for the boost mode.

3. Proposed Fault Diagnostics Algorithm

4. Simulation Results

5. Experimental Results

Comparison with the State of the Art

6. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Evolution of Households Energy Consumption Patterns across the EU. Available online: https://www.enerdata.net/publications/executive-briefing/households-energy-efficiency.html (accessed on 28 September 2022).

- Bento, F.; Ribeiro, E. DC-DC Converters. In Diagnosis and Fault Tolerance of Electric Machines, Power Electronics and Drives; Marques Cardoso, A.J., Ed.; IET: Hertfordshire, UK, 2018; ISBN 978-1-78561-531-3. [Google Scholar]

- Bento, F.; Marques Cardoso, A.J. A Comprehensive Survey on Fault Diagnosis and Fault Tolerance of DC-DC Converters. Chin. J. Electr. Eng. 2018, 4, 1–12. [Google Scholar] [CrossRef]

- Kumar, G.K.; Elangovan, D. Review on Fault-Diagnosis and Fault-Tolerance for DC-DC Converters. IET Power Electron. 2020, 13, 1–13. [Google Scholar] [CrossRef]

- Park, K.; Chen, Z. Open-Circuit Fault Detection and Tolerant Operation for a Parallel-Connected SAB DC–DC Converter. In Proceedings of the 2014 IEEE Applied Power Electronics Conference and Exposition—APEC 2014, Fort Worth, TX, USA, 16–20 March 2014; pp. 1966–1972. [Google Scholar]

- Ribeiro, E.; Cardoso, A.J.M.; Boccaletti, C. Open-Circuit Fault Diagnosis in Interleaved DC-DC Converters. IEEE Trans. Power Electron. 2014, 29, 3091–3102. [Google Scholar] [CrossRef]

- Jamshidpour, E.; Poure, P.; Saadate, S. Photovoltaic Systems Reliability Improvement by Real-Time FPGA-Based Switch Failure Diagnosis and Fault-Tolerant DC-DC Converter. IEEE Trans. Ind. Electron. 2015, 62, 7247–7255. [Google Scholar] [CrossRef]

- Kamel, T.; Biletskiy, Y.; Chang, L. Real-Time Diagnosis for Open-Circuited and Unbalance Faults in Electronic Converters Connected to Residential Wind Systems. IEEE Trans. Ind. Electron. 2016, 63, 1781–1792. [Google Scholar] [CrossRef]

- Bento, F.; Cardoso, A.J.M. Fault Diagnosis in DC-DC Converters Using a Time-Domain Analysis of the Reference Current Error. In Proceedings of the IECON 2017—43rd Annual Conference of the IEEE Industrial Electronics Society, Beijing, China, 29 October–1 November 2017; pp. 5060–5065. [Google Scholar]

- Ribeiro, E.; Cardoso, A.J.M.; Boccaletti, C. Fault Diagnosis in Unidirectional Non-Isolated DC–DC Converters. In Proceedings of the 2014 IEEE Energy Conversion Congress and Exposition (ECCE), Pittsburgh, PA, USA, 14–18 September 2014; pp. 1140–1145. [Google Scholar]

- Li, C.; Yu, Y.; Tang, T.; Liu, Q.; Peng, X. A Robust Open-Circuit Fault Diagnosis Method for Three-Phase Interleaved Boost Converter. IEEE Trans. Power Electron. 2022, 37, 11187–11198. [Google Scholar] [CrossRef]

- Zandi, O.; Poshtan, J. A Novel Algorithm for Open Switch Fault Detection and Fault Tolerant Control of Interleaved DC-DC Boost Converters. IET Power Electron. 2024, 17, 721–730. [Google Scholar] [CrossRef]

- Bento, F.; Cardoso, A.J.M. Open-Circuit Fault Diagnosis and Fault Tolerant Operation of Interleaved DC-DC Boost Converters for Homes and Offices. IEEE Trans. Ind. Appl. 2019, 55, 4855–4864. [Google Scholar] [CrossRef]

- Farjah, E.; Givi, H.; Ghanbari, T. Application of an Efficient Rogowski Coil Sensor for Switch Fault Diagnosis and Capacitor ESR Monitoring in Nonisolated Single-Switch DC–DC Converters. IEEE Trans. Power Electron. 2017, 32, 1442–1456. [Google Scholar] [CrossRef]

- Bento, F.; Cardoso, A.J.M. Fault Tolerant DC-DC Converters in DC Microgrids. In Proceedings of the 2017 IEEE Second International Conference on DC Microgrids (ICDCM), Nuremberg, Germany, 27–29 June 2017; pp. 484–490. [Google Scholar]

- Muhammed Ramees, M.K.P.; Ahmad, M.W. An Integrated Approach for Current Balancing and Open-Circuit Fault Diagnosis for Interleaved Boost Converter. IEEE Trans. Ind. Electron. 2024, 71, 13310–13318. [Google Scholar] [CrossRef]

- Ribeiro, E.; Cardoso, A.J.M.; Boccaletti, C. Fault-Tolerant Strategy for a Photovoltaic DC–DC Converter. IEEE Trans. Power Electron. 2013, 28, 3008–3018. [Google Scholar] [CrossRef]

- Sheng, H.; Wang, F.; Tipton IV, C.W. A Fault Detection and Protection Scheme for Three-Level DC–DC Converters Based on Monitoring Flying Capacitor Voltage. IEEE Trans. Power Electron. 2012, 27, 685–697. [Google Scholar] [CrossRef]

- Bi, K.; An, Q.; Duan, J.; Sun, L.; Gai, K. Fast Diagnostic Method of Open Circuit Fault for Modular Multilevel DC/DC Converter Applied in Energy Storage System. IEEE Trans. Power Electron. 2017, 32, 3292–3296. [Google Scholar] [CrossRef]

- Chen, Y.; Pei, X.; Nie, S.; Kang, Y. Monitoring and Diagnosis for the DC–DC Converter Using the Magnetic Near Field Waveform. IEEE Trans. Ind. Electron. 2011, 58, 1634–1647. [Google Scholar] [CrossRef]

- Li, P.; Li, X.; Zeng, T. A Fast and Simple Fault Diagnosis Method for Interleaved DC-DC Converters Based on Output Voltage Analysis. Electronics 2021, 10, 1451. [Google Scholar] [CrossRef]

- Li, C.; Yu, Y.; Yang, Z.; Wang, W.; Peng, X. A Sensorless Open-Circuit Fault Identification Method for Interleaved Boost Converter. IEEE Trans. Instrum. Meas. 2024, 73, 3525508. [Google Scholar] [CrossRef]

- Nie, S.; Pei, X.; Chen, Y.; Kang, Y. Fault Diagnosis of PWM DC–DC Converters Based on Magnetic Component Voltages Equation. IEEE Trans. Power Electron. 2014, 29, 4978–4998. [Google Scholar] [CrossRef]

- Givi, H.; Farjah, E.; Ghanbari, T. A Comprehensive Monitoring System for Online Fault Diagnosis and Aging Detection of Non-Isolated DC–DC Converters’ Components. IEEE Trans. Power Electron. 2019, 34, 6858–6875. [Google Scholar] [CrossRef]

- Givi, H.; Farjah, E.; Ghanbari, T. Switch and Diode Fault Diagnosis in Non-Isolated DC–DC Converters Using Diode Voltage Signature. IEEE Trans. Ind. Electron. 2018, 65, 1606–1615. [Google Scholar] [CrossRef]

- Ahmad, M.W.; Gorla, N.B.Y.; Malik, H.; Panda, S.K. A Fault Diagnosis and Postfault Reconfiguration Scheme for Interleaved Boost Converter in PV-Based System. IEEE Trans. Power Electron. 2021, 36, 3769–3780. [Google Scholar] [CrossRef]

- Wang, Y.; Guan, Y.; Molinas, M.; Fosso, O.B.; Hu, W.; Zhang, Y. Open-Circuit Switching Fault Analysis and Tolerant Strategy for Dual-Active-Bridge DC–DC Converter Considering Parasitic Parameters. IEEE Trans. Power Electron. 2022, 37, 15020–15034. [Google Scholar] [CrossRef]

- Rastogi, S.K.; Shah, S.S.; Singh, B.N.; Bhattacharya, S. Vector-Based Open-Circuit Fault Diagnosis Technique for a Three-Phase DAB Converter. IEEE Trans. Ind. Electron. 2024, 71, 8207–8211. [Google Scholar] [CrossRef]

- Mahdavi, M.S.; Karimzadeh, M.S.; Rahimi, T.; Gharehpetian, G.B. A Fault-Tolerant Bidirectional Converter for Battery Energy Storage Systems in DC Microgrids. Electronics 2023, 12, 679. [Google Scholar] [CrossRef]

- Han, W.; Cheng, L.; Han, W.; Yu, C.; Hao, Z.; Yin, Z. Soft Fault Diagnosis for DC–DC Converter Based on Improved ResNet-50. IEEE Access 2023, 11, 81157–81168. [Google Scholar] [CrossRef]

- Espinoza-Trejo, D.R.; Castro, L.M.; Bárcenas, E.; Sánchez, J.P. Data-Driven Switch Fault Diagnosis for DC/DC Boost Converters in Photovoltaic Applications. IEEE Trans. Ind. Electron. 2024, 71, 1631–1640. [Google Scholar] [CrossRef]

- Hang, J.; Ge, C.; Ding, S.; Li, W.; Huang, Y.; Hua, W. A Global State Observer-Based Open-Switch Fault Diagnosis for Bidirectional DC–DC Converters in Hybrid Energy Source System. IEEE Trans. Power Electron. 2023, 38, 13085–13098. [Google Scholar] [CrossRef]

- Ding, S.; Tang, D.; Hang, J.; Zhao, J.; Gui, S. Robust Open-Switch Fault Diagnosis of Bidirectional DC/DC Converters Based on Extended Kalman Filter With Multiple Corrections. IEEE Trans. Circuits Syst. Regul. Pap. 2024, 71, 4363–4374. [Google Scholar] [CrossRef]

- Rastogi, S.K.; Shah, S.S.; Singh, B.N.; Bhattacharya, S. Mode Analysis, Transformer Saturation, and Fault Diagnosis Technique for an Open-Circuit Fault in a Three-Phase DAB Converter. IEEE Trans. Power Electron. 2023, 38, 7644–7660. [Google Scholar] [CrossRef]

- Yang, W.; Ma, J.; Zhu, M.; Hu, C. Open-Circuit Fault Diagnosis and Tolerant Method of Multiport Triple Active-Bridge DC-DC Converter. IEEE Trans. Ind. Appl. 2023, 59, 5473–5487. [Google Scholar] [CrossRef]

- Wassinger, N.; Penovi, E.; Retegui, R.G.; Maestri, S. Open-Circuit Fault Identification Method for Interleaved Converters Based on Time-Domain Analysis of the State Observer Residual. IEEE Trans. Power Electron. 2019, 34, 3740–3749. [Google Scholar] [CrossRef]

- Poon, J.; Jain, P.; Konstantakopoulos, I.C.; Spanos, C.; Panda, S.K.; Sanders, S.R. Model-Based Fault Detection and Identification for Switching Power Converters. IEEE Trans. Power Electron. 2017, 32, 1419–1430. [Google Scholar] [CrossRef]

- Zhuo, S.; Gaillard, A.; Xu, L.; Liu, C.; Paire, D.; Gao, F. An Observer-Based Switch Open-Circuit Fault Diagnosis of DC-DC Converter for Fuel Cell Application. IEEE Trans. Ind. Appl. 2020, 56, 3159–3167. [Google Scholar] [CrossRef]

- Jain, P.; Jian, L.; Poon, J.; Spanos, C.; Sanders, S.R.; Xu, J.-X.; Panda, S.K. A Luenberger Observer-Based Fault Detection and Identification Scheme for Photovoltaic DC-DC Converters. In Proceedings of the IECON 2017—43rd Annual Conference of the IEEE Industrial Electronics Society, Beijing, China, 1 October 2017; pp. 5015–5020. [Google Scholar]

- Zhuo, S.; Xu, L.; Gaillard, A.; Huangfu, Y.; Paire, D.; Gao, F. Robust Open-Circuit Fault Diagnosis of Multi-Phase Floating Interleaved DC–DC Boost Converter Based on Sliding Mode Observer. IEEE Trans. Transp. Electrif. 2019, 5, 638–649. [Google Scholar] [CrossRef]

- Xu, L.; Ma, R.; Xie, R.; Xu, J.; Huangfu, Y.; Gao, F. Open-Circuit Switch Fault Diagnosis and Fault-Tolerant Control for Output-Series Interleaved Boost DC–DC Converter. IEEE Trans. Transp. Electrif. 2021, 7, 2054–2066. [Google Scholar] [CrossRef]

- Su, Q.; Wang, Z.; Xu, J.; Li, C.; Li, J. Fault Detection for DC-DC Converters Using Adaptive Parameter Identification. J. Frankl. Inst. 2022, 359, 5778–5797. [Google Scholar] [CrossRef]

- Poon, J.; Jain, P.; Spanos, C.; Panda, S.K.; Sanders, S.R. Fault Prognosis for Power Electronics Systems Using Adaptive Parameter Identification. IEEE Trans. Ind. Appl. 2017, 53, 2862–2870. [Google Scholar] [CrossRef]

- Pazouki, E.; De Abreu-Garcia, J.A.; Sozer, Y. Short Circuit Fault Diagnosis for Interleaved DC–DC Converter Using DC-Link Current Emulator. In Proceedings of the 2017 IEEE Applied Power Electronics Conference and Exposition (APEC), Tampa, FL, USA, 26–30 March 2017; pp. 230–236. [Google Scholar]

- Pazouki, E.; Sozer, Y.; De Abreu-Garcia, J.A. Fault Diagnosis and Fault Tolerant Operation of Non-Isolated DC–DC Converter. IEEE Trans. Ind. Appl. 2018, 54, 310–320. [Google Scholar] [CrossRef]

- Jain, P.; Poon, J.; Singh, J.P.; Spanos, C.; Sanders, S.R.; Panda, S.K. A Digital Twin Approach for Fault Diagnosis in Distributed Photovoltaic Systems. IEEE Trans. Power Electron. 2020, 35, 940–956. [Google Scholar] [CrossRef]

- Jiang, Y.; Xia, L.; Zhang, J. A Fault Feature Extraction Method for DC–DC Converters Based on Automatic Hyperparameter-Optimized 1-D Convolution and Long Short-Term Memory Neural Networks. IEEE J. Emerg. Sel. Top. Power Electron. 2022, 10, 4703–4714. [Google Scholar] [CrossRef]

- Ren, T.; Han, T.; Guo, Q.; Li, G. Analysis of Interpretability and Generalizability for Power Converter Fault Diagnosis Based on Temporal Convolutional Networks. IEEE Trans. Instrum. Meas. 2023, 72, 3518511. [Google Scholar] [CrossRef]

- Liu, Y.; Zhang, G.; Miao, J.; Zhao, Z.; Yin, Q.; Zhao, J. Fault Diagnosis of DC/DC Buck Converter for Embedded Applications Based on BO-ELM. IEEE Trans. Ind. Electron. 2024, 71, 15034–15043. [Google Scholar] [CrossRef]

- Jia, Z.; Liu, Z.; Vong, C.-M.; Wang, S.; Cai, Y. DC-DC Buck Circuit Fault Diagnosis with Insufficient State Data Based on Deep Model and Transfer Strategy. Expert Syst. Appl. 2023, 213, 118918. [Google Scholar] [CrossRef]

- Miao, J.; Liu, Y.; Yin, Q.; Ju, B.; Zhang, G.; Wang, H. A Novel Soft Fault Detection and Diagnosis Method for a DC/DC Buck Converter Based on Contrastive Learning. IEEE Trans. Power Electron. 2024, 39, 1501–1513. [Google Scholar] [CrossRef]

- Ni, L.; Patterson, D.J.; Hudgins, J.L. High Power Current Sensorless Bidirectional 16-Phase Interleaved DC–DC Converter for Hybrid Vehicle Application. IEEE Trans. Power Electron. 2012, 27, 1141–1151. [Google Scholar] [CrossRef]

| D | DM | q1d State Transition | , Healthy | , Faulty |

|---|---|---|---|---|

| OFF → ON | ||||

| ON → OFF | ||||

(BCM and CCM) | OFF → ON | |||

| ON → OFF | ||||

| OFF → ON | ||||

| ON → OFF | ||||

| OFF → ON | ||||

| ON → OFF | ||||

| OFF → ON | ||||

| ON → OFF | ||||

(BCM and CCM) | OFF → ON | |||

| ON → OFF | ||||

| OFF → ON | ||||

| ON → OFF | ||||

| OFF → ON | ||||

| ON → OFF | ||||

(BCM and CCM) | OFF → ON | |||

| ON → OFF | ||||

| OFF → ON | ||||

| ON → OFF | ||||

| OFF → ON | ||||

| ON → OFF | ||||

(BCM and CCM) | OFF → ON | |||

| ON → OFF | ||||

| OFF → ON | ||||

| ON → OFF | ||||

(BCM and CCM) | OFF → ON | |||

| ON → OFF | ||||

| OFF → ON | ||||

| ON → OFF |

| D | DM | q1u State Transition | , Healthy | , Faulty |

|---|---|---|---|---|

| OFF → ON | ||||

| ON → OFF | ||||

(BCM and CCM) | OFF → ON | |||

| ON → OFF | ||||

| OFF → ON | ||||

| ON → OFF | ||||

| OFF → ON | ||||

| ON → OFF | ||||

| OFF → ON | ||||

| ON → OFF | ||||

(BCM and CCM) | OFF → ON | |||

| ON → OFF | ||||

| OFF → ON | ||||

| ON → OFF | ||||

| OFF → ON | ||||

| ON → OFF | ||||

(BCM and CCM) | OFF → ON | |||

| ON → OFF | ||||

| OFF → ON | ||||

| ON → OFF | ||||

| OFF → ON | ||||

| ON → OFF | ||||

(BCM and CCM) | OFF → ON | |||

| ON → OFF | ||||

| OFF → ON | ||||

| ON → OFF | ||||

(BCM and CCM) | OFF → ON | |||

| ON → OFF | ||||

| OFF → ON | ||||

| ON → OFF |

| Left-side voltage (VL) | 48 V |

| Right-side voltage (VH) | {70, 90} V |

| Inductance (Li) | {4, 10} mH |

| Output capacitance (CH) | 680 μF |

| Load resistance (RL) | {50, 100} Ω |

| Switching frequency (fsw) | {2.5, 5} kHz |

| Simulation sampling time (Ts) | 5 μs |

| Ref. | Target Converter Topologies | Diagnostic Variable | fsw(1) | Ts(2) | td_max(3) | td_max/Ts(4) |

|---|---|---|---|---|---|---|

| [17] | DC-DC converters for PV applications | PV variables | 5 kHz | 50 μs | 250 ms | 5000 |

| [6] | Interleaved boost converter | Input current derivative sign | 1 kHz | 25 μs, 50 μs | 2 Tsw (5) (2 ms) | 40 |

| [44,45] | Non-isolated DC-DC converters | Inductor current emulation | {10, 20} kHz | 10 μs | Tsw (100 μs, 50 μs) | 5 |

| [37] | Switching power converters | State estimation | 10 to 20 kHz | 100 μs | 10 ms | 100 |

| [43] | Interleaved boost converters | Parameter identification | 10 kHz | 10 μs | Tsw (100 μs) | 10 |

| [13] | Interleaved boost converters | Input current slope | {1, 3, 5} kHz | 20 μs | 2 Tsw (400 μs) | 20 |

| [11] | Interleaved boost converters | Input current sampling | 20 kHz | 16.7 μs | 2 Tsw (100 μs) | 6 |

| [24,25] | Non-isolated DC-DC converters | Diode voltage monitoring | 50 kHz | - | Tsw (20 μs) | - |

| [39] | Boost converters | Luenberger observer | 10 kHz | 10 μs | Tsw (100 μs) | 10 |

| [36] | Interleaved buck converters | State observer | 25 kHz | 0.67 μs | 2 Tsw (80 μs) | 119.4 |

| [41] | IPOS boost converters | I&I observer for input voltage | 25 kHz | 20 μs | 2 Tsw (80 μs) | 4 |

| [46] | Four-switch buck-boost converter | Digital twin | 50 kHz | 2 μs | 201 Tsw (4.03 ms) | 2015 |

| Proposed | Bidirectional interleaved converters | Second-order current derivative | {2.5, 5} kHz | 20 μs | Tsw (200 μs) | 10 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Bento, F.; Cardoso, A.J.M. Diagnosis of DC-DC Converter Semiconductor Faults Based on the Second-Order Derivative of the Converter Input Current. Electronics 2024, 13, 3778. https://doi.org/10.3390/electronics13183778

Bento F, Cardoso AJM. Diagnosis of DC-DC Converter Semiconductor Faults Based on the Second-Order Derivative of the Converter Input Current. Electronics. 2024; 13(18):3778. https://doi.org/10.3390/electronics13183778

Chicago/Turabian StyleBento, Fernando, and Antonio J. Marques Cardoso. 2024. "Diagnosis of DC-DC Converter Semiconductor Faults Based on the Second-Order Derivative of the Converter Input Current" Electronics 13, no. 18: 3778. https://doi.org/10.3390/electronics13183778