An 88 dB SNDR 100 kHz BW Sturdy MASH Delta-Sigma Modulator Using Self-Cascoded Floating Inverter Amplifiers

Abstract

:1. Introduction

1.1. Background

1.2. Literature Review

1.3. Contributions

2. Proposed DT DSM Architecture

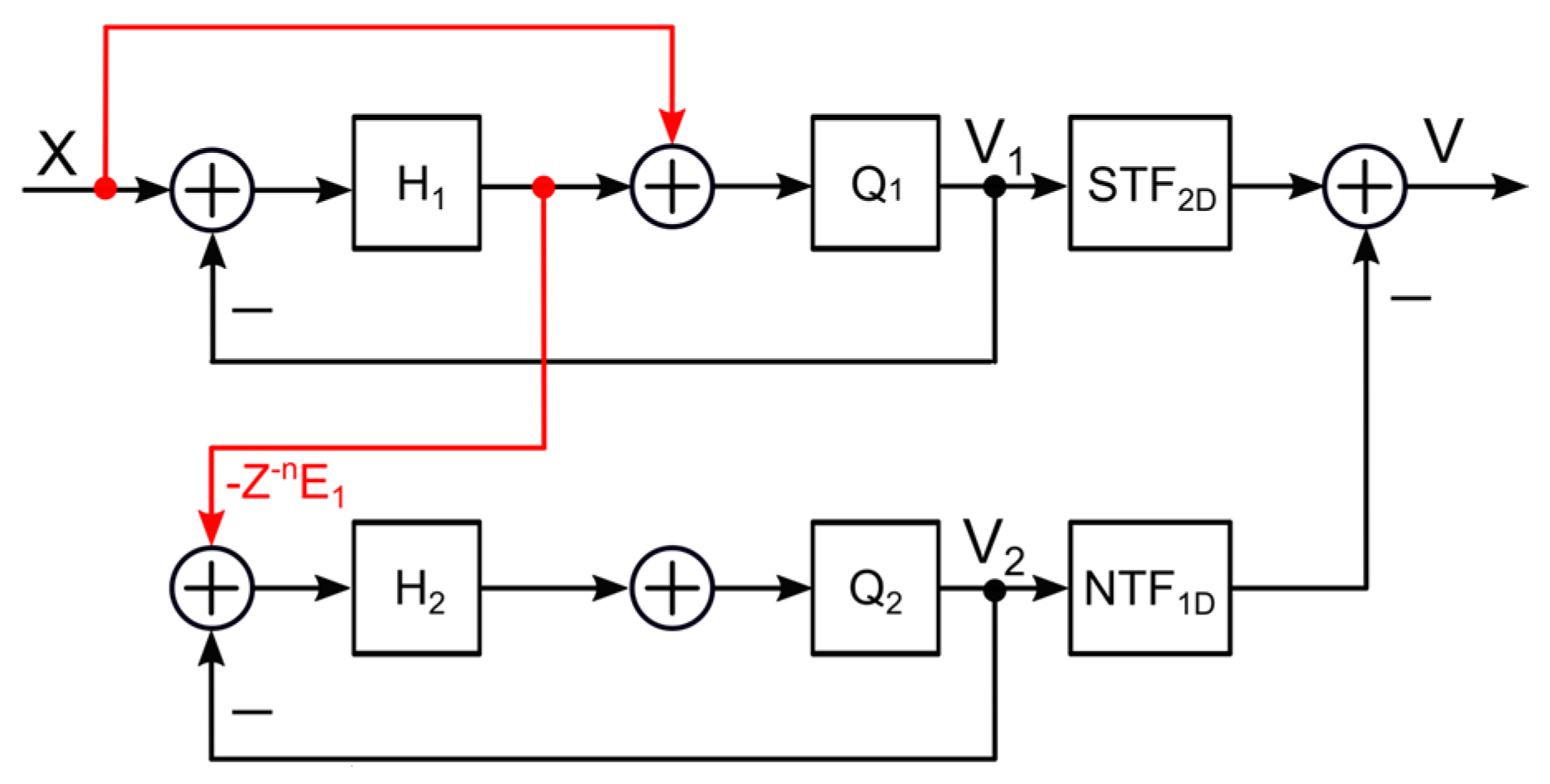

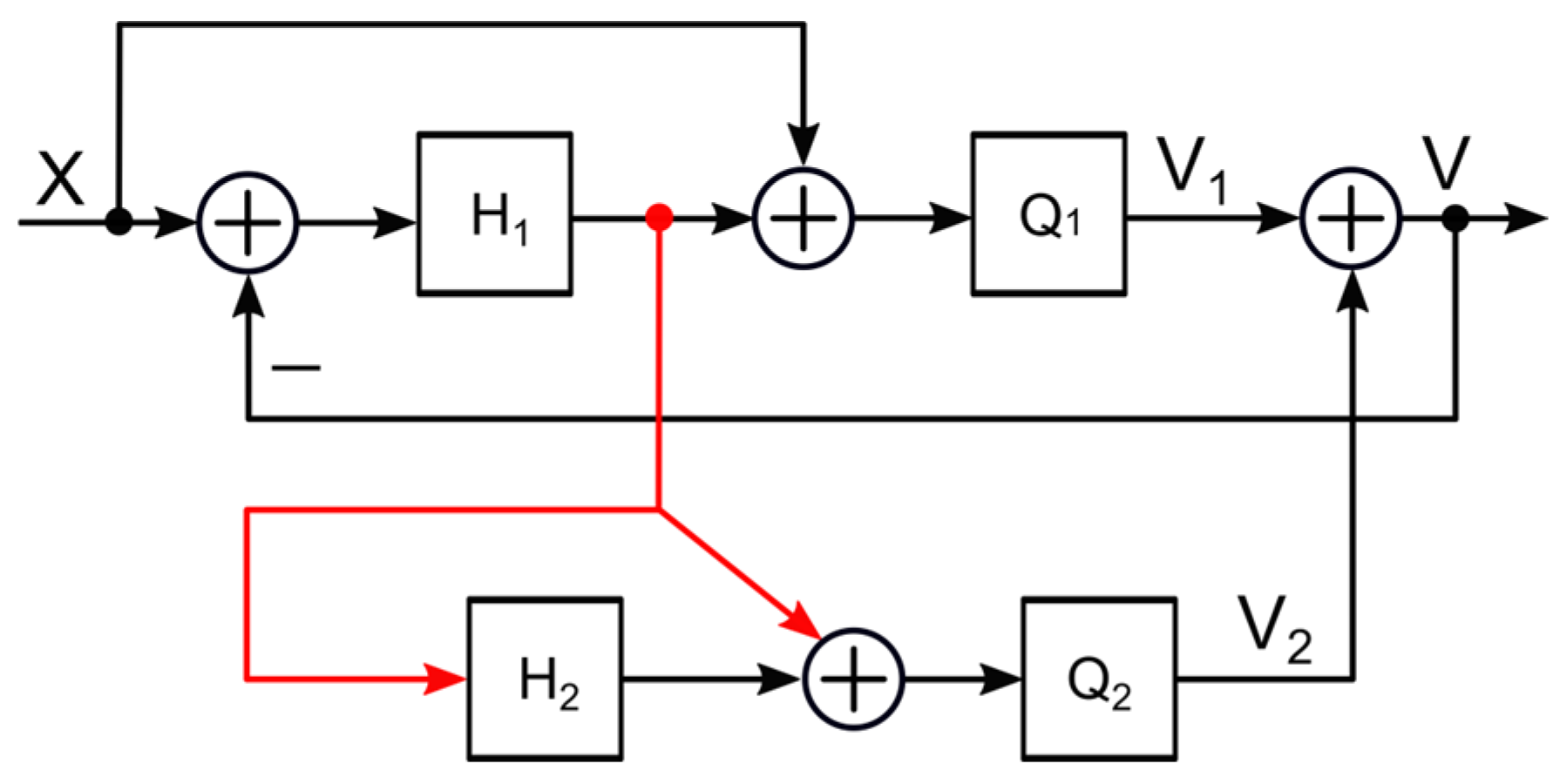

2.1. Overview of MASH and SMASH DSMs

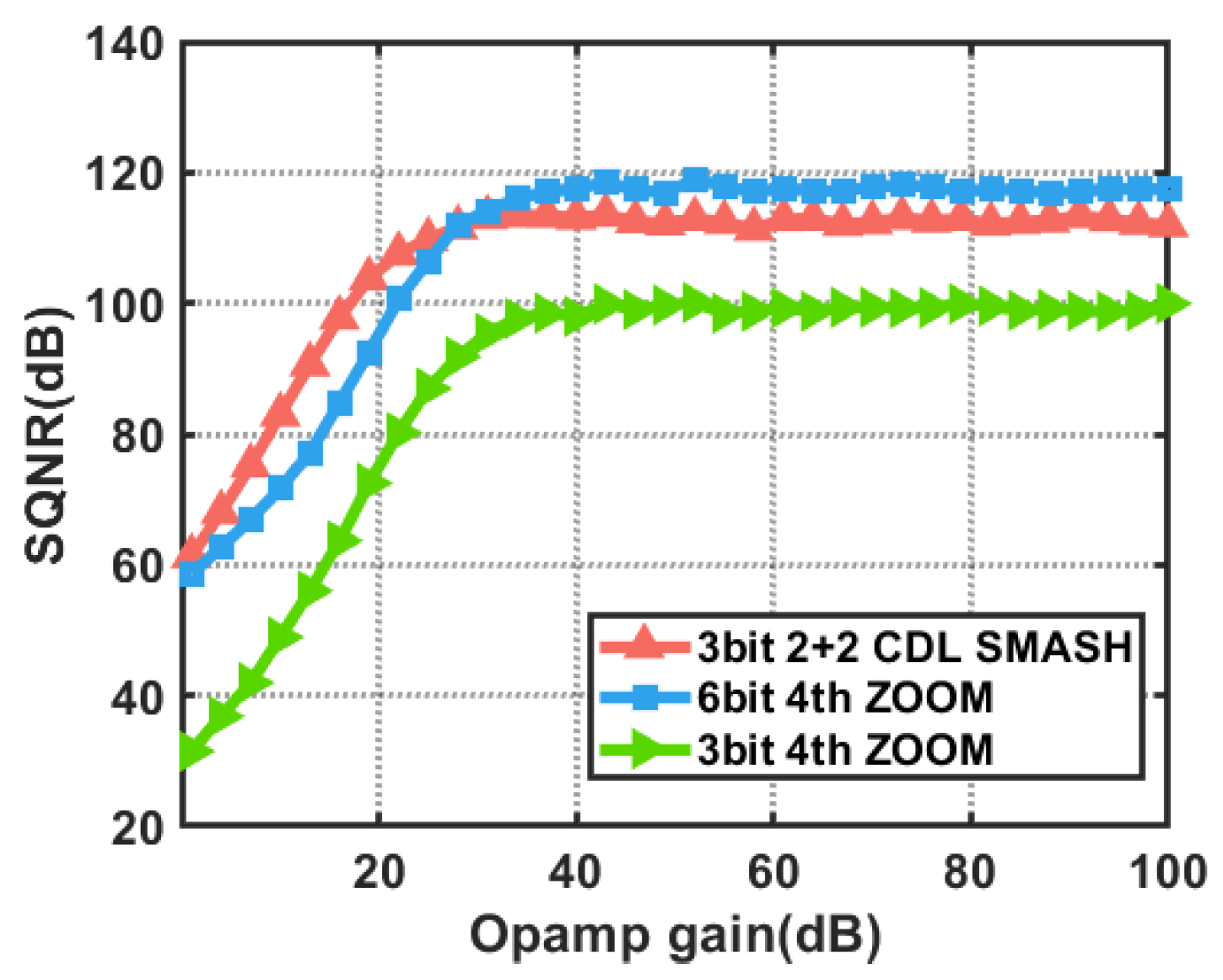

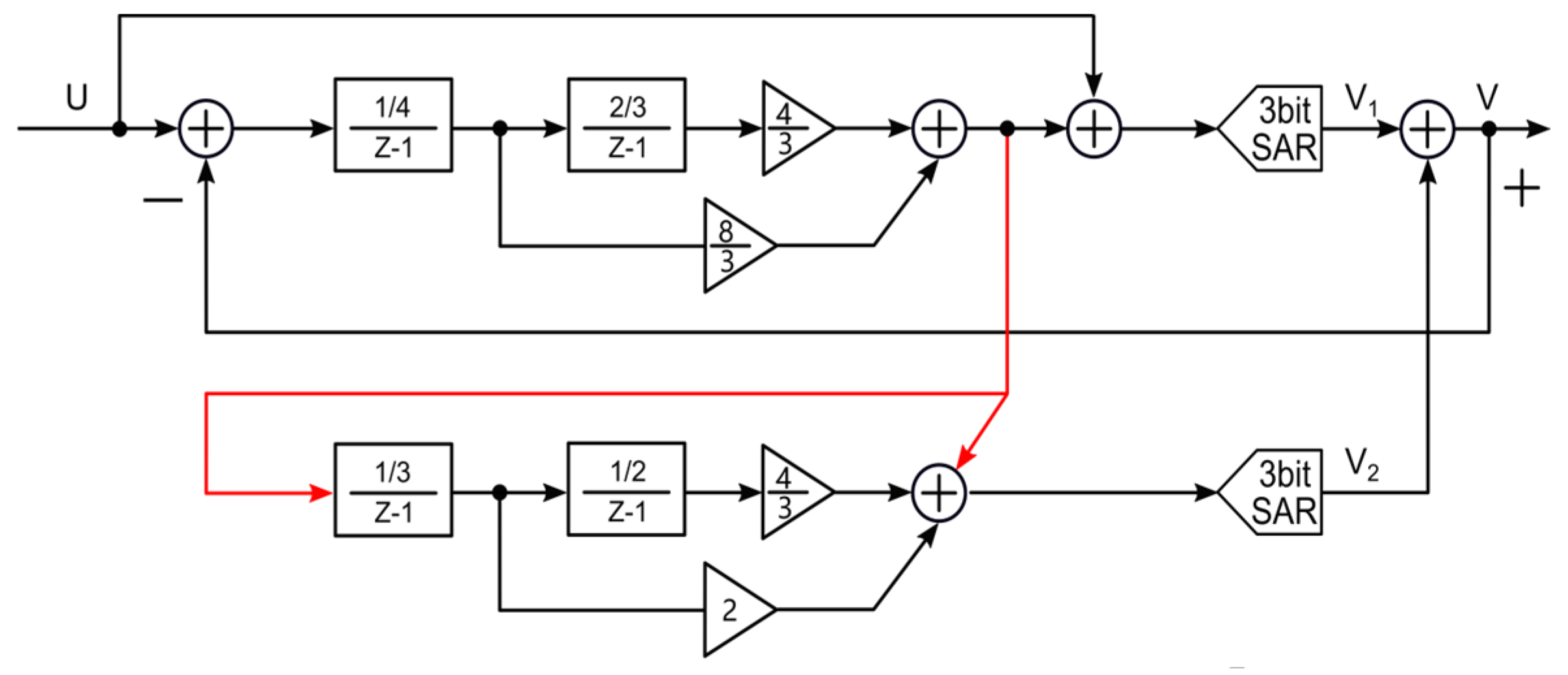

2.2. CDL SMASH DSMs

3. Circuit Implementation

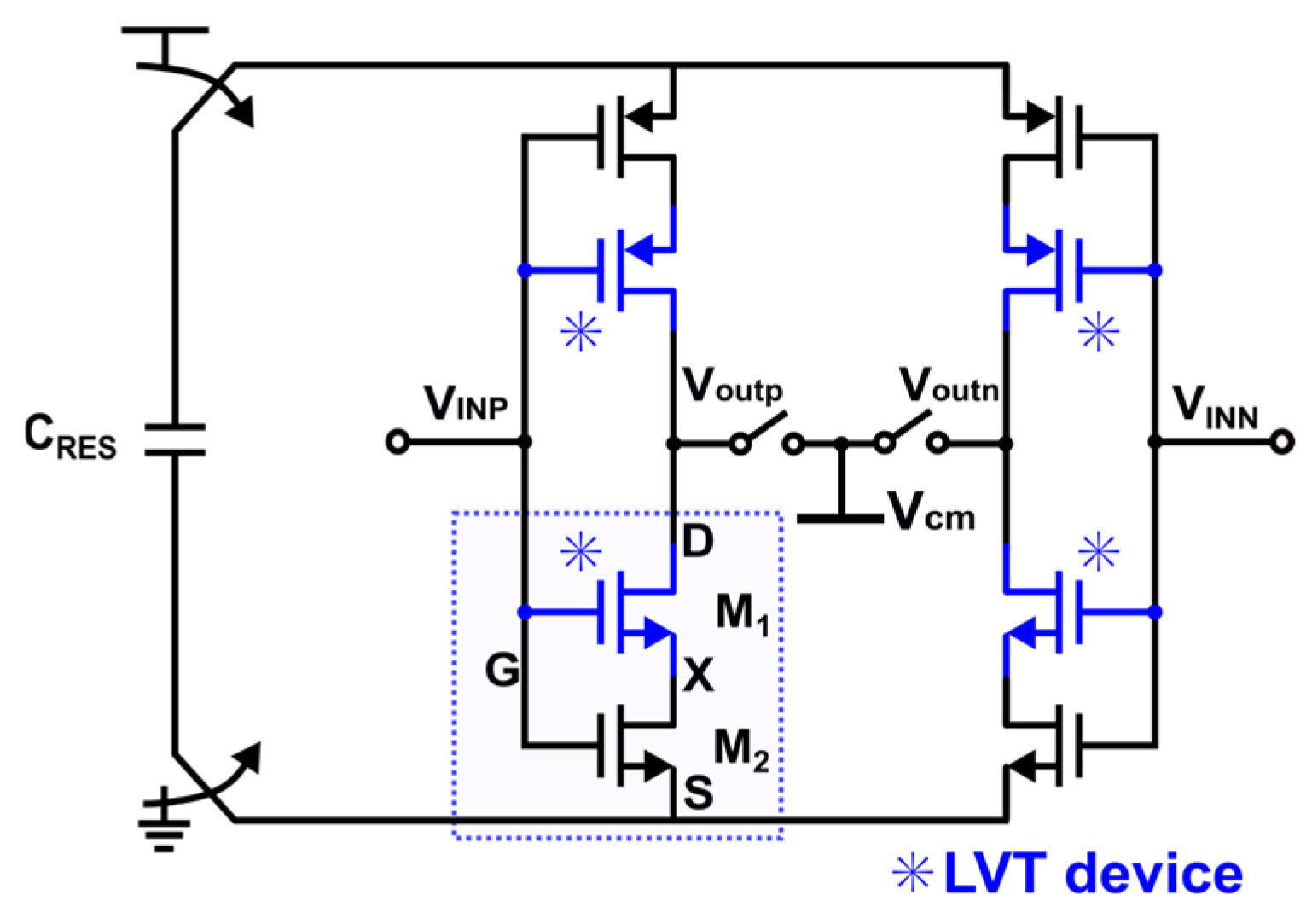

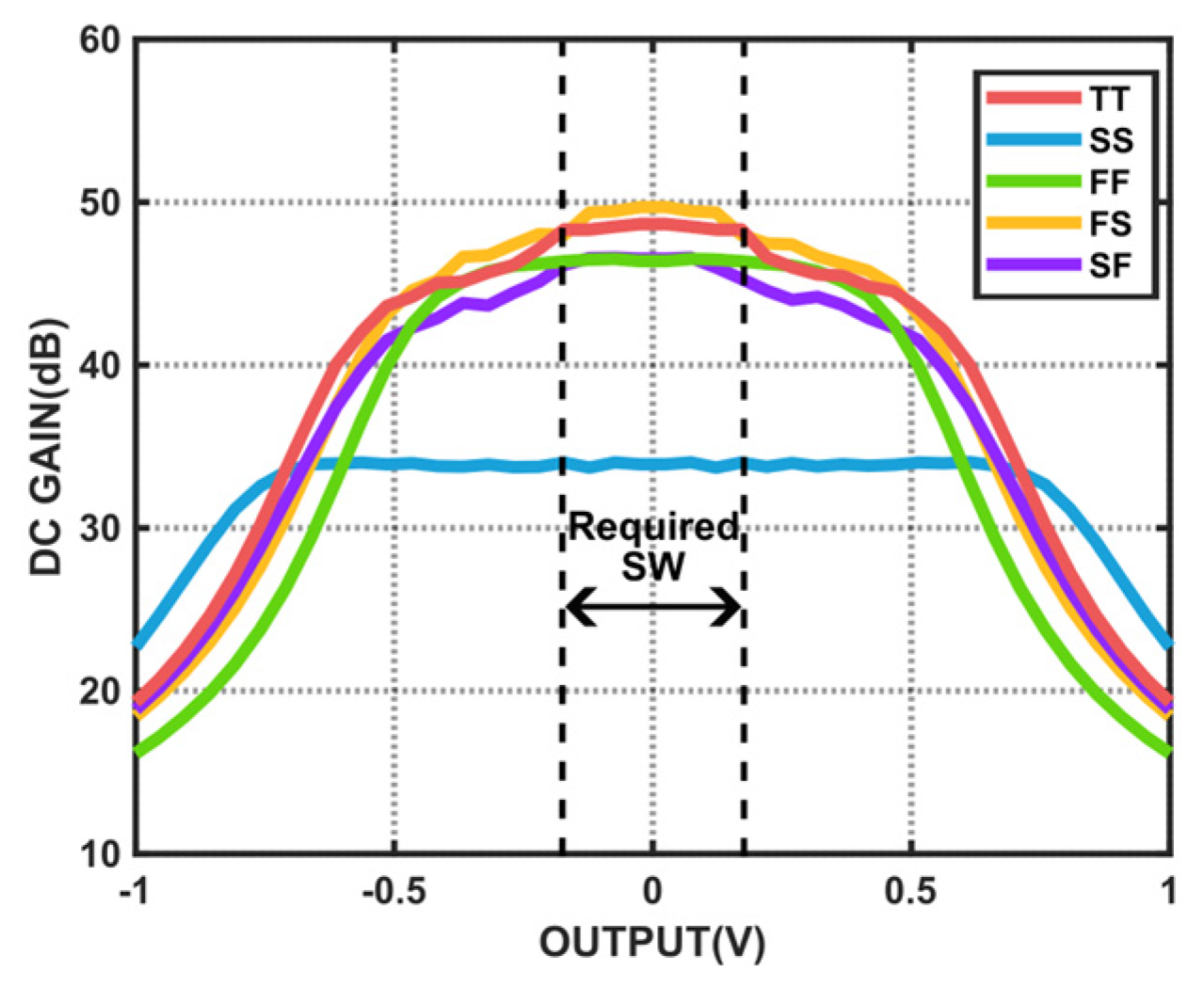

3.1. The Proposed Self-Cascoded FIA

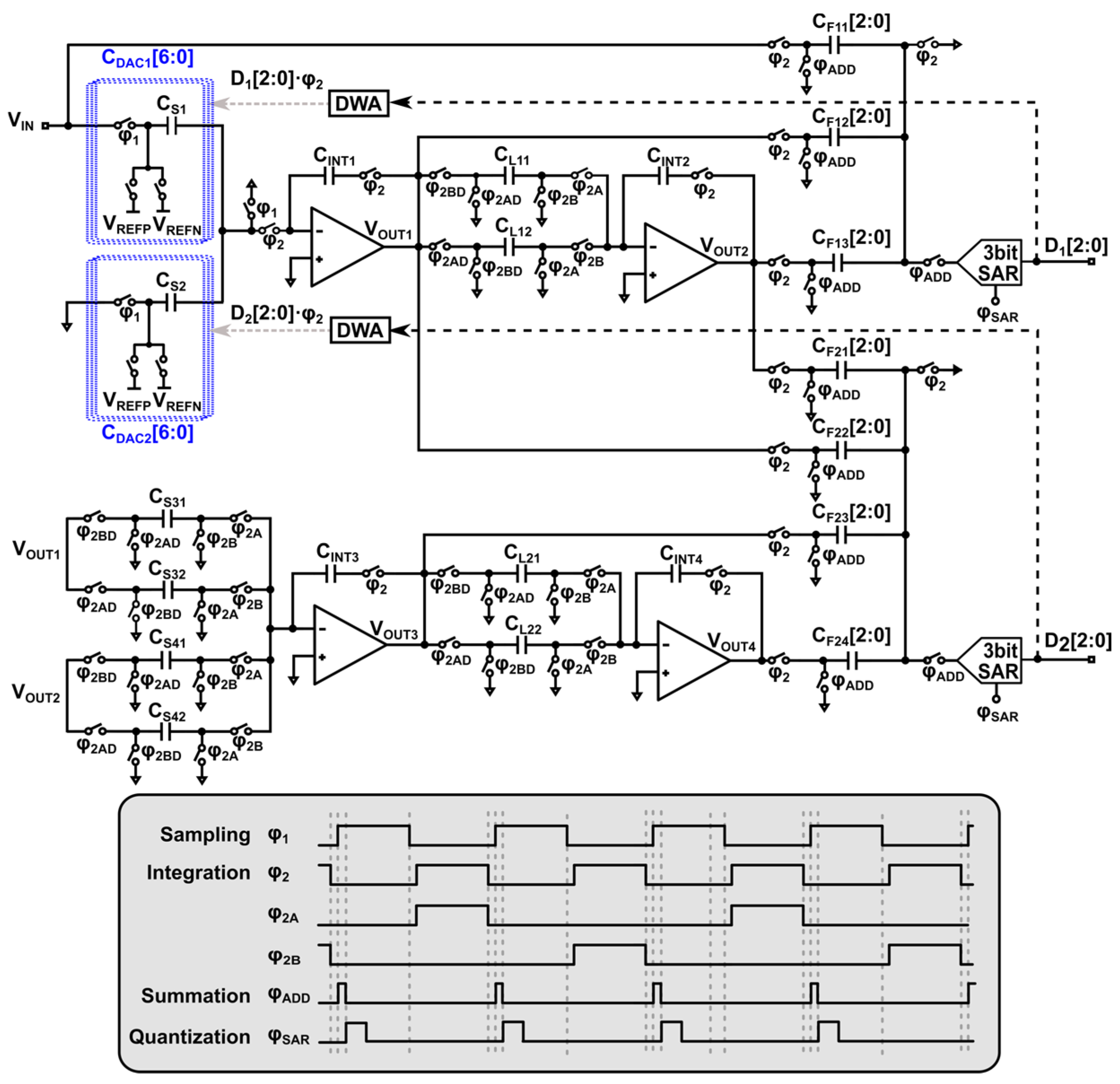

3.2. 2+2 DT SMASH DSM Implementation

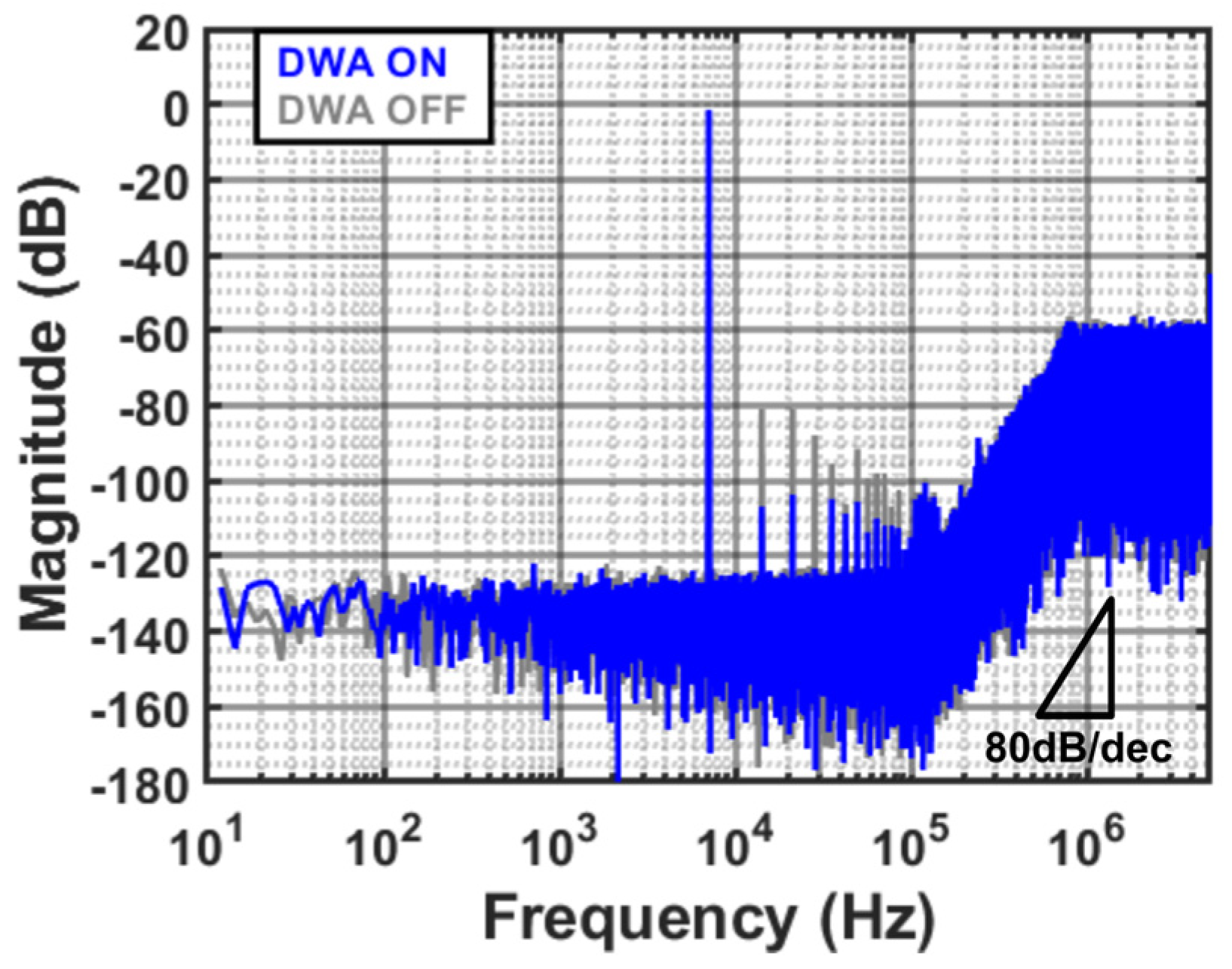

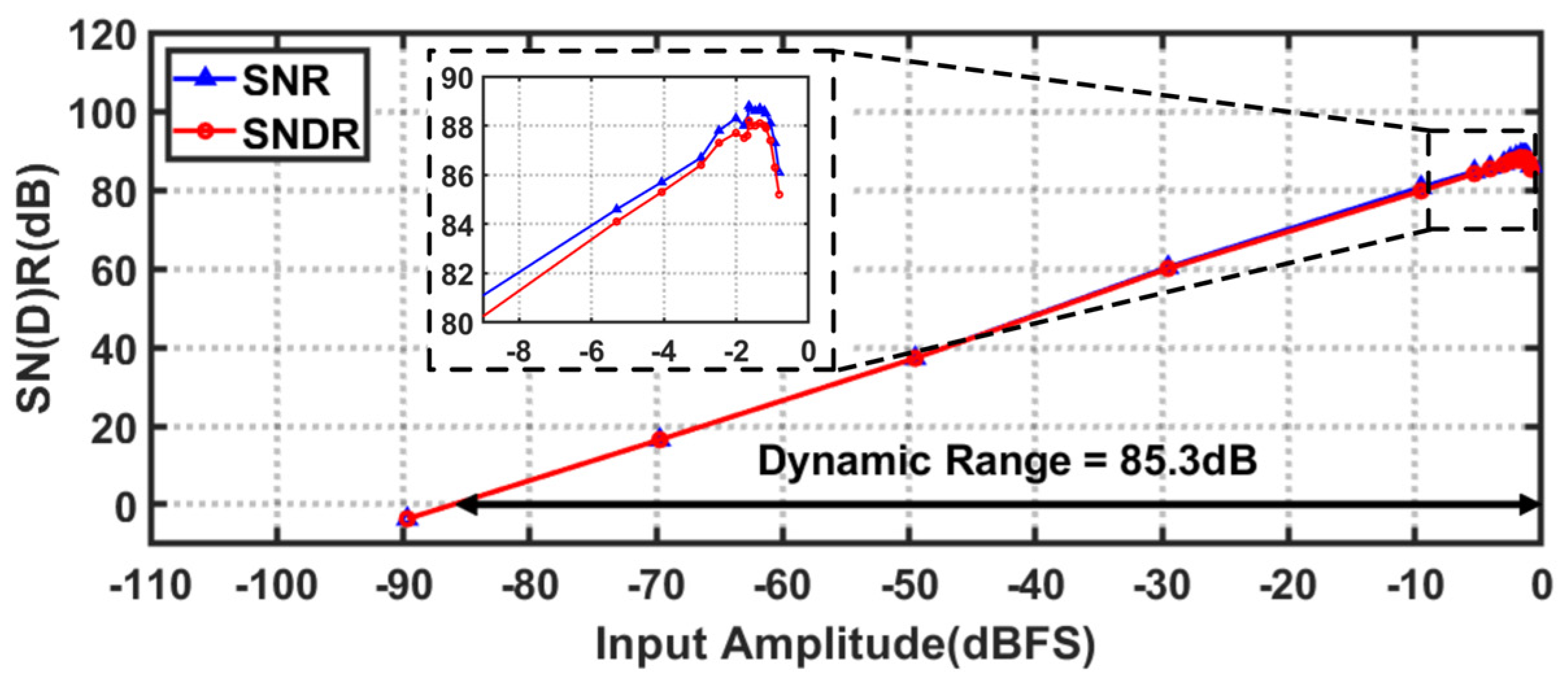

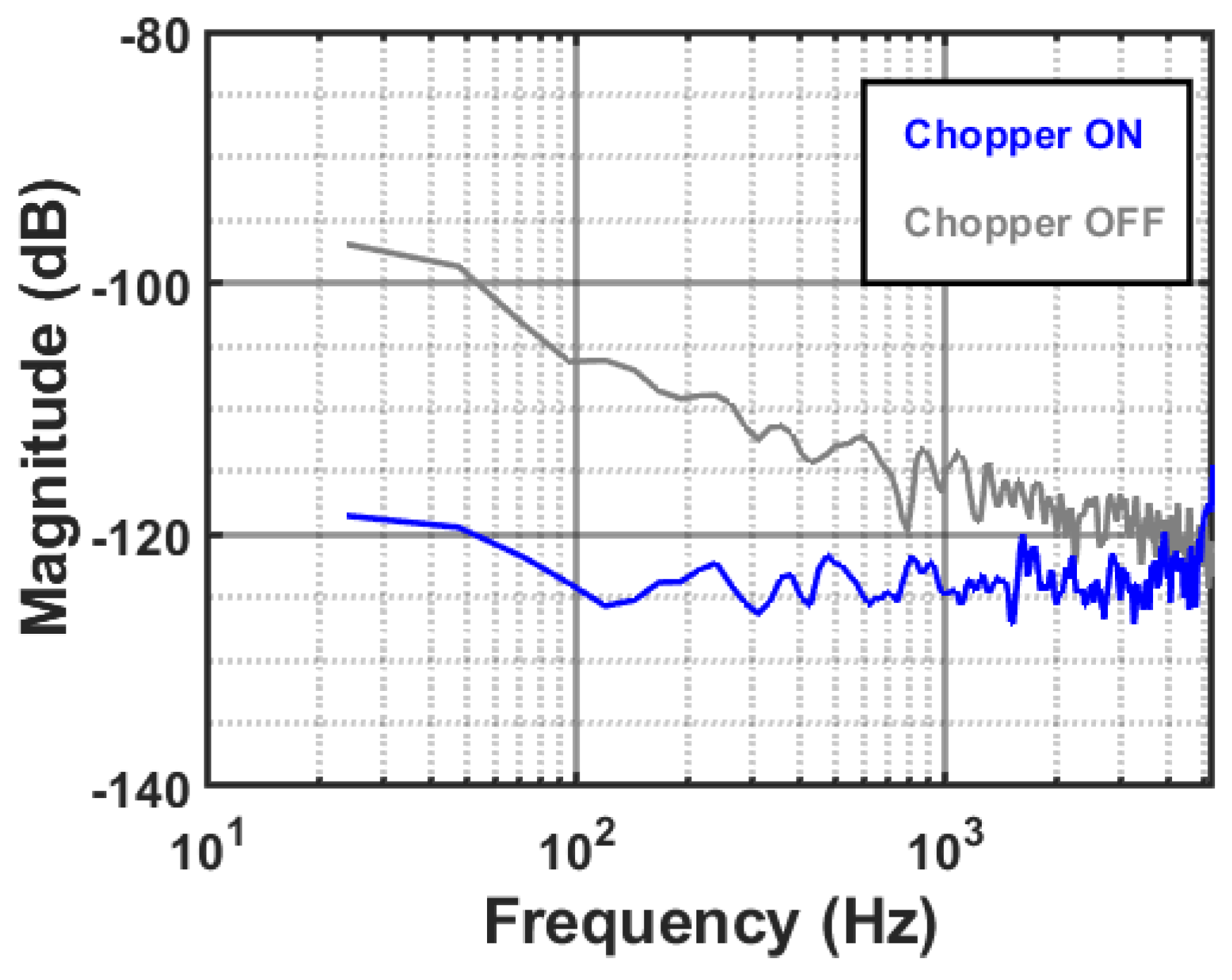

4. Measurement Results

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Schreier, R.; Temes, G.C. Understanding Delta Sigma Data Converters; IEEE Press: New York, NY, USA, 2005. [Google Scholar]

- Kwak, Y.-S.; Cho, K.-I.; Kim, H.-J.; Lee, S.-H.; Ahn, G.-C. A 72.9-dB SNDR 20-MHz BW 2-2 Discrete-Time Resolution-Enhanced Sturdy MASH Delta–Sigma Modulator Using Source-Follower-Based Integrators. IEEE J. Solid-State Circuits 2018, 53, 2772–2782. [Google Scholar] [CrossRef]

- Bos, L.; Vandersteen, G.; Rombouts, P.; Geis, A.; Morgado, A.; Rolain, Y.; Van der Plas, G. Multirate Cascaded Discrete-Time Low-Pass ΔΣ Modulator for GSM/Bluetooth/UMTS. IEEE J. Solid-State Circuits 2010, 45, 1198–1208. [Google Scholar] [CrossRef]

- Maghari, N.; Kwon, S.; Moon, U.-K. 74 dB SNDR Multi-Loop Sturdy-MASH Delta-Sigma Modulator Using 35 dB Open-Loop Opamp Gain. IEEE J. Solid-State Circuits 2009, 44, 2212–2221. [Google Scholar] [CrossRef]

- Yoon, D.-Y.; Ho, S.; Lee, H.-S. A Continuous-Time Sturdy-MASH ΔΣ Modulator in 28 nm CMOS. IEEE J. Solid-State Circuits 2015, 50, 2880–2890. [Google Scholar] [CrossRef]

- Park, B.; Han, C.; Maghari, N. Correlated Dual-Loop Sturdy MASH CT ΔΣ ADC with Indirect Signal Feedforward. In Proceedings of the 2021 IEEE Asian Solid-State Circuits Conference (A-SSCC), Busan, Republic of Korea, 7–10 November 2021. [Google Scholar]

- Breems, L.J. A cascaded continuous-time Sigma Delta modulator with 67dB dynamic range in 10MHz bandwidth. In Proceedings of the 2004 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 15–19 February 2004. [Google Scholar]

- Tang, X.; Yang, X.; Zhao, W.; Hsu, C.; Liu, J.; Shen, L.; Mukherjee, A.; Shi, W.; Li, S.; Pan, D.Z.; et al. A 13.5-ENOB, 107-μW Noise-Shaping SAR ADC With PVT-Robust Closed-Loop Dynamic Amplifier. IEEE J. Solid-State Circuits 2020, 55, 3248–3259. [Google Scholar] [CrossRef]

- Tang, X.; Yang, X.; Liu, J.; Wang, Z.; Shi, W.; Pan, D.Z.; Sun, N. A Bandwidth-Adaptive Pipelined SAR ADC with Three-Stage Cascoded Floating Inverter Amplifier. IEEE J. Solid-State Circuits 2023, 58, 2564–2574. [Google Scholar] [CrossRef]

- Meng, L.; Chen, J.; Zhao, M.; Tan, Z. A 1.2-V 2.87-μ W 94.0-dB SNDR Discrete-Time 2–0 MASH Delta-Sigma ADC. IEEE J. Solid-State Circuits 2023, 58, 1636–1645. [Google Scholar] [CrossRef]

- Kumar, R.S.A.; Krishnapura, N.; Banerjee, P. Analysis and Design of a Discrete-Time Delta-Sigma Modulator Using a Cascoded Floating-Inverter-Based Dynamic Amplifier. IEEE J. Solid-State Circuits 2022, 57, 3384–3395. [Google Scholar] [CrossRef]

- Park, B.; Han, C.; Maghari, N. Correlated Dual-Loop Sturdy MASH Continuous-Time Delta-Sigma Modulators. IEEE J. Solid-State Circuits 2022, 57, 2934–2943. [Google Scholar] [CrossRef]

- Qin, X.; Zhang, J.; Qi, L.; Sin, S.-W.; Martins, R.P.; Wang, G. Discrete-Time MASH Delta-Sigma Modulator with Second-Order Digital Noise Coupling for Wideband High-Resolution Applications. In Proceedings of the 2021 IEEE International Symposium on Circuits and Systems (ISCAS), Daegu, Republic of Korea, 23–26 May 2021. [Google Scholar]

- Gönen, B.; Sebastiano, F.; Quan, R.; van Veldhoven, R.; Makinwa, K.A.A. A Dynamic Zoom ADC with 109-dB DR for Audio Applications. IEEE J. Solid-State Circuits 2017, 52, 1542–1550. [Google Scholar] [CrossRef]

- Eland, E.; Karmakar, S.; Gönen, B.; van Veldhoven, R.; Makinwa, K.A.A. A 440-μW, 109.8-dB DR, 106.5-dB SNDR Discrete-Time Zoom ADC with a 20-kHz BW. IEEE J. Solid-State Circuits 2021, 56, 1207–1215. [Google Scholar] [CrossRef]

- Gönen, B.; Karmakar, S.; van Veldhoven, R.; Makinwa, K.A.A. A Continuous-Time Zoom ADC for Low-Power Audio Applications. IEEE J. Solid-State Circuits 2020, 55, 1023–1031. [Google Scholar] [CrossRef]

- Karmakar, S.; Gönen, B.; Sebastiano, F.; van Veldhoven, R.; Makinwa, K.A.A. A 280μW Dynamic Zoom ADC with 120 dB DR and 118 dB SNDR in 1 kHz BW. IEEE J. Solid-State Circuits 2018, 53, 3497–3507. [Google Scholar] [CrossRef]

- Li, H.; Shen, Y.; Cantatore, E.; Harpe, P. A 77.3-dB SNDR 62.5-kHz Bandwidth Continuous-Time Noise-Shaping SAR ADC with Duty-Cycled Gm-C Integrator. IEEE J. Solid-State Circuits 2023, 58, 939–948. [Google Scholar] [CrossRef]

- Vogelmann, P.; Haas, M.; Ortmanns, M. A 1.1mW 200kS/s incremental ΔΣ ADC with a DR of 91.5dB using integrator slicing for dynamic power reduction. In Proceedings of the 2018 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 11–15 February 2018. [Google Scholar]

- Katayama, T.; Miyashita, S.; Sobue, K.; Hamashita, K. A 1.25MS/S Two-Step Incremental ADC with 100DB DR and 110DB SFDR. In Proceedings of the 2018 IEEE Symposium on VLSI Circuits, Honolulu, HI, USA, 18–22 June 2018. [Google Scholar]

- Theertham, R.; Koottala, P.; Billa, S.; Pavan, S. A 24mW Chopped CTDSM Achieving 103.5dB SNDR and 107.5dB DR in a 250kHz Bandwidth. In Proceedings of the 2019 Symposium on VLSI Circuits, Kyoto, Japan, 9–14 June 2019. [Google Scholar]

| Topology | Extraction | Resolution | Num. of DACs | Loop Filter Req. | Gain Req. | |

|---|---|---|---|---|---|---|

| MASH | DT 2-2 | No √ | High | 2 √ | High x | High x |

| SMASH | CT 3-1 [5] | Yes x | High | 3 x | Low √ | Low √ |

| CT 2-2 [6] | No √ | Medium | 2 √ | High x | Low √ | |

| DT 2-2 [4] | Yes x | Medium | 3 x | Low √ | Low √ | |

| Proposed | DT CDL 2-2 | No √ | Medium | 2 √ | Low √ | Low √ |

| [19] | [20] | [21] | [18] | [2] | This Work | |

|---|---|---|---|---|---|---|

| Architecture | Incre- mental | Incre- mental | CTDSM | CT NSSAR | DT SMASH | DT SMASH |

| Shaping order | 3 | - | 4 | 1 | 4 | 4 |

| Technology [nm] | 180 | 180 | 180 | 65 | 65 | 55 |

| Chip area [mm2] | 0.363 | 0.716 | 2.85 | 0.03 | 0.34 | 0.66 |

| Supply [V] | 3 | 3 | 1.8 | 1 | 1.2 | 1.2 |

| Bandwidth [kHz] | 100 | 625 | 250 | 62.5 | 20,000 | 100 |

| OSR | 150 | 44 | 64 | 16 | 12 | 50 |

| SNDR [dB] | 86.6 | 96.6 | 103.5 | 77.3 | 72.9 | 88.0 *** |

| * ENOB [bit] | 14.1 | 15.8 | 16.9 | 12.5 | 11.8 | 14.3 |

| Power [μW] | 1098 | 2770 | 24,000 | 13.5 | 20,400 | 249.1 |

| ** FoMS [dB] | 171.1 | 173.6 | 173.7 | 174.0 | 162.8 | 174.0 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Hao, X.; Yuan, Y.; Pan, J.; Lu, Z.; Song, S.; Yu, X.; Zhao, M. An 88 dB SNDR 100 kHz BW Sturdy MASH Delta-Sigma Modulator Using Self-Cascoded Floating Inverter Amplifiers. Electronics 2024, 13, 3865. https://doi.org/10.3390/electronics13193865

Hao X, Yuan Y, Pan J, Lu Z, Song S, Yu X, Zhao M. An 88 dB SNDR 100 kHz BW Sturdy MASH Delta-Sigma Modulator Using Self-Cascoded Floating Inverter Amplifiers. Electronics. 2024; 13(19):3865. https://doi.org/10.3390/electronics13193865

Chicago/Turabian StyleHao, Xirui, Yidong Yuan, Jie Pan, Zhaonan Lu, Shuang Song, Xiaopeng Yu, and Menglian Zhao. 2024. "An 88 dB SNDR 100 kHz BW Sturdy MASH Delta-Sigma Modulator Using Self-Cascoded Floating Inverter Amplifiers" Electronics 13, no. 19: 3865. https://doi.org/10.3390/electronics13193865