Test Solution for Heatsinks in Power Electronics Applications

Abstract

:1. Introduction

2. Background

2.1. End-of-Manufacturing Tests

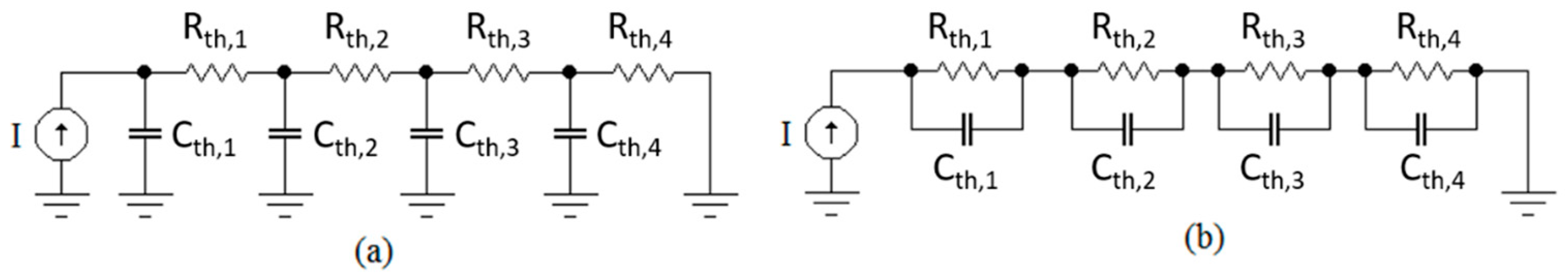

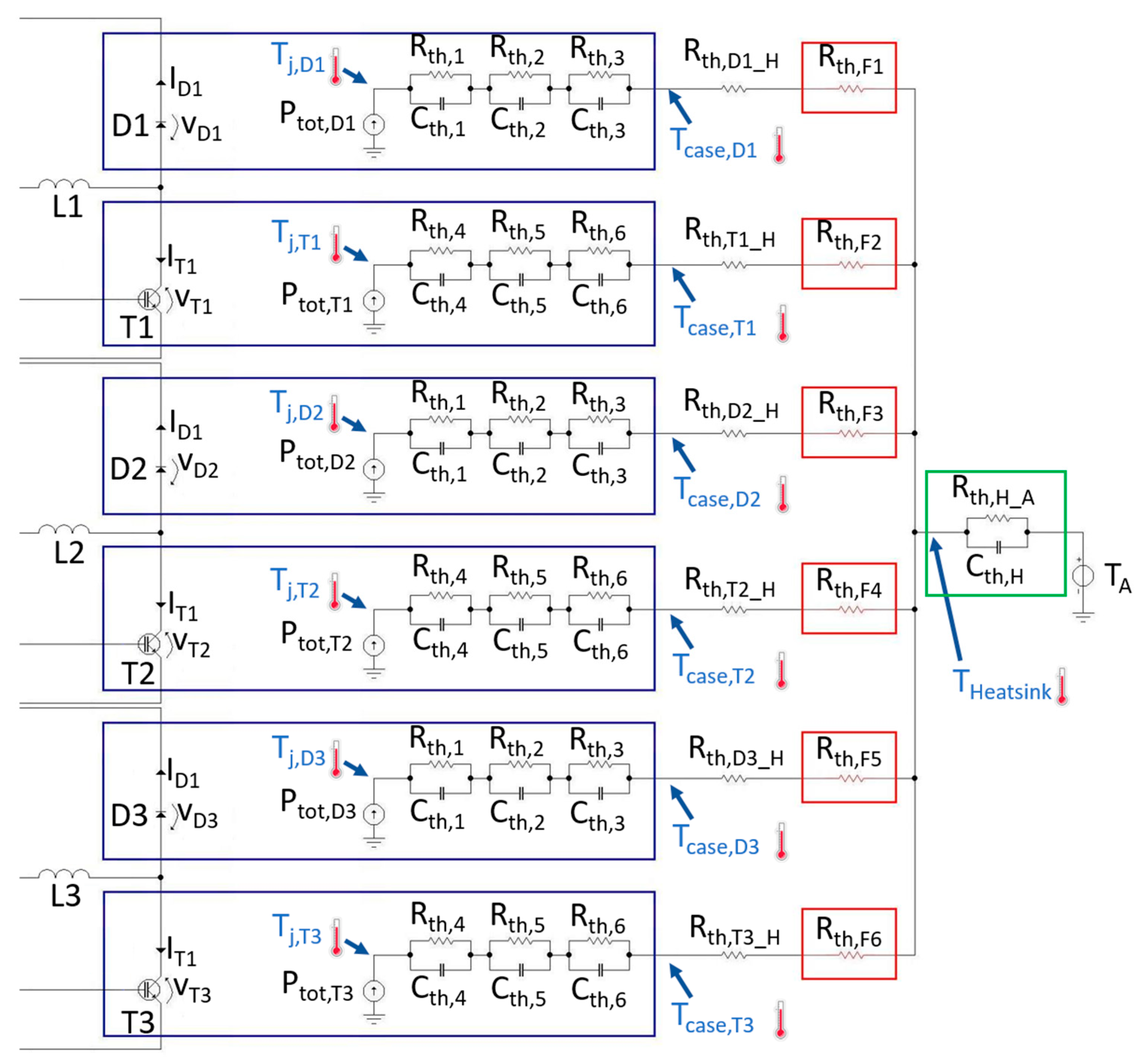

2.2. Thermal Model Concept

2.3. Temperature-Sensitive Electrical Parameters (TSEPs)

3. Proposed Approach

3.1. Thermal Faults

3.2. Thermal Faults Simulation

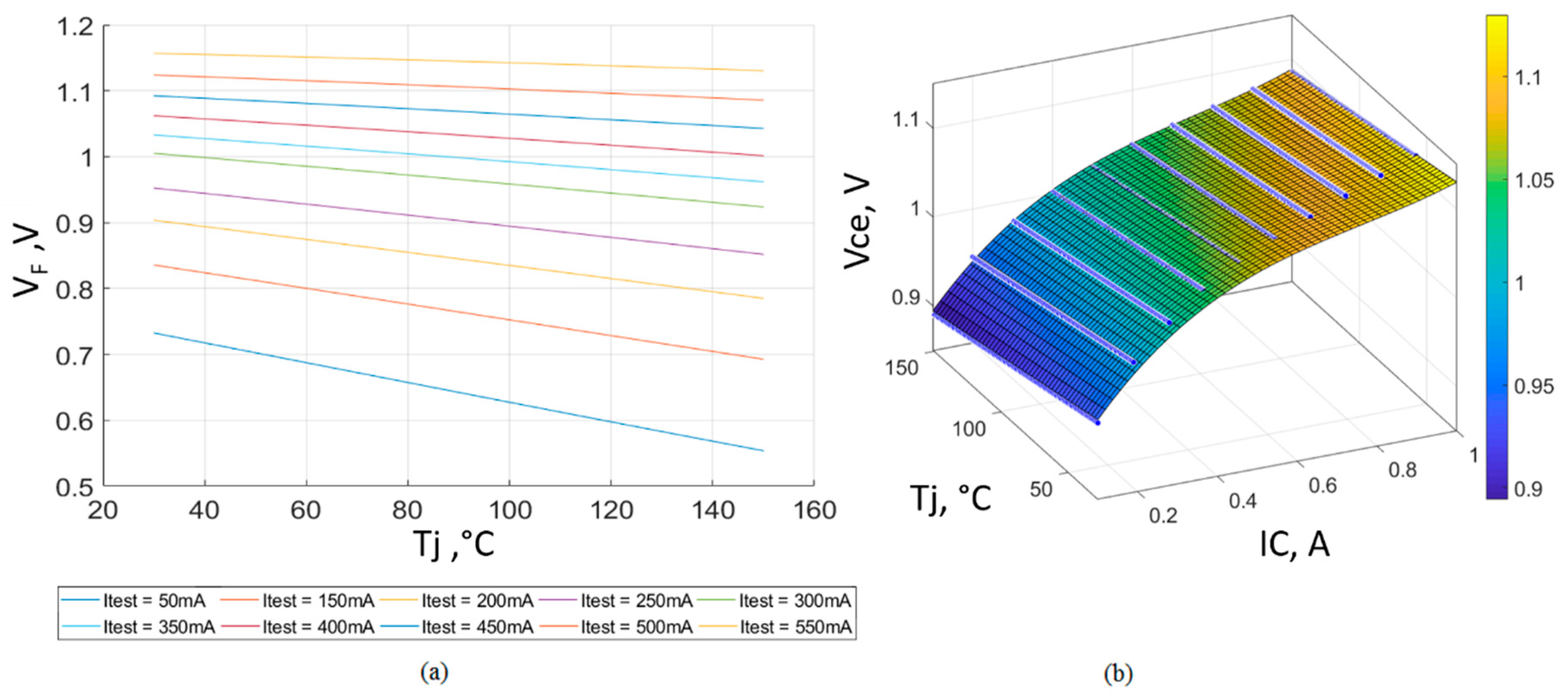

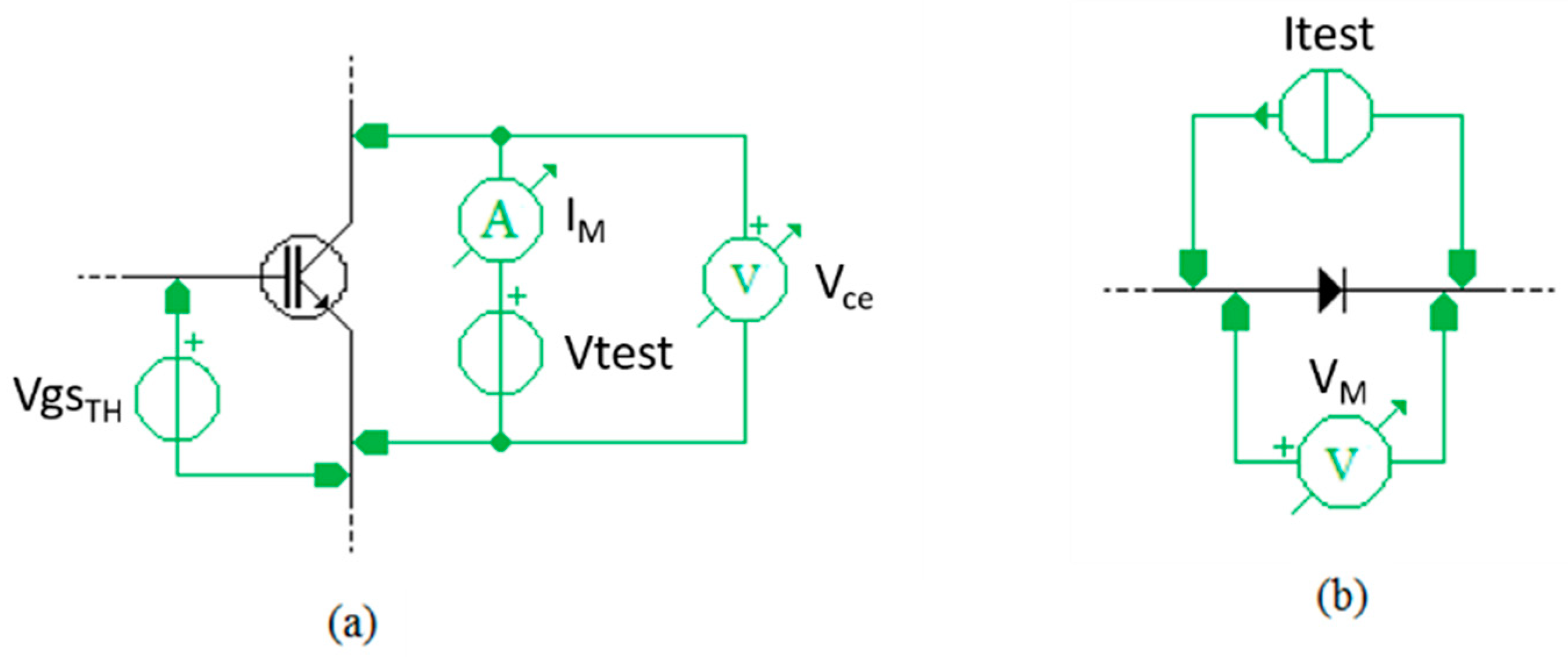

3.3. TSEP Test Characterization

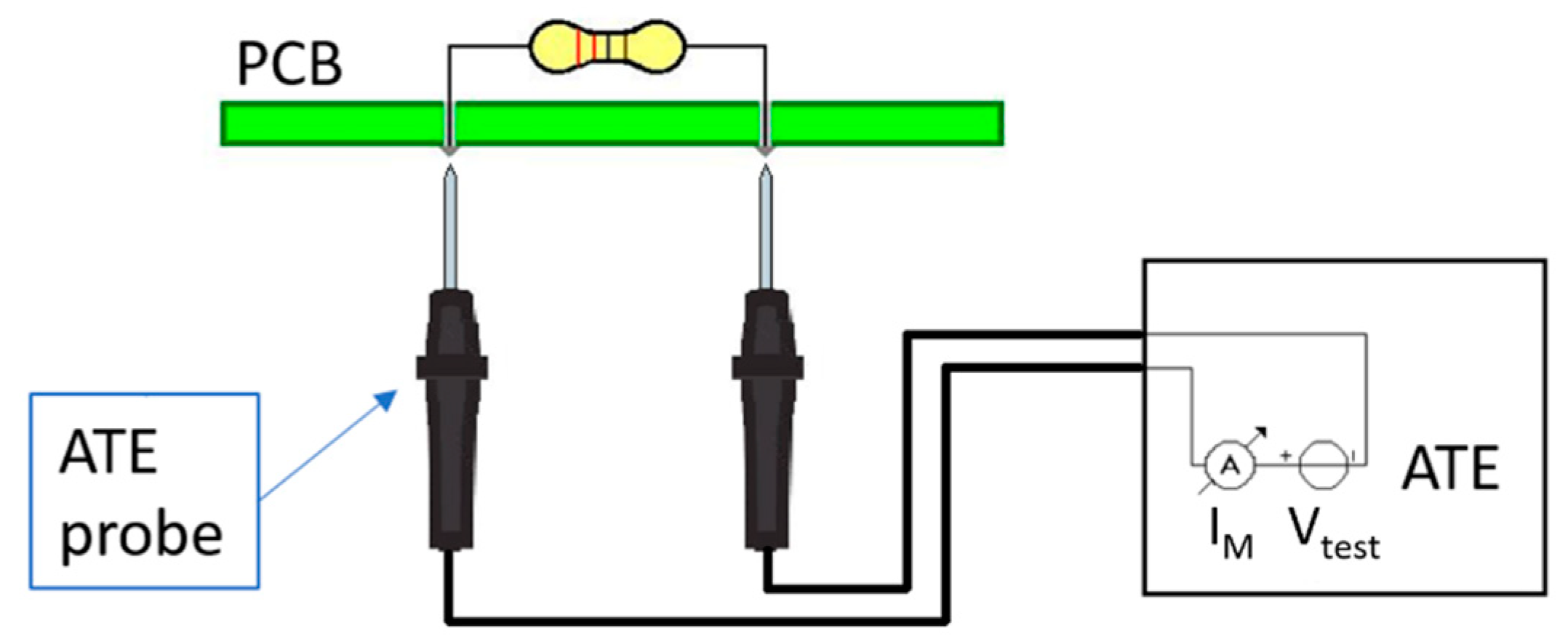

3.4. In-Circuit Thermal Test

3.5. Functional Thermal Test

4. Case Study

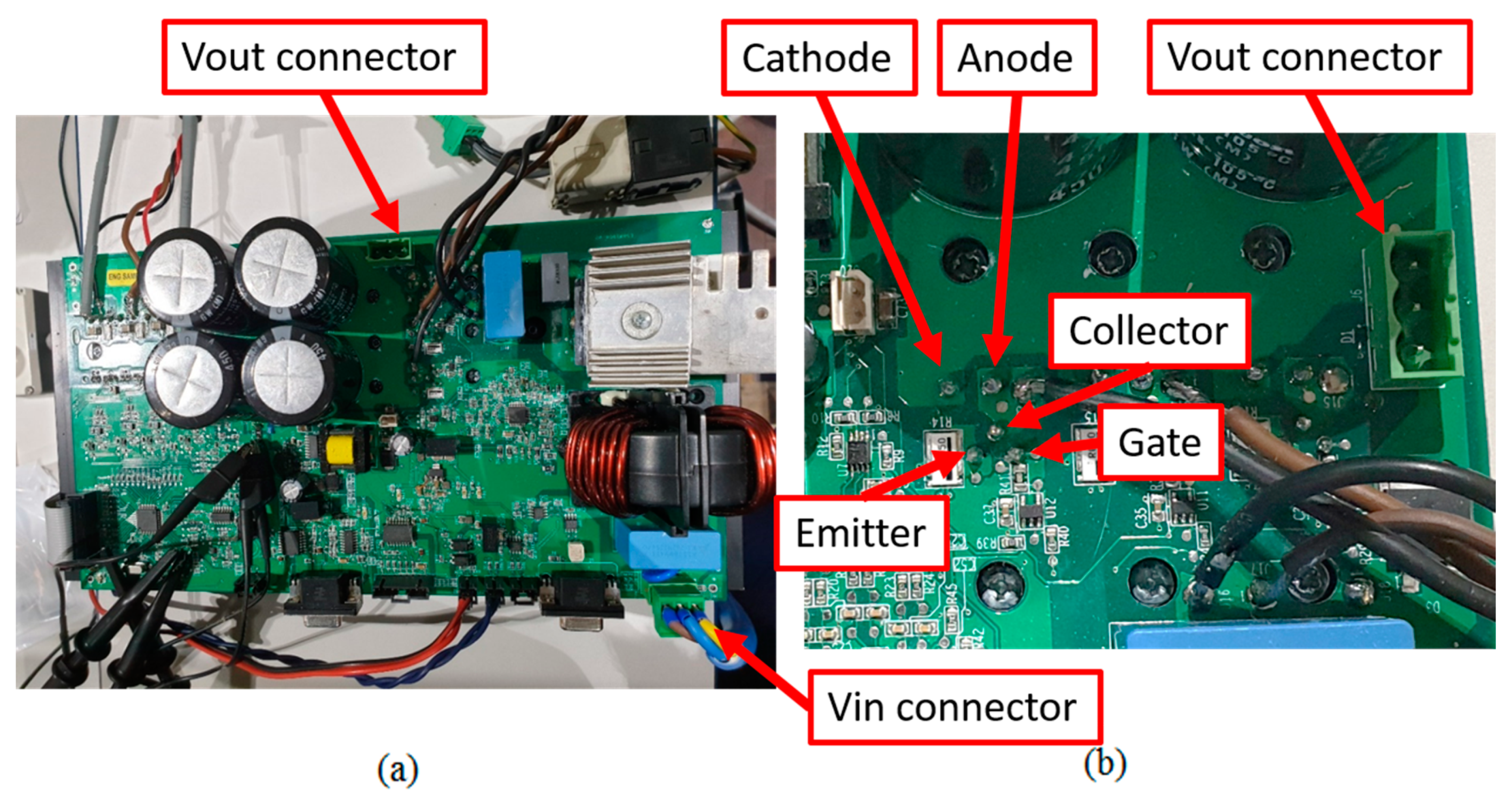

4.1. The Power Supply Unit

4.2. Thermal Model of the PSU Cooling System

5. Results Analysis

5.1. In-Circuit Thermal Test

5.2. Functional Thermal Test

5.3. Tests Results

6. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Jose, J.; Ravindran, A.; Nair, K.K. Study of temperature dependency on MOSFET parameter using MATLAB. Res. J. Eng. Technol. 2016, 3, 1530–1533. [Google Scholar]

- Baodong, B.; Dezhi, C. Inverter IGBT loss analysis and calculation. In Proceedings of the 2013 IEEE International Conference on Industrial Technology (ICIT), Cape Town, South Africa, 25–28 April 2013; pp. 563–569. [Google Scholar]

- Vassighi, A.; Sachdev, M. Thermal and Power Management of Integrated Circuits; Springer: Berlin/Heidelberg, Germany, 2006; ISBN 978-1-4419-3832-9. [Google Scholar]

- Chen, H.; Ji, B.; Pickert, V.; Cao, W. Real-time temperature estimation for power MOSFETs considering thermal aging effects. IEEE Trans. Device Mater. Reliab. 2014, 14, 220–228. [Google Scholar] [CrossRef]

- Dusmez, S.; Duran, H.; Akin, B. Remaining useful lifetime estimation for thermally stressed power mosfets based on on-state resistance variation. IEEE Trans. Ind. Appl. 2016, 52, 2554–2563. [Google Scholar] [CrossRef]

- Russo, S.; Bazzano, G.; Cavallaro, D.; Sitta, A.; Calabretta, M. Thermal analysis approach for predicting power device lifetime. IEEE Trans. Device Mater. Reliab. 2019, 19, 159–163. [Google Scholar] [CrossRef]

- High-Power Device. Toshiba Application Note 2016-12-05. Available online: https://www.google.com/url?sa=t&rct=j&q=&esrc=s&source=web&cd=1&ved=2ahUKEwithNvTq_7nAhWQCOwKHQ77CVQQFjAAegQIBBAB&url=https%3A%2F%2Ftoshiba.semicon-storage.com%2Finfo%2Fdocget.jsp%3Fdid%3D60472&usg=AOvVaw2GiUlKBN7lxE7civ593myo (accessed on 12 May 2016).

- Mersen, Cooling of Power Electronics—Solutions for Power Management. Available online: https://www.mersen.com/sites/default/files/publications-media/4-spm-cooling-of-power-electronics-mersen.pdf (accessed on 1 January 2017).

- Quitadamo, M.V.; Piumatti, D.; Sonza Reorda, M.; Fiori, F. Faults detection in the heatsinks mounted on power electronic transistors. Inter. J. Electr. Electron. Eng. Telecommun. 2020, 9, 206–212. [Google Scholar] [CrossRef]

- Piumatti, D.; Quitadamo, M.V.; Sonza Reorda, M.; Fiori, F. testing heatsink faults in power transistors by means of thermal model. In Proceedings of the 2020 IEEE Latin-American Test Symposium (LATS), Maceio, Brazil, 30 March–2 April 2020; pp. 1–6. [Google Scholar]

- Khandpur, R.S. Printed Circuit Boards Design, Fabrication, and Assembly; McGraw-Hill Education Book: New York, NY, USA, 2005; ISBN 0071331476. [Google Scholar]

- Coombs, C.; Holden, H. Printed Circuits Handbook, 7th ed.; McGraw-Hill Education Book: New York, NY, USA, 2016; ISBN 9780071833950. [Google Scholar]

- Introduction to the In-Circuit Testing. GenRad. 1984. Available online: https://www.ietlabs.com/pdf/Handbooks/Introduction%20to%20In-Circuit%20Testing.pdf (accessed on 1 January 1984).

- Crandall, E. Power Supply Testing Handbook: Strategic Approaches in Test Cost Reduction; Springer: Berlin/Heidelberg, Germany, 1997; ISBN 978-1-4615-6055-5. [Google Scholar]

- Piumatti, D.; Borlo, S.; Mandrile, F.; Reorda, M.S.; Bojoi, R. Assessing the effectiveness of the test of power devices at the board level. In Proceedings of the 2019 XXXIV Conference on Design of Circuits and Integrated Systems (DCIS), Bilbao, Spain, 20–22 November 2019; pp. 1–6. [Google Scholar]

- Thermal Modeling of Power-electronic Systems. Dr. Martin März, Fraunhofer Institute for Integrated Circuits IIS-B, Erlangen Paul Nance, Infineon Technologies AG, Munich, Document. Available online: https://www.iisb.fraunhofer.de (accessed on 1 February 2000).

- Thermal System Modeling. Dr. Martin März, Paul Nance, Infineon Technologies AG, Munich, Document. Available online: https://www.infineon.com (accessed on 1 February 2000).

- Shahjalal, M. Electric-thermal Modelling of Power Electronics Components. Ph.D. Thesis, University of Greenwich, London, UK, 2018. Available online: https://gala.gre.ac.uk/id/eprint/23658/1/Mohammad%20Shahjalal%202018%20-%20secured.pdf (accessed on 1 April 2018).

- Altet, J.; Rubio, A. Thermal Testing of Integrated Circuits; Springer Book: Berlin/Heidelberg, Germany, 2002; ISBN 978-1-4419-5287-5. [Google Scholar]

- Sathik, M.H.M.; Pou, J.; Prasanth, S.; Muthu, V.; Simanjorang, R.; Gupta, A.K. Comparison of IGBT junction temperature measurement and estimation methods-a review. In Proceedings of the 2017 Asian Conference on Energy, Power and Transportation Electrification (ACEPT), Singapore, 24–26 October 2017; pp. 1–8. [Google Scholar]

- Kadir, E.; Songül, D.; Nuhoglu, C.; Urhan, F.; Turut, A. Effect of temperature on the current (capacitance and conductance)–voltage characteristics of Ti/n-GaAs diode. J. Appl. Phys. 2014, 116, 234503. [Google Scholar]

- Cao, H.; Ning, P.; Yuan, T.; Wen, X. Online monitoring of IGBT junction temperature based on vce measuremnt. In Proceedings of the 2019 22nd International Conference on Electrical Machines and Systems (ICEMS), Harbin, China, 11–14 August 2019; pp. 1–5. [Google Scholar]

- Andrew Sawle and Arthur Woodworth Mounting Guidelines for the Super-247, International Rectifier, Application Note AN-997. Available online: https://www.fer.unizg.hr/_download/repository/ineu_sasa/06_Hladnjaci/Predavanje-Spoj_tr_na_hladnjak.pdf (accessed on 22 May 2020).

- Künzi, R. Thermal Design of Power Electronic Circuits. In Proceedings of the CAS-CERN Accelerator School: Power Converters, Baden, Switzerland, 7–14 May 2014. [Google Scholar]

- Zhou, Z.; Holland, P.M.; Igic, P. Compact thermal model of a three-phase IGBT inverter power module. In Proceedings of the 2008 26th International Conference on Microelectronics, Nis, Serbia & Montenegro, 11–14 May 2008; pp. 167–170. [Google Scholar]

- Thermal Design of Light Emitting Diode” NICHIA, Application Note, SE-AP00002. 15 June 2011. Available online: https://www.nichia.co.jp/specification/products/led/ApplicationNote_SE-AP00002-E.pdf (accessed on 22 May 2020).

- Ocaya, R. An experiment to profile the voltage, current and temperature behaviour of a P–N diode. Eur. J. Phys. 2006, 27, 625. [Google Scholar] [CrossRef]

- FAN9673 Three-Channel Interleaved CCM PFC Controller, Datasheet. Available online: https://www.onsemi.com/pub/Collateral/FAN9673-D.PDF (accessed on 1 June 2019).

- STTH12S06 STMicroelectronics Datasheet. Available online: https://www.st.com/resource/en/datasheet/stth12s06.pdf (accessed on 1 October 2007).

- STDGB19NC60HDT4 Power IGBT developed by STMicroelectronics, Datasheet. Available online: https://www.st.com/resource/en/datasheet/stgb19nc60hdt4.pdf (accessed on 1 September 2016).

- SK 56 Heatsink Datasheet Produced by Fischer Elektronik, Datasheet. Available online: https://www.fischerelektronik.de/web_fischer/en_GB/heatsinks/A01/Standard%20extruded%20heatsinks/PR/SK56_/$productCard/parameters/index.xhtml (accessed on 13 October 2006).

- Merrikh, A.; McNamara, A.J. Parametric evaluation of foster RC-network for predicting transient evolution of natural convection and radiation around a flat plate. In Proceedings of the Fourteenth Intersociety Conference on Thermal and Thermomechanical Phenomena in Electronic Systems (ITherm), Orlando, FL, USA, 27–30 May 2014. [Google Scholar]

- PLECS Tool Reference. Available online: https://www.plexim.com/home (accessed on 5 January 2020).

| Rth,F2 (°C/W) | IM (A) | Vce,T1 (V) | Tj,T1 (°C) | TCASE,T1 (°C) | THEATSINK (°C) | |

|---|---|---|---|---|---|---|

| Fault-free | 0 | 1.04 | 1.41 | 72 | 42 | 26 |

| With fault | 10.3 | 1.27 | 1.43 | 148 | 117 | 25 |

| Rth,F1 (°C/W) | VM (V) | Tj,D (°C) | TCASE,D1 (°C) | THEATSINK (°C) | |

|---|---|---|---|---|---|

| Fault-free | 0 | 1.46 | 31.2 | 27.2 | 25.4 |

| With fault | 16.7 | 1.45 | 176.3 | 51.7 | 25.5 |

| Rth,F2 (°C/W) | IL (A) | IA (A) | Vout (V) | Vce,T1 (V) | Tj,T1 (°C) | TCASE,T1 (°C) | THEATSINK (°C) | |

|---|---|---|---|---|---|---|---|---|

| Fault-free | 0 | 8.5 | 16.1 | 400 | 0.75 | 71.1 | 33.7 | 28.3 |

| With fault | 10.3 | 8.5 | 16.1 | 400 | 1.21 | 151.2 | 86.3 | 28.5 |

| Rth,F1 (°C/W) | IL (A) | IA (A) | Vout (V) | VF,D1 (V) | Tj,D1 (°C) | TCASE,D1 (°C) | THEATSINK (°C) | |

|---|---|---|---|---|---|---|---|---|

| Fault-free | 0 | 8.5 | 16.1 | 400 | 1.3 | 82.9 | 38.4 | 28.2 |

| With fault | 16.7 | 8.5 | 16.1 | 400 | 1.1 | 181.1 | 95.6 | 28.4 |

| Thermal Fault | Power Device | In-Circuit | Base Functional Test | Observability Enhanced Functional Test |

|---|---|---|---|---|

| Rth,F1; Rth,F3; Rth,F5 | Diodes D1, D2, D3 | NDT | NDT | DT |

| Rth,F2; Rth,F4; Rth,F6 | IGBTs T1, T2, T3 | DT | NDT | DT |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Piumatti, D.; Borlo, S.; Quitadamo, M.V.; Sonza Reorda, M.; Giacomo Armando, E.; Fiori, F. Test Solution for Heatsinks in Power Electronics Applications. Electronics 2020, 9, 1020. https://doi.org/10.3390/electronics9061020

Piumatti D, Borlo S, Quitadamo MV, Sonza Reorda M, Giacomo Armando E, Fiori F. Test Solution for Heatsinks in Power Electronics Applications. Electronics. 2020; 9(6):1020. https://doi.org/10.3390/electronics9061020

Chicago/Turabian StylePiumatti, Davide, Stefano Borlo, Matteo Vincenzo Quitadamo, Matteo Sonza Reorda, Eric Giacomo Armando, and Franco Fiori. 2020. "Test Solution for Heatsinks in Power Electronics Applications" Electronics 9, no. 6: 1020. https://doi.org/10.3390/electronics9061020